用quartusⅡ设计一个四位二进制全减器

- 格式:doc

- 大小:65.50 KB

- 文档页数:3

实验一一名二进制全减器设计一、实验目的1.学习一般的数字电路设计;2.学习数码管的输出方式;3.进一步熟悉Quartes II集成开发软件的利用和PH-1V型实验装置的利用二、实验内容与要求采用原理图输入法和文本输入法别离实现,分层设计,底层由半减器和逻辑组成。

三、设计思路半减器真值表如下X Y DIFF SUB_OUT0 0 0 00 1 1 11 0 1 01 1 0 0XIN YIN SUB_IN DIFF SUB_OUT0 0 0 0 01 0 0 1 00 1 0 1 11 1 0 0 00 0 1 1 10 1 1 0 11 0 1 0 01 1 1 1 1原理图如下四、实验程序半减器:LIBRARY IEEE;USE h_suber IsPORT(X,Y:IN STD_LOGIC;Diff1,s_out1:OUT STD_LOGIC);END ENTITY h_suber;ARCHITECTURE fh1 OF h_suber IsBEGINDiff1<=X XOR Y;s_out1<=(NOT X)AND Y;END ARCHITECTURE fh1;或门:LIBRARY IEEE;USE or2a ISPORT(a,b:IN STD_LOGIC;c:OUT STD_LOGIC);END ENTITY or2a;ARCHITECTURE one OF or2a ISBEGINc<=a OR b;END ARCHITECTURE one;五、实验步骤成立工作库文件夹和编辑设计文件;1)打开quartusII,成立新的工程文件,命名为f_suber保留在E:\object\。

2)新成立一个VHDL文件,输入半减器文本和或门文本,别离保留为h_suber和or2a。

3)编译无误后,在File菜单下选择Create下拉菜单里的Creat Symbol选项将两个文件制作成元件。

数电实验报告—四位减法器实验报告学生姓名:班级学号:指导老师:38033 9一、实验名称:1.进一步学习quartusII的基本功能和使用方法,完成四位减法器原理图输入和文本输入、编译校验及功能仿真2.进一步学习quartusII的基本功能和使用方法,完成yf(a,b,c)!((a&b)|c)所对应逻辑电路设计及功能仿真。

二、实验学时:4学时三、实验目的:熟悉Quartus II基本功能和使用方法,掌握原理图输入、文本输入的步骤。

四、实验内容:完成四位减法器原理图输入和文本输入、编译校验及功能仿真;完成yf(a,b,c)!((a&b)|c)所对应逻辑电路设计及功能仿真。

五、实验原理:数字逻辑电路中各种门电路的功能和使用方法及quartusII的运用。

六、实验步骤:1)原理图输入方法:通过本部分重点学习元器件的放置、连线、电源、地的表示,标号的使用,输入、输出的设置,以及各种元件库的使用等。

①创建文件②创建元器件③设置输入输出④添加连接线:将选定期间及设置好的输入输出按照设计好的原理图进行正确连线。

2)文本输入方式学习verilog语言的扩展文件名位.v,verilog 文件名必须与实体文件名保持一致,文件必须放在一个工程中。

①创建verilog HDL源程序文件②用verilog HDL进行二选一数据选择器逻辑功能描述设计编译校验①建立仿真波形文件②添加仿真测试点③添加输入端仿真信号④开始仿真七、实验结果:A.四位减法器原理图:文本:波形图:B.完成yf(a,b,c)!((a&b)|c)所对应逻辑电路设计及功能仿真。

原理图:波形图:八、心得体会:这是使用这个软件的第三次实验对于软件的使用已经比较熟练能够很快连接好电路进行试验九、附录:四位减法器module fourbit(A,B,CI,CO,S); parameter size=4; input [size:1]A,B; output [size:1]S; input CI; output CO;wire [1:size-1]Temp;onebitadd1(A[1],B[1],CI,S[1],Temp[1]),add2(A[2],B[2],Temp[1],S[2],Temp[2]), add3(A[3],B[3],Temp[2],S[3],Temp[3]),add4(A[4],B[4],Temp[3],S[4],CO); endmodulemodule onebit(A,B,CI,CO,S); input A,B,CI; output CO,S;wire n1,n2,n3,out1,out2,out3,out4,out5,out6,out7; notnoti1(n1,CI), noti2(n2,A), noti3(n3,B); andand1(out1,n1,n2), and2(out2,n2,n3), and3(out3,n1,n3), and4(out4,CI,A,B), and5(out5,n1,A,B), and6(out6,n1,n2,n3), and7(out7,CI,B,n3); nornor1(CO,out1,out2,out3), nor2(S,out4,out5,out6,out7); endmodule实验报告学生姓名:班级学号:指导老师:38033 9一、实验名称:1.进一步学习quartusII的基本功能和使用方法,完成四位减法器原理图输入和文本输入、编译校验及功能仿真2.进一步学习quartusII的基本功能和使用方法,完成yf(a,b,c)!((a&b)|c)所对应逻辑电路设计及功能仿真。

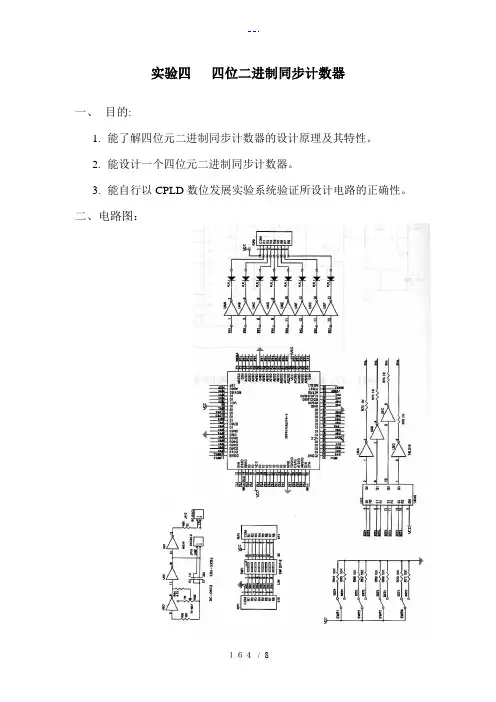

实验四四位二进制同步计数器一、目的:1.能了解四位元二进制同步计数器的设计原理及其特性。

2.能设计一个四位元二进制同步计数器。

3.能自行以CPLD数位发展实验系统验证所设计电路的正确性。

二、电路图:三、实验器配置图:四、实验步骤与画面:1.建立一个名为count16.vhd的新文件,并在QuartusⅡ文字编辑器中,以VHDL语言来设计程式,图为四位二进制计数器的VHDL代码。

其中clk为时钟端口,clk为异步清零端,Q为计数输出端口,co为进位输出端口。

2.存储、检查及编译。

3.创建元件符号。

4.创建波形文件,设定合适的端口信号,仿真元件的波形。

观察波形图可以看出当芯片可以实现16进制计数功能。

五、相关说明:1.同步计数器的意义是将所有正反器的时脉连接在一起,当时脉进来时,所有的正反器同时被触发而动作,因此传递延迟时间就可以大为缩短,计数的速度就会增快。

2.我们可以利用MAX+plusⅡ的Timing Analyzer来比较同步计数器与非同步计数器(单元十)的传递延迟状况,图U12-3(a)与图U12-3(b)为分析所得结果,从图中可以发现,同步计数器从时脉输入到各级的输出,其传递延迟时间皆相同,而非同步计数器则越到后级传递延迟时间越长。

3.图U12-2的程式设计方法,也可以改用D型正反器来设计,如图U12-4所示,您可以发现此种设计同步计数器的方法较简洁。

4.若要将图U12-4改成下数计数器,只要将叙述ff[].d=ff[].q+1;改成ff[].d=ff[].q-l;即可。

5.图U12-5为四位元含致能及清除的模10上下数计数器,其中的设计重点为:(1)为了能在高频计数电路应用,本电路的清除方式采同步清除式设计,并不利用正反器本身的elrn脚,而是当clr脚输入为鬲态时,令所有正反器的D输入脚为o,达到清除的目的。

(2)程式中使用了巢状的IF THEN叙述,须注意每一层的IF THEN、 ELSIF、ELSE及END IF的对应,不要弄乱了,否则会很麻烦。

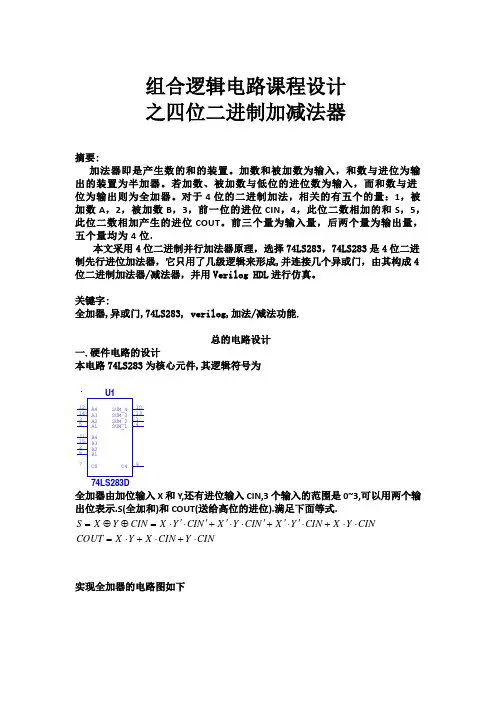

组合逻辑电路课程设计之四位二进制加减法器摘要:加法器即是产生数的和的装置。

加数和被加数为输入,和数与进位为输出的装置为半加器。

若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。

对于4位的二进制加法,相关的有五个的量:1,被加数A ,2,被加数B ,3,前一位的进位CIN ,4,此位二数相加的和S ,5,此位二数相加产生的进位COUT 。

前三个量为输入量,后两个量为输出量,五个量均为4位.本文采用4位二进制并行加法器原理,选择74LS283,74LS283是4位二进制先行进位加法器,它只用了几级逻辑来形成,并连接几个异或门,由其构成4位二进制加法器/减法器,并用Verilog HDL 进行仿真。

关键字:全加器,异或门,74LS283, verilog,加法/减法功能.总的电路设计 一.硬件电路的设计本电路74LS283为核心元件,其逻辑符号为U174LS283DSUM_410SUM_313SUM_14SUM_21C49B411A412B315A314B22A23B16A15C07全加器由加位输入X 和Y ,还有进位输入CIN,3个输入的范围是0~3,可以用两个输出位表示.S(全加和)和COUT(送给高位的进位).满足下面等式.CINY CIN X Y X COUT CINY X CIN Y X N CI Y X N CI Y X CIN Y X S ⋅+⋅+⋅=⋅⋅+⋅'⋅'+'⋅⋅'+'⋅'⋅=⊕⊕=实现全加器的电路图如下74LS08D本电路还需要4个异或门,要实现加法器和减法器的双重功能,需要有选择功能端,设A为四位二进制被加数,B为二进制被减数.当使能端为0时,电路实现加法运算,当使能端为1时电路实现减法运算.电路原理图如下1.Multisim原理图2.MAX plus2原理图当A口输入为0011,B口输入为0001,使能端为0时.输出为0100.电路图如下当A口输入为0011,B口输入为0001,使能端输入为1时.输出为0010.电路图如下二.软件程序设计Verilog HDL语言程序module b(A,B,C,D,E);input[3:0] A,B;input C;output[3:0] D;output E;assign {E,D}=C?(A+B):(A-B);endmodule当A口输入为0011,B口输入为0001,使能端输入为0,输出为0010,仿真图如下.当A口输入为0011,B口输入为0001,使能端输入为1时.输出为0010.仿真图如下三.总结及心得体会1.通过本次课题设计,自学了一些相关的Verilog语言和MAX+plusII,Multisim 软件的使用方法.2.基本掌握了74LS283的基本原理及使用方法.。

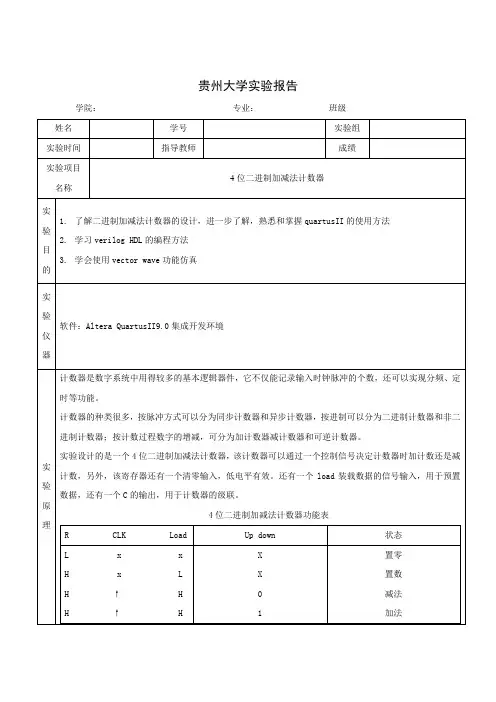

贵州大学实验报告学院:专业:班级设计原理框图从原理图中可见,需要有1bit装载位(load)、1bit清零位(clr)、方向控制位up_down和4bit数据选择位DIN[3..0]。

装载位我们采用SW0,清零位采用SW1,方向控制位为SW2。

SW3-SW6作为数据输入端,LED1-LED4显示数据的输出,LED5为溢出标志位。

实验内容编写一个带预置输入,清零输入,可加可减计数器的verilog代码或VHDL代码并仿真,编译下载验证module counter4(load,clr,c,DOUT,clk,up_down,DIN);//定义模块input load;//定义输入信号input clk;//wire load;//定义线网型input clr;//wire clr;//input up_down;//wire up_down;//input [3:0]DIN;//定义4位二进制输入信号wire [3:0]DIN;// 定义4位二进制线网型信号output c;//定义输出信号reg c;//定义寄存器类型信号output [3:0]DOUT;//wire [3:0]DOUT;reg [3:0]data_r;assign DOUT=data_r;always@(posedge clk or posedge clr or posedge load)//检测clk,clr,load的上升沿beginif(clr)//当clr=1的时候进行下面的运行程序data_r<=0;//将data_r置零else if(load) //当load=1的时候进行下面的运行程序data_r<=DIN;//将DIN的值赋给data_relse begin if(up_down)//load=0的时候进行下面的操作beginif(data_r==4'b1111)begin///当data_r==4'b1111的时候进行下面的运行程序data_r<=4'b0000;c=1;endelse begin//当data_r不等于4'b1111的时候进行下面的运行程序data_r<=data_r+1;//进行加法计数c=0;endendelsebeginif(data_r==4'b0000)begin//当data_r==4'b0000的时候进行下面的运行程序data_r<=4'b1111;c=1;endelse begin//当data_r不等于4'b1111的时候进行下面的运行程序data_r<=data_r-1;//进行减法计数c=0;endendendendendmodule//结束模块实验数据如图为波形仿真结果,当clr为1的时候,输出结果为0000;当clr为0,load为1时,输出结果为输入数据DIN的值,当up_down为1时,加法进位,进行加1运算,当data_r达到1111时,data_r变为0000,级零信号c为1;当up_down为0时,减法进位,进行减1运算,当data_r达到0000时,data_r变为1111,级零信号c为0。

实验2 Quartus II实现全加全减器

一.实验目的

1 、了解可编程数字系统设计的流程;

2 、掌握Quartus II 软件的使用方法;

3 、掌握采用硬件描述语言设计数字系统的方法和流程。

二、实验设备

1、计算机:Quartus II 软件;

2、Altera DE0 多媒体开发平台。

三、实验内容

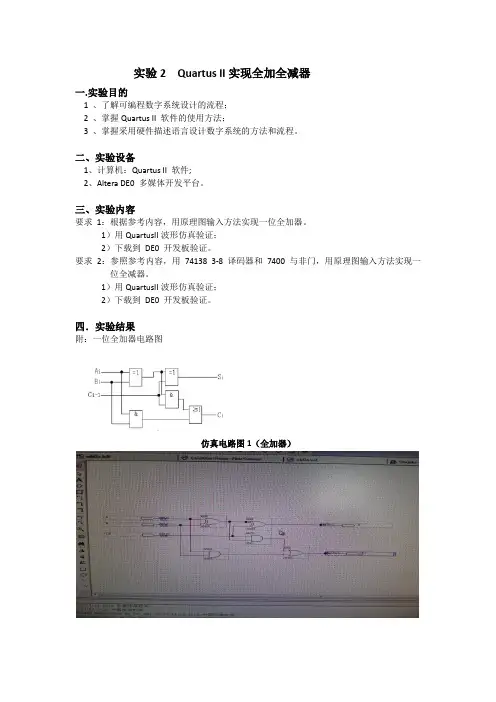

要求1:根据参考内容,用原理图输入方法实现一位全加器。

1)用QuartusII波形仿真验证;

2)下载到DE0 开发板验证。

要求2:参照参考内容,用74138 3-8 译码器和7400 与非门,用原理图输入方法实现一位全减器。

1)用QuartusII波形仿真验证;

2)下载到DE0 开发板验证。

四.实验结果

附:一位全加器电路图

仿真电路图1(全加器)

仿真电路图2(全减器)

波形仿真图1

波形仿真图2

工程运行成功

引脚示意图

五.实验心得

1)整个实验并不难,难度在于软件的使用。

第一次使用这个软件肯定会有很多不会的地方,不过我们慢慢看以及问同学总是可以解决的。

2)通过这个实验,我们对与非门有了更深刻的理解,对设计电路也有了一些具体的实践,相信在以后的学习中,还可以取得更深入的了解。

采用VHDL层次化文件设计一个四位全减器一、实训目的1.巩固VHDL层次化文件设计方法。

2.培养应用VHDL层次化文件设计法的技能。

二、实训器材计算机与Quartus Ⅱ工具软件。

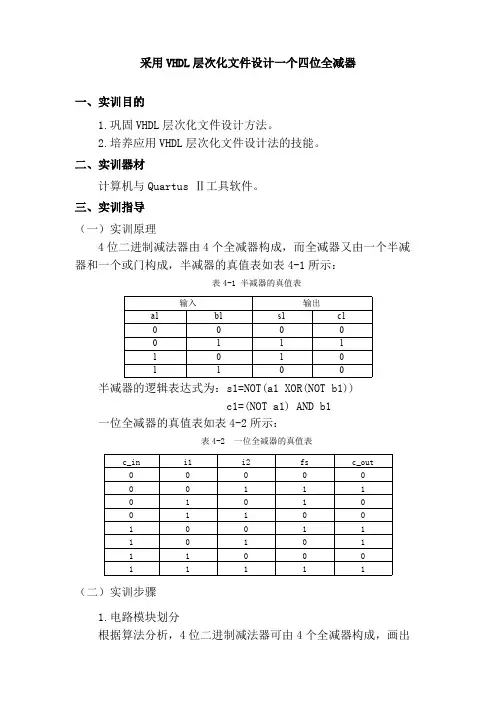

三、实训指导(一)实训原理4位二进制减法器由4个全减器构成,而全减器又由一个半减器和一个或门构成,半减器的真值表如表4-1所示:表4-1 半减器的真值表输入输出a1b1s1c10000011110101100半减器的逻辑表达式为:s1=NOT(a1 XOR(NOT b1))c1=(NOT a1) AND b1一位全减器的真值表如表4-2所示:表4-2 一位全减器的真值表c_in i1i2fs c_out0000000111010100110010011101011100011111(二)实训步骤1.电路模块划分根据算法分析,4位二进制减法器可由4个全减器构成,画出其原理方框图。

全减器的原理方框图如图4-1所示。

而每个全减器又可划分为一个半减器和一个或门这两个更小的模块,画出其原理方框图。

4位二进制减法器的原理方框图如图4-2所示。

图4-1一位全减器原理方框图图4-2 4位二进制减法器原理框图2.设计底层设计文件(1)设计半减器文件halfsub.vhd 。

(2)设计或门电路文件orgate.vhd 。

(3)设计全减器电路文件fullsub.vhd ,其中把半减器和或门电路文件作为元件调用。

3.设计顶层设计文件设计顶层设计文件sub4.vhd ,其中把全减器文件作为元件调用。

VHDL 代码如下:halfsub.vhd文件代码如下:ENTITY halfsub ISPORT(a1,b1:IN BIT;s1,c1:OUT BIT);END halfsub;ARCHITECTURE a OF halfsub ISBEGINPROCESS(a1,b1)BEGINs1<=NOT(a1 XOR(NOT b1)) AFTER 10ns; c1<=(NOT a1) AND b1 AFTER 10 ns;END PROCESS;END a;orgate.vhd文件代码如下:ENTITY orgate ISPORT(a,b:IN BIT;o:OUT BIT);END orgate;ARCHITECTURE a OF orgate ISBEGINo<=a OR b;END a;fullsub.vhd文件代码如下:ENTITY fullsub ISPORT(i1,i2,c_in:IN BIT;fs,c_out:OUT BIT);END fullsub;ARCHITECTURE a OF fullsub ISSIGNAL temp_s,temp_c1,temp_c2:BIT; COMPONENT halfsubPORT(a1,b1:IN BIT;s1,c1:OUT BIT);END COMPONENT;COMPONENT orgatePORT(a,b:IN BIT;o:OUT BIT);END COMPONENT;BEGINU0:halfsub PORT MAP(i1,i2,temp_s,temp_c1);U1:halfsub PORT MAP(temp_s,c_in,fs,temp_c2);U2:orgate PORT MAP(temp_c1,temp_c2,c_out);END a;sub4.vhd文件代码如下:ENTITY sub4 ISPORT(a,b:IN BIT_VECTOR(3 DOWNTO 0);cin:IN BIT;fs:OUT BIT_VECTOR(3 DOWNTO 0);cout:OUT BIT);END sub4;ARCHITECTURE a OF sub4 ISSIGNAL temp_co0,temp_co1,temp_co2:BIT;COMPONENT fullsub ISPORT(i1,i2,c_in:IN BIT;fs,c_out:OUT BIT);END COMPONENT;BEGINU0:fullsub PORT MAP(a(0),b(0),cin,fs(0),temp_co0);U1:fullsub PORT MAP(a(1),b(1),temp_co0,fs(1),temp_co1); U2:fullsub PORT MAP(a(2),b(2),temp_co1,fs(2),temp_co2); U3:fullsub PORT MAP(a(3),b(3),temp_co2,fs(3),cout); END a;1.编译顶层设计文件把以上各个模块的VHDL设计文件放入同一个文件夹中,以顶层文件建立工程,直接编译顶层文件同时也就编译各个底层模块文件。

E D A实验报告实验一、QuartusⅡ软件使用一、试验目的学习QUARTUS II软件的使用,掌握软件工程的建立、VHDL源文件的设计和波形仿真等基本内容;二、试验内容利用QuartusⅡ完成2选1多路选择器的文本编辑输入(mux21a.vhd)和仿真测试等步骤,给出仿真波形。

设计含有异步清零和计数使能的4位二进制加减可控计数器。

三、设计过程VHDL设计程序如下二选一:LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL ;USE IEEE.STD_LOGIC_UNSIGNED.ALL ;ENTITY mux21 ISPORT ( a, b : IN BIT;s : IN BIT;y : OUT BIT );END ENTITY mux21;-- behave descriptionARCHITECTURE one OF mux21 ISBEGINy <= a WHEN s = '0' ELSE b ;END ARCHITECTURE one ;四位二进制计数器:LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL ;USE IEEE.STD_LOGIC_UNSIGNED.ALL ; -- 运算符重载ENTITY mycounter ISPORT ( ena,clr,d_ctr,clk : IN STD_LOGIC ;q : OUT STD_LOGIC_VECTOR(3 DOWNTO 0 )) ;END ENTITY mycounter;ARCHITECTURE bhv OF mycounter ISSIGNAL q1 : STD_LOGIC_VECTOR(3 DOWNTO 0 );BEGINq <= q1 ;PROCESS (clk,clr,ena,d_ctr)BEGINIF clr='1' THEN q1<="0000";ELSIF clk'EVENT AND clk = '1' THENIF ena='1' THENIF d_ctr='1' THENq1 <= q1 + '1';ELSEq1<=q1-'1';END IF;ELSEq1<=q1;END IF;END IF;END PROCESS ;END ARCHITECTURE bhv;四、仿真波形与分析二选一:四位二进制计数器:实验二、原理图输入设计方法一、试验目的熟悉利用QUARTUS II中的原理图输入法设计组合电路,掌握层次化设计的方法,并通过一个4位全减器的设计把握文本和原理图输入方式设计的详细流程。

实验八 4位二进制计数器74x163的设计一、实验目的熟悉QuartusⅡ仿真软件的基本操作,并用VHDL/Verilog语言或者逻辑图完成4位二进制计数器74x163的设计。

二、实验内容用VHDL语言设计由边沿触发式D触发器构成的74x163四位二进制计数器,并进行仿真分析;(参看新、老教材中器件74x163的逻辑功能及其VHDL源代码)三、实验原理1.计数器是数字系统中用得较多的基本逻辑器件。

2.计数器的种类很多。

按时钟脉冲输入方式的不同,可分为同步计数器和异步计数器;按进位体制的不同,可分为二进制计数器和非二进制计数器;按计数过程中数字增减趋势的不同,可分为加计数器、减计数器和可逆计数器。

四、实验方法与步骤实验方法:采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII(或MaxplusⅡ)软件仿真平台,采用的硬件平台是Altera EPF10K20TI144_4的FPGA试验箱(由于实验室条件有限,无法实现)。

实验步骤:1)编写源代码。

打开QuartusII软件平台,点击File中得New建立一个文件。

编写的文件名与实体名一致,点击File/Save as以“.vhd”为扩展名存盘文件(画逻辑图实现则新建block文件)。

2)按照实验箱上FPGA的芯片名更改编程芯片的设置。

操作是点击Assign/Device,选取芯片的类型。

建议选“Altera的EPF10K20TI144_4”。

3)编译与调试。

确定源代码文件为当前工程文件,点击Complier进行文件编译。

编译结果有错误或警告,则将要调试修改直至文件编译成功。

4)波形仿真及验证。

在编译成功后,点击Waveform开始设计波形。

点击“insert the node”,按照程序所述插入节点。

任意设置输入节点的输入波形…点击保存按钮保存。

5)时序仿真。

将波形区域分段显示,如每个10.0ns重复一次步骤四,分别设置不同的a,b的输入波形,点击保存按钮保存,从而得出相应的结果,最后形成完整的连续的时序仿真图。

组合逻辑电路课程设计——4位二进制全加器/全减器作者:学号:课程设计题目要求:1)使用74LS283构成4位二进制全加/全减器。

2)阐述设计思路。

3)列出真值表。

4)画出设计的逻辑图。

5)用VHDL对所画电路进行仿真。

目录摘要 (1)1总电路设计 (2)1.1硬件电路的设计 (2)1.2全加器(full-adder ) (3)1.2.1四位二级制加法器 (4)1.2.1.1串行进位加法器 (4)1.2.1.2超前进位加法器 (5)1.2.1.3超前位链结构加法器 (5)1.3全减器(full-substracter ) (5)1.4总电路设计 (6)2设计思路 (7)2.1全加器 (7)2.2全减器 (7)3真值表 (8)4逻辑图与仿真 (9)5软件程序的设计 (13)6结果分析与总结 (15)摘要加法器是数字系统中产生数的和的装置。

加数和被加数为输入,和数与进位为输出的装置为半加器。

若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。

例如:为了节省资源,减法器和硬件乘法器都可以用加法器来构成。

但宽位加法器的设计是很耗资源的,因此在实际的设计和相关饿得设计与开发中需要注意资源的利用率和进位速度两方面的问题,多位加法器的构成主要有两种:并行进位和串行进位。

并行进位加法器设有并行进位产生逻辑,运行速度比串行进位快;串行进位是将全加器采取并行级联或菊花链式级联构成多位加法器。

加法器也是常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

此外还可以用来表示各种数值,如:BCD、加三码,主要的加法器是以二进制作运算。

本文将采用4位二进制并行加法器作为折中选择,所选加法器为74LS283,74LS283是4位二进制先行进位的加法器,它只用了几级逻辑来形成和及进位输出,故由其构成4位二进制全加器;而四位全减器可以用加法器简单的改造而来,最后本文采用 VHDL对四位全加器/全减器进行仿真。

关键字74LS283全加器、四位二进制、迭代电路、并行进位、串行进位、VHDL1总电路设计1.1硬件电路的设计该4位二进制全加器以74LS283为核心,74LS283芯片引脚图如下图,本文采用先行进位方式,极大地提高了电路运行速度,下面是对4位全加器电路设计的具体分析。

组合逻辑电路的课程设计之4位二进制全加\全减器(改进版——加法器与减法器的复合器)自动化工程学院摘要:加法器是产生数的和的装置。

加数和被加数为输入,和数与进位为输出的装置为半加器。

若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。

常用作计算机算算术逻辑部件,执行逻辑操作、移位与指指令调用。

在电子学中,加法器是一种数位电路,其可进行数字的加法计算。

在现代的电脑中,加法器存在于算术逻辑单元(ALU)之中。

加法器可以用来表示各种数值,如:BCD、加三码,主要的加法器是以二进制作运算。

简介:对于简单的四位二进制全加器,本文只做简要介绍,因为对于单一的加法器,显然是不够实用的,本文将着重就一种加法器与减法器的组合,即设计电路一个电路实现2个4位符号数(原码表示)的加减运算。

另有一个控制信号select 选择加法运算或减法运算。

若有溢出则产生溢出指示信号。

这种加法器与减法器的复合器将在实际操作中表现的更加的适用。

关键字:四位二进制全加器,四位二进制全减器,原理图Verilog HDL仿真电路的设计:常见的四位二进制全加器,通过两片74 283可以实现全加器的功能,即如下图所示:单一加法器的真值表如图所示:A3 A2 A1 A0 B3 B2 B1 B0 CIN S3 S2 S1 S0 COUT而详细的电路图为:加法器与减法器的复合器:接下来,我将对于这种加法器与减法器的复合器做详细介绍。

对于这种复合器,通过两个片子来实现。

而详细的电路如图所示:通过select作为选择端口,控制select的电平即可对加减复合器的加减功能进行选择,本电路中当当select接高电平是,选择的是加法器,当select接低电平时选择的是减法器,通过改变select的电平,可以轻松实现加法器和减法器的转换。

在用select选择了加法或是减法功能后,在输入端A3A2A1A0与B3B2B1B0分别为两个运算数的二进制代码,以高低电平来代表1或0,实现了目标数的输入。

<熟悉QuartusII和Verilog HDL数字逻辑电路设计基础环境>实验报告学生姓名:班级学号:***** 9指导老师:<实验报告内容>一、实验名称:1.进一步学习quartusII的基本功能和使用方法,完成四位减法器原理图输入和文本输入、编译校验及功能仿真2.进一步学习quartusII的基本功能和使用方法,完成caa=所对应逻辑电路设计及功能仿真。

by=fb((!&|)(c)),,二、实验学时:4学时三、实验目的:熟悉Quartus II基本功能和使用方法,掌握原理图输入、文本输入的步骤。

四、实验内容:完成四位减法器原理图输入和文本输入、编译校验及功能仿真;完成babcf=所对应逻辑电路设计及功能仿真。

y=a)|)(c&),,((!五、实验原理:数字逻辑电路中各种门电路的功能和使用方法及quartusII的运用。

六、实验步骤:1)原理图输入方法:通过本部分重点学习元器件的放置、连线、电源、地的表示,标号的使用,输入、输出的设置,以及各种元件库的使用等。

①创建文件②创建元器件③设置输入输出④添加连接线:将选定期间及设置好的输入输出按照设计好的原理图进行正确连线。

2)文本输入方式(Verilog HDL)学习verilog语言的扩展文件名位.v,verilog 文件名必须与实体文件名保持一致,文件必须放在一个工程中。

①创建verilog HDL源程序文件②用verilog HDL进行二选一数据选择器逻辑功能描述设计编译校验①建立仿真波形文件②添加仿真测试点③添加输入端仿真信号④开始仿真七、实验结果:A.四位减法器原理图:文本:波形图:B.完成)cabf=所对应逻辑电路设计及功能仿真。

bay=(c&|)!((),,原理图:波形图:八、心得体会:这是使用这个软件的第三次实验对于软件的使用已经比较熟练能够很快连接好电路进行试验九、附录:<程序代码>四位减法器module fourbit(A,B,CI,CO,S);parameter size=4;input [size:1]A,B;output [size:1]S;input CI;output CO;wire [1:size-1]Temp;onebitadd1(A[1],B[1],CI,S[1],Temp[1]),add2(A[2],B[2],Temp[1],S[2],Temp[2]),add3(A[3],B[3],Temp[2],S[3],Temp[3]),add4(A[4],B[4],Temp[3],S[4],CO);endmodulemodule onebit(A,B,CI,CO,S);input A,B,CI;output CO,S;wire n1,n2,n3,out1,out2,out3,out4,out5,out6,out7; notnoti1(n1,CI),noti2(n2,A),noti3(n3,B);andand1(out1,n1,n2),and2(out2,n2,n3),and3(out3,n1,n3),and4(out4,CI,A,B),and5(out5,n1,A,B),and6(out6,n1,n2,n3),and7(out7,CI,B,n3);nornor1(CO,out1,out2,out3),nor2(S,out4,out5,out6,out7);endmodule以下是附加文档,不需要的朋友下载后删除,谢谢顶岗实习总结专题13篇第一篇:顶岗实习总结为了进一步巩固理论知识,将理论与实践有机地结合起来,按照学校的计划要求,本人进行了为期个月的顶岗实习。

EDA技术与VHDL作业作业名称用quartusⅡ设计一个四位二进制全减器学生姓名邹运班级电技122学号2012301030230 任课教师吴君鹏完成时间2014.3.22用VHDL语言编写如下:library ieee;use ieee.std_logic_1164.all;entity quanjian isport(a,b,c:in std_logic;sout,jout:out std_logic);end;architecture one of quanjian issignal abc:std_logic_vector(2 downto 0);beginabc<=a&b&c;process(abc)begincase abc iswhen"000"=> sout<='0';jout<='0';when"001"=> sout<='1';jout<='1';when"010"=> sout<='1';jout<='1';when"011"=> sout<='0';jout<='1';when"100"=> sout<='1';jout<='0';when"101"=> sout<='0';jout<='0';when"110"=> sout<='0';jout<='0';when"111"=> sout<='1';jout<='1';when others=>null;end case;end process;end one;library ieee;use ieee.std_logic_1164.all;entity quanjian4 isport(a11,a12,a13,a14,b11,b12,b13,b14:in std_logic;s1,s2,s3,s4,j4:out std_logic);end;architecture two of quanjian4 issignal d,e,f:std_logic;component quanjianport(a,b,c:in std_logic;sout,jout:out std_logic);end component;beginu1:quanjian port map(a=>a14,b=>b14,c=>'0',jout=>d,sout=>s4); u2:quanjian port map(a=>a13,b=>b13,c=>d,jout=>e,sout=>s3); u3:quanjian port map(a=>a12,b=>b12,c=>e,jout=>f,sout=>s2); u4:quanjian port map(a=>a11,b=>b11,c=>f,jout=>j4,sout=>s1); end two;生成电路图如下:仿真波形如下:。

基于Quartus设计四位二进制减法器一、实验目的利用Quartus设计一个四位二进制减法器二、实验程序及程序分析library ieee;use ieee.std_logic_1164.all;IEEE库使用说明entity sub1 isport(a,b,c:in std_logic;output,carry:out std_logic);end sub1;实体说明,其中a,b,c为输入,output为当前位输出,carry为借位architecture beha of sub1 issignal abc:std_logic_vector(2 downto 0);beginabc<=a&b&c;process(abc)begincase abc iswhen"000"=> output<='0';carry<='0';when"001"=> output<='1';carry<='1';when"010"=> output<='1';carry<='1';when"011"=> output<='0';carry<='1';when"100"=> output<='1';carry<='0';when"101"=> output<='0';carry<='0';when"110"=> output<='0';carry<='0';when"111"=> output<='1';carry<='1';when others=>null;end case;end process;end beha;以上为构造体,将a&b&c赋值给abc,通过判断abc的8种情况实现当前位的输出及进位。

EDA技术与VHDL作业

作业名称用quartusⅡ设计一个四位二进制全减器

学生姓名邹运

班级电技122

学号2012301030230 任课教师吴君鹏

完成时间2014.3.22

用VHDL语言编写如下:

library ieee;

use ieee.std_logic_1164.all;

entity quanjian is

port(a,b,c:in std_logic;

sout,jout:out std_logic);

end;

architecture one of quanjian is

signal abc:std_logic_vector(2 downto 0);

begin

abc<=a&b&c;

process(abc)

begin

case abc is

when"000"=> sout<='0';jout<='0';

when"001"=> sout<='1';jout<='1';

when"010"=> sout<='1';jout<='1';

when"011"=> sout<='0';jout<='1';

when"100"=> sout<='1';jout<='0';

when"101"=> sout<='0';jout<='0';

when"110"=> sout<='0';jout<='0';

when"111"=> sout<='1';jout<='1';

when others=>null;

end case;

end process;

end one;

library ieee;

use ieee.std_logic_1164.all;

entity quanjian4 is

port(a11,a12,a13,a14,b11,b12,b13,b14:in std_logic;

s1,s2,s3,s4,j4:out std_logic);

end;

architecture two of quanjian4 is

signal d,e,f:std_logic;

component quanjian

port(a,b,c:in std_logic;

sout,jout:out std_logic);

end component;

begin

u1:quanjian port map(a=>a14,b=>b14,c=>'0',jout=>d,sout=>s4); u2:quanjian port map(a=>a13,b=>b13,c=>d,jout=>e,sout=>s3); u3:quanjian port map(a=>a12,b=>b12,c=>e,jout=>f,sout=>s2); u4:quanjian port map(a=>a11,b=>b11,c=>f,jout=>j4,sout=>s1); end two;

生成电路图如下:

仿真波形如下:。