EDAS上机操作

- 格式:ppt

- 大小:319.50 KB

- 文档页数:63

EDA技术实训室操作规程为了加强EDA技术实训室的管理,充分发挥实验设备的作用,确保机房安全、可靠地运行,更好地为教学、科研、技术开发服务,创造一个良好的实验环境,特制订本操作规程,本办法共分机房管理人员操作规程、指导教师操作规程和学生实验注意事项三部分,具体内容如下:一、机房管理人员操作规程1、应具有较强的计算机实际操作及维护能力,能及时处理所管理EDA技术实训室设备的软、硬件故障,保证设备的正常运行。

定期对设备进行检查维护,确保设备完好率达到90%以上。

2、负责EDA技术实训室的清洁卫生工作,保持实验室及周围环境整洁卫生。

3、做好EDA技术实训室安全防范工作及防火工作,下班前应关闭电源、门窗等,尤其是做好节假日期间的安全防范工作,避免事故的发生。

4、经常巡视学生实验现场,及时处理学生实验时出现的机器软、硬件故障。

督促学生遵守实验守则,对违反实验纪律的学生要耐心教育,严格管理。

在学生实验期间,工作人员不得随意擅自离开EDA技术实训室。

5、严格遵守各项规章制度,按时准确填写实验室进程表、实验室使用记录表。

如因管理不严造成严重后果的,除对当事人予以追究责任外,实验室管理人员也应承担相应的管理责任。

6、EDA技术实训室管理人员要努力学习新的知识,掌握新技能,要熟悉教学内容,尤其要了解各门课程的实验内容。

二、EDA技术实训室指导教师操作规程1、EDA技术需要上机操作,应有EDA技术实训室使用申请表,并经实验室所在部门领导批准后,方可到EDA技术实训室安排上机操作。

实验室使用申请表应在开学第一周内交到实验室,并由EDA技术实训室根据任务书和具体情况,统一安排上机操作时间和具体的EDA技术实训室。

2、实验指导教师应在实验课开始前5分钟提前到达,填写有关实验登记手续。

在实验指导过程中,不得擅自离开实验室,应负责维持好自己所指导实验班级学生的纪律。

对违反实验纪律的学生要耐心教育,严格管理。

3、实验指导教师对实验软件及硬件如有特殊要求(如EDA技术实训室从未安装使用过的新的软、硬件),应在教学任务下达后立即与实验室管理人员联系,并与实验室管理人员一起安装调试新的软、硬件,做好上机准备工作。

EDA上机实验报告学院:计算机科学与技术学院班级:计科09-4班姓名:学号:实验4-1 组合电路的设计一、实验目的:熟悉Quartus2的VHDL文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

二、实验任务:实验任务1:首先利用Quartus2完成2选1 多路选择器的文本编辑输入和仿真测试等步骤,给出仿真波形图。

最后在实验系统上进行硬件测试,并验证功能。

实验任务2:将此多路选择器看成一个元件,利用元件例化语句描述程序。

三、实验过程及结果:任务一、这个实验的程序比较简单,实验的结果如下:任务二、首先建立工程,然后建立vhdl文件,并进行编辑,在编辑好之后进行仿真测试如下所示:设置好输入输出之后,进行测试,测试效果如下;图形输出正确,然后生成RTL电路图,如下所示:四、实验代码:任务一、ENTITY MZ ISPORT (a,b,s:IN BIT;y:OUT BIT);END ENTITY MZ;ARCHITECTURE one OF MZ ISBEGINy<=a WHEN S='0' else b;END ARCHITECTURE one;任务二、LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL ;ENTITY MUX21A ISPORT (a1,a2,a3,s1,s0 :IN STD_LOGIC;outy :OUT STD_LOGIC);END ENTITY MUX21A ;ARCHITECTURE BHV OF MUX21A ISCOMPONENT MZPORT (a,b,s:IN STD_LOGIC;y:OUT STD_LOGIC);END COMPONENT ;SIGNAL tmp : STD_LOGIC;BEGINu1 : MZ PORT MAP (a=>a2, b=>a3, s=>s0, y=>tmp);u2 : MZ PORT MAP (a=>a1, b=>tmp,s =>s1, y=>outy);END ARCHITECTURE BHV ;五、程序分析:实验任务一和任务二都是多路选择器,实验任务一是一个二路选择器有2个输入,然后根据输入进行选择。

edas操作手册摘要:一、edas 简介1.edas 的定义2.edas 的作用二、edas 操作手册的使用1.手册的适用对象2.手册的结构和内容概述三、edas 操作步骤1.准备工作2.具体操作流程2.1 登录edas2.2 创建和管理资源2.3 监控资源2.4 配置和管理服务2.5 管理和监控服务2.6 创建和管理部署2.7 管理和监控部署2.8 备份和恢复数据2.9 设置安全策略2.10 管理权限和用户四、edas 的高级功能1.自动化部署2.负载均衡3.弹性伸缩4.容器编排五、edas 的常见问题和解决方案1.问题概述2.解决方案六、edas 的维护和升级1.维护策略2.升级流程正文:edas(Elastic Data Analysis System)是一款强大的大数据处理和分析平台,旨在为企业提供快速、高效、安全的大数据分析解决方案。

为了帮助用户更好地使用edas,我们编写了这本操作手册,详细介绍了edas 的使用方法和技巧。

一、edas 简介edas 是一个集数据采集、存储、计算、分析和可视化于一体的大数据平台。

通过edas,用户可以轻松地处理海量数据,并从中挖掘出有价值的信息,以支持企业决策。

二、edas 操作手册的使用本手册适用于具有一定大数据基础知识的用户,旨在帮助用户快速掌握edas 的使用方法。

手册分为六个部分,分别是edas 简介、操作手册的使用、edas 操作步骤、高级功能、常见问题和维护升级。

三、edas 操作步骤在使用edas 之前,用户需要进行一些准备工作,如安装和配置相关依赖项。

接下来,用户可以按照操作手册的指引,逐步完成edas 的创建、管理和监控等功能。

此外,本部分还介绍了如何备份和恢复数据、设置安全策略、管理权限和用户等操作。

四、edas 的高级功能edas 提供了许多高级功能,如自动化部署、负载均衡、弹性伸缩和容器编排等。

这些功能可以帮助用户更高效地管理和优化大数据处理环境。

eda上机proteus课程设计一、课程目标知识目标:1. 掌握EDA(电子设计自动化)的基本概念和原理;2. 学会使用Proteus软件进行电路设计与仿真;3. 理解并掌握常见电子元件的功能及其在电路中的应用;4. 了解电路图的绘制规则和电路分析方法。

技能目标:1. 能够运用Proteus软件绘制简单的电路图;2. 学会使用Proteus进行电路仿真,分析电路性能;3. 能够根据实际需求,设计简单的电子电路;4. 培养动手操作能力和团队协作能力。

情感态度价值观目标:1. 培养学生对电子设计的兴趣,激发创新意识;2. 增强学生的实践操作能力,提高自信心;3. 培养学生严谨、细致的学习态度,养成良好的学习习惯;4. 培养学生团队协作精神,提高沟通与表达能力。

课程性质:本课程为实践性较强的课程,以学生动手实践为主,结合理论知识,培养学生的实际操作能力和创新意识。

学生特点:学生处于年级阶段,具有一定的电子基础知识,对新鲜事物充满好奇心,动手能力强,但注意力容易分散,需要引导。

教学要求:结合课本内容,注重实践操作,让学生在动手实践中掌握EDA技术和Proteus软件的使用。

教师需关注学生学习进度,及时调整教学方法和节奏,确保学生能够达到预期学习成果。

二、教学内容1. 电子设计自动化(EDA)基本概念:介绍EDA的定义、发展历程和应用领域,使学生了解EDA技术的重要性。

- 教材章节:第一章 EDA技术概述2. Proteus软件入门:讲解Proteus软件的基本操作、界面布局及常用工具,使学生熟悉软件环境。

- 教材章节:第二章 Proteus软件使用入门3. 常见电子元件及其应用:学习电阻、电容、二极管、晶体管等常见电子元件的原理和功能,并在Proteus中进行仿真应用。

- 教材章节:第三章 常用电子元件及其应用4. 电路图绘制与仿真:学习电路图的绘制规则,运用Proteus软件进行电路设计与仿真,分析电路性能。

---------------------------------------------------------------最新资料推荐------------------------------------------------------EDA上机实验-6(新)实验六MAX+PLUSⅡ的设计处理定时分析一实验目的 1 掌握MAX+PLUSⅡ的基本使用。

2 掌握MAX+PLUSⅡ的设计处理过程中的三种定时分析模式。

二实验设备与仪器 1 计算机 2 MAX+PLUSⅡ工具软件三三实验内容 1 设计项目的建立与设计输入。

编辑 60 十进制同步计数器(见实验一)。

2 设计项目的编译和仿真(见实验四)。

4 MAX+PLUSⅡ的定时分析及器件编程-延时矩阵分析模式和建立/保持矩阵分析模式。

四实验原理MAX+PLUSⅡ定时分析器提供了三种分析模式,这三种分析模式分别是:(1)延时矩阵分析模式:分析多个源节点和目标节点之间的传输路径延时时间;(2)分析时序电路的性能,包括性能上有限定值的延时、最小时钟周期和最高工作频率等;(3)计算从输入引脚到触发器和锁存器的信号输入所需要的最小的建立时间和保持时间。

五实验步骤五实验步骤 1.打开编辑好的图形设计文件,进行编译和仿真。

2.定时分析选择默认的延时矩阵分析模式,打开定时分析器窗口运行定时分析器,可看到源节点和目标节点之间的传输路径延1 / 2时时间。

60 十进制同步计数器的延时矩阵分析结果如图 6-1 所示。

图 6-1 延时矩阵分析模式选择建立/保持矩阵分析模式,打开定时分析器窗口运行定时分析器,可看到 60 十进制同步计数器的建立/保持矩阵分析结果,如图 6-2 所示。

图 6-2 建立/保持矩阵分析结果选择分析时序电路的性能定时分析模式打开定时分析器窗口运行定时分析器,如图 6-3 所示。

可看到 60 十进制同步计数器的时钟周期为 15.3ns,最佳工作频率为 65.35MHz。

EDA实践安全操作规程

(一)启动计算机前,检查计算机电源、显示器和实验箱等外部设备是否连接妥当。

(二)计算机启动后,首先要仔细阅读注意事项,严格按规定步骤操作。

(三)使用计算机时,应熟悉操作系统、教学软件,做到操作准确。

(四)使用实验箱之前,应先检查实验箱电源是否连接,并熟悉实验箱各功能模块。

(五)在进行实验连线时,一定在实验箱无电的情况下进行,随时检查导线是否正确连接,是否存在短路现象,以免造成实验箱损坏。

(六)拔插导线时,应捏紧导线护套部,严禁拉拽导线线体。

(七)下载实验数据时,注意检查数据线是否正确连接,实验箱是否正确设置。

(八)在进行综合性设计时,注意按模块设计,严格区分顶层和底层模块,严禁模块间重名。

(九)实验结束后,先将实验箱断电,然后逐一拆除导线,在捆绑好后摆放到相应位置。

EDA上机实验报告02081407 高彬02081405潘吉祥一、实验目的:了解qunters2的使用方法及操作方法。

二、设计任务:设计出秒表计时器。

三、程序代码libraryieee;use ieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entityclk isport(clk : in std_logic ;reset : in std_logic ;en : in std_logic ;jw : out std_logic ;q1,q2,q3,q4,q5,q6 : out std_logic_vector ( 3 downto 0 ) );end entity clk;architecturealg_clk of clk issignal couL,couH,couL1,couH1,couL2,couH2 : std_logic_vector ( 3 downto 0 ); signal jw1,jw2 : std_logic;beginprocess (clk,reset)beginif reset='0' thencouL<="0000";couH<="0000";elsifclk'event and clk='1' thenif en = '1' thenif ( couL=9 and couH=9 ) thencouL<="0000";couH<="0000";elsifcouL=9 thencouL<="0000";couH<=couH+1;elsecouL<=couL+1;end if;end if;end if;end process;process (couL,couH)beginif ( couL=9 and couH=9 ) thenjw1<='1';else jw1<='0';end if;end process;process (clk,reset)beginif reset='0' thencouL1<="0000";couH1<="0000";elsifclk'event and clk='1' thenif en = '1' thenif jw1='0' thencouL1<=couL1;couH1<=couH1; elsif couL1=9 thencouL1<="0000";couH1<=couH1+1; elsecouL1<=couL1+jw1; end if;end if;end if;end process;process (couL1,couH1)beginif ( couL1=9 and couH1=5 ) thenjw2<='1';else jw2<='0';end if;end process;process (clk,reset)beginif reset='0' thencouL2<="0000";couH2<="0000";elsifclk'event and clk='1' thenif en = '1' thenif jw2='0' thencouL2<=couL2;couH2<=couH2; elsif couL2=9 thencouL2<="0000";couH2<=couH2+1; elsecouL2<=couL2+jw2; end if;end if;end if;end process;process (couL2,couH2)beginif ( couL2=9 and couH2=5 ) thenjw<='1';elsejw<='0';end if;end process;q1<=couL;q2<=couH;q3<=couL1;q4<=couH1;q5<=couL2;q6<=couH2;end architecture alg_clk;四、仿真图形五、实验说明:q1代表毫秒的低位q2代表毫秒的高位,当低位是9高位也是9时进位,q3代表秒的低位q4代表秒的高位当他们是59时进位q5q6分别代表分的低高位当他们是59时进位en是使能端jw代表进位。

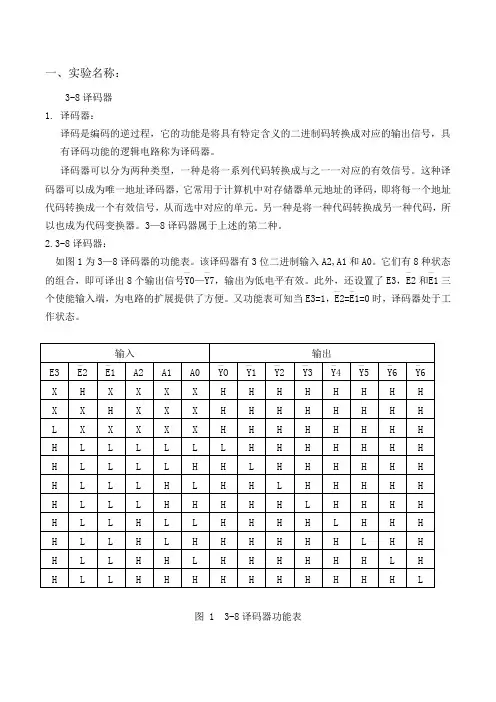

一、实验名称:3-8译码器1.译码器:译码是编码的逆过程,它的功能是将具有特定含义的二进制码转换成对应的输出信号,具有译码功能的逻辑电路称为译码器。

译码器可以分为两种类型,一种是将一系列代码转换成与之一一对应的有效信号。

这种译码器可以成为唯一地址译码器,它常用于计算机中对存储器单元地址的译码,即将每一个地址代码转换成一个有效信号,从而选中对应的单元。

另一种是将一种代码转换成另一种代码,所以也成为代码变换器。

3—8译码器属于上述的第二种。

2.3-8译码器:如图1为3—8译码器的功能表。

该译码器有3位二进制输入A2,A1和A0。

它们有8种状态的组合,即可译出8个输出信号Y—0—Y—7,输出为低电平有效。

此外,还设置了E3,E—2和E—1三个使能输入端,为电路的扩展提供了方便。

又功能表可知当E3=1,E—2=E—1=0时,译码器处于工作状态。

图 1 3-8译码器功能表二、实验工具:ModelSim软件简介:ModelSim是业界最优秀的HDL语言仿真器,它提供最友好的调试环境,是唯一的单内核支持VHDL和Verilog混合仿真的仿真器。

是作FPGA/ASIC设计的RTL级和门级电路仿真的首选,它采用直接优化的编译技术、Tcl/Tk技术、和单一内核仿真技术,编译仿真速度快,编译的代码与平台无关,便于保护IP核,个性化的图形界面和用户接口,为用户加快调错提供强有力的手段。

全面支持VHDL和Verilog语言的IEEE 标准,支持C/C++功能调用和调试。

ModelSim专业版,具有快速的仿真性能和最先进的调试能力,全面支持UNIX(包括64位)、Linux和Windows平台。

主要特点:RTL和门级优化,本地编译结构,编译仿真速度快;单内核VHDL和Verilog 混合仿真;源代码模版和助手,项目管理;集成了性能分析、波形比较、代码覆盖等功能;数据流ChaseX;Signal Spy;C和Tcl/Tk接口,C调试。

EDA技术实验指导书山东建筑大学信息与电气工程学院前言一、实验目的本实验课程的目的,旨在通过上机实验,使学生加深理解EDA技术的基本方法,帮助和培养学生建立利用原理图和硬件描述语言进行电路设计的基本方法和利用EDA工具软件(QuartusⅡ)设计简单数字电子系统的能力,为以后从事有关数字电子系统方面的设计和研究开发工作打下基础。

二、实验前预习每次实验前,学生须仔细阅读本实验指导书的相关内容,明确实验目的和实验内容;明确实验原理与步骤;复习与实验内容有关的理论知识;预习仪器设备的使用方法、操作规程及注意事项。

三、实验注意事项1.实验开始前,应先检查本人的计算机是否安装相关软件,了解其软件的使用方法和要求。

2.实验时每个同学应单独设计程序、操作、记录实验结果等,使每个同学受到全面训练。

3.测量数据或观察现象要认真细致,实事求是。

使用计算机要符合操作规程,切勿随便重启频繁开关计算机。

4.未经许可,不得动用其它人的仪器设备或计算机等物。

5.实验结束后,实验记录交指导教师查看并认为无误后,离开机房。

最后,应清理计算机,备份编写程序。

6.爱护公物,发生仪器设备等损坏事故时,应及时报告指导教师,按有关实验管理规定处理。

7.自觉遵守学校和实验室管理的其它有关规定。

四、实验总结每次实验后,应对实验进行总结,即实验数据进行整理,绘制波形和图表,分析实验现象,撰写实验报告。

实验报告除写明学院、班级、姓名、学号、课程、实验日期、实验名称外,还应包括:1.实验目的。

2.实验仪器与设备。

3.实验内容。

4.实验原理与步骤。

5.实验结果与分析。

目录实验一半加器设计 (1)实验二全加器设计 (5)实验三译码器设计 (8)实验四数据选择器设计 (11)实验五触发器设计 (14)实验六计数器设计 (16)实验七计数译码系统电路设计 (19)实验八BCD数加法系统电路设计 (24)实验一半加器设计一、实验目的1、学习QuartusⅡ工具软件的基本功能和使用方法2、学习使用原理图输入法设计半加器,掌握原理图输入法的操作步骤3、初步掌握设计电路原理图的编辑、编译、仿真等操作方法二、实验仪器与设备1、PC机2、Quartus II 软件三、实验内容以Altera公司的Quartus II为工具软件,采用原理图输入法设计半加器h_adder,生成元件符号,并仿真验证设计结果。

edas操作手册【实用版】目录1.Edas 简介2.Edas 的功能3.Edas 的使用方法4.Edas 的优点和局限性5.总结正文1.Edas 简介Edas(Elastic Data Access Service)是一款面向企业级应用的数据访问服务,主要用于解决大数据存储和访问的问题。

Edas 具有高度可扩展性,可以满足大规模数据的存储和快速访问需求,同时提供了丰富的数据分析功能,帮助企业轻松应对数据挑战。

2.Edas 的功能Edas 主要包括以下功能:(1)数据存储:Edas 支持多种数据存储方式,包括 HDFS、HBase、Ceph 等,可根据业务需求选择合适的存储方式。

(2)数据访问:Edas 提供了 RESTful API 和 SDK,方便开发者进行数据访问和操作。

同时,Edas 支持多种数据分析工具,如 SQL、MapReduce、Spark 等,满足不同业务场景的数据处理需求。

(3)数据管理:Edas 提供了统一的数据管理平台,可以实现对数据的生命周期管理、权限控制、数据备份和恢复等功能。

(4)监控和告警:Edas 提供了实时的监控和告警功能,可以帮助企业及时发现和处理数据存储和访问中的问题。

3.Edas 的使用方法(1)安装和配置:首先需要下载并安装 Edas,然后根据业务需求进行相关配置,如数据存储、访问权限等。

(2)创建数据表:在 Edas 中创建数据表,用于存储和管理数据。

(3)编写数据访问代码:使用 Edas 提供的 API 或 SDK 编写数据访问代码,实现数据的增、删、改、查等操作。

(4)调试和优化:在实际使用过程中,需要不断调试和优化数据访问代码,以提高数据处理效率。

4.Edas 的优点和局限性(1)优点:a.高度可扩展:Edas 可以很好地支持大规模数据的存储和访问,满足企业不断增长的数据需求。

b.易用性强:Edas 提供了丰富的 API 和 SDK,降低了开发者使用数据访问服务的难度。

edas操作手册EDAS(Elastic Distributed Application Service)是一种云原生分布式应用程序开发和运行管理平台,提供了一套完整的开发、测试、部署和运行管理服务。

EDAS可以帮助开发者快速构建、测试和部署分布式应用程序,并提供一系列的服务和工具来监控和管理应用程序的运行。

下面是EDAS操作手册的一些基本步骤和常用操作:1. 注册EDAS账号:首先需要注册一个EDAS账号,并完成账号的认证。

2. 创建应用:在EDAS控制台上创建一个新的应用。

需要填写应用的名称、描述和所属的命名空间等信息。

3. 编写应用程序:按照EDAS的要求编写分布式应用程序。

可以使用Java、Python、Node.js等编程语言。

4. 部署应用:将应用程序部署到EDAS平台上。

可以通过上传项目代码、部署脚本或使用Docker等方式进行部署。

5. 配置应用:配置应用所需要的资源和依赖项。

可以设置应用的CPU和内存限制,配置数据库、消息队列等资源的连接信息。

6. 监控应用:使用EDAS的监控服务来监控应用的运行情况。

可以查看应用的实时状态、性能指标和日志信息等。

7. 扩展应用:根据应用的需求,可以通过EDAS提供的扩展功能来扩展应用的规模和容量。

可以增加实例数量、调整资源分配等。

8. 管理应用:使用EDAS的管理功能来管理应用的配置、版本和运行状态。

可以进行应用的升级、回滚和维护等操作。

9. 高可用和安全:使用EDAS的高可用和安全功能来保障应用的可靠性和安全性。

可以设置应用的备份策略、访问权限和数据加密等。

以上是EDAS的基本操作手册,更详细的信息可以参考EDAS 官方文档或联系EDAS技术支持团队。

edas操作手册引言随着云计算的快速发展,企业对于高效、可靠的应用部署和运维管理的需求也越来越迫切。

针对这一需求,阿里云推出了EDAS(Enterprise Distributed Application Service)平台,为企业提供了一站式的云上应用托管和管理解决方案。

本文将详细介绍EDAS的操作指南,帮助用户了解如何使用EDAS平台。

1. 登录与注册要使用EDAS平台,首先需要在阿里云官网注册一个账号。

注册完成后,在阿里云官网登录账号,进入管理控制台。

然后,在控制台页面中找到EDAS入口,点击进入EDAS平台。

2. 创建应用在EDAS平台中,创建应用是第一步。

点击入口后,进入应用管理页面,可以看到“创建应用”按钮。

点击该按钮,填写应用的基本信息,例如应用名称、部署区域等,然后点击“确认”按钮即可成功创建应用。

接着,我们可以开始配置应用的运行环境。

3. 配置运行环境配置运行环境是EDAS平台中的重要步骤,它决定了应用的部署方式和资源配置。

在应用管理页面中找到刚刚创建的应用,进入应用详情页,选择“环境配置”标签。

用户可以根据自己的需求选择虚拟机、容器等不同的部署模式,并根据实际情况调整资源配置。

4. 部署应用配置完运行环境后,我们就可以开始部署应用了。

在应用详情页中,选择“部署”标签,可以看到“选择应用包”按钮。

点击该按钮,选择本地的应用包进行上传。

上传完成后,选择要运行的版本,并设置启动参数,然后点击“确认”按钮即可完成应用部署。

5. 监控与管理EDAS平台提供了强大的监控与管理功能,方便用户对应用进行实时监控和故障处理。

在应用详情页中,选择“监控”标签,可以看到各种监控指标,例如应用的访问量、响应时间等。

用户可以根据具体的需求自定义监控指标,并设置报警规则,确保应用的稳定性。

此外,EDAS平台还提供了日志管理、配置中心等功能,方便用户进行日常运维管理。

在应用详情页中,点击“日志管理”标签,可以查看应用的日志情况,并根据需要进行搜索和分析。

EDA上机指导书电气与信息工程学院2011年6月上机一MAX+PLUSII使用(简单逻辑电路设计与仿真)一.上机目的1.学习并掌握MAX+PLUSII CPLD开发系统的基本操作。

2.掌握简单逻辑电路的设计方法与功能仿真技巧。

二.上机仪器设备1.PC机,1台2.MAX+PLUSII CPLD软件开发系统,1套三.上机预习要求1.预习教材中的相关内容;2.预习老师教学演示的相关内容;3.阅读并熟悉本次上机内容。

四.上机内容用原理图设计一个1位二进制的全加器(由两个1位二进制半加器构成)并进行电路功能仿真与验证。

五.上机操作步骤(1)开机,进入MAX+PLUSII开发系统;(2)在D盘建立自己的目录(注意要以英文命名);(3)在主菜单中选NEW,从输入文件类型选择菜单中选图形编辑文件输入方式,见图1-1。

图1-1 输入文件类型选择菜单4)在空白屏幕上双击,从元件库中确定并选择基本元件。

注意:从prim子目录中选择输入引脚input和输出引脚output和相应的门电路。

见图1-2。

图1-2 符号元件库选择目录(5)在图形编辑窗口完成电路的连线及对引脚的命名。

图1-3 1位半加器的电路(6)打开FILE主菜单,选择SAVE AS,将画好的线路图以自己设定的某个名称保存在自己的目录下(文件的扩展名必是.gdf )。

(7)并将该设计文件指定成项目文件(选择菜单“FILE”→ project→ set project to current file).(8)对所设计的电路进行编译。

(选择菜单“FILE”→ project→ save&compile).编译成功会弹出如下信息。

(9)软件仿真。

在图1-1新建仿真波形文件,后缀名.SCF。

出现图1-4的仿真波形编辑界面。

图1-4仿真波形编辑界面(10)双击Name下方的空白处,在弹出的对话框中点击“List”按钮,添加输入、输出节点。

选择输入节点A,点OK,再选择输入节点B,点OK。

第4章常用EDA工具软件操作指南本章提要:本章阐述了Altera MAX+plusⅡ,Xilinx ISE Series、Lattice ispDesignEXPERT 等常用的主流EDA工具软件的基本使用方法,包括软件的安装,原理图、VHDL等输入方式的设计操作的步骤与方法。

学习要求:在对三个软件作简单介绍的基础上,概括地讲述三个主流厂家LATTICE、ALTERA、XILINX公司的设计开发软件中的一个的使用,并要求学生通过实验和上机熟悉地掌握其中一个软件的使用。

对其余的两个软件至少有个基本的了解。

关键词:MAX+plusⅡ,ISE Series、ispDesignEXPERT4.1 Altera MAX+plusⅡ操作指南4.1.1 MAX+plusⅡ10.2的安装4.1.2 MAX+plusⅡ开发系统设计入门4.2 Xilinx ISE Series的使用4.2.1 ISE的安装4.2.2 ISE工程设计流程4.2.3 VHDL设计操作指南4.2.4 ISE综合使用实例4.3 Lattice ispDesignEXPERT的使用4.3.1 ispDesignEXPERT的安装4.3.2 原理图输入方式设计操作4.3.3 VHDL输入方式设计操作4.1 Altera MAX+plusⅡ操作指南Alter公司的MAX+plusⅡ是一个高度集成化的可编程逻辑器件开发系统,可以开发Alter公司的MAX系列和FLEX系列的可编程器件。

该系统的主要特点如下:①支持多种设计输入方式。

如:原理图、VHDL语言、AHDL语言、波形图等。

同时还支持主流的第三方EDA工具,如:Synopsys、Cadence、ViewLogic、Synplicity、Mentor和Model Technology等等。

②提供完善的功能仿真,同时还提供精确的时间仿真。

③该系统把设计输入、功能仿真、时间仿真、设计编译以及器件编程集成于统一的开发环境下,从而更方便、更快捷。