Verilog程序6、UART(串口通信)

- 格式:doc

- 大小:132.00 KB

- 文档页数:10

uart通信原理与程序UART(通用异步收发传输器)是一种串行通信协议,用于在电子设备之间传输数据。

它广泛应用于各种通信设备和嵌入式系统中,是实现设备间通信的一种基本方式。

本文将详细介绍UART的工作原理和编写UART通信程序的步骤。

一、UART的工作原理UART通信是一种简单的、异步的、串行通信方式。

它使用一个数据线(TXD)和一个时钟线(CLK)实现数据的收发。

UART通信的工作原理如下:1.数据传输格式:UART通信使用帧来表示一个完整的数据包,每个帧由起始位、数据位、校验位和停止位组成。

起始位是一个低电平信号,用来告诉接收方接下来的数据的开始。

数据位是实际要传输的数据,可以是一个字节或多个字节。

校验位用于检查数据的准确性,常用的校验方式有奇偶校验和循环冗余校验(CRC)。

停止位是一个高电平信号,用来表示数据的结束。

2.波特率:3.串行传输:UART通信使用串行传输方式,即每个bit按顺序依次传输。

发送方将数据一位一位地发送到TXD线上,接收方通过CLK线来同步数据的传输。

发送方和接收方都在预定的时钟频率下将数据从一个电平变为另一个电平,以便接收方正确地接收数据。

4.启动和停止:UART通信在数据的开始和结束位置需要一些额外的控制位来标识。

当数据传输开始时,发送方发送一个起始位(低电平),接收方通过检测起始位来确定数据传输的开始。

当数据传输完毕时,发送方发送一个或多个停止位(高电平)来表示数据的结束。

5.同步与异步:UART通信是一种异步通信方式,即发送方和接收方的时钟不同步。

发送方和接收方使用各自的时钟来同步数据的传输,接收方通过检测起始位和停止位来确定数据的开始和结束位置。

二、编写UART通信程序的步骤下面是编写UART通信程序的一般步骤:1.设置波特率:首先,需要设置UART的波特率,确保发送方和接收方使用相同的波特率。

波特率的设置通常是通过设置寄存器完成的,具体的方法可以参考芯片的数据手册。

UART串口通信协议1. 引言串行通信是在计算机和外设之间传输数据的一种常见方式,而UART(通用异步收发传输器)是其中一种广泛使用的串口通信协议。

UART串口通信协议在各种领域中被广泛应用,例如嵌入式系统、通信设备等。

本文将介绍UART串口通信协议的基本原理、数据格式和常见应用场景。

2. 基本原理UART串口通信协议采用异步通信方式,通过单个数据线进行数据传输。

通信的两个设备之间共享一个时钟信号,其中一个设备充当发送器(Transmitter),另一个设备充当接收器(Receiver)。

发送器将数据按照一定规则发送到数据线上,接收器则根据相同的规则从数据线上接收数据。

UART串口通信协议的基本原理可以概括为以下几个步骤:1.确定波特率(Baud Rate):波特率是指单位时间内传输的位数,常见的波特率有9600、115200等。

发送器和接收器必须使用相同的波特率才能正常通信。

2.确定数据位数(Data Bits):数据位数指的是每个数据包中实际传输的位数,通常为5、6、7或8位。

3.确定奇偶校验位(Parity Bit):奇偶校验位用于检测数据传输过程中是否发生错误。

奇偶校验可以分为奇校验和偶校验两种方式,发送器和接收器必须使用相同的奇偶校验方式。

4.确定停止位(Stop Bits):停止位用于标识每个数据包的结束,通常为1或2位。

3. 数据格式UART串口通信协议中的数据包由起始位、数据位、奇偶校验位和停止位组成。

其中,起始位和停止位的逻辑电平分别为高和低,用于标识每个数据包的开始和结束。

数据位包含了实际要传输的数据,奇偶校验位用于检测数据的正确性。

下面是UART串口通信协议中常用的数据格式示例:起始位数据位奇偶校验位停止位0 8位 None 1位在以上示例中,数据位为8位,没有奇偶校验位,停止位为1位。

这种数据格式在许多UART串口通信应用中被广泛使用。

4. 应用场景UART串口通信协议在许多领域中得到了广泛应用,以下是一些常见的应用场景:4.1 嵌入式系统在嵌入式系统中,UART串口通信协议用于与外部设备进行通信。

1 UART原理串行通信是指外部设备和计算机间使用一根数据线(另外需要地线,可能还需要控制线)进行数据传输的方式。

数据在一根数据线上一位一位传输,每一位数据都占据一个固定的时间长度。

与并行通信方式相比,串行通信方式的传输速度较慢,但这种通信方式使用的数据线少,在远距离通信中可以节约通信成本,因此得到了广泛的应用。

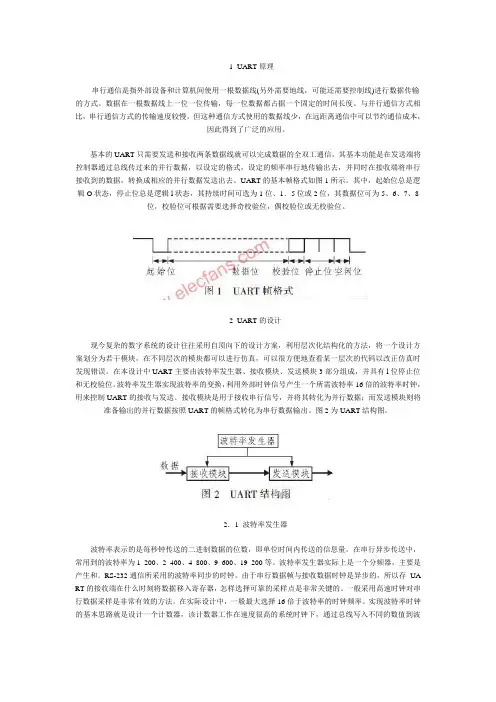

基本的UART只需要发送和接收两条数据线就可以完成数据的全双工通信,其基本功能是在发送端将控制器通过总线传过来的并行数据,以设定的格式,设定的频率串行地传输出去,并同时在接收端将串行接收到的数据,转换成相应的并行数据发送出去。

UART的基本帧格式如图1所示。

其中,起始位总是逻辑O状态,停止位总是逻辑l状态,其持续时间可选为1位、1.5位或2位,其数据位可为5、6、7、8位,校验位可根据需要选择奇校验位,偶校验位或无校验位。

2 UART的设计现今复杂的数字系统的设计往往采用自顶向下的设计方案,利用层次化结构化的方法,将一个设计方案划分为若干模块,在不同层次的模块都可以进行仿真,可以很方便地查看某一层次的代码以改正仿真时发现错误。

在本设计中UART主要由波特率发生器、接收模块、发送模块3部分组成,并具有l位停止位和无校验位。

波特率发生器实现波特率的变换,利用外部时钟信号产生一个所需波特率16倍的波特率时钟,用来控制UART的接收与发送。

接收模块是用于接收串行信号,并将其转化为并行数据;而发送模块则将准备输出的并行数据按照UART的帧格式转化为串行数据输出。

图2为UART结构图。

2.1 波特率发生器波特率表示的是每秒钟传送的二进制数据的位数,即单位时间内传送的信息量。

在串行异步传送中,常用到的波特率为1 200、2 400、4 800、9 600、19 200等。

波特率发生器实际上是一个分频器,主要是产生和。

RS-232通信所采用的波特率同步的时钟。

由于串行数据帧与接收数据时钟是异步的,所以存UA RT的接收端在什么时刻将数据移入寄存器,怎样选择可靠的采样点是非常关键的。

串口通信UART模块基本介绍串口通信(UART)是一种通过串行接口进行数据传输的通信协议和硬件实现方式。

它是计算机和外设之间最常用的通信方式之一,也是嵌入式系统和单片机等小型设备中常用的通信方式。

UART通过串行方式传输数据,即通过单一的数据线一次只能传输一个bit位。

在串口通信中,通常需要两条线,一条用于发送数据(TX),一条用于接收数据(RX)。

UART通常通过一对相互连接的芯片实现,称为UART芯片或UART模块。

它包含一个发送器和一个接收器。

发送器将要发送的数据从并行格式转换为串行格式,并通过发送线路发送出去。

接收器则接收到的串行数据转换为并行格式以供系统使用。

UART芯片通常由硬件设计工程师在集成电路中设计和实现。

UART通信具有以下特点和优势:1.简单易用:UART通信是一种非常简单和易用的通信协议。

它的实现简单,适用于各种不同的应用场景。

2.可靠性高:UART通信使用的是硬件实现,不受软件的控制和干扰。

它具有较高的可靠性和稳定性。

3. 速度灵活可调:UART通信可以根据不同的应用需求进行速度调整。

通常,UART通信支持的波特率范围很大,可以从几十bps到多Mbps。

4.支持半双工和全双工通信:UART通信可以支持半双工和全双工两种通信方式。

在半双工模式下,发送和接收不能同时进行;而在全双工模式下,可以同时进行发送和接收。

5.通信距离远:UART通信使用串行线路进行数据传输,因此可以通过扩展串行线路的长度来实现较远距离的通信。

6.多种应用:UART通信广泛应用于各种设备和领域,如计算机、嵌入式系统、单片机、电子设备、通信设备等。

值得注意的是,UART通信只是一个物理层的通信协议,它只负责数据的传输,而不负责数据的解码和处理。

因此,在使用UART通信时,通常需要配合其他协议或编码方式,如RS-232、RS-485、Modbus等,来完成完整的通信过程。

总结来说,UART通信是一种简单、可靠、灵活的串行通信协议和硬件实现方式。

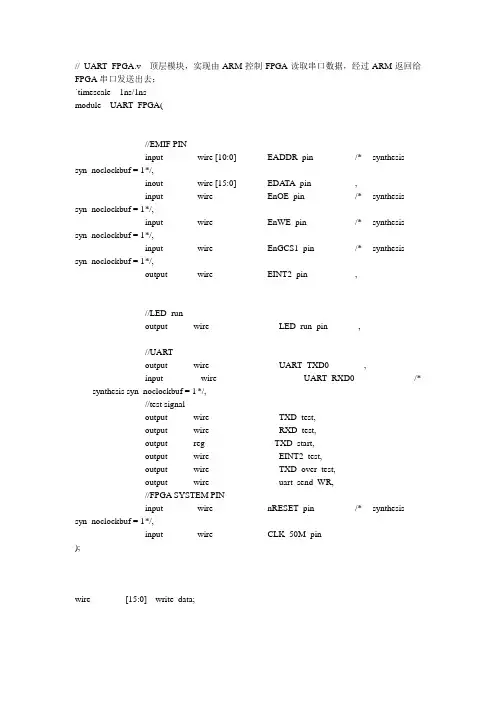

// UART_FPGA.v 顶层模块,实现由ARM控制FPGA读取串口数据,经过ARM返回给FPGA串口发送出去;`timescale 1ns/1nsmodule UART_FPGA(//EMIF PINinput wire [10:0] EADDR_pin /* synthesis syn_noclockbuf = 1 */,inout wire [15:0] EDATA_pin ,input wire EnOE_pin /* synthesis syn_noclockbuf = 1 */,input wire EnWE_pin /* synthesis syn_noclockbuf = 1 */,input wire EnGCS1_pin /* synthesis syn_noclockbuf = 1 */,output wire EINT2_pin ,//LED_runoutput wire LED_run_pin ,//UARToutput wire UART_TXD0 ,input wire UART_RXD0 /* synthesis syn_noclockbuf = 1 */,//test signaloutput wire TXD_test,output wire RXD_test,output reg TXD_start,output wire EINT2_test,output wire TXD_over_test,output wire uart_send_WR,//FPGA SYSTEM PINinput wire nRESET_pin /* synthesis syn_noclockbuf = 1 */,input wire CLK_50M_pin);wire [15:0] write_data;//-------------------DSP ARM uart to EMIF---------------------- reg [7:0] ARM_DSP_data;wire [7:0] DSP_ARM_data;reg uart_send_WR_reg;//reg [7:0] T_data;//reg [1:0] TXD_start_cnt;wire [7:0] R_data;wire R_ready;reg [2:0] UART_INT_cnt;wire TXD_over;wire [1:0] baud_select;reg [12:0] baud_devide;//wire clkrec;parameter baud_9600 = 5208; //50M/9600 parameter baud_19200 = 2604;parameter baud_38400 = 1302;parameter baud_115200 = 434;assign TXD_test = UART_TXD0;assign RXD_test = UART_RXD0;assign EINT2_test = EINT2_pin;assign TXD_over_test=TXD_over;/*--------------Program start-------------------*//*----------baud select------------*/always @( negedge nRESET_pin or posedge CLK_50M_pin ) beginif( !nRESET_pin )beginbaud_devide <= 'h1FFF;endelsebegincase ( baud_select )'d0 : baud_devide <= baud_9600 ;'d1 : baud_devide <= baud_19200 ;'d2 : baud_devide <= baud_38400 ;'d3 : baud_devide <= baud_115200 ;endcaseendend/*----------INT generator------------*/always @( negedge nRESET_pin or posedge R_ready )beginif( !nRESET_pin )beginARM_DSP_data <= 8'd0;endelsebeginARM_DSP_data <= R_data;endendalways @( negedge nRESET_pin or negedge R_ready or posedge CLK_50M_pin ) beginif( !nRESET_pin )beginUART_INT_cnt <= 3'd5;endelse if( !R_ready )beginUART_INT_cnt <= 3'd0;endelse if( UART_INT_cnt < 3'd5 )beginUART_INT_cnt <= UART_INT_cnt + 1'b1;endassign EINT2_pin = ( UART_INT_cnt >= 3'd1 && UART_INT_cnt <= 3'd4 ) ? 1'b0 : 1'b1 ;/*---------------DSP to ARM data---------------*/always@(negedge nRESET_pin or posedge CLK_50M_pin) //当接收了一个数据后,把数据加1后发回PC机,注意串口一个一个数据发beginif( !nRESET_pin )beginuart_send_WR_reg <= 1'b0;TXD_start <= 1'b0;endelse if( uart_send_WR_reg != uart_send_WR )beginif( TXD_over )beginTXD_start <= 1'b1;uart_send_WR_reg <= uart_send_WR;endendelsebeginTXD_start <= 1'b0;endend//----------------EMIF read ,fpga TO ARM---------------------------EMIF_R EMIF_R_M(.EADDR_pin (EADDR_pin ),.EDA TA_pin (EDA TA_pin ),.EnOE_pin (EnOE_pin ),.EnGCS1_pin (EnGCS1_pin ),.write_data (write_data ),.ARM_DSP_data (ARM_DSP_data ),.nRESET_pin (nRESET_pin )// .CLK_50M_pin (CLK_50M_pin )//----------------EMIF write,ARM to fpga---------------------------EMIF_W EMIF_W_M(.EADDR_pin (EADDR_pin ),.EDA TA_pin (EDATA_pin ),.EnWE_pin (EnWE_pin ),.EnGCS1_pin (EnGCS1_pin ),//uart.DSP_ARM_data (DSP_ARM_data ),.uart_send_WR (uart_send_WR ),.write_data (write_data ),.baud_select (baud_select ),//LED run.LED_run_pin (LED_run_pin ),.nRESET_pin (nRESET_pin )// .CLK_50M_pin (CLK_50M_pin ) );UART_rec UART_rec_M (//input.RXD (UART_RXD0 ),.baud_devide (baud_devide ),//output.R_data (R_data ),.R_ready (R_ready ),//FPGA sys pin.nRESET_pin (nRESET_pin ),.CLK_50M_pin (CLK_50M_pin));UART_txd UART_txd_M (//input.TXD_start (TXD_start ),.T_data (DSP_ARM_data ),.baud_devide (baud_devide ),//output.TXD (UART_TXD0 ),.TXD_over (TXD_over ),//FPGA sys pin.nRESET_pin (nRESET_pin ),.CLK_50M_pin (CLK_50M_pin));Endmodule// UART_rec.v`timescale 1ns/1nsmodule UART_rec (//inputRXD,baud_devide,//outputR_data,R_ready,//FPGA sys pinnRESET_pin,CLK_50M_pin);input wire RXD;input wire [12:0] baud_devide;output reg [7:0] R_data;output reg R_ready;input wire nRESET_pin;input wire CLK_50M_pin;reg [1:0] RXD_sync;reg [2:0] RXD_cnt;reg RXD_bit;reg [3:0] rec_bit_cnt;//reg [8:0] baud_16_reg;reg [12:0] baud_cnt;reg [8:0] baud_16_cnt;wire baud_tick_16;wire baud_tick;wire [11:0] baud_devide_2;wire [8:0] baud_devide_16;/*----------Program start------------*/assign baud_devide_2 = baud_devide / 2;assign baud_devide_16 = baud_devide / 16;/*--------------baud 16 devided clk used in sample-----------*/ always @( negedge nRESET_pin or posedge CLK_50M_pin ) beginif( !nRESET_pin )beginbaud_16_cnt <= 'd0;endelsebeginif( baud_16_cnt < baud_devide_16 )beginbaud_16_cnt <= baud_16_cnt + 1'b1;endelsebeginbaud_16_cnt <= 'd0;endendendassign baud_tick_16 = ( baud_16_cnt == baud_devide_16 );//--------baud clk used in receiving data-------always @( negedge nRESET_pin or posedge CLK_50M_pin )beginif( !nRESET_pin )beginbaud_cnt <= 'd0;endelsebeginif( !R_ready )beginif( baud_cnt < baud_devide - 1'b1 )beginbaud_cnt <= baud_cnt + 1'b1;endelsebeginbaud_cnt <= 'd0;endendelsebeginbaud_cnt <= 'd0;endendendassign baud_tick = ( baud_cnt == baud_devide_2 );/*-----------jitter filter--------------*/always @( negedge nRESET_pin or posedge CLK_50M_pin )beginif( !nRESET_pin )beginRXD_sync <= 2'd0;endelsebeginRXD_sync <= {RXD_sync[0], RXD};endendalways @( negedge nRESET_pin or posedge baud_tick_16 ) beginif( !nRESET_pin )beginRXD_cnt <= 3'd7;endelsebeginif( RXD_sync[1] && RXD_cnt != 3'd7 )beginRXD_cnt <= RXD_cnt + 1;endelsebeginif( ~RXD_sync[1] && RXD_cnt != 3'd0 )beginRXD_cnt <= RXD_cnt - 1;endendendendalways @( negedge nRESET_pin or posedge baud_tick_16 ) beginif( !nRESET_pin )beginRXD_bit <= 1'b1;endelsebeginif( RXD_cnt == 3'd7)beginRXD_bit <= 1'b1;endelse if( RXD_cnt == 3'd0 )beginRXD_bit <= 1'b0;endendend/*---------------receive data cnt---------------*/always @( negedge nRESET_pin or posedge CLK_50M_pin ) beginif( !nRESET_pin )beginR_ready <= 1'b1;rec_bit_cnt <= 4'd0;endelsebeginif( R_ready )beginrec_bit_cnt <= 4'd0;if( !RXD_bit )beginR_ready <= 1'b0;endendelse if( baud_tick )beginif( rec_bit_cnt < 4'd9 )beginrec_bit_cnt <= rec_bit_cnt + 1'b1;R_ready <= 1'b0;endelsebeginrec_bit_cnt <= 4'd0;R_ready <= 1'b1;endendendendalways @( negedge nRESET_pin or posedge baud_tick ) beginif( !nRESET_pin )beginR_data <= 8'd0;endelse if( !R_ready )beginif( rec_bit_cnt == 0 )beginR_data <= 8'd0;endelsebeginif( rec_bit_cnt >= 4'd1 && rec_bit_cnt<= 4'd8 )R_data[rec_bit_cnt - 1'b1 ] <= RXD_bit;endendendendmodule// UART_TXD.v`timescale 1ns/1nsmodule UART_txd (//inputbaud_devide,TXD_start,T_data,//outputTXD,TXD_over,//FPGA sys pinnRESET_pin,CLK_50M_pin);input wire TXD_start;input wire [7:0] T_data;input wire [12:0] baud_devide;output reg TXD;output reg TXD_over;input wire nRESET_pin;input wire CLK_50M_pin;//regs & wireswire baud_tick;//reg baud_ctrl;reg [3:0] T_state;reg [7:0] T_data_reg;reg [12:0] baud_cnt;/*----------Program start---------------*//*-----------------Baud generator------------------------*/assign baud_tick = ( baud_cnt == baud_devide - 1'b1 );always @( negedge nRESET_pin or posedge CLK_50M_pin ) beginif( !nRESET_pin )beginbaud_cnt <= 'd0;endelse if( baud_cnt < baud_devide - 1'b1 )beginbaud_cnt <= baud_cnt + 1'b1;endelsebeginbaud_cnt <= 'd0;endend/*----------transmit state machine---------------*/always @( negedge nRESET_pin or posedge CLK_50M_pin ) beginif( !nRESET_pin )beginT_state <= 4'd0;endelsebegincase(T_state)4'd0: if(TXD_start) T_state <= 4'd1;4'd1: if(baud_tick) T_state <= 4'd2; // 开始位04'd2: if(baud_tick) T_state <= 4'd3; // bit 04'd3: if(baud_tick) T_state <= 4'd4; // bit 14'd4: if(baud_tick) T_state <= 4'd5; // bit 24'd5: if(baud_tick) T_state <= 4'd6; // bit 34'd6: if(baud_tick) T_state <= 4'd7; // bit 44'd7: if(baud_tick) T_state <= 4'd8; // bit 54'd8: if(baud_tick) T_state <= 4'd9; // bit 64'd9: if(baud_tick) T_state <= 4'd10; // bit 74'd10: if(baud_tick) T_state <= 4'd0; // 停止位1default: if(baud_tick) T_state <= 4'd0;endcaseendendalways @(negedge nRESET_pin or posedge baud_tick ) beginif( !nRESET_pin )beginTXD <= 1'b1;T_data_reg <= 8'd0;endelsebegincase(T_state)// 4'd0: TXD <= 1'b1;4'd1: beginTXD <= 1'b0;T_data_reg <= T_data;end4'd2: TXD <= T_data_reg[0];4'd3: TXD <= T_data_reg[1];4'd4: TXD <= T_data_reg[2];4'd5: TXD <= T_data_reg[3];4'd6: TXD <= T_data_reg[4];4'd7: TXD <= T_data_reg[5];4'd8: TXD <= T_data_reg[6];4'd9: TXD <= T_data_reg[7];4'd10: TXD <= 1'b1;default: TXD <= 1'b1;endcaseendend//assign TXD = TXD;always @( negedge nRESET_pin or posedge CLK_50M_pin ) beginif( !nRESET_pin )beginTXD_over <= 1'b0;endelsebeginif( T_state ==4'd0 )TXD_over <= 1'b1;elseTXD_over <= 1'b0;endendendmodule。

uart串口通信电路设计-回复UART(通用异步收发传输)是一种常用的串口通信协议,可以实现设备之间的数据传输和通信。

在本文中,将详细介绍UART串口通信电路的设计步骤。

一、什么是UART串口通信电路?UART串口通信电路是一种数字电路,用于将串行数据转换为并行数据,实现设备之间的数据传输和通信。

UART串口通信电路通常由发送电路和接收电路两部分组成。

发送电路:发送电路将并行数据转换为串行数据,并对数据进行格式化。

它通常由一个发送缓冲器、一个发送时钟和控制逻辑组成。

接收电路:接收电路将串行数据转换为并行数据,并对数据进行解码和处理。

它通常由一个接收缓冲器、一个接收时钟和控制逻辑组成。

二、UART串口通信电路的设计步骤1. 确定通信参数在设计UART串口通信电路之前,首先需要确定通信参数,包括波特率、数据位数、校验位数和停止位数等。

这些参数将决定串口通信的速率和精度。

2. 设计发送电路发送电路的主要任务是将并行数据转换为串行数据,并将数据发送到接收设备。

设计发送电路时,需要考虑以下几点:(1)发送缓冲器:发送缓冲器用于存储待发送的数据。

它通常由一个FIFO (先进先出)缓冲器实现,可以提高通信的效率。

(2)时钟和控制逻辑:发送电路需要一个时钟信号来同步数据传输,并且需要控制逻辑来控制数据的发送和处理。

(3)格式化:发送电路需要对数据进行格式化,包括数据位、校验位和停止位的配置。

格式化的目的是提高数据的准确性和可靠性。

3. 设计接收电路接收电路的主要任务是将串行数据转换为并行数据,并将数据传输到接收设备。

设计接收电路时,需要考虑以下几点:(1)接收缓冲器:接收缓冲器用于存储接收到的数据。

它通常由一个FIFO 缓冲器实现,可以提高数据的接收效率。

(2)时钟和控制逻辑:接收电路需要一个时钟信号来同步数据传输,并且需要控制逻辑来控制数据的接收和处理。

(3)解码和处理:接收电路需要对接收到的数据进行解码和处理,包括校验数据的正确性和提取有效数据。

FPGA和单片机串行通信接口的实现FPGA(Field-Programmable Gate Array)和单片机(Microcontroller)是两种常用的数字电子设备,它们在串行通信接口方面有不同的实现方式。

首先,我们需要了解串行通信是一种将数据以位的形式逐个传输的通信方式。

常见的串行通信协议包括UART(Universal Asynchronous Receiver/Transmitter)、SPI(Serial Peripheral Interface)和I2C (Inter-Integrated Circuit)等。

对于FPGA和单片机之间的串行通信,我们可以基于以下几种方式进行实现:1. UART:UART是一种常见的串行通信协议,可以实现全双工的通信。

在FPGA和单片机之间建立UART通信,需要在FPGA中实现UART模块,并将其与单片机的UART接口连接。

在FPGA中,我们可以使用硬件语言(如Verilog或VHDL)来实现UART模块,该模块负责将FPGA内部的数据通过UART协议进行封装和解封装。

单片机与FPGA之间通过TX(发送)和RX (接收)引脚建立连接。

单片机可以通过串口发送数据给FPGA,FPGA接收到数据后进行处理,然后再通过串口将处理后的数据发送给单片机。

2.SPI:SPI是一种用于片上外设之间通信的串行通信协议,常用于FPGA与外部设备(例如传感器、显示器等)之间的通信。

在FPGA和单片机之间建立SPI通信,需要在FPGA中实现SPI控制器,并将其与单片机的SPI接口连接。

FPGA通过把数据写入SPI发送缓冲区或从SPI接收缓冲区读取数据来实现与单片机的通信。

单片机通过控制SPI接口的时钟、数据和使能信号来与FPGA进行数据传输。

3.I2C:I2C是一种双线制串行总线,常用于连接多个设备的系统,例如FPGA、单片机和其他外部设备之间的通信。

在FPGA和单片机之间建立I2C通信,需要在FPGA中实现I2C控制器,并将其与单片机的I2C接口连接。

uart串口通信的波特率UART串口通信的波特率引言:UART(Universal Asynchronous Receiver/Transmitter)是一种常用的串口通信协议,广泛应用于各种嵌入式系统和通信设备中。

波特率是UART通信中的重要参数,决定了数据传输的速率和稳定性。

本文将深入探讨UART串口通信的波特率相关知识,包括波特率的定义、选择和设置方法。

一、波特率的定义波特率是指UART串口通信中单位时间内传输的数据位数。

它用波特(baud)来表示,波特率越高,传输速率越快。

常见的波特率有9600、115200等。

波特率的选择应根据具体应用场景和硬件支持情况来确定,过高或过低的波特率都会导致通信错误或效率低下。

二、波特率的选择在选择波特率时,需要综合考虑以下几个因素:1.硬件支持:不同的UART芯片或模块对波特率的支持范围有限,应根据实际硬件情况选择合适的波特率。

2.传输距离:高波特率会增加串口传输的干扰和误码率,对于长距离传输或噪声干扰较大的环境,应选择较低的波特率以保证通信的可靠性。

3.传输速率:根据数据传输的实时性要求,选择合适的波特率可以提高数据传输的效率。

如果数据传输不是很频繁或对实时性要求不高,可以选择较低的波特率。

4.数据长度:波特率与数据长度有一定的相关性,较长的数据长度需要较高的波特率才能保证及时传输。

三、波特率的设置方法设置UART的波特率需要通过相应的配置寄存器或命令来实现,具体方法因芯片或模块而异。

下面是一种常见的波特率设置方法:1.选择合适的波特率:根据前述因素选择合适的波特率。

2.配置波特率寄存器:通过读写UART的波特率寄存器,将波特率的数值设置为对应的值。

波特率寄存器通常是一个16位的寄存器,其中包含了分频器的值,根据具体芯片的手册来设置。

3.使能UART模块:在波特率设置完成后,需要使能UART模块才能开始通信。

使能UART模块的方法因芯片或模块而异,可参考相应的手册或参考资料。

verilog串口发送例化逻辑函数摘要:1.引言2.Verilog 串口发送的基本原理3.例化逻辑函数的定义和应用4.实例:使用例化逻辑函数实现串口发送5.总结正文:1.引言在数字电子系统中,串口通信是一种常见的通信方式。

Verilog 作为一种硬件描述语言,可以用来描述和实现串口发送功能。

例化逻辑函数是Verilog 中的一种重要编程技巧,可以用来简化和优化代码。

本文将介绍如何使用例化逻辑函数实现串口发送。

2.Verilog 串口发送的基本原理Verilog 中的串口发送功能主要通过两个模块实现:发送器(sender)和接收器(receiver)。

发送器负责将数据字符从并行转换为串行,按位发送给接收器。

接收器负责将串行数据字符接收并转换为并行数据。

3.例化逻辑函数的定义和应用例化逻辑函数是一种可重用的模块,它包含一个或多个输入端口和相应的输出端口。

通过实例化例化逻辑函数,可以方便地实现不同功能的模块。

在Verilog 中,例化逻辑函数的定义和使用方法如下:```verilogmodule example_module (input wire clk,input wire rst,input wire data_in,output wire data_out);reg data_out;always @(posedge clk or posedge rst) beginif (rst) begindata_out <= 1"b0;end else begindata_out <= data_in;endendendmodule```在需要使用例化逻辑函数的地方,可以使用以下方法实例化:```verilogexample_module my_module (.clk(clk),.rst(rst),.data_in(data_in),.data_out(data_out));```4.实例:使用例化逻辑函数实现串口发送下面是一个使用例化逻辑函数实现串口发送的简单示例:```verilogmodule sender (input wire clk,input wire rst,input wire start,input wire [7:0] data,output wire busy);reg [7:0] shift_reg;reg busy_temp;always @(posedge clk or posedge rst) begin if (rst) beginshift_reg <= 8"b0;busy <= 1"b0;end else if (start &&!busy) beginshift_reg <= data;busy <= 1"b1;end else if (!start && busy) beginshift_reg <= {shift_reg[6:0], data};busy <= 1"b0;endendassign busy = busy_temp;endmodulemodule receiver (input wire clk,input wire rst,input wire busy,output reg [7:0] data);reg [7:0] shift_reg;always @(posedge clk or posedge rst) begin if (rst) beginshift_reg <= 8"b0;end else if (busy) beginshift_reg <= {shift_reg[6:0], data};endendassign data = shift_reg[6:0];endmodulemodule top (input wire clk,input wire rst,input wire start,input wire [7:0] data_in,output wire data_out );sender s (.clk(clk),.rst(rst),.start(start),.data(data_in),.busy(busy));receiver r (.clk(clk),.rst(rst),.busy(busy),.data(data_out));endmodule```5.总结本文介绍了如何使用Verilog 编写一个简单的串口发送模块,并使用例化逻辑函数实现不同功能的模块。

verilog串⼝通信程序FPGA实现RS-232串⼝收发的仿真过程(Quartus+Synplify+ModelSim)(2007-09-11 12:17:37)⽹上关于RS-232的异步收发介绍得很多,最近没事学着摸索⽤ModelSim来做时序仿真,就结合⽹上的参考资料和⾃⼰的琢磨,做了这个东西。

针对我这个⼩程序结合FPGA的开发流程,主要⾛了以下⼏步:1. ⽂本程序输⼊(Verilog HDL)2. 功能仿真(ModelSim,查看逻辑功能是否正确,要写⼀个Test Bench)3. 综合(Synplify Pro,程序综合成⽹表)4. 布局布线(Quartus II,根据我选定的FPGA器件型号,将⽹表布到器件中,并估算出相应的时延)5. 时序仿真(ModelSim,根据时延做进⼀步仿真)这⾥贴出我的程序和各个详细步骤,能和各位正在学习的新⼿们⼀起分享。

0. 原理略⼀、⽂本程序输⼊(Verilog HDL)发送端:module trans(clk,rst,TxD_start,TxD_data,TxD,TxD_busy);input clk,rst,TxD_start;input[7:0] TxD_data; lk(clk),.rst(rst),.TxD_start(TxD_start),.TxD_busy(TxD_busy),.TxD_data(TxD_data),.TxD(TxD));rcv rcv(.clk(clk),.rst(rst),.RxD(TxD), xD_data(RxD_data),.RxD_data_ready(RxD_data_ready));initial beginTxD_start = 0;TxD_data = 0;clk = 0;rst = 1;#54 rst = 0;#70 rst = 1;#40 TxD_start = 1'b1;#10 TxD_data = 8'b;#100 TxD_start = 1'b0;endalways begin#30 clk = ~clk;#10 clk = ~clk;endendmodule⼆、综合三、FPGA与PC串⼝⾃收发通信串⼝通信其实简单实⽤,这⾥我就不多说,只把⾃⼰动⼿写的verilog代码共享下。

uart通信的详细讲解

UART通信是一种串行通信方式,用于在数字系统之间传输数据。

UART代表通用异步收发器,它在大多数数字系统中都很普遍,因为它是一种简单而可靠的通信协议。

UART通信基于两个主要的信号线:数据线和时钟线。

数据线用于发送和接收数据,而时钟线则用于同步传输。

在UART通信中,每个数据字符由一个或多个数据位(通常为8位)、一个起始位和一个或多个停止位组成。

起始位用于标记数据字符的开始,而停止位则用于

标记数据字符的结束。

UART通信中的每个数据字符都可以使用相同的格式,并且可以以连续的方式传输。

UART通信的速率由波特率决定,波特率指的是每秒钟传输的位数。

波特率越高,每秒钟传输的数据量就越大。

UART通信的波特率通常在1至115200位/秒之间。

UART通信有两种工作模式:同步和异步。

同步模式使用时钟线进行同步,并且数据字符传输速率与时钟线速率相同。

异步模式不使用时钟线进行同步,并且数据字符的传输速

率与时钟线速率可以不同。

因此,异步模式比同步模式更常用,因为它更简单,并且不需

要与其他设备进行协调。

UART通信具有许多优点,包括可靠性和通用性。

它可以与大多数数字系统和微控制器集成,而且成本低廉。

UART通信还可以用于许多不同的应用程序,如串口通信、远程管理和数据采集。

verilog语法基础Verilog语法基础Verilog是一种硬件描述语言(HDL),用于描述数字电路和系统。

它是一种基于事件的语言,能够描述电路的结构和行为。

本文将介绍Verilog语法的基础知识,包括模块、端口、信号、赋值和运算等。

一、模块(Module)在Verilog中,模块是描述电路的基本单元。

一个模块可以包含多个端口和信号,并定义了电路的功能和结构。

模块的定义使用关键字module,后跟模块的名称和端口列表。

二、端口(Port)Verilog中的端口是模块与外部环境进行通信的接口。

端口可以是输入端口、输出端口或双向端口。

输入端口用于接收外部信号,输出端口用于输出信号至外部,而双向端口则可同时进行输入和输出。

端口的定义使用关键字input、output或inout,后跟端口的类型和名称。

三、信号(Signal)Verilog中的信号用于在模块内部传递和存储数据。

信号可以是寄存器类型或线网类型。

寄存器类型信号用于存储数据,线网类型信号用于传递数据。

信号的定义使用关键字reg或wire,后跟信号的宽度和名称。

四、赋值(Assignment)在Verilog中,使用赋值语句将值分配给信号或变量。

赋值语句可以是阻塞式赋值或非阻塞式赋值。

阻塞式赋值使用等号(=)将右侧的值赋给左侧的信号,而非阻塞式赋值使用双等号(<=)进行赋值。

赋值语句的左侧可以是信号或变量,右侧可以是常数、信号、变量或表达式。

五、运算(Operator)Verilog中支持多种运算,包括算术运算、逻辑运算、位运算和比较运算等。

算术运算包括加法、减法、乘法和除法等;逻辑运算包括与、或、非和异或等;位运算包括位与、位或、位非和位异或等;比较运算包括等于、不等于、大于、小于等。

运算符可以用于常数、信号、变量或表达式之间的运算。

六、条件语句(Conditional Statement)Verilog中的条件语句用于根据条件选择执行不同的操作。

uart通信的详细讲解UART(Universal Asynchronous Receiver/Transmitter,通用异步收发器)是一种半双工的通信方式,应用广泛,主要用于提供客户端/服务器之间的一种简单的连接,尤其是在嵌入式系统中。

UART具有较低的成本和多种可选择的配置,因此受到广泛的欢迎。

UART也称为串行通信,是指数据传输的一种方式,是按字符串顺序发送的一组位。

使用UART来传输的每个数据帧包括前导字节、校验和后缀字节等。

UART通信有两个不同的端口:TTL(经典UART)和RS-232。

TTL 端口的常规电压范围是0-2.8V,而RS-232端口则提供了许多种不同的电压等级,从而容许其他类型的设备(如计算机)通过这种端口进行接口。

很多情况下,UART协议可以在两个不同的芯片之间实现,例如Arduino与Raspberry Pi,甚至是Arduino与手机之间的UART连接。

UART可以分为三个主要组成部分:发送模块、接收模块和控制器。

发送模块用来将信息发送到其他设备,而接收模块则用来从其他设备接收信息。

控制器用来控制两个模块之间通信,并处理奇偶校验等。

UART有两个关键参数:波特率和数据位。

波特率指的是每秒钟发送的比特数。

通常情况下,波特率越高,通信速度越快,但高波特率也意味着更多的误码率。

数据位是指每个字符有多少位,通常为7位或8位。

另外,它还有一个介绍的参数:停止位。

停止位是当发送者读取数据时,发送另一个字节之前的延迟时间。

总的来说,UART通信是一种常见的通信技术,能够方便客户端与服务器之间的数据传输。

它具有低成本、多种可选配置、简单的连接以及容易接入的优势,使其受到各行业的青睐。

uart串口通信时序摘要:一、引言1.串口通信的基本概念2.UART 串口通信的优势二、UART 串口通信的工作原理1.UART 的工作原理2.UART 的数据传输过程三、UART 串口通信时序1.波特率2.数据位3.停止位4.奇偶校验四、UART 串口通信的帧结构1.起始位2.数据位3.奇偶校验位4.停止位5.帧间隔五、UART 串口通信的应用1.计算机与外部设备通信2.嵌入式系统通信3.物联网通信正文:UART 串口通信是一种异步通信方式,广泛应用于各种电子设备之间的数据传输。

它的优势在于通信双方不需要同步时钟信号,只需约定好波特率、数据位、停止位等参数,即可实现稳定的数据传输。

UART 串口通信的工作原理是通过UART(Universal Asynchronous Receiver/Transmitter,通用异步接收/发送器)芯片将串行数据转换为并行数据,或将并行数据转换为串行数据。

UART串口通信的数据传输过程主要包括:数据的接收、数据的发送、波特率发生器以及数据流控制。

在UART 串口通信时序中,波特率是一个关键参数,决定了数据传输的速率。

数据位表示一个字符所占的位数,常见的有7 位、8 位、9 位等。

停止位用于表示一个字符的结束,常见的有1 位、2 位。

奇偶校验用于检测数据传输过程中的错误,常见的有奇校验、偶校验、无校验等。

UART 串口通信的帧结构包括起始位、数据位、奇偶校验位、停止位和帧间隔。

起始位用于标识一个字符的开始,数据位用于传输有效数据,奇偶校验位用于检测数据传输过程中的错误,停止位用于表示一个字符的结束,帧间隔用于分隔不同的字符。

UART 串口通信在许多应用场景中发挥着重要作用,如计算机与外部设备(如鼠标、键盘、打印机等)通信、嵌入式系统之间的通信以及物联网通信。

uart的基本编程步骤UART(通用异步收发传输)是一种常见的串行通信协议,用于在微控制器和外部设备之间进行数据传输。

下面是UART的基本编程步骤:1. 初始化UART,首先,你需要在微控制器上初始化UART模块。

这通常涉及设置波特率(通信速率)、数据位、停止位和校验位等参数。

这些参数的设置取决于你的具体应用需求和外部设备的要求。

2. 配置引脚,UART通常使用两个引脚进行数据传输,一个用于发送(TX),一个用于接收(RX)。

你需要在微控制器上配置这些引脚,并确保它们与外部设备正确连接。

3. 发送数据,要发送数据,你需要将要发送的数据加载到UART发送缓冲区。

一旦数据被加载,UART模块将自动开始发送数据。

你需要确保发送的数据符合UART的规范,并且在发送数据之前,需要检查发送缓冲区是否为空,以避免数据丢失。

4. 接收数据,接收数据与发送类似,你需要设置接收缓冲区,并在接收到数据后从中读取数据。

同样,你需要检查接收缓冲区是否有新的数据可用,以避免数据丢失。

5. 中断处理(可选),在一些情况下,你可能需要使用中断来处理UART的发送和接收。

这可以帮助你及时响应数据的到来或发送完成等事件。

6. 错误处理,最后,你需要考虑如何处理可能出现的错误,比如数据丢失、校验错误等。

这可能涉及到错误标志的检查和相应的处理流程。

总的来说,UART的基本编程步骤包括初始化UART模块、配置引脚、发送数据、接收数据、中断处理(可选)和错误处理。

在实际编程中,你需要根据具体的微控制器型号和外部设备的通信协议要求来进行相应的设置和处理。

UART串口通信的基本原理和通信过程UART(Universal Asynchronous Receiver/Transmitter)是一种常见的串口通信协议,用于在计算机和外部设备之间进行数据传输。

本文将详细解释UART串口通信的基本原理和通信过程,并提供一个全面、详细、完整且深入的解释。

1. UART串口通信的基本原理UART串口通信是一种基于异步传输的通信协议,它使用两根信号线(TX和RX)来实现数据的传输。

UART通信的基本原理如下:•数据位:UART通信中的每个字符由一定数量的数据位组成,通常为8位。

每个数据位可以表示一个字节(8位二进制数)。

•停止位:每个字符之后会有一个停止位,用于指示一个字符的结束。

通常情况下,UART通信中的停止位为1个。

•起始位:每个字符之前会有一个起始位,用于指示一个字符的开始。

通常情况下,UART通信中的起始位为1个。

•波特率:UART通信中的波特率(Baud Rate)表示每秒钟传输的比特数。

常见的波特率有9600、115200等。

UART通信使用的是异步传输,即发送端和接收端没有共同的时钟信号。

因此,在通信过程中,发送端和接收端需要事先约定好相同的波特率,以确保数据的正确传输。

2. UART串口通信的通信过程UART串口通信的通信过程包括数据的发送和接收两个步骤。

下面将详细介绍UART串口通信的通信过程。

数据发送过程1.发送端准备数据:发送端需要准备要发送的数据,并将数据存储在发送缓冲区中。

2.发送端发送起始位:发送端在发送数据之前,会先发送一个起始位,用于指示一个字符的开始。

起始位的电平通常为低电平。

3.发送端发送数据位:发送端按照数据位的顺序,将数据位的电平依次发送出去。

每个数据位的电平表示一个二进制位(0或1)。

4.发送端发送停止位:发送端在发送完所有的数据位之后,会发送一个停止位,用于指示一个字符的结束。

停止位的电平通常为高电平。

数据接收过程1.接收端等待起始位:接收端在接收数据之前,会等待接收到一个起始位的电平变化,用于指示一个字符的开始。

这个程序没有仿真、没有测试。

1 UART功能设计1.1 UART的工作原理异步通信时,UART发送/接收数据的传输格式如图1所示,一个字符单位由开始位、数据位、停止位组成。

异步通信的一帧传输经历以下步骤:(1)无传输。

发送方连续发送信号,处于信息“1”状态。

(2)起始传输。

发送方在任何时刻将传号变成空号,即“1”跳变到“O”,并持续1位时间表明发送方开始传输数据。

而同时,接收方收到空号后,开始与发送方同步,并期望收到随后的数据。

(3)奇偶传输。

数据传输之后是可供选择的奇偶位发送或接收。

(4)停止传输。

最后是发送或接收的停止位,其状态恒为“1”。

其程序的结构框图如下:该程序的效果是串口接受到从计算机发送过来的数据后,又把数据发回给计算机,串口通信是串行的。

其uart.v为顶层文件,包含其他模块,speed_select.v文件的作用为为uart_rx.v和uart_tx.v 设置波特率。

uart.v(顶层文件)`timescale 1ns / 1ps///////////////////////////////////////////////////////////////////// /////////////// Company:// Engineer://// Create Date: 16:08:27 11/12/2010// Design Name:// Module Name: uart// Project Name:// Target Devices:// Tool versions:// Description://// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments://///////////////////////////////////////////////////////////////////// /////////////module uart(clk,rst_n,rs232_rx,rs232_tx);input clk,rst_n,rs232_rx;output rs232_tx;wire bps_start1,bps_start2,clk_bps1,clk_bps2,rx_int;wire [7:0] rx_data;//发送模块的时钟speed_select speed_tx (.clk(clk),.rst_n(rst_n),.bps_start(bps_start2),.clk_bps(clk_bps1));//接受模块的时钟speed_select speed_rx (.clk(clk),.rst_n(rst_n),.bps_start(bps_start2),.clk_bps(clk_bps2));//接受模块uart_rx uart_rx (.clk(clk),.rst_n(rst_n),.clk_bps(clk_bps1),.rs232_rx(rs232_rx),.bps_start(bps_start1),.rx_int(rx_int),.rx_data(rx_data));//发送模块uart_tx uart_tx (.clk(clk),.rst_n(rst_n),.clk_bps(clk_bps2),.rx_int(rx_int),.rx_data(rx_data),.bps_start(bps_start2),.rs232_tx(rs232_tx));endmodulespeed_select.v`timescale 1ns / 1ps///////////////////////////////////////////////////////////////////// /////////////// Company:// Engineer://// Create Date: 16:12:45 11/12/2010// Design Name:// Module Name: speed_select// Project Name:// Target Devices:// Tool versions:// Description://// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments://///////////////////////////////////////////////////////////////////// /////////////module speed_select(clk,rst_n,bps_start,clk_bps);input clk,rst_n,bps_start;output clk_bps;reg [12:0] cnt;reg clk_bps_r;/*波特率对应的脉冲的个数。

计算方法如下:以9600bps为例:1s/9600/20ns=5208.33333,即有5208个周期。

parameter bps9600 = 5208,bps19200 = 2604,bps38400 = 1302,bps57600 = 868,bps115200 = 434;个数的一半,即在周期的中间位置。

进行采样。

parameter bps9600_2 = 2604,bps19200_2 = 1302,bps38400_2 = 652,bps57600_2 = 434,bps115200_2 =217;*/`define bps9600 5208`define bps9600_2 2604always @(posedge clk or negedge rst_n)beginif(!rst_n)cnt <= 0;else if((cnt == `bps9600)|| !bps_start) //在bps_start为低时,进行开始计数,bps_start 为高时,停止计数。

cnt <= 0;elsecnt <= cnt+1;endalways @(posedge clk or negedge rst_n)if(!rst_n)clk_bps_r <= 0;else if(cnt == `bps9600_2) //岂不是只在一个时刻为高电平clk_bps_r <= 1;elseclk_bps_r <= 0;assign clk_bps = clk_bps_r;endmoduleuart_rx.v`timescale 1ns / 1ps///////////////////////////////////////////////////////////////////// /////////////// Company:// Engineer://// Create Date: 16:14:13 11/12/2010// Design Name:// Module Name: uart_rx// Project Name:// Target Devices:// Tool versions:// Description://// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments://///////////////////////////////////////////////////////////////////// /////////////module uart_rx(clk,rst_n,clk_bps,rs232_rx,bps_start,rx_int,rx_data); input clk,rst_n,clk_bps,rs232_rx;output bps_start,rx_int;output [7:0] rx_data;//接受数据寄存器,捕捉rs232_rx的下降沿reg rs232_rx0,rs232_rx1,rs232_rx2,rs232_rx3;wire neg_rs232_rx; //表示数据线接收到下降沿always @(posedge clk or negedge rst_n)if(!rst_n)beginrs232_rx0 <= 1'b0;rs232_rx1 <= 1'b0;rs232_rx2 <= 1'b0;rs232_rx3 <= 1'b0;endelsebeginrs232_rx0 <= rs232_rx;rs232_rx1 <= rs232_rx0;rs232_rx2 <= rs232_rx1;rs232_rx3 <= rs232_rx2;end//下面的下降??检测??以滤掉20ns-40ns之间的毛刺。

assign neg_rs232_rx = rs232_rx3 & rs232_rx2 & ~rs232_rx1 & ~rs232_rx;reg bps_start_r;reg [3:0] num;reg rx_int;always @(posedge clk or negedge rst_n)if(!rst_n)beginbps_start_r <= 1'bz;rx_int <= 1'b0;endelse if(neg_rs232_rx)beginbps_start_r <= 1'b1;rx_int <= 1'b1;endelse if(num == 4'd12) // 当数据传送结束时,bps_start==0,则,波特率中的计数器不用工作。

beginbps_start_r <= 1'b0;rx_int <= 1'b0;endassign bps_start = bps_start_r;reg [7:0] rs_data_r; //串口接受数据寄存器reg [7:0] rs_temp_data;always @(posedge clk or negedge rst_n)if(!rst_n)beginnum = 4'd0;rs_data_r = 8'd0;rs_temp_data = 8'd0;endelse if(rx_int)beginif(clk_bps)beginnum <= num+1;case(num)4'd1: rs_temp_data[0] = rs232_rx;4'd2: rs_temp_data[1] = rs232_rx;4'd3: rs_temp_data[2] = rs232_rx;4'd4: rs_temp_data[3] = rs232_rx;4'd5: rs_temp_data[4] = rs232_rx;4'd6: rs_temp_data[5] = rs232_rx;4'd7: rs_temp_data[6] = rs232_rx;4'd8: rs_temp_data[7] = rs232_rx;default: ;endcaseendendelse if(num == 4'd12)beginnum <= 0;rs_data_r <= rs_temp_data;endassign rs232_data = rs_data_r;endmoduleuart_tx.v`timescale 1ns / 1ps///////////////////////////////////////////////////////////////////// /////////////// Company:// Engineer://// Create Date: 16:16:24 11/12/2010// Design Name:// Module Name: uart_tx// Project Name:// Target Devices:// Tool versions:// Description://// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments://///////////////////////////////////////////////////////////////////// /////////////module uart_tx(clk,rst_n,clk_bps,rx_int,rx_data,bps_start,rs232_tx); input clk,rst_n,clk_bps,rx_int;input [7:0] rx_data;output bps_start,rs232_tx;reg rx_int0,rx_int1,rx_int2; //信号寄存器,捕捉下降沿。