数字电路逻辑设计课后习题解答(标注)

- 格式:pdf

- 大小:5.41 MB

- 文档页数:128

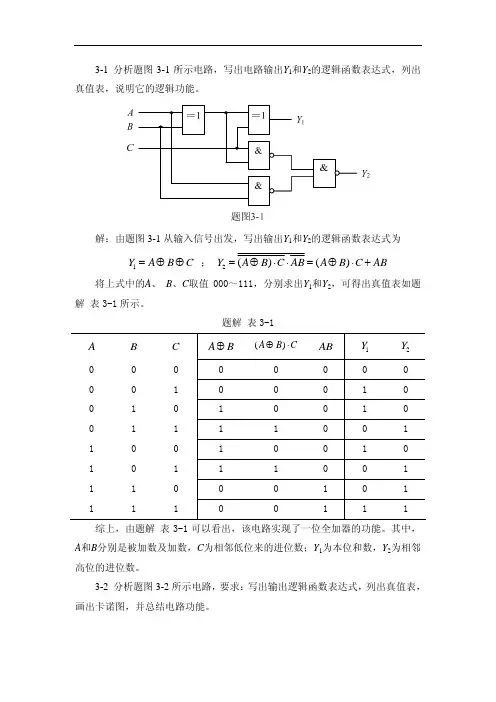

3-1 分析题图3-1所示电路,写出电路输出Y 1和Y 2的逻辑函数表达式,列出真值表,说明它的逻辑功能。

解:由题图3-1从输入信号出发,写出输出Y 1和Y 2的逻辑函数表达式为1Y A B C =⊕⊕ ; 2()()Y A B C AB A B C A =⊕⋅⋅=⊕⋅+B将上式中的A 、 B 、C 取值000~111,分别求出Y 1和Y 2,可得出真值表如题解 表3-1所示。

题解 表3-1ABCA B ⊕()A B C ⊕⋅AB1Y2Y0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 1 0 0 1 0 0 1 1 1 1 0 0 1 1 0 0 1 0 0 1 0 1 0 1 1 1 0 0 1 1 1 0 0 0 1 0 1 111111综上,由题解 表3-1可以看出,该电路实现了一位全加器的功能。

其中,A 和B 分别是被加数及加数,C 为相邻低位来的进位数;Y1为本位和数,Y 2为相邻高位的进位数。

3-2 分析题图3-2所示电路,要求:写出输出逻辑函数表达式,列出真值表,画出卡诺图,并总结电路功能。

解:由题图3-2从输入信号出发,写出输出F 的逻辑函数表达式为()()F A B C D =:::将上式中的A 、 B 、C 、D 取值0000~1111,求出F ,可得真值表和卡诺图分别如题解 表3-2和题解 图3-1所示。

题解 表3-2A B C DA B : C D :F0 0 0 0 1 1 1 0 0 0 1 1 0 0 0 0 1 0 1 0 0 0 0 1 1 1 1 1 0 1 0 0 0 1 0 0 1 0 1 0 0 1 0 1 1 0 0 0 1 0 1 1 1 0 1 0 1 0 0 0 0 1 0 1 0 0 1 0 0 11 0 1 0 0 0 1 1 0 1 1 0 1 0 1 1 0 0 1 1 1 1 1 0 1 1 0 0 1 1 1 0 1 0 0 1 1 1 1 1 1 1综上,由题解 表3-2可以看出,当输入A 、 B 、C 、D 中含有偶数个“1”时,输出;否则,当输入A 、 B 、C 、D 中含有奇数个“1”时,输出。

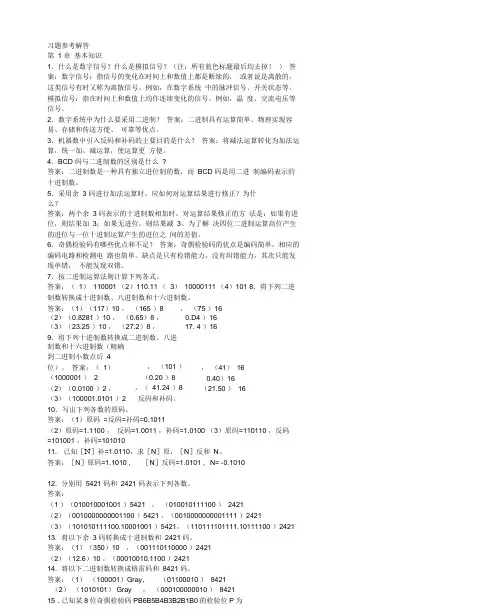

习题参考解答第1章基本知识1.什么是数字信号?什么是模拟信号?(注:所有蓝色标题最后均去掉!)答案:数字信号:指信号的变化在时间上和数值上都是断续的,或者说是离散的,这类信号有时又称为离散信号。

例如,在数字系统中的脉冲信号、开关状态等。

模拟信号:指在时间上和数值上均作连续变化的信号。

例如,温度、交流电压等信号。

2.数字系统中为什么要采用二进制?答案:二进制具有运算简单、物理实现容易、存储和传送方便、可靠等优点。

3.机器数中引入反码和补码的主要目的是什么?答案:将减法运算转化为加法运算,统一加、减运算,使运算更方便。

4.BCD码与二进制数的区别是什么?答案:二进制数是一种具有独立进位制的数,而BCD码是用二进制编码表示的十进制数。

5.采用余3码进行加法运算时,应如何对运算结果进行修正?为什么?答案:两个余3码表示的十进制数相加时,对运算结果修正的方法是:如果有进位,则结果加3;如果无进位,则结果减3。

为了解决四位二进制运算高位产生的进位与一位十进制运算产生的进位之间的差值。

6.奇偶检验码有哪些优点和不足?答案:奇偶检验码的优点是编码简单,相应的编码电路和检测电路也简单。

缺点是只有检错能力,没有纠错能力,其次只能发现单错,不能发现双错。

7.按二进制运算法则计算下列各式。

答案:(1)110001 (2)110.11 (3)10000111 (4)1018.将下列二进制数转换成十进制数、八进制数和十六进制数。

答案:(1)(117)10 ,(165)8 ,(75)16(2)(0.8281)10 ,(0.65)8 ,(0.D4)16(3)(23.25)10 ,(27.2)8 ,(17. 4)169.将下列十进制数转换成二进制数、八进制数和十六进制数(精确到二进制小数点后4位)。

答案:(1)(1000001)2 ,(101)8 ,(41)16(2)(0.0100)2 ,(0.20)8 ,(0.40)16(3)(100001.0101)2 ,(41.24)8 ,(21.50)1610.写出下列各数的原码、反码和补码。

![数字逻辑电路与系统设计[蒋立平主编][习题解答]](https://uimg.taocdn.com/fd945382a21614791611283f.webp)

![数字逻辑电路与系统设计[蒋立平主编][习题解答]](https://uimg.taocdn.com/cddc61bd700abb68a882fb25.webp)

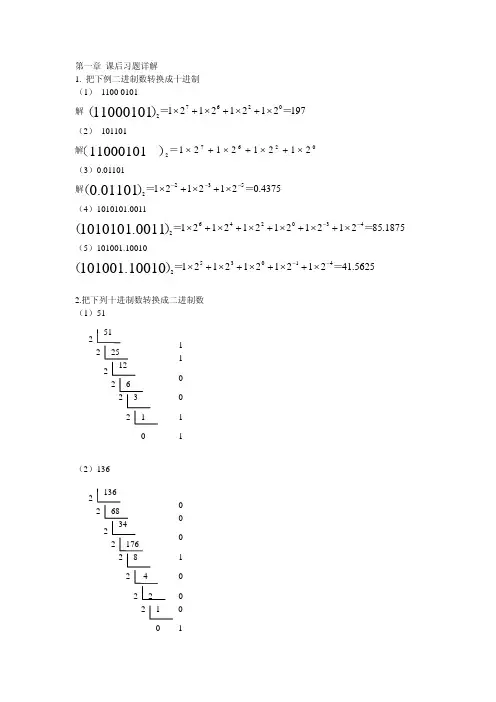

第1章习题及解答1.1 将下列二进制数转换为等值的十进制数。

(1)(11011)2 (2)(10010111)2(3)(1101101)2 (4)(11111111)2(5)(0.1001)2(6)(0.0111)2(7)(11.001)2(8)(101011.11001)2题1.1 解:(1)(11011)2 =(27)10 (2)(10010111)2 =(151)10(3)(1101101)2 =(109)10 (4)(11111111)2 =(255)10(5)(0.1001)2 =(0.5625)10(6)(0.0111)2 =(0.4375)10(7)(11.001)2=(3.125)10(8)(101011.11001)2 =(43.78125)10 1.3 将下列二进制数转换为等值的十六进制数和八进制数。

(1)(1010111)2 (2)(110111011)2(3)(10110.011010)2 (4)(101100.110011)2题1.3 解:(1)(1010111)2 =(57)16 =(127)8(2)(110011010)2 =(19A)16 =(632)8(3)(10110.111010)2 =(16.E8)16 =(26.72)8(4)(101100.01100001)2 =(2C.61)16 =(54.302)81.5 将下列十进制数表示为8421BCD码。

(1)(43)10 (2)(95.12)10(3)(67.58)10 (4)(932.1)10题1.5 解:(1)(43)10 =(01000011)8421BCD(2)(95.12)10 =(10010101.00010010)8421BCD(3)(67.58)10 =(01100111.01011000)8421BCD(4)(932.1)10 =(100100110010.0001)8421BCD1.7 将下列有符号的十进制数表示成补码形式的有符号二进制数。

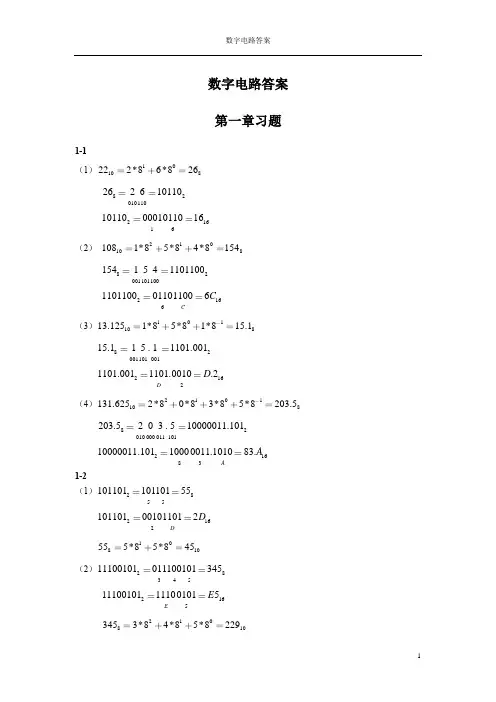

数字电路与逻辑设计习题及参考答案数字电路与逻辑设计习题及参考答案- 2 -⼀、选择题1. 以下表达式中符合逻辑运算法则的是 D 。

A.C ·C=C 2B.1+1=10C.0<1D.A+1=12. ⼀位⼗六进制数可以⽤ C 位⼆进制数来表⽰。

A. 1B. 2C. 4D. 163. 当逻辑函数有n 个变量时,共有 D 个变量取值组合?A. nB. 2nC. n 2D. 2n4. 逻辑函数的表⽰⽅法中具有唯⼀性的是 A 。

A .真值表 B.表达式 C.逻辑图 D.状态图5. 在⼀个8位的存储单元中,能够存储的最⼤⽆符号整数是 D 。

A.(256)10B.(127)10C.(128)10D.(255)106.逻辑函数F=B A A ⊕⊕)( = A 。

A.BB.AC.B A ⊕D. B A ⊕7.求⼀个逻辑函数F 的对偶式,不可将F 中的 B 。

A .“·”换成“+”,“+”换成“·” B.原变量换成反变量,反变量换成原变量 C.变量不变D.常数中“0”换成“1”,“1”换成“0” 8.A+BC= C 。

B B.A+C C.(A+B)(A+C) D.B+C9.在何种输⼊情况下,“与⾮”运算的结果是逻辑0。

DA.全部输⼊是0 B.任⼀输⼊是0 C.仅⼀输⼊是0 D.全部输⼊是110.在何种输⼊情况下,“或⾮”运算的结果是逻辑1。

AA.全部输⼊是0 B.全部输⼊是1 C.任⼀输⼊为0,其他输⼊为1 D.任⼀输⼊为1 11.⼗进制数25⽤8421BCD码表⽰为 B 。

A.10 101B.0010 0101C.100101D.1010112.不与⼗进制数(53.5)10等值的数或代码为C 。

A.(0101 0011.0101)8421BCDB.(35.8)16C.(110101.11)2D.(65.4)813.以下参数不是矩形脉冲信号的参数D 。

A.周期B.占空⽐C.脉宽D.扫描期14.与⼋进制数(47.3)8等值的数为: B A. (100111.0101)2 B.(27.6)16 C.(27.3 )16D. (100111.101)215. 常⽤的BCD码有 D 。

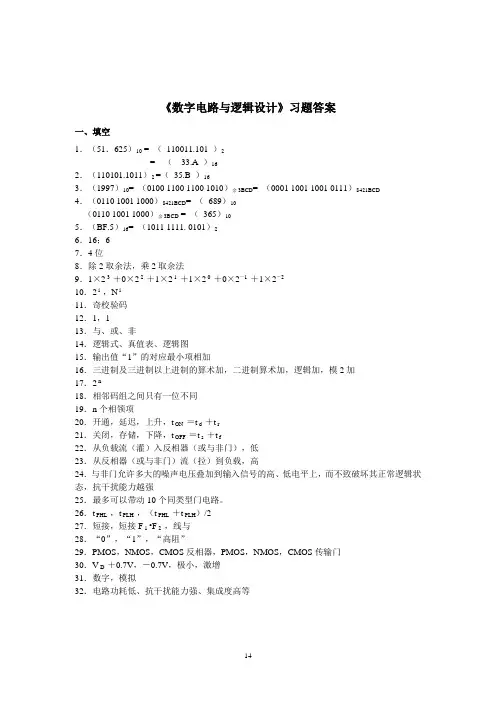

《数字电路与逻辑设计》习题答案一、填空1.(51.625)10 = (110011.101 )2= (33.A )162.(110101.1011)2 =(35.B )163.(1997)10= (0100 1100 1100 1010)余3BCD= (0001 1001 1001 0111)8421BCD 4.(0110 1001 1000)8421BCD= (689)10(0110 1001 1000)余3BCD = (365)105.(BF.5)16= (1011 1111. 0101)26.16;67.4位8.除2取余法,乘2取余法9.1×2 3 +0×2 2 +1×2 1 +1×2 0 +0×2-1 +1×2-210.2 i ,N i11.奇校验码12.1,113.与、或、非14.逻辑式、真值表、逻辑图15.输出值“1”的对应最小项相加16.三进制及三进制以上进制的算术加,二进制算术加,逻辑加,模2加17.2 n18.相邻码组之间只有一位不同19.n个相领项20.开通,延迟,上升,t ON =t d +t r21.关闭,存储,下降,t OFF =t s +t f22.从负载流(灌)入反相器(或与非门),低23.从反相器(或与非门)流(拉)到负载,高24.与非门允许多大的噪声电压叠加到输入信号的高、低电平上,而不致破坏其正常逻辑状态,抗干扰能力越强25.最多可以带动10个同类型门电路。

26.t PHL ,t PLH ,(t PHL +t PLH)/227.短接,短接F 1 •F 2 ,线与28.“0”,“1”,“高阻”29.PMOS,NMOS,CMOS反相器,PMOS,NMOS,CMOS传输门30.V D+0.7V,-0.7V,极小,激增31.数字,模拟32.电路功耗低、抗干扰能力强、集成度高等33.V NL= V iL(max) -V oL(max)34.电路任一时刻的输出仅取决于该时刻的输入状态,而与电路前一时刻的状态无关35.只包含门电路(无存储元件)36.37.确定它的逻辑功能,并加以改进38.两数的本位加,不带低位的进位加,带进位加39.16个,低电平“0”,高电平“1”40.它们都有两个稳态,可以触发翻转,故具有记忆能力41.特性表、特性方程、波形图42.D、T'、T、RS、JK43.可以用CP控制其翻转时刻,同步触发器、主从触发器、边沿触发器,电平触发、主从触发、边沿触发44.主从、边沿触发器可以克服空翻,而同步触发器不能克服空翻45.两门之间因交叉耦合而产生的自锁作用46.RS=0,R、S不能同时为“1”47.0,148.可控制的计数,计数翻转,保持原状态49.下降,上升,150.边沿触发方式51.同步时序电路,异步时序电路52.触发器53.统计计数脉冲个数54.Q i-1 Q i-2‥‥‥Q 1 Q 0 ,Q n-1 Q n-2 ‥‥‥Q 1Q 055.暂存,平移56.串/并转换57.16μS58.波形变换、整形、脉冲鉴幅二、选择题:1. A D2. B C D3. A B4. D5. C6. A B D7. D.8. C9. B10. D11. B12. A.13. B14. A B三、化简下列各题1.用代数法化简下列函数为最简与或表达式(1)F=A B+B C+AC=B(A+C)+AC=B AC+AC=B+AC(2)F=C D+CD+C D+C D=(C D+C D)+(CD+C D)=C+C=1(3)F=AB C+AB+B C+AC=AB+B C+AC=AB+B C(4)F=A+CDAD=A+BCD+AD+B+B+B=A+B2.将下列函数式化为最小项表达式(1)F=AB+BC+AC=AB(C+C)+(A+A)BC+A(B+B)C =ABC+AB C+A BC+A B C(2)F=BCAB =AB+BC=AB(C+C)+(A+A)BC=ABC+AB C+A BC3.用代数法证明下列等式(1)左式=(A B+B)+(A CD+C)+D=A+B+A D+C+D=A +B +D +C +D=1(2)A ⊕0=A ·0+A ·1=A(3)A ⊕1=A ·1+A ·1 =A(4)A ⊕A =A ·A +A ·A=A +A =14.直接写出下列各函数的对偶式F',并用反演规则写出其反演式F(1)F'=(A +B )(B +C )(C +A D )F =(A +B )(B +C )(C +A D )(2)F'=A ·)+(E D C BF =A ·)+(E D C B5.用对偶规划求下列各式的对偶等式(1)左式的对偶式为(A +B )(A +C )(B +C +D )右式的对偶式为(A +B )(A +C )∴其对偶等式为:(A +B )(A +C )(B +C +D )=(A +B )(A +C )(根据对偶规则两式相等,则其对偶式也相等)(2)左式的F'1 =C B A ⋅⋅右式的F'2 =A +B +C其对偶等式为:C B A ⋅⋅=A +B +C6.试写出下列卡诺图的最小项表达式,并用卡诺图法求其最简与或式(1)最小项表达式F (A 、B 、C )=∑),,,,(54310 或F =A B C +A B C +A BC +A B C +A B C 最简与或式F =A C +B(2)最小项表达式F (A 、B 、C 、D )=),,,,,(1086420∑或F =A B C D +A B C D +A B C D +A BC D +A B C D +A B C D ;最简与或式F =B D +A D7.用卡诺图法化简下列函数为最简与或式(1)F =A B C +AD +D (B +C )+A C +A D =A +B C +D(2)10157φ32869)+(,(11,,,,,,,=A B+A C+B D+CD9.(1)错(2) 错(3) 对10.⋅⋅=+F⋅BCBAC1⋅B=C+⊕F⋅BCA2+⋅=3⋅⋅BCF⋅ACBA11.当控制信号BC=00时,输出是输入变量的反码。

![数字电路与逻辑设计习题学生常见问题答疑[1]](https://uimg.taocdn.com/fe7dfaf63086bceb19e8b8f67c1cfad6195fe988.webp)

数字电路与逻辑设计习题学生常见问题答疑[1]第一章绪论1、数字电路有什么优点?答:首先数字电路能产生更廉价,更可靠的数字处理系统。

其次数字处理硬件允许可编程操作,同时数字硬件和软件实现与模拟电路和模拟信号处理系统相比,通常具有更高的精度。

2、数字电路与模拟电路有什么区别?答:数字电路与模拟电路同等重要,构成数字电路与模拟电路的基本元件都是半导体器件。

但是它们工作状态不同,实现功能不同,工作信号不同,如:数字电路中三极管工作在饱和区和截止区,模拟电路中三极管工作在放大区。

数字电路实现逻辑功能,完成逻辑运算,模拟电路主要是放大电信号。

数字电路处理离散信号,模拟电路处理连续信号。

3、数字电路设计的趋势?答:当前数字电路设计的趋势是,越来越大的设计,越来越短的推向市场的时间,越来越低的价格,设计方法越来越依赖于电子设计自动化(EDA)工具。

多层次的设计表述,集成电路的设计与制造分离,芯片生产厂家提供模型或标准单元库,设计公司负责电路功能设计。

电路功能设计已进入片上系统(SOC)时代,知识产权模块(IP 核)产品化。

第二章逻辑函数及其简化1、逻辑函数为什么要化简?答:一个逻辑函数可以写成不同的表达式形式,表达式越简单,所表示的逻辑关系越明显。

化简电路的目的,就是为了降低系统的成本,提高电路的可靠性,以用最少的逻辑门实现逻辑函数。

2、公式法化简中那么多公式怎么记?它有什么优缺点?答:逻辑代数的常用公式,反映了逻辑代数运算的基本规律,是化简逻辑函数、分析和设计逻辑电路的基本公式,必须熟悉和掌握。

公式法化简没有固定的步骤。

能否以最快的速度进行化简,与经验、技巧和对公式掌握及运用的熟练程度有关。

该方法的优点是输入变量个数不受限制,缺点是结果是否为最简有时不易判断。

3、卡诺图法化简的优点?答:利用卡诺图可以直观、方便地化简逻辑函数,并且克服了公式化简法对最终化简结果难以确定等缺点。

第三章集成逻辑门1、第三章感觉和其它章节没关系,是否不重要?答:第三章介绍了常用逻辑门的内部电路结构以及外部特性,对后续学习非常重要。

数字逻辑电路设计第二版答案【篇一:蒋立平版数字逻辑电路与系统设计习题答案】1.1 将下列二进制数转换为等值的十进制数。

(1)(11011)2(2(10010111)2 (3)(1101101)2 (4(11111111)2 (5)(0.1001)2 (6 (0.0111)2 (7)(11.001)2 (8 (101011.11001)2题1.1 解:(1)(11011)2 =(27)10(10010111)2 =(151)10(3)(1101101)2 =(109)10 (11111111)2 =(255)10(5)(0.1001)2 =(0.5625)10 (0.0111)2 =(0.4375)10(7)(11.001)2 =(3.125)10(101011.11001)2 =(43.78125)101.3 数。

(1)(1010111)2(110111011)2 (3)(10110.011010)2(4)(101100.110011)2 题1.3 解:(1)(1010111)2 =(57)16 =(127)8(2)(110011010)2 =(19a)16 =(632)8 (3)(10110.111010)2 =(16.e8)16 =((4)(101100.01100001)2 =(2c.61)16 =1.5 将下列十进制数表示为8421bcd码。

(1)(43)10(95.12)10 (3)(67.58)10 ((932.1)10题1.5 解:(1)(43)10 =(01000011)8421bcd(2)(95.12)10 =(10010101.00010010)8421bcd (3)(67.58)10 =(01100111.01011000)8421bcd (4)(932.1)10 =(1.7 将下列有符号的十进制数表示成补二进制数。

(1) +13 (2)?9(3)+3 (4)?题1.7解:(1) +13 =(01101)2 ((10111)2(3) +3 =(00011)2 ((11000)21.9 用真值表证明下列各式相等。