数字电路逻辑设计第3章

- 格式:ppt

- 大小:1.71 MB

- 文档页数:73

习题参考解答第1章基本知识1.什么是数字信号?什么是模拟信号?(注:所有蓝色标题最后均去掉!)答案:数字信号:指信号的变化在时间上和数值上都是断续的,或者说是离散的,这类信号有时又称为离散信号。

例如,在数字系统中的脉冲信号、开关状态等。

模拟信号:指在时间上和数值上均作连续变化的信号。

例如,温度、交流电压等信号。

2.数字系统中为什么要采用二进制?答案:二进制具有运算简单、物理实现容易、存储和传送方便、可靠等优点。

3.机器数中引入反码和补码的主要目的是什么?答案:将减法运算转化为加法运算,统一加、减运算,使运算更方便。

4.BCD码与二进制数的区别是什么?答案:二进制数是一种具有独立进位制的数,而BCD码是用二进制编码表示的十进制数。

5.采用余3码进行加法运算时,应如何对运算结果进行修正?为什么?答案:两个余3码表示的十进制数相加时,对运算结果修正的方法是:如果有进位,则结果加3;如果无进位,则结果减3。

为了解决四位二进制运算高位产生的进位与一位十进制运算产生的进位之间的差值。

6.奇偶检验码有哪些优点和不足?答案:奇偶检验码的优点是编码简单,相应的编码电路和检测电路也简单。

缺点是只有检错能力,没有纠错能力,其次只能发现单错,不能发现双错。

7.按二进制运算法则计算下列各式。

答案:(1)110001 (2)110.11 (3)10000111 (4)1018.将下列二进制数转换成十进制数、八进制数和十六进制数。

答案:(1)(117)10 ,(165)8 ,(75)16(2)(0.8281)10 ,(0.65)8 ,(0.D4)16(3)(23.25)10 ,(27.2)8 ,(17. 4)169.将下列十进制数转换成二进制数、八进制数和十六进制数(精确到二进制小数点后4位)。

答案:(1)(1000001)2 ,(101)8 ,(41)16(2)(0.0100)2 ,(0.20)8 ,(0.40)16(3)(100001.0101)2 ,(41.24)8 ,(21.50)1610.写出下列各数的原码、反码和补码。

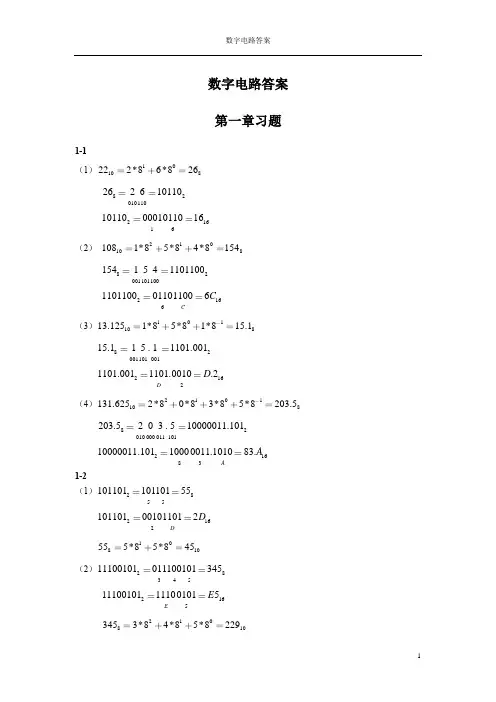

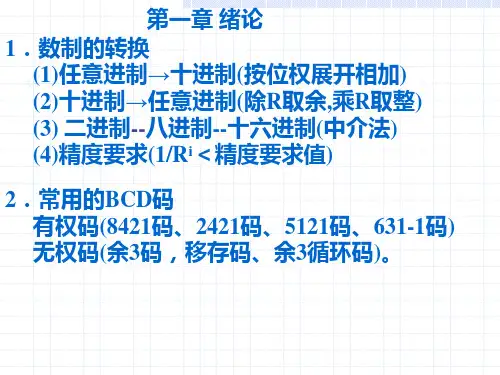

第一章1.4(1)10101=1∗104+1∗102+1∗100(2)0.10101=1∗10−1+1∗10−3+1∗10−5(3)1010.101=1∗103+1∗101+1∗10−1+1∗10−31.5(1)(163)10=(10100011)2(2)(0.525)10=(0.100001)2(3)(41.41)10=(101001.01101000111)21.6(123)8=(1∗82+2∗8+3)10=(83)10 1.76n<(0.3)3⇒n log6<3(log3−1)⇒n<3(log3−1)log6=−2.016⇒n≤−3(8.705)10≈(12.412)61.8A(B+C+D)+BC(A̅+D̅)+D̅⇒A+A BC+D̅1.9A̅+BA+C+DA⇒A̅+B+C+D 1.10(1)F(A,B,C)|B=1&C=1=(AB+A̅C)|B=1&C=1=1(2)F(A,B,C)|A̅=1&B=1&C=1=A̅BC|A̅=1&B=1&C=1=11.11(1)1.12A̅+C ̅̅̅̅̅̅̅+D ∙(A +C ̅)(A +B )(B ̅+C )̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅= 1.13(1)F =A (B̅+C +D )(B +D ̅)=ABC +A (B⨀D ) (2)F =A̅⋅B ̅+(AB +AB ̅+A ̅B )C =A ̅⋅B ̅+C (3)F =A +A ⋅B̅⋅C ̅+AC ̅D +(C ̅+D ̅)E =A +C ̅E +D ̅E (4)F =AB̅(C +D )+BC ̅+A ̅∙B ̅+A ̅C +BC +B ̅⋅C ̅⋅D ̅=A ̅+B ̅ (5)F =(A +B )(A +C )(A +C̅)=A (6)F =(A +BC̅)(A ̅+D ̅B)̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅=B ̅+A ̅C +AD (7)F =A (A +B̅+C ̅)(A ̅+C +D )(E +C ̅⋅D ̅)=ACE +ADE 1.14(1)F (A,B,C )=∑m(2,3,6,7)=A BC +A BC +ABC +ABC =B(2)F (A,B,C,D,E )=∏M (0,4,8,12,16,20,24,28)=A ⋅B̅⋅C ⋅D ̅⋅E ̅+A ⋅B ̅⋅C ⋅D ̅⋅E ̅+A ⋅B ⋅C ⋅D ̅⋅E ̅+A ⋅B ⋅C ⋅D ̅⋅E ̅+A ⋅B ̅⋅C ⋅D ̅⋅E ̅+A ⋅B̅⋅C ⋅D ̅⋅E ̅+A ⋅B ⋅C ⋅D ̅⋅E ̅+A ⋅B ⋅C ⋅D ̅⋅E ̅=D ̅E ̅ 1.15(1)F (A,B,C )=∑m (1,3,7)=∏M (0,2,4,5,6)(2)F (A,B,C,D )=∑m(0,2,6,12,13,14)=∏M(1,3,4,5,7,8,9,10,11,15)1.16(1)F (A,B,C )=∏M(0,3,6,7)=∑m(1,2,4,5)(2)F (A,B,C,D )=∏M(0,1,2,3,4,6,12)∑m(5,7,8,9,10,11,13,14,15)1.17(1)F (A,B,C,D )=AB +A̅B ̅+CD ̅=ABC D ̅+ABC D +ABCD ̅+ABCD +A B ̅C D ̅+A B ̅C D +A B̅CD ̅+A B ̅CD +AB ̅CD ̅+A BCD ̅=∑m(0,1,2,3,6,10,12,13,14,15) (2)F (A,B,C )=(A +B )(B̅+C )=∏M(6,7,5,1)=∑m(0,2,3,4) 1.18(1)F (A,B,C )=A ⊕B +AC̅=A B +AB ̅+A C =A BC +A BC +AB ̅C +AB ̅C +A B ̅C +A BC =∑m (2,3,4,5,1)=∏M(0,6,7)(2)F (A,B,C,D )=(A +B̅+C )(A +B ̅)(A +C ̅+D ̅)(B +C ̅+D ̅)=∏M(10,11,8,9,12,4) 1.19(1)F =(AB +A B̅)(C +D )(E +C D ̅)⇒F ̅=A ⊕B +C D ̅+E ̅ (2)F =A +B +C ̅+D +E ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅⇒F ̅=A(B +C ̅+D +E ̅̅̅̅̅̅̅̅)=AB +AC +AD̅E 1.20(1)F =AB +CD +A̅C ⇒F ∗=(A +B )(C +D )(A +C )=A BC +AC +A BD (2)F =A (B̅C +BC ̅)+AC ̅⇒F ∗=(A +(B ̅+C )(B +C ))(A +C )=A +B ̅C (3)F =(A ̅+B)(B +A ̅C)̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅⇒F ∗=A B +B(A +C)̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅=B̅+AC 1.21(1)A ̅⊕B =A ⊕B ̅=A ⊕B ̅̅̅̅̅̅̅̅A̅⊕B =A ̅B ̅+AB =A⨀B A ⊕B̅=AB +A ̅B ̅=A⨀B A ⊕B ̅̅̅̅̅̅̅̅=A⨀B(2)A̅B ̅C +A ̅BC ̅+AB ̅C ̅+ABC =A ⊕B ⊕C A ⊕B ⊕C =(A ̅B +AB ̅)⊕C =(A ̅B +AB ̅)C +(A ̅B +AB̅)̅̅̅̅̅̅̅̅̅̅̅̅̅̅C =A BC +AB ̅C +A B ̅C +ABC (3)AB +BC +CA =(A +B)(B +C)(C +A)(A+B)(B+C)(C+A)=(B+AC)(C+A)=AB+BC+CA (4)AB̅+BC̅+CA̅=A̅B+B̅C+C̅A令:AB̅+BC̅+CA̅=K,K=1或0{A⟶A̅B⟶B̅C⟶C⇒A̅B+B̅C+C̅A=KAB̅+BC̅+CA̅=K=A̅B+B̅C+C̅A1.22(2)1.23(1)F(A,B,C,D)=∏M(1,3,5,7,13,15)=∑m(0,2,4,6,8,9,10,11,12,14)(2)F(A,B,C,D,E)=∏M(0,1,2,3,4,6,8,10,12,13,14)1.24(1)F(A,B,C,D)=∑m(3,5,6,9,12,13,14,15)+∑ϕ(0,1,7)()∑∑(4)F(A,B,C,D,E)=A̅̅̅̅̅̅(5)F(A,B,C,D)=A̅̅̅1.25̅̅12(2)F̅̅12(3)F1(A,B,C,D)=∑m(1,3,4,5,6,7,15)F2(A,B,C,D)=∑m(1,3,10,14,15)12第二章2.1关门电平V off=1.3V:保持电路输出高电平状态所允许的输入低电平的最大值开门电平V on=1.5V:保持电路输出低电平状态所允许的输入高电平的最小值≈1.4V:V off至V on这一段狭窄转折的中值阈值电压VT输入高电平时的抗干扰容限VNH=VOHmin−V on=2.4−1.5=0.9V输入低电平时的抗干扰容限VNL=V off−VOLmax=1.3−0.7=0.6V高电平:V OH(2.4~5.0V),标称值3.6V 低电平:V OL(0~0.7V),标称值0.3V2.2TTL与非门:高电平:V OH(2.4~5.0V),标称值3.6V 低电平:V OL(0~0.7V),标称值0.3V 关门电平V off=1.3V开门电平V on=1.5V阈值电压VT≈1.4V输入高电平时的抗干扰容限VNH=VOHmin−V on=2.4−1.5=0.9V输入低电平时的抗干扰容限VNL=V off−VOLmax=1.3−0.7=0.6V输出低电平的工作状态:N0L=I OLmax(驱动门)I IL(负载门)输出高电平的工作状态:N0H=I OH(驱动门)I IH(负载门)N I≤5V1:输入信号,V0:反相输出信号;V0下降到V m/2相对应于V1上升到V m/2之间的延迟时间称为导通延迟t PLHV0上升到V m/2相对应于V1下降到V m/2之间的延迟时间称为截止延时t PHLt PLH>t PHLt pd=(t PLH+t PHL)/2平均功耗小,速度快不能并联OC门方便线与逻辑,可并联,主要应用(1)实现与或非逻辑(2)电平转换(3)实现数据采集三态与非门(TSL)具有一个使能状态CMOS与非门抗干扰容限低,负载高,速度接近TTL,可并联2.3将与门、与非门的闲置端接1电平,而将或门、或非门闲置端接接0电平。

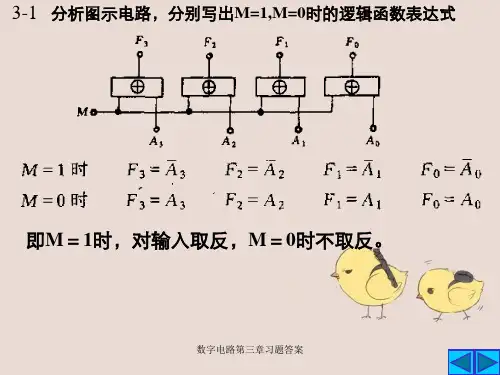

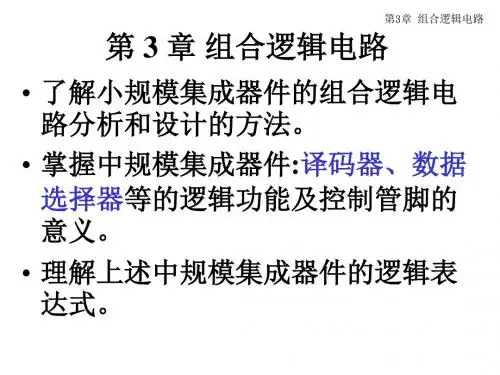

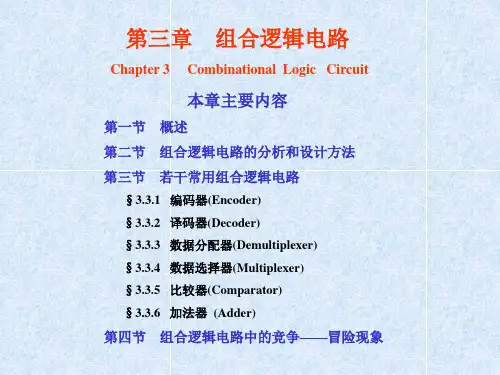

第3章组合逻辑电路3.1 组合逻辑电路的概述按照逻辑功能的不同特点,可以把数字电路分成两大类,一类叫做组合逻辑电路,另一类叫做时序逻辑电路。

什么叫组合逻辑电路呢?在t=a时刻有输入X1、X2、……Zn,那么在t=a时刻就有输出Z1、Z2、……Zm,每个输出都是输入X1、X2、……Zn的函数,Z1=f1(X1、X2、……Xn)Z1=f2(X1、X2、……Xn)Zm=fm(X1、X2、……Xn)从以上概念可以知道组合逻辑电路的特点就是即刻输入,即刻输出。

任何组合逻辑电路可由表达式、真值表、逻辑图和卡诺图等四种方法中的任一种来表示其逻辑功能。

3.2 组合逻辑电路的分析方法和设计方法3.2.1组合逻辑电路的分析方法分析组合逻辑电路的目的,就是要找出电路输入和输出之间的逻辑关系,分析步骤如下:(1)根据已知的逻辑电路,写出逻辑函数表达式(采用逐级写出逻辑函数表达式),最后写出该电路的输出与输入的逻辑表达式。

(2)首先对写出的逻辑函数表达式进行化简,一般系用公式法或卡诺图法。

(3)列出真值表进行逻辑功能的分析。

以上步骤可用框图表示,如图3-2所示。

图3-2 组合逻辑电路分析框图下面举例说明对组合逻辑电路的分析,掌握其基本思路及方法。

【例3-1】 分析图3-3所示电路的逻辑功能图3-3 [例3-1]逻辑电路解:(1)写出输出Z 的逻辑表达式: Z1=B A , Z2=B AZ=21Z Z •=B A B A • (2)化简Z=B A B A •=A B +A B=A ⊕B (3)列出真值表进行逻辑功能说明 列出该函数真值表,如表3.1所示: 表3-1 [例3-1]真值表 A B Z 0 0 0 0 1 1 1 0 1 1 13.2.2组合逻辑电路的设计方法组合逻辑电路的设计步骤与分析步骤相反,设计任务就是根据逻辑功能的要求设计逻辑电路,其步骤如下:(1)首先对命题要求的逻辑功能进行分析,确定哪些是输入变量,哪些为输出函数,以及它们之间的相互逻辑关系,并对它们进行逻辑赋值。

一、分析题:1、试分析如下面图(a )和图(B)所示逻辑电路,说明分别是什么逻辑功能。

(10分).2、(10分)、试分析下图所示逻辑电路。

2B L =11AC&L &=1&3-1、(12分)、分析下图电路的逻辑功能。

要求写出逻辑函数表达式,画出真值表,说明电路的逻辑功能。

3-2(8分)、由译码器74138和8选1数据选择器74151组成如下图所示的逻辑电路。

X 2X 1X 0及Z 2Z 1Z 0为两个三位二进制数,试分析下图电路的逻辑功能。

(74138是3-8线译码器,74151是8选1数据选择器)。

A1&B1&&L≥1≥1≥1≥1LAB(a)(b)5Y 6D 074138D 13401A Y 7G 0Y 13D A 52D Y D A 6G D 1Y Y Y D 274201Y2BD 74151G 2A1A A 02A Y1X 02X X 10Z Z Z 24、(6分)由译码器74138和门电路组成的电路如下图所示,试写出L 1、L 2的最简表达式。

5、6、(12分)、下图所示的TTL 门电路中,要求实现下列规定的逻辑功能时,其连接有无错误?说明正确或错误的理由。

如有错误请改正。

CD AB L ⋅=1 AB L =2 C AB L +=3+V &R PC D&L CCB A 1B&A =1V CCL 2&L 3CB A ≥1(a ) (b) (c)7、(12分)、在下图(a )(b )(c )中,所有的门电路都为TTL 门,设输入A 、B 、C 的波形如图(d )所示,试分析电路的逻辑关系,写出表达式,并定量画出各输出的波形图。

BA =1V CCL 1≥1A 2L BC &≥1EN&△B C1G L 3A &ABC(a)(b)(c)(d)8、(8分)、分析下图所示电路,求输入S 1、S 0各种取值下的输出Y ,填入下表中。

蒋立平版数字逻辑电路与系统设计 第1章习题及解答1.1 将下列二进制数转换为等值的十进制数。

(1) (11011)2(2(10010111)2 (3) (1101101)2(4 (11111111)2 (5) (0.1001)2 (6 (0.0111)2 (7) (11.001)2 (8 (101011.11001)2题1.1 解: (1) (11011)2 =(27)10(10010111)2 =(151)10(3) (1101101)2 =(109)10 (11111111)2 =(255)10(5) (0.1001)2 =(0.5625)10 (0.0111)2 =(0.4375)10(7) (11.001)2 =(3.125)10 (101011.11001)2 =(43.78125)101.3 数。

(1) (1010111)2(110111011)2 (3) (10110.011010)2(4) (101100.110011)2 题1.3 解: (1) (1010111)2=(57)16 =(127)8(2) (110011010)2 =(19A )16 =(632)8 (3) (10110.111010)2 =(16.E8)16 =((4) (101100.01100001)2 =(2C.61)16 =1.5 将下列十进制数表示为8421BCD 码。

(1) (43)10 (95.12)10 (3) (67.58)10 ( (932.1)10题1.5 解:(1) (43)10 =(01000011)8421BC D(2) (95.12)10 =(10010101.00010010)8421BC D (3) (67.58)10 =(01100111.01011000)8421BC D (4) (932.1)10 =(1.7 将下列有符号的十进制数表示成补二进制数。

(1) +13 (2)−9 (3)+3 (4)−题1.7解:(1) +13 =(01101)2 ((10111)2(3) +3 =(00011)2 ((11000)21.9 用真值表证明下列各式相等。