简单8位模型机设计

- 格式:doc

- 大小:373.39 KB

- 文档页数:17

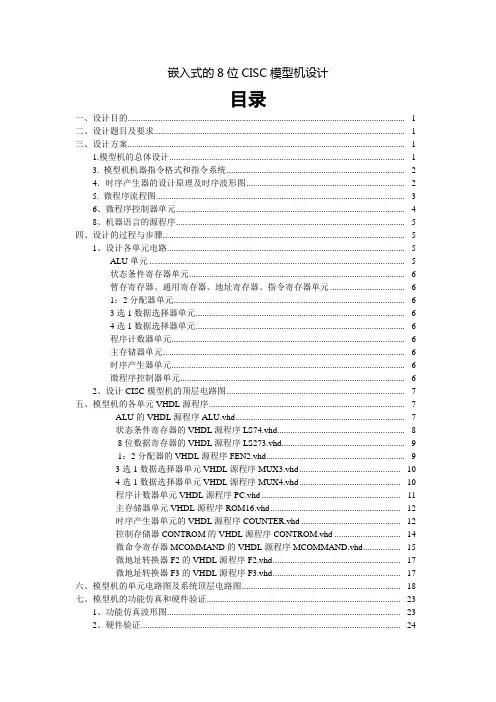

嵌入式的8位CISC模型机设计目录一、设计目的.............................................................................................................................. - 1 -二、设计题目及要求.................................................................................................................. - 1 -三、设计方案.............................................................................................................................. - 1 -1.模型机的总体设计........................................................................................................... - 1 -3. 模型机机器指令格式和指令系统................................................................................. - 2 -4.时序产生器的设计原理及时序波形图........................................................................ - 2 -5. 微程序流程图................................................................................................................. - 3 -6、微程序控制器单元........................................................................................................ - 4 -8、机器语言的源程序........................................................................................................ - 5 -四、设计的过程与步骤.............................................................................................................. - 5 -1、设计各单元电路............................................................................................................ - 5 -ALU单元 .................................................................................................................... - 5 -状态条件寄存器单元.................................................................................................. - 6 -暂存寄存器、通用寄存器、地址寄存器、指令寄存器单元.................................. - 6 -1:2分配器单元......................................................................................................... - 6 -3选1数据选择器单元............................................................................................... - 6 -4选1数据选择器单元............................................................................................... - 6 -程序计数器单元.......................................................................................................... - 6 -主存储器单元.............................................................................................................. - 6 -时序产生器单元.......................................................................................................... - 6 -微程序控制器单元...................................................................................................... - 6 -2、设计CISC模型机的顶层电路图................................................................................. - 7 -五、模型机的各单元VHDL源程序......................................................................................... - 7 ---ALU的VHDL源程序ALU.vhd ............................................................................. - 7 ---状态条件寄存器的VHDL源程序LS74.vhd.......................................................... - 8 --- 8位数据寄存器的VHDL源程序LS273.vhd........................................................ - 9 --- 1:2分配器的VHDL源程序FEN2.vhd ............................................................... - 9 ---3选1数据选择器单元VHDL源程序MUX3.vhd .............................................. - 10 ---4选1数据选择器单元VHDL源程序MUX4.vhd .............................................. - 10 ---程序计数器单元VHDL源程序PC.vhd ............................................................... - 11 ---主存储器单元VHDL源程序ROM16.vhd ........................................................... - 12 ---时序产生器单元的VHDL源程序COUNTER.vhd ............................................. - 12 ---控制存储器CONTROM的VHDL源程序CONTROM.vhd .............................. - 14 ---微命令寄存器MCOMMAND的VHDL源程序MCOMMAND.vhd ................. - 15 ---微地址转换器F2的VHDL源程序F2.vhd .......................................................... - 17 ---微地址转换器F3的VHDL源程序F3.vhd .......................................................... - 17 -六、模型机的单元电路图及系统顶层电路图........................................................................ - 18 -七、模型机的功能仿真和硬件验证........................................................................................ - 23 -1、功能仿真波形图.......................................................................................................... - 23 -2、硬件验证...................................................................................................................... - 24 -八、设计总结............................................................................................................................ - 24 -九、参考文献............................................................................................................................ - 24 -课程设计题目:组成原理课程设计嵌入式的8位CISC模型机设计一、设计目的通过课程设计加深对计算机各功能部件的理解;掌握数据信息流和控制信息流的流动和实现过程,建立起整机概念;培养设计、开发和调试计算机的能力。

基于8位模型机的定点原码一位乘法的实现摘要:本文介绍了基于8位模型机的定点原码一位乘法的实现方法。

首先介绍了定点原码乘法的基本概念,然后详细讲解了实现过程中所需的寄存器、逻辑电路和运算流程,并给出了具体的示例。

最后,对该方法的优缺点进行了讨论,并提出了改进方法。

关键词:定点原码乘法;8位模型机;寄存器;逻辑电路;运算流程;优缺点;改进方法一、引言定点原码乘法是数字电路设计中的基本运算之一,其实现方法多种多样。

本文介绍了基于8位模型机的定点原码一位乘法的实现方法,该方法具有简单、直观、易于理解等优点,适合初学者学习。

二、定点原码乘法的基本概念定点原码乘法是指两个定点数相乘的运算。

定点数是指小数点位置固定的数,一般用二进制表示。

定点数可以分为无符号数和有符号数两种。

无符号数是指没有正负之分的数,而有符号数则包含正负两种情况。

在定点原码乘法中,两个数的小数点位置相同,相乘后的结果的小数点位置也相同。

在计算机中,定点原码乘法通常使用加法器和移位器实现。

三、实现过程1. 寄存器实现定点原码乘法需要使用多个寄存器,主要包括乘数寄存器、被乘数寄存器、积寄存器、进位寄存器等。

乘数寄存器用于存储乘数,被乘数寄存器用于存储被乘数,积寄存器用于存储乘积。

进位寄存器用于存储进位信号,通常为1或0。

2. 逻辑电路实现定点原码乘法需要使用多个逻辑电路,主要包括加法器、移位器、比较器等。

加法器用于实现乘法中的加法操作,移位器用于实现乘法中的位移操作,比较器用于判断乘积是否溢出。

3. 运算流程定点原码乘法的运算流程如下:(1)将乘数和被乘数分别存入乘数寄存器和被乘数寄存器中;(2)将积寄存器清零;(3)按位乘法的规则,将乘数的最低位与被乘数相乘,并将结果加到积寄存器中;(4)将乘数右移一位,被乘数左移一位;(5)重复步骤3和步骤4,直到乘数的所有位数都处理完毕;(6)判断乘积是否溢出,若溢出则进行相应的处理。

4. 示例以乘数为1011,被乘数为1101为例,演示定点原码乘法的实现过程。

东北大学秦皇岛分校计算机与通信工程学院计算机组成原理课程设计专业名称计算机科学与技术班级学号学生姓名指导教师设计时间2014.12.22~2015.1.2课程设计任务书专业:计算机科学与技术学号:学生姓名(签名):设计题目:8位模型机设计-指令系统及通用寄存器设计一、设计实验条件综合楼808实验室二、设计任务及要求总的设计目标是:设计一个8 位的模型机,其组成为:总线结构:单总线,数据总线位数8位、地址总线8位;●存储器:内存容量64K*8bit●控制器:用硬联线控制器实现26位微操作控制信号●运算器:单累加器,实现加、减等8种操作外设:●输入:用开关输入二进制量●输出:7段数码管和LED显示指令系统规模:64 条指令,7种类型,5种寻址方式本组任务是:1.设计12、15、22、32号指令;2.模型机的通用寄存器R1设计;3.BCD编码器的设计。

三、设计报告的内容1.设计题目与设计任务(设计任务书)设计内容如下:1、指令系统设计:ADDC A, #II 将立即数II加入累加器A中带进位SUB A, EM 从A中减去存储器EM地址的值AND A, @R? 累加器A“与”间址存储器的值MOV A, #II 将立即数II送到累加器A中2、模型机硬件设计:通用寄存器R13、逻辑电路设计:BCD码编码器2.前言(绪论)(设计的目的、意义等)1.融会贯通计算机组成原理课程的内容,通过知识的综合运用,加深对计算机系统各个模块的工作原理及相互联系的认识;2.学习运用VHDL进行FPGA/CPLD设计的基本步骤和方法,熟悉EDA的设计、模拟调试工具的使用,体会FPGA/CPLD技术相对于传统开发技术的优点;3.培养科学研究的独立工作能力,取得工程设计与组装调试的实践经验。

3.设计主体(各部分设计内容、分析、结论等)【系统设计】1、模型机逻辑框图图1 模拟机整体逻辑框图图2 XCV200芯片引脚图3 CPU逻辑框图2、指令系统设计:ADDC A, #II 将立即数II加入累加器A中带进位助记符:ADDC A, #II类型:算数运算指令寻址方式:立即数寻址指令格式:第一字节001011XX第二字节立即数:SUB A, EM 从A中减去存储器EM地址的值助记符:SUB A, EM类型:算数运算指令寻址方式:存储器直接寻址指令格式:第一字节001110XX第二字节存储地址:AND A, @R? 累加器A“与”间址存储器的值助记符:AND A, @R?类型:算数运算指令寻址方式:寄存器间接寻址指令格式:第一字节010101XX:MOV A, #II 将立即数II送到累加器A中助记符:MOV A, #II类型:数据传送指令寻址方式:立即数寻址指令格式:第一字节011111XX第二字节立即数3、微操作控制信号:外部设备读信号,当给出了外设的地址后,输出此信号,从指定外设读数据。

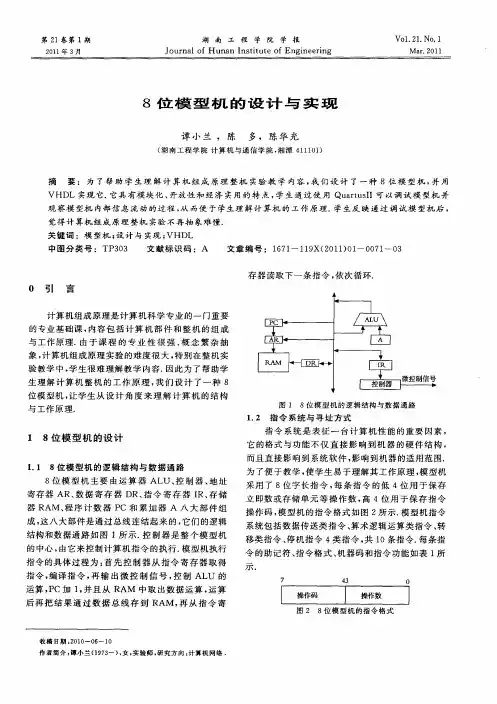

摘要随着计算机在人们生活中重要性和不可或缺性的提高,为了更方便的为大众使用,发展计算机性能成为IT行业的热点,但计算机的部结构极其复杂,为了便于研究便产生了模型计算机。

本文完成了基于VHDL的8位模型计算机的设计与实现。

文中首先阐述了8位模型计算机的原理,然后对其十个功能模块〔算术逻辑运算单元,累加器,控制器,地址寄存器,程序计数器,数据寄存器,存储器,节拍发生器,时钟信号源,指令寄存器和指令译码器进行了分析与设计。

最后在Quartus II 9.0环境下进行了仿真,完成了8位模型计算机的整体实现。

本文综合了计算机组成原理和数字逻辑与系统设计的知识,设计的8位模型计算机能更方便的了解计算机部构造和工作原理。

整个系统的开发体现了在Quartus II软件平台上用VHDL设计数字控制系统的实用性。

关键词:8位模型机; Quartus II ;VHDL语言AbstractWith the improvement of importance and indispensability in computer in people's life,in order to use more conveniently for public ,computer performance is becoming a hot in the IT industry development.but the internal structure of the computer is very complicate,Computer model simplifies the difficulty of the research.This article completed the design and implementation of eight model computer based on VHDL.First ,this article expounds the principle of eight model computer,then divides it into 10 modules<arithmetic logic unit, accumulator, controllers, address register, the program counter and data registers, memory, beat generator, a clock signal, instruction register and instruction decoder>and analyse and design each of them.Finally under the environment of the Quartus II 9.0 simulation, completed overall implementation of the 8 model computer. The analysis and design of the eight model computer integrated the knowledge of computer constitute principle and Digital logic and system design. The design of the eight model computer can be more convenient to understand internal structure and working principle.The whole system development manifests the practicability of designing the numerical control system on the Quartus II software platform with VHDL.Key words:eight model computer ; VHDL language; Quartus II目录1 绪论11.1 本课题研究的目的11.2 本课题研究的背景及意义12 基于VHDL编程的基础知识32.1 VHDL语言概述32.2 VHDL的设计流程 (4)2.3 有关Quartus II 的介绍52.4 本课题基于Quartus II的设计流程73 基于VHDL8位模型机的原理与设计73.1 模型计算机的原理73.2 模型机的总体设计要求83.3 模型机逻辑框图的设计83.3 模型机的指令系统设计83.4 模型机的指令执行流程设计83.5 基于VHDL8位模型机各模块的设计与实现 (10)3.5.1 算术逻辑单元ALU模块103.5.2 累加器模块113.5.3 控制器模块123.5.4 节拍发生器143.5.5 指令寄存器模块IR和指令译码器163.5.6 时钟产生器173.5.7 程序计数器模块183.5.8 地址寄存器MAR203.5.9 存储器RAM213.5.10 数据寄存器DR224 基于VHDL的8位模型计算机的实现234.1 基于VHDL的微程序执行流程图234.2 8位模型机的顶层原理图设计244.3 基于VHDL的8位模型机工作流程244.4 顶层VHDL源程序设计254.4.1 头文件cpu_defs的VHDL设计254.4.2 CPU的VHDL源程序设计264.5 8位模型机的整体实现34结论34致 35参考文献36附录A 英文原文.......................................... 错误!未定义书签。

计算机组成原理课程设计报告130732102015.7. 128位模型机总体结构设计8位模型机数据通路设计8位模型机具体部件设计图时序发生器CLK : 时钟信号HALT: 停机信号m[7..0] : 输出时序信号Timer波形程序计数器CPPC :上升沿控制信号PC1 :PC自加一控制信号PC-BUS :三态门控制BUS[7..0] : 数据输入/输出运算器BUS[7..0] : 数据输入/输出CPSA:A暂存器控制信号CPSB:B暂存器控制信号ALU-BUS :三态门控制CN :运算信号M :运算信号S[3..0] :运算控制信号通用寄存器组BUS[7..0] : 数据输入/输出WE :写入控制信号使能端WA :寄存器写入控制信号WB :寄存器写入控制信号RE:读取控制信号使能端RA:寄存器读取控制信号RB :寄存器读取控制信号主存BUS[7..0] : 数据输入/输出CPMAR : 主存地址写入控制信号WRE :主存写入控制使能端WR :主存写入控制信号RD主存读取控制信号RAM-BUS :三态门控制CPMDR :主存数据写入控制信号总线暂存器BUS[7..0] : 数据输入/输出CPBUS :暂存器输入控制信号OUTBUS:暂存器输出控制信号uPCIR控存8位模型机机器指令设计8位模型机微指令表8位模型机微指令8位模型机模型机调试波形MOV A, 88HMOV B, 66HADD A, BDEC AAND A, BINC AHALTJMP 80h8位模型机指令汇总公共取值(小组共同)MOV A , 88H (小组共同)MOV B , 66H (自己设计)ADD A, B (小组共同)DEC A (自己设计)AND A, B (小组设计)DEC A (自己设计)JMP 80H (小组设计)HALT (小组设计)心得体会在完成了本次课程设计后,我的感触颇多。

首先,我深刻的体会到了计算机结构的复杂性,感受到这门学科的奥妙和趣味,真正的意识到计算机是人类历史上最伟大的发明。

转盘式八工位双圈一体成型电感自动生产机设计

设计目的:

为了提高电感产品的生产效率和质量稳定性,设计一种转盘式八工位双圈一体成型电感自动生产机。

设计方案:

1.设计结构:采用转轴和驱动系统将转盘驱动到不同的工位,每个工位都有自己的成型装置和控制系统。

2.转盘设计:转盘采用八个工位的设计,可以同时完成8个电感的成型工序。

转盘由高强度合金材料制成,确保稳定和耐用。

3.成型装置:每个工位都配备有成型装置,用于将线圈和磁环等部件组装在一起,并通过加热和压力形成电感产品。

成型装置采用高精度的导轨和压力控制系统,确保成型过程的准确性和一致性。

4.控制系统:每个工位都有自己的控制系统,用于控制成型装置的动作和参数设置。

控制系统采用PLC和触摸屏,操作简便,可以实时监控工艺参数和设备状态。

5.送料系统:设计一个自动送料系统,用于定位和供料。

该系统可以根据产品规格自动调整送料位置和速度,确保产品的准确性和一致性。

6.检测系统:设计一个自动检测系统,用于检测电感产品的尺寸和质量。

该系统采用高精度传感器和图像识别技术,可以实时检测产品的尺寸和外观缺陷,并通过控制系统进行报警和处理。

7.故障检测与排除系统:设计一个故障检测与排除系统,用于自动检测和排除生产过程中的故障。

该系统通过监测各个工位的运行状态和传感器的输出,可以判断故障类型,并提供相应的排除方案。

总结:

通过转盘式八工位双圈一体成型电感自动生产机的设计,可以实现电感产品的批量生产和自动化生产。

该设备具有高效率、稳定性好、操作简便等特点,能够提高生产效率和产品质量,减少人工投入和劳动强度,是电感行业的理想选择。

基于FPGA技术的8位模型机设计与实现

张胜;胡建明;蔡虹;付娜

【期刊名称】《南昌航空大学学报(自然科学版)》

【年(卷),期】2010(024)003

【摘要】利用EDA技术在FPGA芯片上设计并实现一个简单的8位模型机,主要包括指令系统、运算器、控制器、存储器、时序产生器和总线等设计,在Quartus Ⅱ6.0集成环境下进行设计、编译和仿真,最后下载到SOPC/EDA实验平台上进行单元和系统测试,达到了设计要求.

【总页数】6页(P21-26)

【作者】张胜;胡建明;蔡虹;付娜

【作者单位】南昌航空大学,江西,南昌,330063;南昌航空大学,江西,南昌,330063;南昌航空大学,江西,南昌,330063;南昌航空大学,江西,南昌,330063

【正文语种】中文

【中图分类】TP368.1

【相关文献】

1.基于FPGA技术的CPU模型机的设计与实现 [J], 周宁宁;刘胜

2.基于VHDL的简易16位模型机设计与实现 [J], 张胜;李方云;曹家庆

3.基于微程序控制模型机的设计与实现 [J], 赵秀娟;詹春;郎长胜;;;

4.基于微程序控制模型机的设计与实现 [J], 赵秀娟;詹春;郎长胜

5.基于CPLD的模型机控制器的设计与实现 [J], 徐丹;耿恒山;张丽纯;李天义;王超

因版权原因,仅展示原文概要,查看原文内容请购买。

华北电力大学实验报告||实验名称 8位模型机的设计课程名称计算机组成与结构||专业班级:成绩:学生姓名:学号:指导教师:实验日期:2015.12.9目录一、摘要...........................................................................................................................................二、前言...........................................................................................................................................三、设计目的、任务与内容...........................................................................................................3.1设计目的..............................................................................................................................根据计算机组成原理课程所学知识,设计一个8位的模型计算机。

................................3.2设计任务..............................................................................................................................3.3设计内容..............................................................................................................................四、八位模型机整体设计...............................................................................................................4.1总体结构..............................................................................................................................4.2指令系统..............................................................................................................................4.3运算器..................................................................................................................................4.4存储器..................................................................................................................................4.5控制器..................................................................................................................................五、实验感想与讨论.......................................................................................................................六、参考文献...................................................................................................................................一、摘要8位模型机采用微程序控制原理。

计算机组成原理

课程设计报告

13073210

2015.7. 12

8位模型机总体结构设计

8位模型机数据通路设计

8位模型机具体部件设计图时序发生器

CLK : 时钟信号

HALT: 停机信号

m[7..0] : 输出时序信号

Timer波形

程序计数器

CPPC :上升沿控制信号

PC1 :PC自加一控制信号

PC-BUS :三态门控制

BUS[7..0] : 数据输入/输出

运算器

BUS[7..0] : 数据输入/输

出

CPSA:A暂存器控制信

号

CPSB:B暂存器控制信

号

ALU-BUS :三态门控制

CN :运算信号

M :运算信号

S[3..0] :运算控制信号

通用寄存器组

BUS[7..0] : 数据输入/输出

WE :写入控制信号使能端

WA :寄存器写入控制信号

WB :寄存器写入控制信号

RE:读取控制信号使能端

RA:寄存器读取控制信号

RB :寄存器读取控制信号

主存

BUS[7..0] : 数据输入

/输出

CPMAR : 主存地址写

入控制信号

WRE :主存写入控

制使能端

WR :主存写入控制

信号

RD主存读取控制信

号

RAM-BUS :三态门

控制

CPMDR :主存数据写入控制信号

总线暂存器

BUS[7..0] : 数据

输入/输出

CPBUS :暂存

器输入控制信

号

OUTBUS:暂存

器输出控制信号

uPC

IR

控存

8位模型机机器指令设计

8位模型机微指令表

8位模型机微指令

8位模型机模型机调试波形

MOV A, 88H

MOV B, 66H

ADD A, B

DEC A

AND A, B

INC A

HALT

JMP 80h

8位模型机指令汇总公共取值(小组共同)

MOV A , 88H (小组共同)MOV B , 66H (自己设计)ADD A, B (小组共同)DEC A (自己设计)

AND A, B (小组设计)DEC A (自己设计)

JMP 80H (小组设计)HALT (小组设计)

心得体会

在完成了本次课程设计后,我的感触颇多。

首先,我深刻的体会到了计算机结构的复杂性,感受到这门学科的奥妙和趣味,真正的意识到计算机是人类历史上最伟大的发明。

我已经能够自己模拟制作出一个简单的8位模型机,深刻的学习到了模型机的工作原理,这是课本所无法提供的一种富有意义的实践。