DSP原理与应用2011-第五章TMS320F28335片(精)

- 格式:doc

- 大小:640.50 KB

- 文档页数:49

T M S320F28335中文资料TMS320F28335中文资料TMS320F28335采用176引脚LQFP四边形封装,其功能结构参见参考文献。

其主要性能如下:高性能的静态CMOS技术,指令周期为6.67 ns,主频达150 MHz;高性能的32位CPU,单精度浮点运算单元(FPU),采用哈佛流水线结构,能够快速执行中断响应,并具有统一的内存管理模式,可用C/C++语言实现复杂的数学算法;6通道的DMA控制器;片上256 Kxl6的Flash存储器,34 Kxl6的SARAM存储器.1 Kx16 OTPROM和8 Kxl6的Boot ROM。

其中Flash,OTPROM,16 Kxl6的SARAM均受密码保护;控制时钟系统具有片上振荡器,看门狗模块,支持动态PLL调节,内部可编程锁相环,通过软件设置相应寄存器的值改变CPU的输入时钟频率;8个外部中断,相对TMS320F281X系列的DSP,无专门的中断引脚。

GPI00~GPI063连接到该中断。

GPI00一GPI031连接到XINTl,XINT2及XNMI外部中断,GPl032~GPI063连接到XINT3一XINT7外部中断;支持58个外设中断的外设中断扩展控制器(PIE),管理片上外设和外部引脚引起的中断请求;增强型的外设模块:18个PWM输出,包含6个高分辨率脉宽调制模块(HRPWM)、6个事件捕获输入,2通道的正交调制模块(QEP);3个32位的定时器,定时器0和定时器1用作一般的定时器,定时器0接到PIE模块,定时器1接到中断INTl3;定时器2用于DSP/BIOS的片上实时系统,连接到中断INTl4,如果系统不使用DSP/BIOS,定时器2可用于一般定时器;串行外设为2通道CAN模块、3通道SCI模块、2个McBSP(多通道缓冲串行接口)模块、1个SPI模块、1个I2C主从兼容的串行总线接口模块;12位的A/D转换器具有16个转换通道、2个采样保持器、内外部参考电压,转换速度为80 ns,同时支持多通道转换;88个可编程的复用GPIO引脚;低功耗模式;1.9 V内核,3.3 V I/O供电;符合IEEEll49.1标准的片内扫描仿真接口(JTAG);TMS320F28335的存储器映射需注意以下几点:片上外设寄存器块0~3只能用于数据存储区,用户不能在该存储区内写入程序。

DSP原理与应用The Technology & Applications of DSP北京交通大学电气工程学院郝瑞祥haorx@本页已使用福昕阅读器进行编辑。

福昕软件(C)2005-2009,版权所有,仅供试用。

§7.1F28335的PWM控制●每个ePWM模块都支持下列特性:●精确的16位时间定时器,可以进行周期和频率控制。

●两个PWM输出(EPWMxA and EPWMxB) 可以用于下面的控制●–两个独立的PWM输出进行单边控制●–两个独立的PWM输出进行双边对称控制●–一个独立的PWM输出进行双边非对称控制●与其它ePWM模块有关的可编程超前和滞后相控。

●在一个循环基础上的硬件锁定(同步)相位关系。

●独立的上升沿和下降沿死区延时控制●可编程控制故障区(trip zone)用于故障时的周期循环控制(trip)和单次(one-shot)控制.●一个控制条件可以使PWM输出强制为高,低,或高阻逻辑电平.●所有事件都可以触发CPU中断,启动ADC开始转换。

●可编程事件有效降低了在中断时CPU的负担。

●PWM高频载波信号对于脉冲变压器门极驱动非常有用。

本页已使用福昕阅读器进行编辑。

福昕软件(C)2005-2009,版权所有,仅供试用。

多个ePWM模块结构框图ePWM模块的子模块和信号连接模块相关信号说明如下:●PWM 输出信号(EPWMxA and EPWMxB) (x=1…6)●通过IO引脚输出PWM信号.●Trip-zone 信号(TZ1 to TZ6).这些输入信号警告ePWM模块有外部故障发生。

设备的每个模块都可以配置成使用或者忽略任何故障区信号(Trip-zone)。

这些信号可以设置为通用IO外设的异步输入。

●基于时间的同步输入信号(EPWMxSYNCI)和输出(EPWMxSYNCO)信号.同步信号雏菊花形将ePWM模块连接在一起。

每个模块可以配置成使用或忽略其同步输入信号。

DSP原理与应用The Technology & Applications of DSPs 第六讲TMS320F28335片内外设---CAN,SPI北京交通大学电气工程学院夏明超郝瑞祥万庆祝mchxia@haorx@qzhwan@TMS320F28335---CAN,SPI 第六讲片内外设,教学目标:掌握TMS320F28335芯片现场总线CAN通信接口,SPI串行外设接口通信相关知识;教学重点:掌握TMS320F28335芯片常用串行通信接口的特点和应用.教学难点:现场总线CAN通信编程及应用.教学内容:第一节:TMS320F28335系列SPI通信接口第二节: TMS320F28335系列CAN总线通信接口6.1.1 TMS320F2833x SPI§6S30833系列S通信SPI模块的主要特点:◆四个外部引脚SPISOMI: SPI slave-output/master-input pinSPISIMO: SPI slave-input/master-output pinSPISTE: SPI slave transmit-enable pinSPISTE:SPI slave transmit enable pinSPICLK: SPI serial-clock pin◆两个可编程模式: 主(master)和从(slave)◆125种可编程波特率设置.◆数据长度1至16位.◆四种时钟模式◆接收和发送可同时操作◆12个SPI模块控制寄存器◆增强特性16级发送/接收FIFO;延时传输控制.SPI 模块C PU 接口SPI 模块内部结构框图§6.1.2 典型SPI主/从通信连接模式一) (MASTER)()主模式()在该模式下(MASTER/SLAVE = 1), SPI模块通过SPICLK引脚提供整个串行通信网络的时钟. 数据通过SPISOMI引脚接收. SPIBRR寄存器决定网络上发送和接收的波特率。

TMS320F28335串口通信实验实验目的:掌握TMS320F28335串口的使用;实现功能:1、与电脑232 接口通讯,波特率9600 8N1;2、电脑发送数据,开发板原数据返回;基础知识:TMS320F28335的3个功能相同的SCIA、SCIB、SCIC模块,都可以看做是UART串口;每个串口各有一个接收器、一个发送器。

接收器和发送器各有一个16级深度的FIFO,他们都还有自己的使能和中断位。

若要使SCI模块工作,DSP需要做如下设置:◆使用GPIOMUX寄存器将对于的GPIO设置为SCIx功能;◆将sysclkout经过低速预定标器之后输出低速时钟LSPCLK供给SCIx;◆使能SCIx相关时钟,即PCLKCR寄存器中的SCIxENCLK置1;◆通信格式、波特率、需要用到FIFO的情况,可以使能FIFO、使能中断等;实现步骤:1、初始化串口IO引进为串口功能;开发板串口连接图,如上图,XRnW为SCITXDA、GPIO35复用引脚;XZCS0n为SCIRXDA、GPIO36复用引脚;2、设置串口相关寄存器、波特率等;3、设置串口中断接收函数;4、设置串口查询发送函数;遇到的问题:1、中断发生后,要记得清PIEACK中断响应寄存器,否则只中断一次,以后再也不进入中断了,串口中断在读数据后会自动清中断标志。

每个外设中断响应后,一定要对PIEACK的相关位进行软件复位,否则同组内的其他中断都不会被响应。

2、了解SCI功能应参考《MS320x2833x, 2823x Serial Communications Interface (SCI)》3、串口端口IO设置成内部上拉、Rx端还应设为异步输入;具体SCI部分程序如下:/** ======= sci_uart ========*** Created on: 2017年9月19日* Author: liu*/#include"DSP2833x_Device.h"// DSP2833x Header File#include"DSP2833x_Examples.h"// DSP2833x Examples Include File#include"sci_uart.h"__interrupt void sciaRxIsr(void);/** ======== sci_uart_init ========*/void SCIA_uart_init(void){//GPIO35、36复用功能选择EALLOW;GpioCtrlRegs.GPBMUX1.bit.GPIO35 = 1 ; //SCIA_TXDAGpioCtrlRegs.GPBMUX1.bit.GPIO36 = 1 ; //SCIA_RXDAGpioCtrlRegs.GPBPUD.bit.GPIO35 = 0; // Enable pull-up for GPIO29 (SCITXDA)GpioCtrlRegs.GPBPUD.bit.GPIO36 = 0; // Enable pull-up for GPIO28 (SCIRXDA)//定义管脚为异步输入GpioCtrlRegs.GPBDIR.bit.GPIO36 = 0 ;//输入GpioCtrlRegs.GPBQSEL1.bit.GPIO36 = 3;//异步输入EDIS;//基本通信参数设置// Note: Clocks were turned on to the SCIA peripheral// in the InitSysCtrl() functionSciaRegs.SCICCR.all =0x0007; // 1 stop bit, No loopback// No parity,8 char bits,// async mode, idle-line protocolSciaRegs.SCICTL1.all =0x0003; // enable TX, RX, internal SCICLK,// Disable RX ERR, SLEEP, TXWAKESciaRegs.SCICTL2.all =0x0003;SciaRegs.SCICTL2.bit.TXINTENA =0; //查询发送SciaRegs.SCICTL2.bit.RXBKINTENA =1;//中断接收SciaRegs.SCIHBAUD=488>>8;// 9600 135MHz@LSPCLK = 33.75MHz /(9600*8)-1=4394 150MHz@LSPCLK = 37.5MHz /(9600*8)-1=488SciaRegs.SCILBAUD=488;SciaRegs.SCICTL1.all =0x0023; // Relinquish SCI from Reset// Initialize the SCI FIFO 禁止FIFO功能SciaRegs.SCIFFTX.bit.SCIFFENA = 0 ; //禁止SCI FIFO功能EALLOW;// This is needed to write to EALLOW protected registersPieVectTable.SCIRXINTA = &sciaRxIsr;EDIS;// This is needed to disable write to EALLOW protected registersPieCtrlRegs.PIEIER9.bit.INTx1=1;// PIE Group 9, int1IER |= M_INT9;// Enable CPU INTEINT;}void SCIA_UART_Send_Byte( unsigned char Dat){while(SciaRegs.SCICTL2.bit.TXRDY !=1);//等待SCIRXBUF准备好才写入下一个所要发送的数据SciaRegs.SCITXBUF = Dat;}//SCIA串口中断接收处理函数__interrupt void sciaRxIsr(void){if(SciaRegs.SCIRXST.bit.RXRDY == 1){SCIA_UART_Send_Byte( SciaRegs.SCIRXBUF.bit.RXDT );}PieCtrlRegs.PIEACK.all=PIEACK_GROUP9;}。

作为一个电子硬件工程师,怎么不能懂DSP,或者我们中有一些同学对DSP的理解还不是很多,今天就让我们给大家介绍一个DSP的入门芯片,来自TI的TMS320F28335。

相信看过了这一系列的内容,大家会对DSP有初步的了解。

TMS320F28335简介:TMS320F28335采用176引脚LQFP四边形封装,其功能结构参见参考文献。

其主要性能如下:高性能的静态CMOS技术,指令周期为6.67 ns,主频达150 MHz;高性能的32位CPU,单精度浮点运算单元(FPU),采用哈佛流水线结构,能够快速执行中断响应,并具有统一的内存管理模式,可用C/C++语言实现复杂的数学算法;6通道的DMA控制器;片上256 Kxl6的Flash存储器,34 Kxl6的SARAM存储器.1 Kx16 OTPROM和8 Kxl6的Boot ROM。

其中Flash,OTPROM,16 Kxl6的SARAM均受密码保护;控制时钟系统具有片上振荡器,看门狗模块,支持动态PLL调节,内部可编程锁相环,通过软件设置相应寄存器的值改变CPU的输入时钟频率;8个外部中断,相对TMS320F281X系列的DSP,无专门的中断引脚。

GPI00~GPI063连接到该中断。

GPI00一GPI031连接到XINTl,XINT2及XNMI外部中断,GPl032~GPI063连接到XINT3一XINT7外部中断;支持58个外设中断的外设中断扩展控制器(PIE),管理片上外设和外部引脚引起的中断请求;增强型的外设模块:18个PWM输出,包含6个高分辨率脉宽调制模块(HRPWM)、6个事件捕获输入,2通道的正交调制模块(QEP);3个32位的定时器,定时器0和定时器1用作一般的定时器,定时器0接到PIE模块,定时器1接到中断INTl3;定时器2用于DSP/BIOS的片上实时系统,连接到中断INTl4,如果系统不使用DSP/BIOS,定时器2可用于一般定时器;串行外设为2通道CAN模块、3通道SCI模块、2个McBSP(多通道缓冲串行接口)模块、1个SPI模块、1个I2C主从兼容的串行总线接口模块;12位的A/D转换器具有16个转换通道、2个采样保持器、内外部参考电压,转换速度为80 ns,同时支持多通道转换;88个可编程的复用GPIO引脚;低功耗模式;1.9 V内核,3.3 V I/O供电;符合IEEEll49.1标准的片内扫描仿真接口(JTAG);TMS320F28335的存储器映射需注意以下几点:片上外设寄存器块0~3只能用于数据存储区,用户不能在该存储区内写入程序。

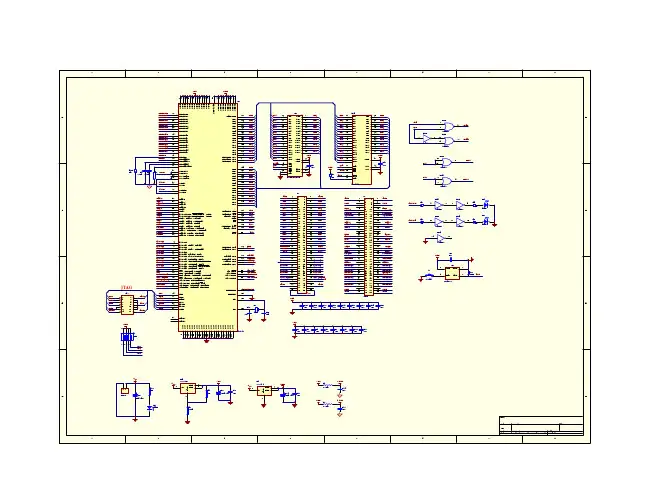

TMSF28335在控制系统中的实际应用1.基本原理图:2.硬件设计:1,在F28335型号的DSP芯片内没有集成D/A转换器,如果需要运用D/A转换的功能,可以通过XINTF接口扩展并行接口的D/A转换芯片,或者通过SPI接口扩展串行接口的D/A 转换芯片,此处采用到的XINTF接口并行扩展的D/A转换芯片。

TMS320F28335的外部接口映射到3块固定的存储空间:Zone 0、Zone 6、Zone 7,当访问外部接口的存储空间时,与该存储空间对应的片选信号XZCS0、XZCS6、XZCS7变为有效的低电平,本题目中采用Zone 7对应的外部接口存储空间,其起始地址为0X200000~0X2FFFFF,对应的外部接口的片选信号为XZCS7,并采用GPIOA1和GPIOA2(I/O功能)为D/A芯片提供功能使能信号。

2,DSP芯片与D/A之间的数据线由GPIO的C口提供(复用C口的GPIO68~GPIO79的数据数据传输功能)。

3,对于输入一阶惯性环节的信号,按阶跃信号进行处理,由自动控制原理可以得,其响应信号为:其中τ为时间常数,当t=3τ时,响应达到稳态值的95%,作为最终的输出响应。

硬件连接图3.软件控制编程:实现功能:AD采样+PI调节+一阶惯性/*****************head file********************/#include "DSP2833x_Device.h"#include "DSP2833x_Examples.h"/****************macro*****************/#define S1 AdcRegs.ADCST.bit.INT_SEQ1/***************global variable************/float this_zl;float upon_zl;int PIn=0; //symbol parameterint SCn=0; // symbol parameterfloat adclo=0; //AD referenced voltagefloat adcres=65536;float Ta; //一阶系统时间常数float temp=0.950213;int sc_D;float mf_scz;float mf_sc; //outputunsigned int * Sda;float power_set;float power_get; // actual output voltagefloat KP_wr; //PI proportion coefficientfloat KI_wr; //PI integral coefficientfloat error_sg; //PI correlative parameterfloat error_1;float error_2;/****************function*******************/interrupt void cpu_timer0_isr(void);interrupt void ad_isr(void);void Init_Timer0(void);void Init_Xintf(void);void Init_Gpio(void); //GPIO initialization program void Initadc(void); //AD initializefloat PI_T(float power_sd,float pow_in); //PI control functionvoid delay_ys(void); //delay subprogram/***************main function**********************/void main(void){unsigned int * Sda =(unsigned int *) 0x200000; //define DA address,XINTF Zone7 InitSysCtrl(); // initialize system subprogramInit_Timer0();DINT;InitPieCtrl();IER=0x0000;IFR=0x0000;InitPieVectTable();Init_Gpio();Initadc();Init_Xintf();CpuTimer0Regs.TCR.bit.TIE=1;EALLOW; // 解除寄存器保护PieVectTable.TINT0=&cpu_timer0_isr; //用CUP_Timer0中断函数入口更新//PIE向量表PieVectTable.ADCINT=&ad_isr; //用AD中断函数更新PIE向量表EDIS; //使能寄存器保护ConfigCpuTimer(&CpuTimer0,150,500); //timing 500usStartCpuTimer0();PieCtrlRegs.PIEIER1.all=0x60; //使能PIE内的CUP_Timer0和AD//中断IER |=0x0001; // 使能CPU INT 1EINT;}*****************CPU timer initialization***********************************void Init_Timer0(void){CpuTimer0Regs.PRD.all=75000; //set timer period timing:500usCpuTimer0Regs.TPR.all=0;CpuTimer0Regs.TPRH.all=0;//CpuTimer0Regs.TCR.bit.TSS=1; //stop timer}********************A/D initialization**********************************void Initadc(void){long i; //AD initializeAdcRegs.ADCTRL1.bit.RESET=1;for(i=0;i<100;i++) {};AdcRegs.ADCTRL1.bit.RESET=0;AdcRegs.ADCTRL1.bit.SUSMOD=0;AdcRegs.ADCTRL1.bit.ACQ_PS=0; //setting sample windowAdcRegs.ADCTRL1.bit.CPS=0;AdcRegs.ADCTRL1.bit.CONT_RUN=0; //启动-停止模式AdcRegs.ADCTRL1.bit.SEQ_CASC=0; //AdcRegs.ADCTRL3.bit.ADCBGRFDN=3; //给ADC模块的内部基准电路上电for(i=0;i<400000;i++) {}; //delay more than 7msAdcRegs.ADCTRL3.bit.ADCPWDN=1; //给ADC模块的其余模拟电路上电for(i=0;i<10000;i++) {}; //delay more than 20usAdcRegs.ADCTRL3.bit.ADCCLKPS=10;AdcRegs.ADCTRL3.bit.SMODE_SEL=0; //choose sample styleAdcRegs.ADCMAXCONV.all=0x0000;AdcRegs.ADCCHSELSEQ1.bit.CONV00=0x0000;AdcRegs.ADCST.bit.INT_SEQ1_CLR=1;AdcRegs.ADCTRL2.bit.RST_SEQ1=1; //复位排序器1AdcRegs.ADCTRL2.bit.INT_ENA_SEQ1=1; //SEQ1 interruptAdcRegs.ADCTRL2.bit.INT_MOD_SEQ1=0; //choose interrupt style}*********************external peripherals initialization****************************** void Init_Xintf(void){EALLOW;XintfRegs.XINTCNF2.bit.XTIMCLK=1;XintfRegs.XTIMING6.bit.XWRLEAD=3;XintfRegs.XTIMING6.bit.XWRACTIVE=7;XintfRegs.XTIMING6.bit.XWRTRAIL=3;XintfRegs.XTIMING6.bit.XRDLEAD=3;XintfRegs.XTIMING6.bit.XRDACTIVE=7;XintfRegs.XTIMING6.bit.XRDTRAIL=3;XintfRegs.XTIMING6.bit.X2TIMING=0;EREADY=0;XintfRegs.XTIMING6.bit.XSIZE=3;EDIS;}********************************I/O initialization*******************************void Init_Gpio(void){EALLOW; //GPIO initializeGpioCtrlRegs.GPBMUX1.all=0xFFFFFC00; //设置B口为地址线以及DAC片选信号GpioCtrlRegs.GPCMUX1.all=0xFFFFFFFF; //set C Port as date addressGpioCtrlRegs.GPAMUX1.all=0x0000;GpioCtrlRegs.GPADIR.all= 0x0003;GpioDataRegs.GPADA T.all= 0x0003;GpioDataRegs.GPACLEAR.all= 0x0003; //choose GPIO1,2 as DA signal address EDIS;}****************************PI function****************************************** portal parameter:power_sd and pow_inexport parameter:this_zlfloat PI_T(float power_sd,float power_in){error_1 = error_sg;error_sg = power_sd - power_in;error_2 = error_sg - error_1;if(PIn == 0){error_2 = 4.0; //avoid error_2 too largePIn++;}this_zl = KP_wr*error_sg + KI_wr*error_2;error_sg = error_1;return this_zl;}*******************************Delay function*********************************** void delay_ys(void){long i;for(i=0;i<100000;i++) {};}*************************timer 0 interrupt deal function***********************interrupt void cpu_timer0_isr(void){DINT;StopCpuTimer0();CpuTimer0Regs.TCR.bit.TIF=1; //清CPU定时器0的中断标志PieCtrlRegs.PIEACK.all |=0x0001; //使能第一组中断以使AD产生的中断能// 被CPU响应AdcRegs.ADCTRL2.bit.SOC_SEQ1=1; //使能排序器,启动AD转换EINT;while(S1==0) {}; //等待AD转换的完成delay_ys();}************************AD interrupt function*********************************interrupt void ad_isr(void){DINT;AdcRegs.ADCTRL2.bit.RST_SEQ1=1;power_get=((float)AdcRegs.ADCRESULT0)*3.0/adcres + adclo; //对采样数据进行转换if(SCn == 0){mf_scz = 2.5;SCn++;}mf_sc=mf_scz;upon_zl=PI_T( power_get, mf_sc); //调用PI环节的函数mf_sc=1/Ta * upon_zl * temp; //通过一阶惯性环节的处理delay_ys();mf_scz=mf_sc;sc_D=(int)(mf_sc * 4096)/5;* (Sda) = sc_D; //写数据到DA的数据线AdcRegs.ADCST.bit.INT_SEQ1_CLR=1;PieCtrlRegs.PIEACK.all |=0x0001; //使能第一组中断EINT;StartCpuTimer0(); //启动定时器0,开始下一次采样}。

TMS320F28335中⽂资料资料讲解T M S320F28335中⽂资料TMS320F28335中⽂资料TMS320F28335采⽤176引脚LQFP四边形封装,其功能结构参见参考⽂献。

其主要性能如下:⾼性能的静态CMOS技术,指令周期为6.67 ns,主频达150 MHz;⾼性能的32位CPU,单精度浮点运算单元(FPU),采⽤哈佛流⽔线结构,能够快速执⾏中断响应,并具有统⼀的内存管理模式,可⽤C/C++语⾔实现复杂的数学算法;6通道的DMA控制器;⽚上256 Kxl6的Flash存储器,34 Kxl6的SARAM存储器.1 Kx16 OTPROM和8 Kxl6的Boot ROM。

其中Flash,OTPROM,16 Kxl6的SARAM均受密码保护;控制时钟系统具有⽚上振荡器,看门狗模块,⽀持动态PLL调节,内部可编程锁相环,通过软件设置相应寄存器的值改变CPU 的输⼊时钟频率;8个外部中断,相对TMS320F281X系列的DSP,⽆专门的中断引脚。

GPI00~GPI063连接到该中断。

GPI00⼀GPI031连接到XINTl,XINT2及XNMI外部中断,GPl032~GPI063连接到XINT3⼀XINT7外部中断;⽀持58个外设中断的外设中断扩展控制器(PIE),管理⽚上外设和外部引脚引起的中断请求;增强型的外设模块:18个PWM输出,包含6个⾼分辨率脉宽调制模块(HRPWM)、6个事件捕获输⼊,2通道的正交调制模块(QEP);3个32位的定时器,定时器0和定时器1⽤作⼀般的定时器,定时器0接到PIE模块,定时器1接到中断INTl3;定时器2⽤于DSP /BIOS的⽚上实时系统,连接到中断INTl4,如果系统不使⽤DSP/BIOS,定时器2可⽤于⼀般定时器;串⾏外设为2通道CAN模块、3通道SCI模块、2个McBSP(多通道缓冲串⾏接⼝)模块、1个SPI模块、1个I2C主从兼容的串⾏总线接⼝模块;12位的A/D转换器具有16个转换通道、2个采样保持器、内外部参考电压,转换速度为80 ns,同时⽀持多通道转换;88个可编程的复⽤GPIO引脚;低功耗模式;1.9 V内核,3.3 V I/O供电;符合IEEEll49.1标准的⽚内扫描仿真接⼝(JTAG);TMS320F28335的存储器映射需注意以下⼏点:⽚上外设寄存器块0~3只能⽤于数据存储区,⽤户不能在该存储区内写⼊程序。

DSP控制器原理及应用课程报告基于TMS320F28335的步进电机控制小组成员:指导教师:2016年12月组员分工目录1 绪论 (1)1.1课题提出的背景 (1)1.2 DSP 的发展及应用 (2)1.3 本课题主要工作 (3)2步进电动机的选择及其驱动控制 (5)2.1 步进电动机概述 (5)2.1.1步进电动机分类 (5)2.1.2 步进电机的步距角 (5)2.1.3 步进电机的相数 (7)2.2 步进电动机的选择 (7)2.3 步进电动机的驱动 (8)2.3.1 驱动系统的组成 (8)2.3.2 驱动器的特点 (9)2.4 驱动器的选择 (10)2.4.1 L297/L298 芯片的介绍 (10)2.4.2 L297 芯片的工作原理 (10)2.4.3 驱动硬件的体系结构 (11)3 系统硬件设计 (11)3.1 DSP 系统的设计流程 (11)3.2 DSP 控制器件的基本结构和特征 (12)3.3 TMS320LF2407 的内部结构及组成 (15)3.3.1 芯片的选型 (15)3.3.2 MS3T20LF2407 芯片体系结构围设备。

(15)3.4 步进电机的DSP 控制 (17)3.4.1 芯片在电机控制中的应用 (17)3.4.2 步进电机的DSP 控制原理 (17)3.5 系统硬件设计说明 (19)3.5.1 时钟电路设计 (19)3.5.2 复位电路设计 (20)3.5.3 外部存储器设计 (21)3.5.4 JTAG 仿真 (22)3.5.5 电源模块 (23)3.5.6 按键接口设计电路 (23)3.5.7 隔离电路 (23)4 控制系统软件部分的设计 (25)4.1 软件设计的基本思想 (25)4.2 主程序设计与分析 (26)4.3 系统初始化程序 (26)4.3.1 变量初始化 (27)4.3.2 系统初始化 (28)4.3.3 I/O 口初始化 (28)4.3.4 PWM 初始化 (28)4.4 键盘扫描和服务程序 (28)4.5 中断服务程序 (28)5 实验结果分析 (31)5.1 实物图 (31)5.2 实验结果及其分析 (32)6 心得体会和工作总结 (33)摘要摘要电动机控制是工业自动化进程中一个相当重要的组成部分,随着工业自动控制对电动机控制产品需求的不断增加,现代电动机控制技术也变得越来越重要,微处理器已经广泛用于电动机控制领域。

DSP 原理与应用The Technology & Applications of DSPs第五章: TMS320F28335片内外设北京交通大学电气工程学院夏明超郝瑞祥万庆祝***************.cn**************.cn**************.cn:TMS320F28335第五讲: TMS320F28335片内外设教学目标:掌握TMS320F28335内核结构,例如A/D转换、串行通信接口、串行外设接口。

外设接重点:TMS320F28335A/DCS308335内部/C 的正确使用,串行通信接口应用。

难点:TMS320F28335的ADC 寄存器操作和串行通信寄存器操作。

教学内容分两部分51§5.1:TMS320F28335内模拟/数字转换§5.2 :TMS320F28335系列串行通信接口SCI 和Modbus 协议介绍DSP 原理与应用2DSP原理与应用3 ADC 有关引脚§5.1 TMS320F28335内模拟/数字转换§5.1 .1Features and functions of ADC module:◆core with built-in dual sample-and-hold◆Simultaneous sampling or sequential sampling modesp g q p g ◆Analog input: ◆Fast conversion time runs at ADC clock orFast conversion time runs at , ADC clock, or 6.25 MSPSmultiplexed inputs◆, multiplexed inputs◆capability provides up to 16 " t i " i i l i E h i "autoconversions" in a single session. Each conversioncan be to select any 1 of 16 input channels.DSP 原理与应用4Sequencer can be operated as two independent 8-state ◆Sequencer can be operated as two independent 8-state sequencers or as one large 16-state sequencer (i.e., two cascaded 8-state sequencerstwo cascaded 8state sequencers.◆(individually addressable to store conversion values store conversion valuesA/DC digital value:DSP 原理与应用2012年9月3日5◆for the start-of-conversion sequence–S/W -software immediate start–ePWM 1-6–GPIO XINT2◆allows interrupt request on every end-of-sequence (EOS or every other EOSy q ( y◆Sequencer can operate in mode, allowing multiple "time-sequenced triggers" to synchronize p q gg yconversions.Sample-and-hold (S/Hacquisition time window has ◆Sample and hold (S/H acquisition time window has separateA/DC模块框图(Block diagram of A/DC Module)§5.1. 2ADC 有关的寄存器控制寄存器通道顺序选择寄存器结果寄存器ADC有关的寄存器(序)控制寄存器状态寄存器参考电压选择寄存器偏移电压调整寄存器§5.1.3 ADC操作模式1 顺序采样模式(Sequential Sampling Mode)根据采样模式划分,包括顺序采样和同步采样2同步采样模式(Simultaneous Sampling Mode)DSP 原理与应用2012年9月3日11根据转换模式划分,包括:级联模式转换和和双序列模式转换1)级联模式转换DSP 原理与应用2012年9月3日122)双序列模式转换DSP 原理与应用2012年9月3日13 单序列模式和级联模式对比DSP 原理与应用2012年9月3日14§5.1.4 ADC电压参考默为使用内部电压参考也以使用外部电压参考允许值为●默认为使用内部电压参考,也可以使用外部电压参考,允许值为2.048V ,1.5V 和1.024V 。

通过寄存器选择参考源如果选择内部参考源●ADCREFSEL 寄存器选择参考源,如果选择内部参考源,ADCREFIN 引脚可以连接选择的参考源、悬空或接地。

如果使用外部2.048V 的参考源,推荐使用工业级REF3020AIDBZ 芯片。

DSP 原理与应用2012年9月3日15§5.1.5 ADC模块时钟ADC 模块有多个时钟定标模式,与其有关的信号即寄存器有外部时钟源XCLKIN ,ADCTRL3寄存器ADCLKPS[3-0], ADCTRL1寄存器CPS 位等。

§5.1.6 ADC运行模式1)非中断自动顺序模式(Uninterrupted Autosequenced Mode)如果ADCTRL1寄存器的CONT_RUN位设为1, ADC工作在连续运行模式。

假设期望SEQ1中7个通道,如ADCINA2,ADCINA3重复两次,ADCINA6, ADCINA7, ADCINB4顺序采样,则MAC_CONV1应设为6,ADCCHSELSEQn 寄存器应按下图配置存器应按下图配置。

有信号位这些通道将按照一旦有SOC 信号,SOC 触发被装入SEQ_CNTR位,这些通道将按照ADCCHSEQn 中预先配置的转换顺序进行转换。

SEQ_CNTR位每转换一次自动减一,一旦SEQ CNTR 减到零,将从新开始下一轮转换(CONT RN=1)。

动减_减到零将从新开始下轮转换_2)顺序启/停模式(Sequencer Start/Stop Mode)如果ADCTRL1寄存器的CONT_RUN位设为0, 则ADC 工作在顺序启/停模式。

假设期望事件一启动I1,I2,I3转换,事件二启动V1,V2,V3转换,而且两个触发则MAX CONV1事件之间时间间隔为25uS 。

则MAX_CONV1应设置为2,ADCCHSELSEQn 配置如下:一旦复位和初始化寄存器,SEQ1将等待第一个触发事件的到来,然后开始CONV00(I1, CON01(I2,CONV02(I3 转换,本次转换完成后,SEQ1在当前状态等待下一个触发事件的到来,然后再开始CONV03(V1,CON04(V2, CONV05(V3。

两次转换中MAX_CONV1值都自动装入SEQ_CNTR,如果两次转换的通道数不一致,则应在下次转换开始之前的适当时刻修改MAX_CONV1的值。

可以通过ADCTRL2中的RST_SEQn来复位序列到预启动状态。

517ADC §5.1.7 ADC采样校准ADC cal(子程序在芯片出厂时已经固化在OPT 存储器中。

BOOT _(子程序片厂固化存储中ROM 自动调用该子程序,初始化ADCREFSEL 和ADCOFFTRIM 寄存器。

在正常操作时,该过程不需要用户操作而自动完成。

如果在开发阶段,BOOT ROM被CCS 旁路,则ADCREFSEL 和ADCOFFTRIM 寄存器必须在应用程序中初始化。

如果该寄存器初始化失败或不正确,将降低精度。

由于TI 存储器被安全保护因此ADC l(TI 保留的OTP 存储器被安全保护,因此ADC_cal(子程序必须在安全存储区内调用或者在安全模块被解锁后的非安全存储区调用。

如果系统被复位或者ADC 模块被ADC 控制寄存器ADCTRL1中的BIT14(RESET复位,则该校准子程序必须从新执行。

5.1.8 ADC上电次序§电次序ADC 模块复位时,进入关闭状态。

如果要使用ADC 给其上电,需要根据如下步骤进行:(1 如果使用外部参考信号,可用寄存器ADCREFSEL 的第15-14位选择外部参考模式。

在带隙上电之前必须配置该模式,以避免内部参考电路驱动外部参考源。

(2)通过设置控制寄存器ADCTRL3的位7-5(ADCBGRFDN[1:0],ADCPWDN 上电参考,带隙和模拟电路。

模块全部上电后在开始第次(3)在ADC 模块全部上电后,在开始第一次ADC 转换之前需要增加至少5mS 的延时。

ADC数值在结果寄存器中的存放!!数值在结果寄存器中的存放§5.2 串行通信接口SCI 和Modbus 协议介绍§5.2.1 F28335芯片的SCI 模块主要特点Features )●有三组模块SCI 模块:SCIA 、SCIB 和SCIC ;●Two external pins:SCITXD SCI i i SCITXD: SCI transmit-output pin;SCIRXD: SCI receive-input pin;Both pins can be used as GPIO if not used for SCI;●Baud rate programmable to 64K different rates●Data-word format1 start bit;Data-word length programmable from 1 to 8 bitsOptional even/odd/no parity bit1 or2 stop bits●Four error-detection flags: parity, overrun(超时, framing, and break detection;T k lti d idl li d ●Two wake-up multiprocessor modes: idle-line and address bit;Half or full duplex opera tion ●Half-or full-duplex operation;●Double-buffered receive and transmit functions;T itt d i ti b●Transmitter and receiver operations can be accomplished through interrupt-driven or polled algorithms with status flags algorithms with status flags;●Sepa rate enable bits for transmitter and receiver interrupts (except BRKDT, Break Detectp (p , ;●NRZ (non-return-to-zero,非归零 format;说明:NRZ 是不归零编码的英文缩写,是一种数据编码本身含步息读借形式,它本身不包含同步时钟信息,对它的读写必须借助读写时钟。