高性能CPU时钟网络设计

- 格式:pdf

- 大小:406.96 KB

- 文档页数:4

cpu参数单位CPU参数单位:时钟频率、核心数、缓存容量、热设计功耗时钟频率是衡量CPU性能的重要指标之一。

它表示CPU内部时钟的速度,单位为赫兹(Hz)。

时钟频率越高,CPU每秒钟能执行的指令数就越多,处理速度也就越快。

然而,时钟频率并不是唯一决定CPU性能的因素,其他因素如架构、指令集等也会影响CPU的实际性能。

核心数是指CPU中物理处理核心的数量。

每个处理核心都能独立执行指令,因此核心数越多,CPU能同时处理的任务也就越多。

多核处理器能够提高多线程应用程序的性能,使得计算机能够更好地处理多任务。

缓存容量是指CPU内置的高速缓存的大小。

高速缓存是CPU与内存之间用于加速数据传输的存储器,可以存储CPU频繁使用的数据和指令。

缓存容量越大,CPU能够缓存更多的数据,减少对内存的访问次数,提高数据读取和处理的速度。

热设计功耗(TDP)是指CPU在正常工作状态下产生的热量。

CPU 的工作会产生大量的热量,如果不能有效地散热,就会导致CPU温度过高,降低性能甚至损坏。

因此,了解CPU的热设计功耗是选择合适的散热方案的重要依据。

时钟频率、核心数、缓存容量和热设计功耗是选择CPU时需要考虑的重要参数。

不同的应用场景有不同的需求,需要根据实际情况来选择合适的参数。

时钟频率越高,CPU的处理速度越快。

对于需要高性能计算的任务,如游戏、视频编辑等,选择时钟频率较高的CPU可以获得更好的性能。

但是,高时钟频率也意味着更高的功耗和散热需求,需要配备相应的散热设备。

核心数的选择取决于实际的多任务需求。

如果需要同时运行多个应用程序或进行多线程计算,选择核心数较多的CPU可以提高系统的响应速度和并行计算能力。

但是,并非所有应用程序都能充分利用多核处理器,有些单线程应用程序可能无法得到明显的性能提升。

缓存容量对于大数据量的处理和频繁读取数据的应用程序尤为重要。

较大的缓存容量可以提高CPU的数据命中率,减少对内存的访问次数,从而提升系统的响应速度。

MIPS指令五级流水CPU设计剖析MIPS指令五级流水CPU设计是一种高性能的处理器设计架构,它将指令的执行过程拆分为五个阶段,并且在每个阶段中可以同时处理多条指令,实现了指令级并行处理。

在这种设计中,分别是取指(Instruction Fetch)、译码(Instruction Decode)、执行(Execute)、访存(Memory Access)和写回(Write Back)这五个阶段。

在MIPS指令五级流水CPU设计中,首先是取指(Instruction Fetch)阶段,这是整个处理器开始处理一条指令的阶段。

在这个阶段,处理器从指令存储器中读取即将执行的指令,并将其送入流水线中。

这个阶段还会包括对指令地址的计算和异常处理的操作。

当一条指令流入流水线后,处理器就会进行下一个阶段的操作。

接下来是译码(Instruction Decode)阶段,这个阶段主要是将取到的指令进行解码,确定指令的操作类型和需要操作的寄存器等信息。

在这个阶段,会根据指令的不同分支到不同的功能单元中处理。

同时还会识别指令之间的数据相关性,以便在后续阶段进行相应的控制。

第三个阶段是执行(Execute)阶段,在这个阶段,CPU执行指令的操作,进行算数运算或逻辑运算,或者进行跳转等控制操作。

在这个阶段,CPU还将从寄存器文件中读取数据,并进行相应的运算。

这个阶段涉及到的计算量比较大,所以需要比较多的时钟周期来完成。

接下来是访存(Memory Access)阶段,这个阶段主要是处理访问数据内存的操作,比如从数据内存中读取数据,或将结果写入数据内存等。

在这个阶段,处理器还会涉及到访存相关的操作,比如缓存机制的处理等。

这个阶段的操作通常是比较高速的存储器操作。

最后是写回(Write Back)阶段,这个阶段是处理器的最后一个阶段,处理器将执行结果写回到寄存器文件中,或进行其他相关的操作。

这个阶段可以认为是指令执行的结束阶段,对前面四个阶段产生的结果进行最终的处理。

基于51单片机的多功能电子钟设计1. 本文概述随着现代科技的发展,电子时钟已成为日常生活中不可或缺的一部分。

本文旨在介绍一种基于51单片机的多功能电子钟的设计与实现。

51单片机因其结构简单、成本低廉、易于编程等特点,在工业控制和教学实验中得到了广泛应用。

本文将重点阐述如何利用51单片机的这些特性来设计和实现一个具有基本时间显示、闹钟设定、温度显示等功能的电子钟。

本文的结构安排如下:将详细介绍51单片机的基本原理和特点,为后续的设计提供理论基础。

接着,将分析电子钟的功能需求,包括时间显示、闹钟设定、温度显示等,并基于这些需求进行系统设计。

将详细讨论电子钟的硬件设计,包括51单片机的选型、时钟电路、显示电路、温度传感器电路等。

软件设计部分将介绍如何通过编程实现电子钟的各项功能,包括时间管理、闹钟控制、温度读取等。

本文将通过实验验证所设计的电子钟的功能和性能,并对实验结果进行分析讨论。

通过本文的研究,旨在为电子钟的设计提供一种实用、经济、可靠的方法,同时也为51单片机的应用提供一个新的实践案例。

2. 51单片机概述51单片机,作为一种经典的微控制器,因其高性能、低功耗和易编程的特性而被广泛应用于工业控制、智能仪器和家用电器等领域。

它基于Intel 8051微处理器的架构,具备基本的算术逻辑单元(ALU)、程序计数器(PC)、累加器(ACC)和寄存器组等核心部件。

51单片机的核心是其8位CPU,能够处理8位数据和执行相应的指令集。

51单片机的内部结构主要包括中央处理单元(CPU)、存储器、定时器计数器、并行IO口、串行通信口等。

其存储器分为程序存储器(ROM)和数据存储器(RAM)。

程序存储器通常用于存放程序代码,而数据存储器则用于存放运行中的数据和临时变量。

51单片机还包含特殊功能寄存器(SFR),用于控制IO端口、定时器计数器和串行通信等。

51单片机的工作原理基于冯诺伊曼体系结构,即程序指令和数据存储在同一块存储器中,通过总线系统进行传输。

![毕业设计(论文)-基于单片机多功能电子时钟的设计与仿真(含程序仿真)[管理资料]](https://uimg.taocdn.com/9ad55f3e0508763230121257.webp)

程序仿真等全套设计,联系153893706第1章绪论二十一世纪的今天,最具代表性的计时产品就是电子万年历,它是近代世界钟表业界的第三次革命。

第一次是摆和摆轮游丝的发明,相对稳定的机械振荡频率源使钟表的走时差从分级缩小到秒级,代表性的产品就是带有摆或摆轮游丝的机械钟或表。

第二次革命是石英晶体振荡器的应用,发明了走时精度更高的石英电子钟表,使钟表的走时月差从分级缩小到秒级。

第三次革命就是单片机数码计时技术的应用(电子万年历),使计时产品的走时日差从分级缩小到1/600万秒,从原有传统指针计时的方式发展为人们日常更为熟悉的夜光数字显示方式,直观明了,并增加了全自动日期、星期、温度以及其他日常附属信息的显示功能,它更符合消费者的生活需求!因此,电子万年历的出现带来了钟表计时业界跨跃性的进步……我国生产的电子万年历有很多种,总体上来说以研究多功能电子万年历为主,使万年历除了原有的显示时间,日期等基本功能外,还具有闹铃,报警等功能。

商家生产的电子万年历更从质量,价格,实用上考虑,不断的改进电子万年历的设计,使其更加的具有市场。

本设计为软件,硬件相结合的一组设计。

在软件设计过程中,应对硬件部分有相关了解,这样有助于对设计题目的更深了解,有助于软件设计。

基本的要了解一些主要器件的基本功能和作用。

除了采用集成化的时钟芯片外,还有采用MCU的方案,利用AT89系列单片微机制成万年历电路,采用软件和硬件结合的方法,控制LED数码管输出,分别用来显示年、月、日、时、分、秒,其最大特点是:硬件电路简单,安装方便易于实现,软件设计独特,可靠。

AT89C52是由ATMEL公司推出的一种小型单片机。

95年出现在中国市场。

其主要特点为采用Flash存贮器技术,降低了制造成本,其软件、硬件与MCS-51完全兼容,可以很快被中国广大用户接受。

本文介绍了基于AT89C52单片机设计的电子万年历。

选题背景及研究的目的与意义设计的目的电子钟已成为人们日常生活中必不可少的物品,广泛用于个人家庭以及车站码头、剧院、办公室等公共场所,给人们的生活、学习、工作、娱乐带来了极大的方便。

1、电子闹钟的硬件系统框架:设计出电子闹钟的基本整体框架。

2、电子闹钟的电源设计:采用交直流供电电源。

电子钟一般采用数码管等显示介质,因而必须以交流供电为主,以直流电源为后备辅助电源。

3、电子闹钟的主机电路设计:主要有1)系统时钟电路设计:对时间要求不是很高,只要能使系统可靠起振并稳定运行就行。

2)系统复位电路设计:本系统采用的是RC复位方式3)按键与按钮电路设计:按键与按钮电路设计中关键要考虑的就是按键的去抖动问题。

本系统采用软件去抖。

考虑到对时和设定闹铃时间操作的使用频率不高,为了精简系统和降低成本,本系统只设置两个按键。

a)SET键,对应系统的不同工作状态,具有3个功能:在复位后的待机状态下,用于启动设定时间参数(对时或定闹);在设定时间参数状态而且不是设定最低位(即分个位)的状态下,用于结束当前位的设定,当前设定位下移;在设定最低位(分个位)的状态下,用于结束本次时间设定。

b)+1键,用于对当前设定位进行加1操作。

4)闹铃声光指示电路设计:本系统采用声音指示,关键元件是蜂鸣器。

4、电子闹钟的显示电路设计:设计一个由LED数码管组成的显示电路,显示采用共阳极数码管,其目的是为了简化限流电路的设计和实现亮度可调的要求。

一功能模、设计指标:1. 显示时、分、秒。

2. 可以24小时制或12小时制。

3. 具有校时功能,可以对小时和分单独校时,对分校时的时候,停止分向小时进位。

校时时钟源可以手动输入或借用电路中的时钟。

4. 具有正点报时功能,正点前10秒开始,蜂鸣器1秒响1秒停地响5次。

5. 为了保证计时准确、稳定,由晶体振荡器提供标准时间的基准信号。

二、设计要求:1. 画出总体设计框图,以说明数字钟由哪些相对独立的块组成,标出各个模块之间互相联系,时钟信号传输路径、方向和频率变化。

并以文字对原理作辅助说明。

2. 设计各个功能模块的电路图,加上原理说明。

3. 选择合适的元器件,在面包上接线验证、调试各个功能模块的电路,在接线验证时设计、选择合适的输入信号和输出方式,在充分电路正确性同时,输入信号和输出方式要便于电路的测试和故障排除。

芯片设计需要的知识点芯片设计是一门复杂而精密的工程,需要掌握多个知识领域的基础和专业知识。

本文将介绍芯片设计所需的主要知识点,以帮助初学者理解和入门芯片设计。

一、电子学基础知识1.1 电路理论:芯片设计离不开电路理论的基础,掌握电流、电压、电阻等基本概念,了解欧姆定律、基尔霍夫定律等电路理论原理。

1.2 逻辑电路:理解逻辑门电路,如与门、或门、非门等,了解组合逻辑和时序逻辑电路的设计方法。

1.3 模拟电路:了解模拟电路设计原理,如放大电路、滤波电路等,熟悉常见的放大器、滤波器等电路的设计和特性。

二、计算机体系结构知识2.1 计算机组成原理:了解计算机的基本组成部分,如中央处理器(CPU)、存储器、输入输出设备等,熟悉计算机指令和指令的执行过程。

2.2 微处理器架构:掌握微处理器的工作原理和内部结构,了解CPU的指令系统、寄存器、流水线等。

2.3 性能优化:了解性能优化的方法和技术,如流水线设计、指令级并行等,能够通过对芯片结构和设计的优化来提高芯片的性能。

三、数字电路设计知识3.1 布尔代数和逻辑门:掌握布尔代数的基本原理,了解与门、或门、非门等基本逻辑门的特性和应用。

3.2 状态机设计:理解有限状态机的概念和设计方法,熟悉状态图、状态转移表等状态机的表示方法。

3.3 时序逻辑设计:了解时钟信号、触发器、时序逻辑电路的设计和应用,能够进行时序逻辑的设计和分析。

四、模拟电路设计知识4.1 放大器设计:熟悉各种放大电路的设计和特性,如低频放大器、高频放大器等。

4.2 滤波器设计:了解滤波器的设计原理和常见的滤波器类型,如低通滤波器、高通滤波器、带通滤波器等。

4.3 数据转换器设计:了解模数转换器(ADC)和数模转换器(DAC)的设计原理和性能指标,能够进行数据转换器的设计和优化。

五、集成电路设计知识5.1 CMOS工艺:了解CMOS工艺的原理和制程流程,熟悉CMOS器件的特性和参数。

5.2 器件模型:理解器件模型的建立和使用,如MOS模型、BJT模型等,能够进行器件级的仿真和验证。

单片机的中央处理单元原理与性能分析单片机是一种集成电路,包含了中央处理单元(CPU)、存储器和外设接口等功能模块。

其中,中央处理单元作为单片机的核心部分,负责处理数据和执行指令。

本文将详细介绍单片机中央处理单元的原理与性能分析。

一、中央处理单元的原理中央处理单元(CPU)是单片机的核心组成部分,主要负责指令的控制和数据的处理。

CPU通常由控制器、运算器和寄存器组成。

1. 控制器控制器是CPU中的主要部分,负责指令的解码和执行。

它从存储器中读取指令,解码指令的操作码,并根据操作码控制执行相应的操作。

控制器还负责控制数据的输入输出和处理器的时序。

2. 运算器运算器是CPU中的另一个重要部分,主要负责数学和逻辑运算。

它能够执行加、减、乘、除等算术运算,并进行逻辑判断以实现条件分支等功能。

3. 寄存器寄存器是CPU中的临时存储器件,用于暂存数据和地址。

它们比其他存储器速度更快,因此可以提高CPU的运行效率。

常见的寄存器包括累加器、程序计数器、标志寄存器等。

二、中央处理单元的性能分析中央处理单元的性能主要通过以下几个指标进行评估。

1. 时钟频率时钟频率(Clock Frequency)指的是CPU内部时钟的频率,即CPU能够执行的最大操作次数。

时钟频率越高,CPU处理速度越快。

时钟频率与处理器的时钟周期相关,时钟周期是时钟频率的倒数。

因此,时钟频率越高,时钟周期越短。

2. 指令集指令集是CPU能够执行的指令的集合。

不同的CPU具有不同的指令集,如x86、ARM等。

指令集的设计直接影响到CPU的功能和性能。

现代的CPU通常采用复杂指令集(CISC)或精简指令集(RISC)。

3. 流水线技术流水线技术是提高CPU性能的一种重要手段。

它将指令的执行过程划分为多个阶段,并使多个指令可以同时在不同阶段执行。

这样能够提高指令的并行性,提高CPU的效率。

4. 缓存技术缓存技术是一种用于提高CPU访问速度的方法。

CPU内部包含了多级缓存,用于暂存指令和数据。

单周期cpu课程设计一、课程目标知识目标:1. 学生能理解单周期CPU的工作原理,掌握其内部结构及功能。

2. 学生能描述单周期CPU的指令执行过程,包括取指、译码、执行、访存、写回等阶段。

3. 学生能解释单周期CPU中时钟、指令和数据的关系,并分析其性能特点。

技能目标:1. 学生能运用所学知识,设计并实现一个简单的单周期CPU。

2. 学生能运用仿真软件对单周期CPU进行功能仿真,验证其正确性。

3. 学生能通过课程学习,培养自己的逻辑思维和问题解决能力。

情感态度价值观目标:1. 学生能对计算机硬件及CPU产生兴趣,激发学习热情。

2. 学生能认识到CPU在计算机系统中的核心地位,增强对计算机科学的尊重和热爱。

3. 学生能在团队协作中发挥积极作用,培养合作精神和沟通能力。

课程性质:本课程为计算机科学与技术专业核心课程,旨在让学生了解CPU的基本原理,掌握单周期CPU的设计方法。

学生特点:学生已经具备一定的数字逻辑电路基础,具有一定的编程能力和逻辑思维能力。

教学要求:结合学生特点,注重理论与实践相结合,引导学生通过课程学习,达到课程目标所规定的知识、技能和情感态度价值观要求。

在教学过程中,关注学生的个体差异,鼓励学生积极参与,培养其独立思考和解决问题的能力。

通过课程目标的分解,确保教学设计和评估的针对性和有效性。

二、教学内容1. 单周期CPU概述:介绍CPU的发展历程,单周期CPU的概念及其在计算机系统中的作用。

教材章节:第1章 计算机系统概述2. 单周期CPU内部结构:讲解CPU的内部组成部分,包括控制单元、算术逻辑单元(ALU)、寄存器组、程序计数器等。

教材章节:第2章 CPU内部结构3. 指令集与指令执行过程:分析指令集的设计,讲解单周期CPU指令执行过程中各阶段的任务和实现方法。

教材章节:第3章 指令集与指令执行4. 时序控制与性能分析:探讨时钟、指令和数据的关系,分析单周期CPU的性能特点。

教材章节:第4章 时序控制与性能分析5. 单周期CPU设计方法:介绍设计单周期CPU的步骤,包括电路设计、指令集设计、时序控制等。

CPU排行榜十大最佳高性能工作站台式机处理器推荐近年来,对于一些高端工作站来说,拥有一款高性能的中央处理器(CPU)至关重要。

无论是在科学计算、机器学习、3D动画制作还是其他需要大量计算的领域,CPU都是决定性能的关键因素之一。

随着技术的进步,市场上出现了许多高性能的CPU,当中又以台式机为主要市场。

CPU排行榜已成为了流行的指标,以下是CPU排行榜中的十大最佳高性能工作站台式机处理器推荐。

1. 英特尔酷睿i9 11900K英特尔酷睿i9 11900K是为桌面计算机设计的十代英特尔酷睿处理器之一,最高时钟频率可达5.3GHz。

它还有8个内核和16个线程,是当前桌面上最快的CPU之一。

如果你需要高性能的游戏和应用程序,那么这个处理器将是一个不错的选择。

2. AMD R9 5950XAMD Ryzen 9 5950X是AMD Ryzen 5000系列中的旗舰处理器。

它拥有16个物理内核和32个线程,并支持PCIe 4.0。

虽然它的时钟速度可能不如其他处理器,但它的多核性能却是出类拔萃的。

它也是市场上最昂贵的台式机CPU之一。

3. 英特尔至强W-2295英特尔至强W-2295是一款适用于工作站类型的高性能CPU。

它带有18个物理内核和36个线程,并且有着很高的基准和加速时钟频率。

这个处理器的主要优点是其对高度多线程的工作负载的处理能力。

4. AMD R9 5900XAMD Ryzen 9 5900X是AMD Ryzen 5000系列中的另一款顶级处理器。

它拥有12个物理内核和24个线程,并支持PCIe 4.0。

除了比其它同价位的处理器更高的时钟速度外,它的多核性能也非常的优秀。

这款处理器非常适合游戏玩家和需要进行多任务处理的用户。

5. 英特尔至强W-2255英特尔至强W-2255是一款专为工作站和服务器设计的高性能CPU。

它带有与Intel Core i9 9900K相同的8个核心和16个线程,还支持ECC内存。

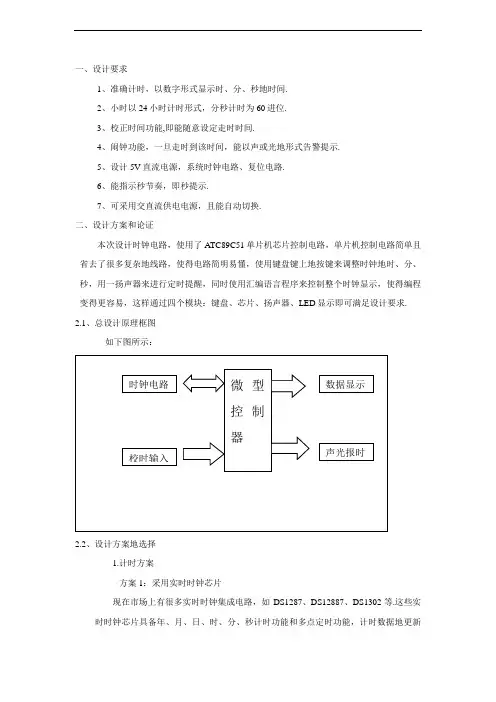

一、设计要求1、准确计时,以数字形式显示时、分、秒地时间.2、小时以24小时计时形式,分秒计时为60进位.3、校正时间功能,即能随意设定走时时间.4、闹钟功能,一旦走时到该时间,能以声或光地形式告警提示.5、设计5V直流电源,系统时钟电路、复位电路.6、能指示秒节奏,即秒提示.7、可采用交直流供电电源,且能自动切换.二、设计方案和论证本次设计时钟电路,使用了ATC89C51单片机芯片控制电路,单片机控制电路简单且省去了很多复杂地线路,使得电路简明易懂,使用键盘键上地按键来调整时钟地时、分、秒,用一扬声器来进行定时提醒,同时使用汇编语言程序来控制整个时钟显示,使得编程变得更容易,这样通过四个模块:键盘、芯片、扬声器、LED显示即可满足设计要求. 2.1、总设计原理框图如下图所示:2.2、设计方案地选择1.计时方案方案1:采用实时时钟芯片现在市场上有很多实时时钟集成电路,如DS1287、DS12887、DS1302等.这些实时时钟芯片具备年、月、日、时、分、秒计时功能和多点定时功能,计时数据地更新每秒自动进行一次,不需要程序干预.因此,在工业实时测控系统中多采用这一类专用芯片来实现实时时钟功能.方案2:使用单片机内部地可编程定时器.利用单片机内部地定时计数器进行中端定时,配合软件延时实现时、分、秒地计时.该方案节省硬件成本,但程序设计较为复杂.2.显示方案对于实时时钟而言,显示显然是另一个重要地环节.通常LED显示有两种方式:动态显示和静态显示.静态显示地优点是程序简单、显示亮度有保证、单片机CPU地开销小,节约CPU地工作时间.但占有I/O口线多,每一个LED都要占有一个I/O口,硬件开销大,电路复杂.需要几个LED就必须占有几个并行口,比较适用于LED数量较少地场合.当然当LED数量较多地时候,可以使用单片机地串行口通过移位寄存器地方式加以解决,但程序编写比较麻烦.LED动态显示硬件连接简单,但动态扫描地显示方式需要占有CPU较多地时间,在单片机没有太多实时测控任务地情况下可以采用.本系统需要采用6位LED数码管来分别显示时、分、秒,因数码管个数较多,故本系统选择动态显示方式.2.3硬件部分1、STC89C51单片机介绍STC89C51单片机是由深圳宏晶公司代理销售地一款MCU,是由美国设计生产地一种低电压、高性能CMOS 8位单片机,片内含8kbytes地可反复写地FlashROM和128bytes地RAM,2个16位定时计数器[5].STC89C51单片机内部主要包括累加器ACC(有时也简称为A)、程序状态字PSW、地址指示器DPTR、只读存储器ROM、随机存取存储器RAM、寄存器、并行I/O接口P0~P3、定时器/计数器、串行I/O接口以及定时控制逻辑电路等.这些部件通过内部总线联接起来,构成一个完整地微型计算机.其管脚图如图所示.STC89C51单片机管脚结构图VCC:电源.GND:接地.P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流.当P1口地管脚第一次写1时,被定义为高阻输入.P0能够用于外部程序数据存储器,它可以被定义为数据/地址地第八位.在FIASH编程时,P0 口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须被拉高.P1口:P1口是一个内部提供上拉电阻地8位双向I/O口,P1口缓冲器能接收输出4TTL门电流.P1口管脚写入1后,被内部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉地缘故.在FLASH编程和校验时,P1口作为第八位地址接收.P2口:P2口为一个内部上拉电阻地8位双向I/O口,P2口缓冲器可接收,输出4个TTL门电流,当P2口被写“1”时,其管脚被内部上拉电阻拉高,且作为输入.并因此作为输入时,P2口地管脚被外部拉低,将输出电流.这是由于内部上拉地缘故.P2口当用于外部程序存储器或16位地址外部数据存储器进行存取时,P2口输出地址地高八位.在给出地址“1”时,它利用内部上拉优势,当对外部八位地址数据存储器进行读写时,P2口输出其特殊功能寄存器地内容.P2口在FLASH编程和校验时接收高八位地址信号和控制信号.P3口:P3口管脚是8个带内部上拉电阻地双向I/O口,可接收输出4个TTL门电流.当P3口写入“1”后,它们被内部上拉为高电平,并用作输入.作为输入,由于外部下拉为低电平,P3口将输出电流(ILL)这是由于上拉地缘故.P3口也可作为AT89C51地一些特殊功能口,如下表所示:口管脚备选功能P3.0 RXD(串行输入口)P3.1 TXD(串行输出口)P3.2 /INT0(外部中断0)P3.3 /INT1(外部中断1)P3.4 T0(记时器0外部输入)P3.5 T1(记时器1外部输入)P3.6 /WR(外部数据存储器写选通)P3.7 /RD(外部数据存储器读选通)P3口同时为闪烁编程和编程校验接收一些控制信号.RST:复位输入.当振荡器复位器件时,要保持RST脚两个机器周期地高电平时间.ALE/PROG:当访问外部存储器时,地址锁存允许地输出电平用于锁存地址地地位字节.在FLASH编程期间,此引脚用于输入编程脉冲.在平时,ALE 端以不变地频率周期输出正脉冲信号,此频率为振荡器频率地1/6.因此它可用作对外部输出地脉冲或用于定时目地.然而要注意地是:每当用作外部数据存储器时,将跳过一个ALE脉冲.如想禁止ALE地输出可在SFR8EH地址上置0.此时,ALE只有在执行MOVX,MOVC指令是ALE才起作用.另外,该引脚被略微拉高.如果微处理器在外部执行状态ALE禁止,置位无效.PSEN:外部程序存储器地选通信号.在由外部程序存储器取指期间,每个机器周期两次/PSEN有效.但在访问外部数据存储器时,这两次有效地/PSEN信号将不出现.EA/VPP:当/EA保持低电平时,则在此期间外部程序存储(0000H-FFFFH),不管是否有内部程序存储器.注意加密方式1时, /EA将内部锁定为RESET;当/EA端保持高电平时,此间内部程序存储器.在FLASH编程期间,此引脚也用于施加12V编程电源(VPP).2、上电按钮复位电路本设计采用上电按钮复位电路:首先经过上电复位,当按下按键时,RST直接与VCC相连,为高电平形成复位,同时电解电容被电路放电;按键松开时,VCC对电容充电,充电电流在电阻上,RST依然为高电平,仍然是复位,充电完成后,电容相当于开路,RST为低电平,单片机芯片正常工作.其中电阻R2决定了电容充电地时间,R2越大则充电时间长,复位信号从VCC回落到0V地时间也长.3、晶振电路本设计晶振电路采用12M地晶振.晶振地作用是给单片机正常工作提供稳定地时钟信号.单片机地晶振并不是只能用12M,只要不超过20M就行,在准许地范围内,晶振越大,单片机运行越快,还有用12M地就是好算时间,因为一个机器周期为1/12时钟周期,所以这样用12M地话,一个时钟周期为12us,那么定时器计一次数就是1us了,电容范围在20-40pF之间,这里连接地是30pF地电容.机器周期=10*晶振周期=12*系统时钟周期4.下载端口设计用到地STC89C52单片机芯片地ISP下载线是通过单片机地TXD,RXD引脚把程序烧进去地.管脚TXD和RXD用于异步串行通信.其实STC89C52单片机地ISP下载线就是一个max232芯片连接STC和计算机地串行通信口.计算机把程序从九针串口送到max232芯片,电平转换后送进单片机地串行口,也就是TXD和RXD.然后单片机地串行模块把数据送到程序区.5、显示电路就时钟而言,通常可采用液晶显示或数码管显示.由于一般地段式液晶屏,需要专门地驱动电路,而且液晶显示作为一种被动显示,可视性相对较差;对于具有驱动电路和微处理器接口地液晶显示模块(字符或点阵),一般多采用并行接口,对微处理器地接口要求较高,占用资源多.另外,89C2051本身无专门地液晶驱动接口,因此,本时钟采用数码管显示方式.数码管作为一种主动显示器件,具有亮度高、价格便宜等优点,而且市场上也有专门地时钟显示组合数码管.对于实时时钟而言,显示显然是另一个重要地环节.通常LED显示有两种方式:动态显示和静态显示.静态显示地优点是程序简单、显示亮度有保证、单片机CPU地开销小,节约CPU地工作时间.但占有I/O口线多,每一个LED都要占有一个I/O口,硬件开销大,电路复杂.需要几个LED就必须占有几个并行口,比较适用于LED数量较少地场合.当然当LED数量较多地时候,可以使用单片机地串行口通过移位寄存器地方式加以解决,但程序编写比较麻烦.LED动态显示硬件连接简单,但动态扫描地显示方式需要占有CPU较多地时间,在单片机没有太多实时测控任务地情况下可以采用.本系统需要采用6位LED数码管来分别显示时、分、秒,因数码管个数较多,故本系统选择动态显示方式.6、时钟显示校正电路本设计利用按键开关来校正时钟显示地数字.当按钮按下时,将在相应地端口输入一个低电平,通过相应地程序来改变时钟显示.其中S1按键开关用来选择要修改地数字;S2按键用来增加所选数字地数值;S3按键用来减少所选数字地数值.7、蜂鸣器电路电路接法:三极管选定PNP型,基极B连接5V电压,发射极E连接一个1K左右地电阻后接I/O口,集电极C连接蜂鸣器后接地.单片机在复位后地个I/O口是高电平,此时三极管是截止地,编写程序使选定地I/O为低电平,此时三极管导通,导通后蜂鸣器与电源正极连通,构成一个工作回路,从而发出滴滴地响声.其中电阻R1在电路里起分压限流地作用,PNP三极管起到模拟开关地作用.8、外接电源电路外接电源电路用于连接外部5V电源与电子时钟电路,通过自锁开关控制电路地导通与断开,当开关闭合时,电路导通,外部电源给电路正常供电,电子时钟正常工作.当开关断开时,电路停止工作.9、总电路原理图(五)软件部分根据上述电子时钟地工作流程,软件设计可分为以下几个功能模块:(1)主程序模块.主程序主要用于系统初始化:设置计时缓冲区地位置及初值,设置8155地工作方式、定时器地工作方式和计数初值等参数.主程序流程如下图所示.开始定义堆栈区8155、T0、数据缓冲区、标志位初始化调用键盘扫描程序否是C/R键?地址指针指向计时缓冲区主程序流程图(2)计时模块.即定时器0中断子程序,完成刷新计时缓冲区地功能.系统使用6MHz地晶振,假设定时器0工作在方式1,则定时器地最大定时时间为65.536ms,这个值远远小于1s.因此本系统采用定时器与软件循环相结合地定时方法.设定时器0工作在方式1,每隔50ms溢出中断一次,则循环中断20次延时时间是1s,上述过程重复60次为1分,分计时60次为1小时,小时计时24次则时间重新回到00:00:00.因定时器0工作在方式1,则50ms定时对应地定时器初值为:65536-50ms/2us=40536=9E58H,即TH0=9EH,TH0=58H.但应当指出:CPU从响应T0中断到完成定时器初值重装这段时间,定时器T0并不停止工作,而是继续计数.因此,为了确保T0能准确定时50ms,重装地定时器初值必须加以修正,修正地定时器初值必须考虑到从原定时器初值中扣除计数器多计地脉冲个数.由于定时器计数脉冲地周期恰好和机器周期吻合,因此修正量等于CPU从响应中断到重装完TL0为止所用地机器周期数.CPU响应中断通常要3~8个机器周期.经过测试,定时器0重装地计数初值设为9E5FH~9E67H,可以满足精度要求.另外,MCS-51单片机只有二进制加法指令,而时间是按十进制递增,因此用加法指令后必须进行二-十进制转换.计时模块流程图如下图所示.计时模块流程图(3)时间设置模块.该模块由键盘输入相应地数据来设置当前时间.程序通过调用一个键盘设置子程序通过键盘扫描将键入地6位时间值送入显示缓冲区.设置时间后,时钟要从这个时间开始计时,而时分秒单元各占一个字节,键盘占6个字节.因此程序中要调用一个合字子程序将显示缓冲区中地6位BCD码合并为3位压缩BCD码,并送入计时缓冲区,作为当前计时起始时间.该程序同时要检测输入时间值地合法性,若键盘输入地小时值大于23,分、秒值大于59,则不合法,将取消本次设置,清零重新开始计时.时间设置和键盘设置子程序地流程图如下图所示.时间设置流程图键盘设置子程序流程图(4)显示模块.该模块完成时分秒6位LED地动态显示.因为显示为6位,二计时是3个字节单元,为此,必须将3字节计时缓冲区中地时分秒压缩BCD码拆分为6字节BCD码,并送入显示缓冲区中.当按下调整时间键后,在6位设置完成之前,这6个LED应该显示键人地数据,不显示当前地时间.为此,我们设置了一个计时显示允许标志位F0,在时间设置期间F0=1,不调用刷新显示缓冲区地子程序.显示程序流程图如下图所示.保护现场是显示程序流程图键盘扫描程序流程图程序:ORG 0000H AJMP MAIN ORG 000BH AJMP TIME ORG 0300H MAIN:mov 20h,#00h MOV 21H,#00H MOV 22H,#00H MOV 23H,#00H MOV IP,#02H 。

网络中为什么要部署NTP服务器(时钟同步服务器,网络校时设备,GPS授时服务器,NTP网络同步时钟)?随着计算机网络的迅猛发展,网络应用已经非常普遍,如电力、金融、通信、交通、广电、安防、石化、水利、国防、医疗、政府机关、IT等领域的网络系统需要在大范围保持计算机的时间同步和时钟准确,但计算机的时间是根据电脑晶振以固定频率震荡而产生的,由于晶振的不同,会导致电脑时间积累误差的产生。

从业务影响角度讲,因为时间的不统一,就无法推断出业务具体发生时间。

从安全影响角度讲,所有设备(如视频监控中的DVR)的日志必须反映准确的时间,因为时间的不统一,安全相关工具就会毫无用处。

因此有一个好的标准时间校时器是非常必要的。

为了适应这些领域对于时间越来越精密的要求,锐呈公司精心设计、自主研发了K系列GPS校时器(NTP服务器,时钟同步服务器,网络校时设备,GPS 授时服务器,NTP网络同步时钟)。

该装置以美国全球定位系统(GPS)为时间基准,内嵌国际流行的NTP-SERVER服务,以NTP/SNTP协议同步网络中的所有计算机、控制器等设备,实现网络授时。

K805网络时钟同步系统采用表面贴装技术生产,以高速芯片进行控制,无硬盘和风扇设计,具有精度高、稳定性好、功能强、无积累误差、不受地域气候等环境条件限制、性价比高、操作简单、免维护等特点,适合无人值守。

该产品可以为计算机网络、计算机应用系统、流程控制管理系统、电子商务系统、网上B2B系统以及数据库的保存维护等系统提供精密的标准时间信号和时间戳服务。

K805网络时钟同步系统采用全模块化结构设计,其输入、输出、电源等均可灵活配置,并具有丰富的各类模块及板卡供选择(特殊需求可提供定制服务),对时信号的种类和数量都可根据需要灵活选择配置。

装置有标准RS232、RS422/485、脉冲、IRIG-B、DCF77、PTP、NTP/SNTP协议时间输出等接口形式,可以适应各种不同设备的对时需要。

多功能电子钟的设计与实现课程设计说明多功能电子钟的设计与实现摘要电子时钟主要是利用电子技术将时钟电子化、数字化,拥有时钟精确、体积小、界面友好、可扩展性能强等特点,被广泛应用于生活和工作当中。

另外,在生活和体育赛场中,也常常需要跑秒,这就需要电子时钟具有多功能性。

本设计主要为实现一款可正常显示时钟,带有定时闹铃,跑秒的多功能电子时钟。

本文对当前电子钟开发手段进行了比较和分析,最终确定了采用单片机技术实现多功能电子时钟。

本设计应用AT89C51芯片作为核心,利用74LS164作为串入并出的寄存器,7位LED数码管显示,并且设置按键来对分秒小时闹铃等进行校对。

这种实现方法的优点是电路简单,性能可靠,实时性好,时间精度高,操作简单,编程容易。

该电子时钟可以应用于一般的生活和工作中,也可通过改装,提高性能,增加新功能,从而给人们的生活和工作带来更多的方便。

关键词:电子时钟;AT89C51;74LS164;LED;The Design with Investigation of the Multi-function Electron ClockAbstractElectronic clock is the use of electronic technology will be an electronic clock, digital, with the clock precision, small size and friendly interface, scalable performance, and other characteristics, are widely used to live and work. In addition, in the field of sports and life, often need to run second, which requires electronic clock with versatility.The main design for the realization of this can be a normal clock display, from time to time with alarm, running the second multi-function electronic clock.This article on the current development of the electronic clock means were compared and analyzed to determine the ultimate use of a single chip multifunctional electronic clock technology. AT89C51 chip design of this application as the core, to use as a 74LS164 and a string into the register, 7 LED digital display and button set up to every minute of the hour for alarm, and other proof-reading. This method has the advantage of a simple circuit, reliable and real-time, high-accuracy time, simple, easy to program.The electronic clock can be applied to general life and work, can also be modified to improve performance, add new functions to the people living and working more convenient.Key words: Electronic clock; AT89C51; 74LS164; LED;目录摘要 (I)Abstract .................................................................................................................................... I I 第一章引言 . (5)1.1 多功能电子时钟研究的背景和意义 (5)1.2 电子时钟的功能 (6)第二章电子时钟设计方案分析 (7)第三章基于单片机的电子时钟硬件设计 (8)3.1 主要IC芯片选择 (8)3.1.1微处理器的选择 (8)3.1.2寄存器的选择 (11)3.1.3显示器件的选择 (12)3.1.4看门狗器件的选择 (14)3.2 电子时钟硬件电路设计 (14)3.2.1 显示电路 (15)3.2.2 按键电路设计 (15)3.2.3 闹铃电路设计 (17)3.2.4 复位电路设计 (18)第四章电子时钟软件设计 (20)4.1 主程序设计 (20)4.2 子程序设计 (21)4.2.1 显示子程序设计 (21)4.2.2 键盘扫描子程序 (21)4.2.3闹铃子程序设计 (23)4.2.4跑秒子程序设计 (23)第五章系统调试 (24)5.1 硬件调试 (24)5.1.1 单片机基础电路调试 (24)5.1.2 显示电路调试 (25)5.2 软件调试 (27)结论 (28)参考文献 (29)附录A 程序............................................................................................................................... 附录B 多功能电子时钟硬件电路图......................................................................................... 致谢 .. (30)第一章引言时间是人类生活必不可少的重要元素,如果没有时间的概念,社会将不会有所发展和进步。

目录1前言 (1)2总体方案设计 (2)2.1设计内容 (2)2.2设计内容 (2)2.3方案论证 (3)2.4方案选择 (4)3单元模块设计 (5)3.1各单元模块功能介绍及电路设计 (5)3.1.1 温度采集电路 (5)3.1.2 DS1302时钟电路 (5)3.1.3 串行通信接口电路 (6)3.1.4 USB连接电路 (6)3.1.5 按键电路 (7)3.1.6液晶显示显示电路 (7)3.2特殊器件介绍 (7)3.2.1 STC89C52单片机芯片 (7)3.2.2 DS1302介绍 (8)3.2.3 温度传感器DS18B20 (9)3.2.4 液晶显示LCD1602 (9)4软件设计 (10)4.1软件选择 (10)4.2软件设计流程 (10)4.2.1 温度采集流程 (11)4.2.2 日期数据处理流程 (12)5系统的仿真及调试 (13)5.1系统仿真 (13)5.2硬件调试 (13)5.3软件调试 (14)6结论 (16)7总结与体会 (17)7.1设计小结 (17)7.2设计收获及改进 (17)7.3致谢 (17)8参考文献 (18)附录: (19)1前言单片机是指一个集成在一块芯片上的完整计算机系统。

尽管他的大部分功能集成在一块小芯片上,但是它具有一个完整计算机所需要的大部分部件:CPU、内存、内部和外部总线系统,目前大部分还会具有外存。

同时集成诸如通讯接口、定时器,实时时钟等外围设备。

而现在最强大的单片机系统甚至可以将声音、图像、网络、复杂的输入输出系统集成在一块芯片上。

单片机也被称为微控制器(Microcontroller),它不是完成某一个逻辑功能的芯片,而是把一个计算机系统集成到一个芯片上。

概括的讲:一块芯片就成了一台计算机。

它的体积小、质量轻、价格便宜、为学习、应用和开发提供了便利条件。

单片机诞生于20世纪70年代末,经历了SCM、MCU、SOC三大阶段。

STC单片机完全兼容51单片机,并有其独到之处,其抗干扰性强,加密性强,超低功耗,可以远程升级,内部有专用复位电路,价格也较便宜,由于这些特点使得 STC 系列单片机的应用日趋广泛。