第6章_Verilog_HDL设计进阶习题

- 格式:ppt

- 大小:933.00 KB

- 文档页数:38

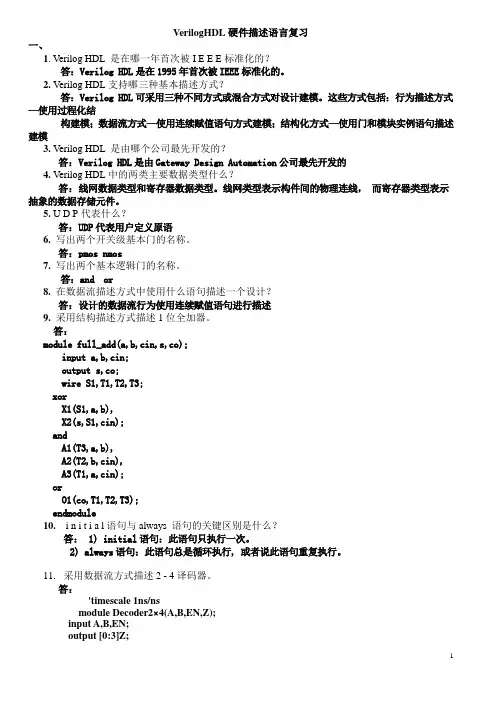

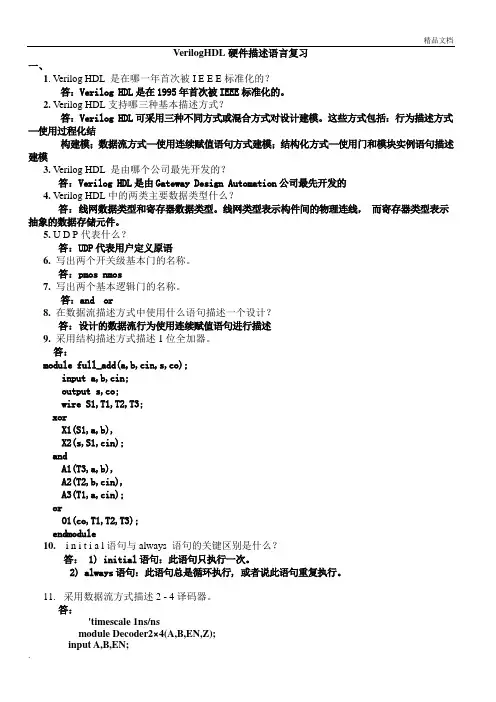

VerilogHDL硬件描述语言复习一、1. Verilog HDL 是在哪一年首次被I E E E标准化的?答:Verilog HDL是在1995年首次被IEEE标准化的。

2. Verilog HDL支持哪三种基本描述方式?答:Verilog HDL可采用三种不同方式或混合方式对设计建模。

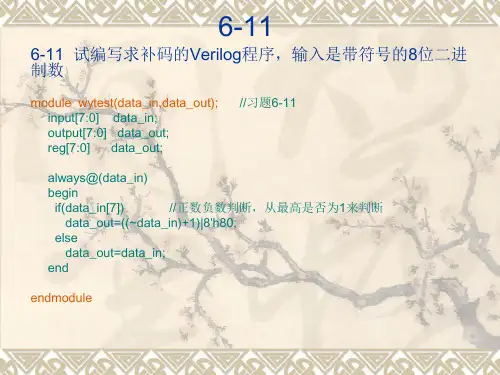

这些方式包括:行为描述方式—使用过程化结构建模;数据流方式—使用连续赋值语句方式建模;结构化方式—使用门和模块实例语句描述建模3. Verilog HDL 是由哪个公司最先开发的?答:Verilog HDL是由Gateway Design Automation公司最先开发的4. Verilog HDL中的两类主要数据类型什么?答:线网数据类型和寄存器数据类型。

线网类型表示构件间的物理连线,而寄存器类型表示抽象的数据存储元件。

5. U D P代表什么?答:UDP代表用户定义原语6. 写出两个开关级基本门的名称。

答:pmos nmos7.写出两个基本逻辑门的名称。

答:and or8.在数据流描述方式中使用什么语句描述一个设计?答:设计的数据流行为使用连续赋值语句进行描述9. 采用结构描述方式描述1位全加器。

答:module full_add(a,b,cin,s,co);input a,b,cin;output s,co;wire S1,T1,T2,T3;xorX1(S1,a,b),X2(s,S1,cin);andA1(T3,a,b),A2(T2,b,cin),A3(T1,a,cin);orO1(co,T1,T2,T3);endmodule10. i n i t i a l语句与always 语句的关键区别是什么?答: 1) initial语句:此语句只执行一次。

2) always语句:此语句总是循环执行, 或者说此语句重复执行。

11.采用数据流方式描述2 - 4译码器。

答:'timescale 1ns/nsmodule Decoder2×4(A,B,EN,Z);input A,B,EN;output [0:3]Z;wire abar,Bbar;assign #1 Abar=~A;assign #1 Bbar=~B;assign #2 Z[0]=~(Abar&Bbar&EN);assign #2 Z[1]=~(Abar&B&EN);assign #2 Z[2]=~(A&Bbar&EN);assign #2 Z[3]=~(A&B&EN);endmodule1 2. 找出下面连续赋值语句的错误。

VerilogHDL硬件描述语言复习一、1. Verilog HDL 是在哪一年首次被I E E E标准化的?答:Verilog HDL是在1995年首次被IEEE标准化的。

2. Verilog HDL支持哪三种基本描述方式?答:Verilog HDL可采用三种不同方式或混合方式对设计建模。

这些方式包括:行为描述方式—使用过程化结构建模;数据流方式—使用连续赋值语句方式建模;结构化方式—使用门和模块实例语句描述建模3. Verilog HDL 是由哪个公司最先开发的?答:Verilog HDL是由Gateway Design Automation公司最先开发的4. Verilog HDL中的两类主要数据类型什么?答:线网数据类型和寄存器数据类型。

线网类型表示构件间的物理连线,而寄存器类型表示抽象的数据存储元件。

5. U D P代表什么?答:UDP代表用户定义原语6. 写出两个开关级基本门的名称。

答:pmos nmos7.写出两个基本逻辑门的名称。

答:and or8.在数据流描述方式中使用什么语句描述一个设计?答:设计的数据流行为使用连续赋值语句进行描述9. 采用结构描述方式描述1位全加器。

答:module full_add(a,b,cin,s,co);input a,b,cin;output s,co;wire S1,T1,T2,T3;xorX1(S1,a,b),X2(s,S1,cin);andA1(T3,a,b),A2(T2,b,cin),A3(T1,a,cin);orO1(co,T1,T2,T3);endmodule10. i n i t i a l语句与always 语句的关键区别是什么?答: 1) initial语句:此语句只执行一次。

2) always语句:此语句总是循环执行, 或者说此语句重复执行。

11.采用数据流方式描述2 - 4译码器。

答:'timescale 1ns/nsmodule Decoder2×4(A,B,EN,Z);input A,B,EN;output [0:3]Z;wire abar,Bbar;assign #1 Abar=~A;assign #1 Bbar=~B;assign #2 Z[0]=~(Abar&Bbar&EN);assign #2 Z[1]=~(Abar&B&EN);assign #2 Z[2]=~(A&Bbar&EN);assign #2 Z[3]=~(A&B&EN);endmodule1 2. 找出下面连续赋值语句的错误。

第六章Verilog的数据类型及逻辑系统学习内容:•学习Verilog逻辑值系统•学习Verilog中不同类的数据类型•理解每种数据类型的用途及用法•数据类型说明的语法Verilog采用的四值逻辑系统’0’, Low, False, Logic Low, Ground,VSS,Negative Assertion‘1’, High, True, Logic High, Power,VDD, VCC, Positive Assertion’X’ Unknown: Occurs at Logical Which Cannotbe Resolved ConflictHiZ, High Impedance, Tri-Stated,Disabled Driver (Unknown)主要数据类型Verilog主要有三类(class)数据类型:•net (线网): 表示器件之间的物理连接•register (寄存器):表示抽象存储元件•parameters(参数) : 运行时的常数(run-time constants)net(线网)net需要被持续的驱动,驱动它的可以是门和模块。

当net驱动器的值发生变化时,Verilog自动的将新值传送到net上。

在例子中,线网out由or门驱动。

当or门的输入信号置位时将传输到线网net上。

•有多种net 类型用于设计(design-specific)建模和工艺(technology-specific)建模•没有声明的net 的缺省类型为1 位(标量)wire 类型。

但这个缺省类型可由下面的编译指导改变:`default_nettype <nettype>net 类型功能wire, trisupply1, supply0wor, triorwand, triandtriregtri1, tri0标准内部连接线(缺省)电源和地多驱动源线或多驱动源线与能保存电荷的net 无驱动时上拉/下拉综合编译器不支持的net 类型•wire类型是最常用的类型,只有连接功能。

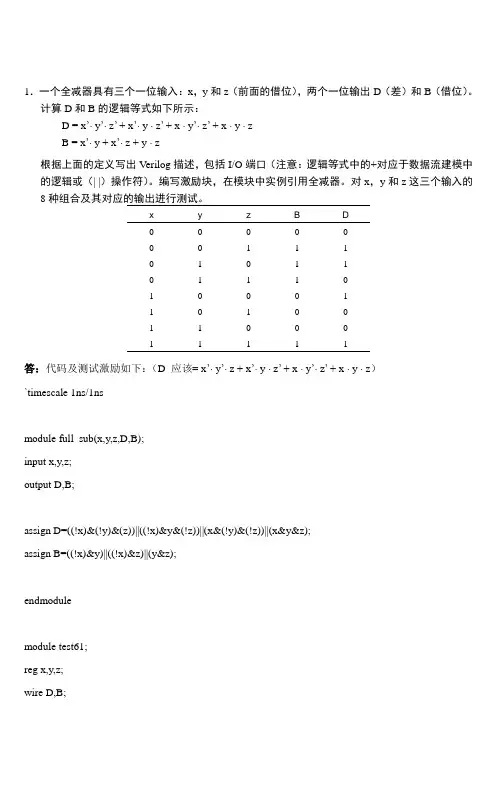

1.一个全减器具有三个一位输入:x,y和z(前面的借位),两个一位输出D(差)和B(借位)。

计算D和B的逻辑等式如下所示:D = x’⋅ y’⋅ z’ + x’⋅ y ⋅ z’ + x ⋅ y’⋅ z’ + x ⋅ y ⋅ zB = x’⋅ y + x’⋅ z + y ⋅ z根据上面的定义写出Verilog描述,包括I/O端口(注意:逻辑等式中的+对应于数据流建模中的逻辑或(| |)操作符)。

编写激励块,在模块中实例引用全减器。

对x,y和z这三个输入的8种组合及其对应的输出进行测试。

x y z B D0 0 0 0 00 0 1 1 10 1 0 1 10 1 1 1 01 0 0 0 11 0 1 0 01 1 0 0 01 1 1 1 1答:代码及测试激励如下:(D 应该= x’⋅y’⋅z + x’⋅ y ⋅z’ + x ⋅y’⋅z’ + x ⋅ y ⋅ z)`timescale 1ns/1nsmodule full_sub(x,y,z,D,B);input x,y,z;output D,B;assign D=((!x)&(!y)&(z))||((!x)&y&(!z))||(x&(!y)&(!z))||(x&y&z);assign B=((!x)&y)||((!x)&z)||(y&z);endmodulemodule test61;reg x,y,z;wire D,B;Verilog HDL数字设计与综合(第二版)58initialbeginx<=0;y<=0;z<=0;#10 x<=0;y<=0;z<=1;#10 x<=0;y<=1;z<=0;#10 x<=0;y<=1;z<=1;#10 x<=1;y<=0;z<=0;#10 x<=1;y<=0;z<=1;#10 x<=1;y<=1;z<=0;#10 x<=1;y<=1;z<=1;#10 $stop;endfull_sub fsubtracter(x,y,z,D,B);initial$monitor($time,"x= %b,y= %b,z= %b,B= %b,D= %b",x,y,z,B,D);endmodule最终输出观测结果:# 0x= 0,y= 0,z= 0,B= 0,D= 0# 10x= 0,y= 0,z= 1,B= 1,D= 1# 20x= 0,y= 1,z= 0,B= 1,D= 1# 30x= 0,y= 1,z= 1,B= 1,D= 0# 40x= 1,y= 0,z= 0,B= 0,D= 1# 50x= 1,y= 0,z= 1,B= 0,D= 0# 60x= 1,y= 1,z= 0,B= 0,D= 0# 70x= 1,y= 1,z= 1,B= 1,D= 1第6章数据流建模592.大小比较器的功能是比较两个数之间的关系:大于、小于或等于。

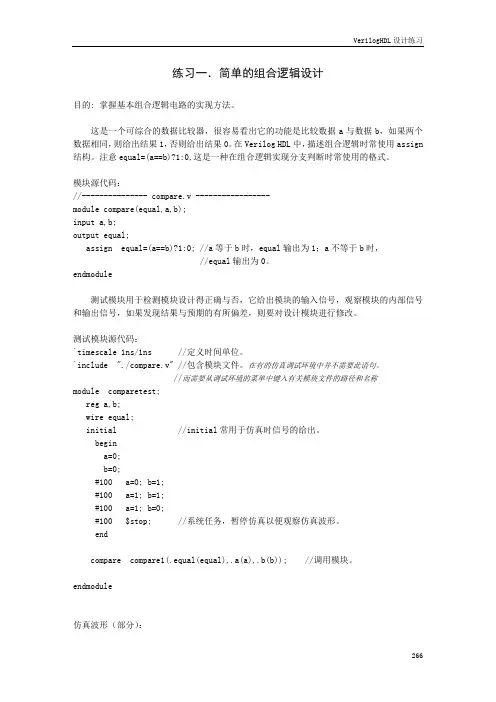

练习一.简单的组合逻辑设计目的: 掌握基本组合逻辑电路的实现方法。

这是一个可综合的数据比较器,很容易看出它的功能是比较数据a与数据b,如果两个数据相同,则给出结果1,否则给出结果0。

在Verilog HDL中,描述组合逻辑时常使用assign 结构。

注意equal=(a==b)?1:0,这是一种在组合逻辑实现分支判断时常使用的格式。

模块源代码://--------------- compare.v -----------------module compare(equal,a,b);input a,b;output equal;assign equal=(a==b)?1:0; //a等于b时,equal输出为1;a不等于b时,//equal输出为0。

endmodule测试模块用于检测模块设计得正确与否,它给出模块的输入信号,观察模块的内部信号和输出信号,如果发现结果与预期的有所偏差,则要对设计模块进行修改。

测试模块源代码:`timescale 1ns/1ns //定义时间单位。

`include "./compare.v" //包含模块文件。

在有的仿真调试环境中并不需要此语句。

//而需要从调试环境的菜单中键入有关模块文件的路径和名称module comparetest;reg a,b;wire equal;initial //initial常用于仿真时信号的给出。

begina=0;b=0;#100 a=0; b=1;#100 a=1; b=1;#100 a=1; b=0;#100 $stop; //系统任务,暂停仿真以便观察仿真波形。

endcompare compare1(.equal(equal),.a(a),.b(b)); //调用模块。

endmodule仿真波形(部分):266练习:设计一个字节(8位)比较器。

要求:比较两个字节的大小,如a[7:0]大于 b[7:0]输出高电平,否则输出低电平,改写测试模型,使其能进行比较全面的测试。

verilog-hdl答案第1章简介HDL是在哪一年首次被IEEE标准化的Verilog HDL是在1995年首次被IEEE标准化的。

HDL支持哪三种基本描述方式Verilog HDL可采用三种不同方式或混合方式对设计建模。

这些方式包括:行为描述方式—使用过程化结构建模;数据流方式—使用连续赋值语句方式建模;结构化方式—使用门和模块实例语句描述建模3.可以使用Verilog HDL描述一个设计的时序吗Verilog HDL可以清晰的建立时序模型,故可以使用Verilog HDL 描述一个设计的时序。

4.语言中的什么特性能够用于描述参数化设计,在行为级描述中, Verilog HDL不仅能够在RT L级上进行设计描述,而且能够在体系结构级描述及其算法级行为上进行设计描述,而且能够使用门和模块实例化语句在结构级进行结构描述,这种特性可用于描述参数化设计。

5.能够使用Verilog HDL编写测试验证程序吗能,可以编写testbench来对编写的程序进行验证。

HDL是由哪个公司最先开发的Verilog HDL是由Gateway Design Automation公司最先开发的HDL中的两类主要数据类型是什么线网数据类型和寄存器数据类型。

线网类型表示构件间的物理连线,而寄存器类型表示抽象的数据存储元件。

,代表什么UDP代表用户定义原语9.写出两个开关级基本门的名称。

pmos nmos10.写出两个基本逻辑门的名称。

and or第2章 HDL指南1. 在数据流描述方式中使用什么语句描述一个设计】设计的数据流行为使用连续赋值语句进行描述2. 使用` t i m e s c a l e 编译器指令的目的是什么举出一个实例。

使用编译指令将时间单位与物理时间相关联。

例如` timescale 1ns /100ps 此语句说明时延时间单位为1ns并且时间精度为100ps (时间精度是指所有的时延必须被限定在内)3. 在过程赋值语句中可以定义哪两种时延请举例详细说明。

数字系统设计与VerilogHDL课后习题习题11.1现代EDA技术的特点有哪些?1.2什么是T op-down设计方式?1.3数字系统的实现方式有哪些?各有什么优缺点?1.4什么是IP复用技术? IP核对EDA技术的应用和发展有什么意义?1.5用硬件描述语言设计数字电路的优势是什么?1.6结合自己的使用情况谈谈对EDA工具的认识。

1.7基于FPGA/CPLD的数字系统设计流程包括哪些步骤?1.8什么是综合?常用的综合工具有哪些?1.9功能仿真与时序仿真有什么区别?1.10 FPGA与ASIC在概念上有什么区别?习题22.1 PLA和PAL在结构上有什么区别?2.2说明GAL的OLMC有什么特点,它怎样实现可编程组合电路和时序电路?2.3简述基于乘积项的可编程逻辑器件的结构特点。

2.4基于查找表的可编程逻辑结构的原理是什么?2.5基于乘积项和基于查找表的结构各有什么优点?2.6 CPLD和FPGA在结构上有什么明显的区别?各有什么特点?2.7 FPGA器件中的存储器块有何作用?2.8 Altera的MAX II器件是属于CPLD还是FPGA,请查阅有关资料并进行分析。

2.9边界扫描技术有什么优点?2.10说说JTAG接口都有哪些功能。

2.11 FPGA/CPLD器件未来的发展趋势有哪些?习题44.1 用Verilog设计一个8位加法器,进行综合和仿真,查看综合和仿真结果。

4.2 用Verilog设计一个8位二进制加法计数器,带异步复位端口,进行综合和仿真,查看综合和仿真结果。

4.3用Verilog设计一个模60的BCD码计数器,进行综合和仿真,查看综合和仿真结果。

习题66.1阻塞赋值和非阻塞赋值有什么本质的区别?6.2用持续赋值语句描述一个4选1数据选择器。

6.3用行为语句设计一个8位计数器,每次在时钟的上升沿,计数器加1,当计数器溢出时,自动从零开始重新计数。

计数器有同步复位端。

6.4设计一个4位移位寄存器。

习题11.1现代EDA技术的特点有哪些?1.2什么是Top-down设计方式?1.3数字系统的实现方式有哪些?各有什么优缺点?1.4什么是IP复用技术? IP核对EDA技术的应用和发展有什么意义?1.5用硬件描述语言设计数字电路的优势是什么?1.6结合自己的使用情况谈谈对EDA工具的认识。

1.7基于FPGA/CPLD的数字系统设计流程包括哪些步骤?1.8什么是综合?常用的综合工具有哪些?1.9功能仿真与时序仿真有什么区别?1.10 FPGA与ASIC在概念上有什么区别?习题22.1 PLA和PAL在结构上有什么区别?2.2说明GAL的OLMC有什么特点,它怎样实现可编程组合电路和时序电路?2.3简述基于乘积项的可编程逻辑器件的结构特点。

2.4基于查找表的可编程逻辑结构的原理是什么?2.5基于乘积项和基于查找表的结构各有什么优点?2.6 CPLD和FPGA在结构上有什么明显的区别?各有什么特点?2.7 FPGA器件中的存储器块有何作用?2.8 Altera的MAX II器件是属于CPLD还是FPGA,请查阅有关资料并进行分析。

2.9边界扫描技术有什么优点?2.10说说JTAG接口都有哪些功能。

2.11 FPGA/CPLD器件未来的发展趋势有哪些?习题44.1 用Verilog设计一个8位加法器,进行综合和仿真,查看综合和仿真结果。

4.2 用Verilog设计一个8位二进制加法计数器,带异步复位端口,进行综合和仿真,查看综合和仿真结果。

4.3用Verilog设计一个模60的BCD码计数器,进行综合和仿真,查看综合和仿真结果。

习题66.1阻塞赋值和非阻塞赋值有什么本质的区别?6.2用持续赋值语句描述一个4选1数据选择器。

6.3用行为语句设计一个8位计数器,每次在时钟的上升沿,计数器加1,当计数器溢出时,自动从零开始重新计数。

计数器有同步复位端。

6.4设计一个4位移位寄存器。

6.5 initial语句与always语句的关键区别是什么?6.6分别用任务和函数描述一个4选1多路选择器。

verilog hdl 习题答案Verilog HDL 习题答案Verilog HDL(硬件描述语言)是一种用于描述数字电路的硬件描述语言,它被广泛应用于数字系统的设计和验证。

在学习Verilog HDL的过程中,练习题是非常重要的,通过解答习题可以加深对Verilog HDL语言的理解,并提高设计和编程的能力。

下面我们将为您提供一些Verilog HDL习题的答案,希望能够帮助您更好地掌握这门语言。

1. 请编写一个Verilog HDL模块,实现一个4位全加器。

module full_adder(input wire a, b, cin,output wire sum, cout);assign sum = a ^ b ^ cin;assign cout = (a & b) | (b & cin) | (a & cin);endmodule2. 请编写一个Verilog HDL模块,实现一个4位加法器。

module adder_4bit(input wire [3:0] a, b,output wire [3:0] sum);wire c0, c1, c2;full_adder fa0(a[0], b[0], 1'b0, sum[0], c0);full_adder fa1(a[1], b[1], c0, sum[1], c1);full_adder fa2(a[2], b[2], c1, sum[2], c2);full_adder fa3(a[3], b[3], c2, sum[3], );endmodule3. 请编写一个Verilog HDL模块,实现一个4位移位寄存器。

module shift_register(input wire clk, rst, shift,input wire [3:0] in,output wire [3:0] out);reg [3:0] reg_data;always @(posedge clk or posedge rst) beginif(rst)reg_data <= 4'b0;else if(shift)reg_data <= {reg_data[2:0], in[0]};elsereg_data <= in;endassign out = reg_data;endmodule以上是一些常见的Verilog HDL习题的答案,通过这些习题的练习,相信您对Verilog HDL语言的掌握会更加深入。

Verilog HDL简介及应用1. 概述Verilog HDL作为一种硬件描述语言,在数字电路设计领域中得到了广泛的应用。

本文将从Verilog HDL的定义、特点、基本语法、应用领域等方面进行介绍,以便读者对Verilog HDL有一个清晰的认识。

2. Verilog HDL的定义Verilog HDL即Verilog Hardware Description Language,是一种硬件描述语言,用于对数字电路进行描述、模拟和验证。

它是一种硬件描述语言,类似于C语言,但是它更关注于硬件层面的描述和设计。

3. Verilog HDL的特点(1)泛型性:Verilog HDL支持泛型编程,能够描述各种类型的数字电路,包括组合逻辑和时序逻辑。

(2)并发性:Verilog HDL支持并发描述,在描述数字电路时可以使用并发结构描述各个逻辑单元的交互关系。

(3)模块化:Verilog HDL支持模块化设计,模块之间可以进行层次化的描述和连接,使得复杂的电路可以被分解成多个独立的模块进行设计和验证。

4. Verilog HDL的基本语法(1)模块声明:使用module关键字声明一个模块,包括输入、输出和内部信号的声明。

(2)数据类型:Verilog HDL支持多种数据类型,包括bit、reg、wire、integer等。

(3)运算符:Verilog HDL支持各种运算符,包括赋值运算符、逻辑运算符、位运算符、条件运算符等。

(4)控制结构:Verilog HDL支持if-else、for循环、while循环等控制结构。

(5)并发语句:Verilog HDL使用always关键字和符号来描述并发执行的逻辑。

5. Verilog HDL的应用领域Verilog HDL广泛应用于数字电路的设计、仿真和验证之中,包括但不限于:(1)集成电路(IC)设计:Verilog HDL可用于描述芯片内部的数字电路,进行功能验证和时序分析。