CPU8086 的引脚及其功能

- 格式:pdf

- 大小:424.13 KB

- 文档页数:83

8086微处理器由哪几部分组成?各部分的功能是什么?【解】:按功能可分为两部分:总线接口单元BlU(BUSInterfaceUnit)和执行单元EU(ExecutionUnit)。

总线接口单元BlU是8086CPU在存储器和I/O设备之间的接口部件,负责对全部引脚的操作,即8086对存储器和I/O设备的全部操作都是由BIU完成的。

全部对外部总线的操作都必需有正确的地址和适当的限制信号,BIU中的各部件主要是围绕这个目标设计的。

它供应了16位双向数据总线,20位地址总线和若干条限制总线。

其具体任务是:负责从内存单元中预取指令,并将它们送到指令队列缓冲器暂存。

CPU执行指令时,总线接口单元要协作执行单元,从指定的内存单元或I/O端口中取出数据传送给执行单元,或者把执行单元的处理结果传送到指定的内存单元或I/O端口中。

执行单元EU中包含1个16位的运算器A1.U,8个16位的寄存器,1个16位标记寄存器FR,1个运算暂存器和执行单元的限制电路。

这个单元进行全部指令的说明和执行,同时管理上述有关的寄存器。

EU对指令的执行是从取指令操作码起先的,它从总线接口单元的指令队列缓冲器中每次取一个字节。

假如指令队列缓冲器中是空的,WJEU就要等待BIU通过外部总线从存储器中取得指令并送到EU,通过译码电路分析,发出相应限制吩咐,限制A1.U数据总线中数据的流向。

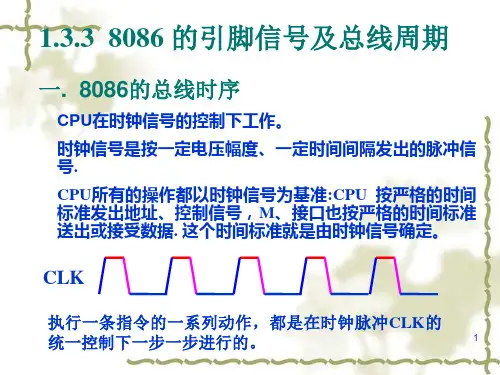

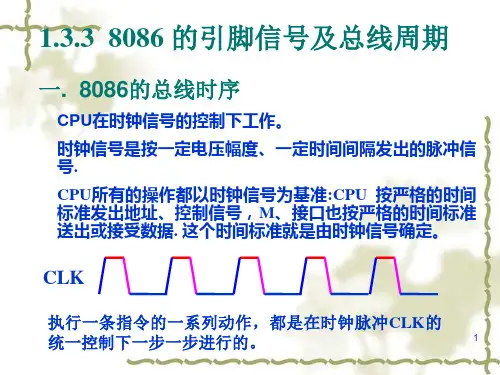

8086的基本总线周期为4个时钟周期,每个时钟周期间隔称为一个T 状态Tl 状态:BlU (总线接口部件)将RAM 或I/O 地址放在地址/数据夏用总线(A/D )上。

T2状态:读总线周期:A/D 总线为接收数据做准备。

变更线路的方向。

写总线周期:A/D 总线上形成待写的数据,且保持到总线周期的结束(T4)。

T3,T4:对于读或写总线周期,AD 总线上均为数据。

还有插入等待周期Tw:当RAV 或I/O 接口速度不够时,T3及T4之间可插入等待状态Tw βTi:当InU 无访问操作数和取指令的任务时,8086不执行总线操作,总线周期处于空闲状态TiO在最小模式中引脚定义GND ・ADl4ADBADUADllADl∙AD9ADt AD7 AD3 ADl 5 6 78 108086H CPU 12 13 14 15 16 17 18 19 20 403938 37 36 35 34 33 3231 302928 27 2625 24 2322 21⅛VCC(÷5V) 1.^^^AD1S AD16/S3 H AD11∕S4・AD18/S5 [ ■她9∕S⅜ 1■ ■^II BHE/S7 M ∙-IM/MXRD 一HO1.D(Wl∕GT0)⅞DA(⅞Q∕GT1)WR(1.OCK) h ⅛M∕iθ⅞) I OT∕R(Si) DEN(So) I 一迎(QSo) -IMTA(QSl) ι⅜TEST - I READY - IESET INTICHGND .AD15~AD0(AddressDataBUS>:16位地址/数据总线,分时复用。

8086处理器的外部引脚⏹8086是Intel系列的16位微处理器,芯片上有2.9万个晶体管,采用HMOS工艺制造,用单一的+5V电源,时钟频率为5MHz~10MHz。

8086有16根数据线和20根地址线,它既能处理16位数据,也能处理8位数据。

可寻址的内存空间为1MB。

⏹在8086推出不久,Intel推出了8088,和8086的区别是外部数据总线宽度不同。

8086处理器工作模式⏹8086/8088有两种工作模式☐最小模式◆只有一8086/8088CPU,所有的总线控制信号都由8086/8088产生,因此系统中的总线控制电路最少☐最大模式◆有两个或两个以上的CPU,一个为主CPU 8086/8088,另一个为协CPU 8087/80898086/8088工作在何种模式完全由硬件决定⏹引脚信号(以最小模式为例)☐数据和地址引脚☐读写控制引脚☐中断请求和响应引脚☐总线请求和响应引脚☐其它引脚1. 数据和地址引脚AD15~AD0(Address/Data)⏹地址/数据分时复用引脚,双向、三态⏹在访问存储器或外设的总线操作周期中,这些引脚在第一个时钟周期输出存储器或I/O端口的低16位地址A15~A0⏹其他时间用于传送16位数据D15~D0什么是分时复用?⏹一个引脚在不同的时刻具有两个甚至多个作用☐最常见的总线复用是数据和地址引脚复用☐总线复用的目的是为了减少对外引脚个数1. 数据和地址引脚A19/S6~A16/S3(Address/Status)⏹地址/状态分时复用引脚,输出、三态⏹这些引脚在访问存储器的第一个时钟周期输出高4位地址A19~A16⏹在访问外设的第一个时钟周期全部输出低电平无效⏹其他时间输出状态信号S6~S32. 读写控制引脚ALE(Address Latch Enable)⏹地址锁存允许,输出、三态、高电平有效⏹ALE引脚高有效时,表示复用引脚:AD15~AD0和A19/S6~A16/S3正在传送地址信息⏹由于地址信息在这些复用引脚上出现的时间很短暂,所以系统可以利用ALE引脚将地址锁存起来2. 读写控制引脚M/IO*(Input and Output/Memory )⏹I/O 或存储器访问,输出、三态⏹该引脚输出高电平时,表示CPU 将访问存储器,这时地址总线A 19~A 0提供20位存储器地址⏹该引脚输出低电平时,表示CPU 将访问I/O 端口,这时地址总线A 15~A 0提供16位I/O 口地址2. 读写控制引脚WR*(Write)⏹写控制,输出、三态、低电平有效⏹有效时,表示CPU正在写出数据给存储器或I/O端口RD*(Read)⏹读控制,输出、三态、低电平有效⏹有效时,表示CPU正在从存储器或I/O端口读入数据2. 读写控制引脚⏹M/IO*、WR*和RD*是最基本的控制信号⏹组合后,控制4种基本的总线周期总线周期M/IO*WR*RD*IO读低高低IO写低低高存储器读高高低存储器写高低高2. 读写控制引脚READY⏹存储器或I/O口就绪,输入、高电平有效⏹在总线操作周期中,8088 CPU会在第3个时钟周期的前沿测试该引脚☐如果测到高有效,CPU直接进入第4个时钟周期☐如果测到无效,CPU将插入等待周期Tw⏹CPU在等待周期中仍然要监测READY信号,有效则进入第4个时钟周期,否则继续插入等待周期Tw。