集成计数器寄存器

- 格式:doc

- 大小:53.50 KB

- 文档页数:3

北京科技大学实验报告学院:高等工程师学院专业:自动化(卓越计划)班级:自E181姓名:杨威学号:41818074 实验日期:2020 年5月26日一、实验名称:集成计数器及其应用1、实验内容与要求(1)用74161和必要逻辑门设计一个带进位输出的10进制计数器,采用同步置数方法设计;(2)用两个74161和必要的逻辑门设计一个带进位输出的60进制秒计数器;2、实验相关知识与原理(1)74161是常用的同步集成计数器,4位2进制,同步预置,异步清零。

引脚图功能表其中X。

3、10进制计数器(1)实验设计1)确定输入/输出变量输入变量:时钟信号CLK、复位信号CLRN;输出变量:计数输出QD、QC、QB、QA,进位输出RCO,显示译码输出OA、OB、OC、OD、OE、OF、OG2)计数范围:0000-10013)预置数值:00004)置数控制端LDN:计数到1001时输出低电平5)进位输出RCO:计数到1001时输出高电平画出如下状态转换表:CP QDQCQBQA0 00001 00012 00103 00114 01005 01016 01107 01117 10009 100110 0000(2)原理图截图仿真波形如下功能验证表格CLRN QD QC QB QA RCO0 0 0 0 0 01 0 0 0 1 01 0 0 1 0 01 0 0 1 1 01 0 1 0 0 01 0 1 0 1 01 0 1 1 0 01 0 1 1 1 01 1 0 0 0 01 1 0 0 1 11 0 0 0 0 04、60进制秒计数器(1)实验设计1)确定输入/输出变量输入变量:时钟信号CLK、复位信号CLRN;输出变量:计数十位输出QD2、QC2、QB2、QA2和计数个位输出QD1、QC1、QB1、QA1,进位输出RCO2)计数范围:0000 0000-0101 10013)预置数值:0000 00004)置数控制端LDN1(个位):计数到0101 1001时输出低电平5)清零端CLRN2(十位):计数到0110时输出低电平6)ENT:个位计数到1001时输出高电平7)进位输出RCO:计数到1001时输出高电平画出如下状态转换表CP QD2QC2QB2QA2QD1QC1QB1QA1CPQD2QC2QB2QA2QD1QC1QB1QA1CPQD2QC2QB2QA2QD1QC1QB1QA10 0000 0000 20 0010 0000 40 0100 00001 0000 0001 21 0010 0001 41 0100 00012 0000 0010 22 0010 0010 42 0100 00103 0000 0011 23 0010 0011 43 0100 00114 0000 0100 24 0010 0100 44 0100 01005 0000 0101 25 0010 0101 45 0100 01016 0000 0110 26 0010 0110 46 0100 01107 0000 0111 27 0010 0111 47 0100 01118 0000 1000 28 0010 1000 48 0100 10009 0000 1001 29 0010 1001 49 0100 100110 0001 0000 30 0011 0000 50 0101 000011 0001 0001 31 0011 0001 51 0101 000112 0001 0010 32 0011 0010 52 0101 001013 0001 0011 33 0011 0011 53 0101 001114 0001 0100 34 0011 0100 54 0101 010015 0001 0101 35 0011 0101 55 0101 010116 0001 0110 36 0011 0110 56 0101 011017 0001 0111 37 0011 0111 57 0101 011118 0001 1000 38 0011 1000 58 0101 100019 0001 1001 39 0011 1001 59 0101 100160 0000 0000 (2)设计原理图截图(3)实验仿真仿真波形:仿真结果表:5、实验思考题:(1)总结任意模计数器的设计方法。

数字电路-实验指导书汇总TPE-D型系列数字电路实验箱数字逻辑电路实验指导书实验⼀门电路逻辑功能及测试实验⼆组合逻辑电路(半加器、全加器及逻辑运算)实验三时序电路测试及研究实验四集成计数器及寄存器实验⼀门电路逻辑功能及测试⼀、实验⽬的1、熟悉门电路逻辑功能。

2、熟悉数字电路实验箱及⽰波器使⽤⽅法。

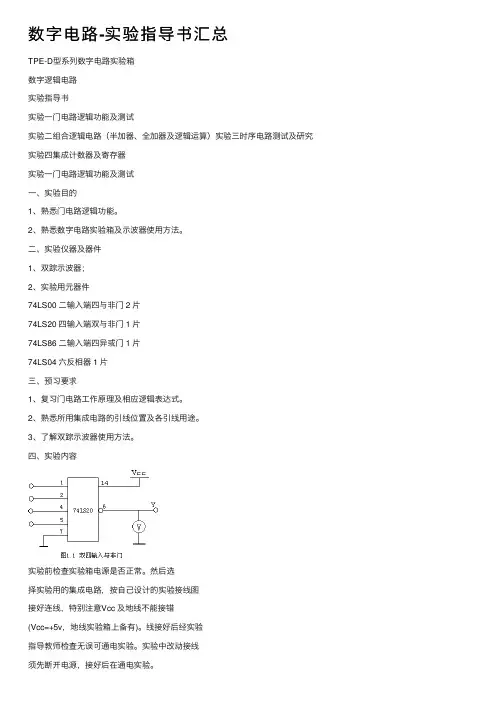

⼆、实验仪器及器件1、双踪⽰波器;2、实验⽤元器件74LS00 ⼆输⼊端四与⾮门 2 ⽚74LS20 四输⼊端双与⾮门 1 ⽚74LS86 ⼆输⼊端四异或门 1 ⽚74LS04 六反相器 1 ⽚三、预习要求1、复习门电路⼯作原理及相应逻辑表达式。

2、熟悉所⽤集成电路的引线位置及各引线⽤途。

3、了解双踪⽰波器使⽤⽅法。

四、实验内容实验前检查实验箱电源是否正常。

然后选择实验⽤的集成电路,按⾃⼰设计的实验接线图接好连线,特别注意Vcc 及地线不能接错(Vcc=+5v,地线实验箱上备有)。

线接好后经实验指导教师检查⽆误可通电实验。

实验中改动接线须先断开电源,接好后在通电实验。

1、测试门电路逻辑功能⑴选⽤双四输⼊与⾮门74LS20 ⼀只,插⼊⾯包板(注意集成电路应摆正放平),按图接线,输⼊端接S1~S4(实验箱左下⾓的逻辑电平开关的输出插⼝),输出端接实验箱上⽅的LED 电平指⽰⼆极管输⼊插⼝D1~D8中的任意⼀个。

⑵将电平开关按表置位,分别测出输出逻辑状态值及电压值填表。

表2、异或门逻辑功能测试⑴选⼆输⼊四异或门电路74LS86,按图接线,输⼊端1、2、4、5 接电平开关输出插⼝,输出端A 、B 、Y 接电平显⽰发光⼆极管。

⑵将电平开关按表的状态转换,将结果填⼊表中。

表3、逻辑电路的逻辑关系⑴⽤ 74LS00 双输⼊四与⾮门电路,按图、图接线,将输⼊输出逻辑关系分别填⼊表,表中。

⑵写出两个电路的逻辑表达式。

4、逻辑门传输延迟时间的测量⽤六反相器(⾮门)按图接线,输⼊80KHz 连续脉冲(实验箱脉冲源),⽤双踪⽰波器测输⼊、输出相位差。

寄存器,计数器寄存器是什么

寄存器的功能是存储⼆进制代码,

它是由具有存储功能的触发器组合起来构成的。

⼀个触发器可以存储1位⼆进制代码,

故存放n位⼆进制代码的寄存器,

需⽤n个触发器来构成。

寄存器是中央处理器内的组成部份。

寄存器是有限存贮容量的⾼速存贮部件,

它们可⽤来暂存指令、数据和位址。

在中央处理器的控制部件中,

包含的寄存器有指令寄存器(IR)和程序计数器(PC)。

在中央处理器的算术及逻辑部件中,包含的寄存器有累加器(ACC)。

计数器是什么

计数器是⼀种最简单基本的运算,

计数器就是实现这种运算的逻辑电路,

计数器在数字系统中主要是对脉冲的个数进⾏计数,

以实现测量、计数和控制的功能,

同时兼有分频功能,

计数器是由基本的计数单元和⼀些控制门所组成,

计数单元则由⼀系列具有存储信息功能的各类触发器构成,

这些触发器有RS触发器、T触发器、D触发器及JK触发器等。

计数器在数字系统中应⽤⼴泛,

如在电⼦计算机的控制器中对指令地址进⾏计数,

以便顺序取出下⼀条指令,

在运算器中作乘法、除法运算时记下加法、减法次数,

⼜如在数字仪器中对脉冲的计数等等。

计数器可以⽤来显⽰产品的⼯作状态,

⼀般来说主要是⽤来表⽰产品已经完成了多少份的折页配页⼯作。

它主要的指标在于计数器的位数,常见的有3位和4位的。

很显然,3位数的计数器最⼤可以显⽰到999,4位数的最⼤可以显⽰到9999。

计数器只能作为计数使⽤,寄存器可以存放任何数值,寄存器可以当计数器⽤,反之不能。

集成块的分类一、引言集成块是一种电子元器件,由多个功能电路组合而成,在现代电子产品中广泛应用。

随着科技的不断发展,集成块的种类也越来越多样化。

本文将介绍集成块的分类。

二、数字集成块数字集成块是由数字逻辑门组合而成的电路。

数字逻辑门包括与门、或门、非门等等。

常见的数字集成块有计数器、寄存器、加法器等等。

1. 计数器计数器是一种能够按照一定规律进行计数的电路。

它通常由触发器和逻辑门组合而成,可以实现二进制计数和十进制计数。

2. 寄存器寄存器是一种能够存储数据的电路。

它可以将输入数据保存在内部,并在需要时输出这些数据。

寄存器通常由触发器和选通逻辑组合而成。

3. 加法器加法器是一种能够对两个二进制数进行加法运算的电路。

它通常由半加器和全加器组合而成,可以实现多位二进制数相加。

三、模拟集成块模拟集成块是由模拟电路组合而成的电路。

模拟电路包括放大器、滤波器、振荡器等等。

常见的模拟集成块有运放、比较器、振荡电路等等。

运放是一种能够将输入信号放大的电路。

它通常由差分放大器和反馈电路组合而成,可以实现不同增益和频率响应的信号放大。

2. 比较器比较器是一种能够对两个信号进行比较的电路。

它可以将一个信号与一个参考电平进行比较,并输出高或低电平。

3. 振荡电路振荡电路是一种能够产生周期性波形的电路。

它通常由反馈网络和放大器组合而成,可以实现正弦波、方波、三角波等不同类型的波形输出。

四、混合集成块混合集成块是由数字和模拟电路组合而成的电路。

它可以同时处理数字信号和模拟信号,广泛应用于通信、控制系统等领域。

常见的混合集成块有DAC(数模转换器)、ADC(模数转换器)、PLL(锁相环)等等。

1. DACDAC是一种能够将数字信号转换为模拟信号输出的电路。

它通常由数字信号处理电路和模拟输出电路组合而成,可以实现高精度的模拟信号输出。

2. ADCADC是一种能够将模拟信号转换为数字信号输出的电路。

它通常由模拟输入电路和数字信号处理电路组合而成,可以实现高精度的模拟信号采集。

一、实验目的1. 理解时序逻辑电路的基本概念和工作原理。

2. 掌握时序逻辑电路的设计方法和测试方法。

3. 熟悉常用中规模集成计数器和寄存器的逻辑功能和使用方法。

二、实验原理时序逻辑电路是指其输出不仅取决于当前输入信号,还取决于电路的过去状态。

本实验主要涉及计数器和寄存器两种时序逻辑电路。

计数器:计数器是一种能够对输入脉冲进行计数的时序逻辑电路。

常见的计数器有二进制计数器、十进制计数器和可编程计数器等。

寄存器:寄存器是一种用于存储二进制信息的时序逻辑电路。

常见的寄存器有D型寄存器、移位寄存器和计数寄存器等。

三、实验设备1. 数字电子技术实验箱2. 示波器3. 信号源4. 集成芯片:74LS163、74LS00、74LS20等四、实验内容1. 计数器设计(1)设计一个4位二进制加法计数器,实现0-15的循环计数。

(2)设计一个10进制计数器,实现0-9的循环计数。

2. 寄存器设计(1)设计一个D型寄存器,实现数据的存储和读取。

(2)设计一个移位寄存器,实现数据的右移和左移。

3. 时序逻辑电路测试(1)测试计数器的计数功能。

(2)测试寄存器的存储和读取功能。

五、实验步骤1. 计数器设计(1)根据计数器的功能要求,设计电路图。

(2)根据电路图,选择合适的集成芯片。

(3)搭建实验电路。

(4)测试计数器的计数功能。

2. 寄存器设计(1)根据寄存器的功能要求,设计电路图。

(2)根据电路图,选择合适的集成芯片。

(3)搭建实验电路。

(4)测试寄存器的存储和读取功能。

3. 时序逻辑电路测试(1)测试计数器的计数功能。

(2)测试寄存器的存储和读取功能。

六、实验结果与分析1. 计数器设计(1)4位二进制加法计数器能够实现0-15的循环计数。

(2)10进制计数器能够实现0-9的循环计数。

2. 寄存器设计(1)D型寄存器能够实现数据的存储和读取。

(2)移位寄存器能够实现数据的右移和左移。

3. 时序逻辑电路测试(1)计数器的计数功能正常。

数字电路中的计数器和移位寄存器在数字电路中,计数器和移位寄存器是两个常用的元件,用于实现不同的功能。

计数器可以用于计算输入信号的频率、计数场合和控制电路等。

移位寄存器则用于数据的移位和存储。

本文将详细介绍计数器和移位寄存器的原理、应用以及设计注意事项。

一、计数器计数器是一种重要的数字电路元件,广泛应用于各种电子设备中。

计数器按照工作原理的不同,可以分为同步计数器和异步计数器。

1. 同步计数器同步计数器是一种在时钟信号的控制下进行计数的计数器。

它使用时钟信号来同步所有的触发器,保证在时钟边沿进行计数操作。

同步计数器的输入信号可以是来自外部的信号,也可以是内部产生的。

同步计数器通常由触发器级联构成,每一个触发器代表计数器中的一个位。

当所有的触发器都到达最大计数值时,计数器就会归零重新开始计数。

2. 异步计数器异步计数器是一种不需要时钟信号进行计数的计数器。

它的计数操作是以输入信号的变化边沿触发的。

异步计数器通常由触发器和门电路组成,输入信号的变化会通过门电路产生控制信号,触发器根据控制信号进行计数操作。

异步计数器在工作时需要特别注意输入信号的稳定性和时序关系,以确保计数的准确性。

二、移位寄存器移位寄存器是一种可以实现数据的移位和存储的元件。

移位寄存器可以分为串行移位寄存器和并行移位寄存器两种。

1. 串行移位寄存器串行移位寄存器是一种将数据逐位进行移位操作的寄存器。

它可以将输入数据从一个端口输入,并从另一个端口输出。

串行移位寄存器通常由触发器和移位电路组成,触发器用于存储数据,移位电路用于实现数据的移位操作。

串行移位寄存器的移位操作可以是向左移位或向右移位。

2. 并行移位寄存器并行移位寄存器是一种同时对多个数据位进行移位操作的寄存器。

它可以将输入数据从一个端口输入,并从另一个端口输出。

并行移位寄存器通常由多个触发器构成,每个触发器用于存储一个数据位。

通过控制信号,可以将输入数据同时存储到各个触发器中,并且可以同时从各个触发器中读取数据。

集成计数器及寄存器的实验原理引言集成计数器和寄存器是数字电路中非常重要的组件,它们用于进行数字信号的计数与存储。

在本实验中,我们将探讨集成计数器和寄存器的原理以及它们在实际电路中的应用。

一、集成计数器的原理1.1 什么是集成计数器集成计数器是一种能够计数连续数字信号的电子器件。

它可以根据输入端的时钟信号来完成计数操作,输出端则会按照特定的规律输出计数结果。

1.2 集成计数器的工作原理集成计数器通常是由触发器构成的。

触发器是一种存储单元,它能够存储一个二进制位,并在时钟信号的作用下改变存储状态。

集成计数器的工作原理可以通过以下步骤来理解:1.初始状态下,集成计数器的触发器处于复位状态,输出端的计数值为0。

2.当时钟信号来临时,触发器将存储状态改变为下一个二进制数值,输出端的计数值也随之改变。

3.当再次收到时钟信号时,触发器再次改变存储状态,计数值也相应地改变。

4.不断重复以上步骤,集成计数器可以持续计数,输出端的计数值会随着每个时钟周期递增。

1.3 集成计数器的分类集成计数器可以根据工作模式和计数范围进行分类。

常见的集成计数器包括二进制计数器、十进制BCD计数器、环形计数器等。

二、寄存器的原理2.1 什么是寄存器寄存器是一种能够存储多个二进制数据的器件。

它可以将输入的数据暂时存储起来,并在需要的时候提供给其他电路使用。

2.2 寄存器的工作原理寄存器通常是由多个触发器构成的。

每个触发器能够存储一个二进制位,这样多个触发器组合起来就能够存储更多的二进制数据。

寄存器的工作原理可以通过以下步骤来理解:1.初始状态下,所有触发器处于复位状态,寄存器中的数据为0。

2.当输入信号到达时,触发器将存储状态改变为对应的输入数据。

3.在需要时,寄存器的输出端将提供存储的数据给其他电路使用。

4.如果需要修改寄存器中的数据,可以将新的数据输入到寄存器中,触发器会相应地改变存储状态。

2.3 寄存器的分类寄存器可以根据功能和位数进行分类。

寄存器计数器及应用寄存器计数器是一种特殊的寄存器,用于记录程序执行过程中特定事件的次数。

它通常用于循环控制、测量时间和计算频率等应用中。

在计算机系统中,寄存器计数器的作用非常重要,下面将详细介绍寄存器计数器的原理、工作方式以及常见的应用。

一、寄存器计数器的原理及工作方式寄存器计数器通常由多个比特位组成,可以用于记录不同范围的计数值。

其工作方式为:1. 初始化:在使用寄存器计数器之前,需要先对其进行初始化操作,将其计数值置为初始值,一般为0。

2. 计数:寄存器计数器每次工作周期都会执行一次计数操作。

计数器的值会根据特定的规则进行更新。

例如,常见的寄存器计数器有递增计数器和递减计数器。

递增计数器在每个工作周期将计数值加一,递减计数器则将计数值减一。

3. 溢出检测:寄存器计数器往往有一个可以检测其溢出状态的位,通常称为溢出标志。

当计数器的值超过其容量范围时,溢出标志位将被置为1,表示计数器的值溢出。

溢出标志位的状态可以被程序读取,并根据实际需要采取相应的操作。

二、寄存器计数器的常见应用1. 循环控制:在程序设计中,循环结构是一种非常常见的控制结构,它可以重复执行一定次数的操作。

寄存器计数器可以用于实现循环控制的计数功能。

程序可以通过读取计数器的值来确定循环次数,并在每次循环结束时更新计数器的值。

当计数器的值达到设定的循环次数时,循环将结束。

2. 测量时间:寄存器计数器可以用于测量程序或操作的执行时间。

计数器的值可以基于程序的时钟信号进行更新,每个时钟周期更新一次。

通过读取计数器的值或计算计数器值的变化量,可以确定程序或操作所花费的时间。

3. 计算频率:寄存器计数器还可以用于测量信号的频率。

当输入信号发生变化时,计数器的值会随之变化。

通过统计计数器的溢出次数或计数器值的变化量,可以计算出输入信号的频率。

4. 脉冲计数:寄存器计数器可以用于脉冲计数应用。

脉冲计数就是统计接收到的脉冲信号的数量。

当每接收到一个脉冲信号时,计数器的值加一。

实验五时序逻辑电路(计数器和寄存器)-实验报告一、实验目的1.掌握同步计数器设计方法与测试方法。

2.掌握常用中规模集成计数器的逻辑功能和使用方法。

二、实验设备设备:THHD-2型数字电子计数实验箱、示波器、信号源器件:74LS163、74LS00、74LS20等。

三、实验原理和实验电路1.计数器计数器不仅可用来计数,也可用于分频、定时和数字运算。

在实际工程应用中,一般很少使用小规模的触发器组成计数器,而是直接选用中规模集成计数器。

2.(1) 四位二进制(十六进制)计数器74LS161(74LS163)74LSl61是同步置数、异步清零的4位二进制加法计数器,其功能表见表。

74LSl63是同步置数、同步清零的4位二进制加法计数器。

除清零为同步外,其他功能与74LSl61相同。

二者的外部引脚图也相同,如图所示。

表 74LSl61(74LS163)的功能表3.集成计数器的应用——实现任意M进制计数器一般情况任意M 进制计数器的结构分为3类,第一类是由触发器构成的简单计数器。

第二类是由集成二进制计数器构成计数器。

第三类是由移位寄存器构成的移位寄存型计数器。

第一类,可利用时序逻辑电路的设计方法步骤进行设计。

第二类,当计数器的模M 较小时用一片集成计数器即可以实现,当M 较大时,可通过多片计数器级联实现。

两种实现方法:反馈置数法和反馈清零法。

第三类,是由移位寄存器构成的移位寄存型计数器。

4.实验电路: 十进制计数器六进制扭环计数器具有方波输出的六分频电路74LS161(74LS163)12345681514131211109V CCGND716R DCP A B C D EP RCOQ AQ BQ CQ DETLD同步置数法同步清零法图 74LS161(74LS163)外部引脚图四、实验内容及步骤1.集成计数器实验(1)按电路原理图使用中规模集成计数器74LS163和与非门74LS00,连接成一个同步置数或同步清零十进制计数器,并将输出连接至数码管或发光二极管。

实验四:时序逻辑电路(集成寄存器和计数器)一、实验目的:1.熟悉中规模集成计数器的逻辑功能和使用方法;掌握用集成计数器组成任意模数为M的计数器。

2.加深理解移位寄存器的工作原理及逻辑功能描述;熟悉中规模集成移位寄存器的逻辑功能和使用方法;掌握用移位寄存器组成环形计数器的基本原理和设计方法。

二、知识点提示和实验原理:㈠计数器:计数器的应用十分广泛,不仅可用来计数,也可用于分频、定时和数字运算。

计数器种类繁多,根据计数体制不同,计数器可分为二进制计数器和非二进制计数器两大类。

在非二进制计数器中,最常用的是十进制计数器,其他的称为任意进制计数器。

根据计数器的增减趋势的不同,计数器可分为加法计数器和减法计数器。

根据计数脉冲引入方式不同,计数又可分为同步计数器和异步计数器。

在实际工程应用中,一般很少使用小规模的触发器组成计数器,而是直接选用中规模集成计数器。

用集成计数器实现任意M进制计数器:一般情况任意M进制计数器的结构分为3类,第一种是由集成二进制计数器构成,第二种为移位寄存器构成的移位寄存型计数器,第三种为集成触发器构成的简单专用计数器。

当M较小时通过对集成计数器的改造即可以实现,当M较大时,可通过多片计数器级联实现。

实现方法:(1)当所需计数器M值小于集成计数器本身二进制计数最大值时,用置数(清零)法构成任意进制计数器;⑵当所需计数器M值大于集成计数器本身二进制计数最大值时,可采用级联法构成任意进制计数器。

常用的中规模集成器件:4位二进制计数器74HC161,十进制计数器74HC160,加减计数器74HC191、74HC193,异步计数器74LS290。

所有芯片的电路、功能表见教材。

㈡寄存器:寄存器用来寄存二进制信息,将一些待运算的数据、代码或运算的中间结果暂时寄存起来。

按功能划分,寄存器可分为数码寄存器和移位寄存器两大类。

数码寄存器用来存放数码,一般具有接收数码、保持并清除原有数码等功能,电路结构和工作原理郡比较简单。

计数器与寄存器原理解析计数器和寄存器是数字电路中常见的组件,具有重要的作用和原理。

本文将对计数器和寄存器的原理进行解析,并深入探讨其在数字电路中的应用。

一、计数器的原理解析计数器是一种特殊的组合逻辑电路,用于生成一系列连续的数字。

它由触发器和逻辑门组成,其中触发器用于存储和转移数据,而逻辑门用于控制触发器的状态。

计数器的工作原理基于触发器的状态转移。

触发器根据输入信号的变化(如时钟信号),在两个状态之间进行切换。

常见的触发器有D触发器、JK触发器和T触发器等。

计数器根据触发器的状态转移规律实现数字的累加或减少。

当计数器的触发器达到一个特定的状态时,会产生一个输出信号,称为溢出信号。

溢出信号可以用于控制其他电路的工作状态。

二、计数器的应用计数器在数字电路中具有广泛的应用,如频率分频器、时序控制器和计时器等。

1. 频率分频器频率分频器是一种常见的应用,用于将输入信号的频率分频为较低的频率。

通过将计数器的输出信号与输入信号进行比较,当计数器达到预设的值时,输出一个脉冲信号,从而实现频率分频的效果。

2. 时序控制器时序控制器是数字系统中用来控制电路运行顺序的重要组件。

计数器可以用来实现时序控制器,通过控制计数器的工作模式,可以实现不同的时序控制功能。

3. 计时器计时器是用于测量时间间隔的重要设备,如秒表和定时器等。

计数器可以用来实现计时器的功能,通过计数器的工作原理,可以精确计算时间间隔。

三、寄存器的原理解析寄存器是一种存储器件,用于存储和传输数据。

它由多个触发器组成,每个触发器都可以存储一个比特的数据。

寄存器的工作原理基于触发器的状态。

当输入数据进入寄存器时,触发器将数据存储起来,并根据时钟信号的变化,将存储的数据传输到输出端口。

寄存器通常由多个比特组成,例如8位寄存器和16位寄存器等。

不同位数的寄存器可以存储和处理不同位数的数据。

四、寄存器的应用寄存器在数字电路和微处理器中具有广泛的应用,如存储数据、地址和指令等。

实验五 集成计数器寄存器

一、实验目的

1.熟悉集成计数器逻辑功能和各控制端作用。

2.掌握计数器使用方法。

二、实验仪器及材料

1. 双踪示波器

2. 器件 74LS290 十进制计数器 2片 74LS00 二输入端四与非门1片。

三、实验内容及步骤

1.集成计数器74LS290功能测试。

74LS290是二一五一十进制异步计数器。

逻辑简图为图5.1所示:

74LS290具有下述功能:

直接置0(R0(1).R0(2)=1),直接置9(S 9(1).S 9(2)=1)

二进制计数(CP1输入Q A 输出),五进制计数(CP 2输入Q D Q C Q B 输出) 十进制计数(两种接法如图5.2A 、B 所示)

按芯片引脚图分别测试上述功能,并列入表5.1、表5.2、表5.3中。

R R 1) 2)

图5.1 74LS290逻辑图

(A)十进制

(B)二一五混合进制

图5.2 十进制计数器

2.分别用2片74LS290计算器级连成二一五混合进制、十进制计数器。

(1)画出连线电路图。

(2)按图接线,并将输出端接到发光二极管的相应输入端,用单脉作为输入脉冲验证是否正确。

(3)画出四位十进制计数器连接图并总结多级计数连规律。

表5.1 功能表

表5.2 二一五混合进制表5.3 十进制

四、实验报告

1.整理实验内容和各实验数据。

2.画出实验内容1、2所要求的电路图及波形图。

3.总结计数器使用特点。

4.。