DSPADC程序中文说明

- 格式:docx

- 大小:7.71 KB

- 文档页数:1

TMS320x280xDSP模数转换器(ADC)参考指南PreliminaryTMS320x280x DSP 模数转换器(ADC)参考指南文献编号:ZHCU0042004年11月–修订2005年6月Preliminary内容目 (3)序7 1模数转换器(ADC) (11)1.1 (12)1.2141.2.1顺序采样模式 (15)1.2.2151.3不间断自动定序模式 (20)1.3.1序列发生器启动/停止模式(具有多个时序触发器的序列发生器启动/停止操作)221.3.2同步采样模式 (24)1.3.3输入触发器说明 (24)1.3.4定序转换期间的中断操作251.4ADC时钟预分频器 (26)1.4.1ADC模块时钟和采样频率271.5低功率模式 (27)1.6281.7序列发生器覆盖功能 (28)1.8内部/外部参考电压选择281.9 (30)2ADC寄存器332.1ADC控制寄存器 (34)2.2最大转换信道数寄存器(ADCMAXCONV)372.3自动定序状态寄存器(ADCASEQSR) (39)2.4ADC状态和标志寄存器(ADCST)392.5ADC参考选择寄存器(ADCREFSEL) (40)2.6ADC偏移微调寄存器(ADCOFFTRIM)412.7ADC输入信道选择定序控制寄存器 (41)2.8ADC转换结果缓冲寄存器(ADCRESULTn) (42)A修订历史记录45Preliminary附图目录1-1ADC模块的结构图 (13)1-2顺序采样模式(SMODE=0) (15)1-3同步采样模式(SMODE=1) (15)1-4级联模式下自动定序的ADC结构图 (16)1-5带双序列发生器的自动定序的ADC结构图 (17)1-6不间断自动定序模式的流程图 (22)1-7ePWM触发器启动序列发生器的示例 (23)1-8定序转换期间的中断操作 (26)1-9ADC内核时钟和采样保持(S/H)时钟 (27)1-10到ADC的时钟链 (27)1-11外部参考的外部偏置 (29)1-12 (30)1-13采样0-V参考电压的理想代码分布 (31)2-1ADC控制寄存器1(ADCTRL1)(地址偏移00h) (34)2-2ADC控制寄存器2(ADCTRL2)(地址偏移01h) (35)2-3ADC控制寄存器3(ADCTRL3)(地址偏移18h) (37)2-4最大转换信道数寄存器(ADCMAXCONV)(偏移地址02h)(38)2-5自动定序状态寄存器(ADCASEQSR)(地址偏移07h) (39) 2-6ADC状态和标志寄存器(ADCST)(地址偏移19h) (40)2-7ADC参考选择寄存器(ADCREFSEL)(地址偏移1Ch) (40)2-8ADC偏移微调寄存器(ADCOFFTRIM)(地址偏移1Dh) (41) 2-9ADC输入信道选择定序控制寄存器(ADCCHSELSEQ1)(地址偏移03h) (41)2-10ADC输入信道选择定序控制寄存器(ADCCHSELSEQ2)(地址偏移04h) (41)2-11ADC输入信道选择定序控制寄存器(ADCCHSELSEQ3)(地址偏移05h) (41)2-12ADC输入信道选择定序控制寄存器(ADCCHSELSEQ4)(地址偏移06h) (42)2-13ADC转换结果缓冲寄存器(ADCRESULTn)-(地址0x7108-0x7117) (42)2-14ADC转换结果缓冲寄存器(ADCRESULTn)-(地址0x0B00-0x0B0F) (42)Preliminary附表目录1-1ADC寄存器 (13)1-2单一工作模式和级联工作模式比较 (18)1-3ADCCHSELSEQn寄存器的值(MAX_CONV1设置为6) (21) 1-4ADCCHSELSEQn的值(MAX_CONV1设置为2) (23)1-5 (24)1-6输入触发器 (24)1-7到ADC的时钟链 (27)1-8 (27)2-1ADC控制寄存器1(ADCTRL1)字段说明 (34)2-2ADC控制寄存器2(ADCTRL2)字段说明 (35)2-3ADC控制寄存器3(ADCTRL3)字段说明 (37)2-4最大转换信道数寄存器(ADCMAXCONV)字段说明 (38)2-5各种转换数的MAX_CONV1的位选择 (38)2-6自动定序状态寄存器(ADCASEQSR)字段说明 (39)2-7活动序列发生器的状态 (39)2-8ADC状态和标志寄存器(ADCST)字段说明 (40)2-9ADC参考选择寄存器(ADCREFSEL)字段说明 (41)2-10ADC偏移微调寄存器(ADCOFFTRIM)字段说明 (41)2-11CONVnn位值和所选的ADC输入信道 (42)PreliminaryPreliminary序言ZHCU004–2004年11月–修订2005年6月请先阅读关于本手册本文档描述了TMS320x280x数字信号处理器(DSP)上可用的模数转换器(ADC)的功能和操作。

32位高性能数字信号处理器内部AD的精度校正方法TMS 320F2812是TI公司设计的一款用于工业控制、机床控制等高精度应用领域的DSP。

它是一款最高主频可达150MHZ的32位高性能数字信号处理器(DSP),内部集成了16路12位ADC转换模块。

该模块内置两个采样保持器(S/H-A、S/H-B),有自动排序功能,且其转换时间最短可在100ns以内进行过采样处理。

但在实际应用中发现,即使使用了过采样处理,TMS 320F2812内部ADC转换器的转换结果仍存在较大误差,在测控系统中,这会降低控制回路的控制精度,导致运行结果出现一定的偏差。

本文提出一种提高ADC转换精度的方法,使得TMS 320F2812的ADC转换精度得到有效提高,能让TMS 320F2812更好的满足高精度控制系统的需要。

适用于控制领域的TMS320C2000系列DSP内部集成了ADC转换模块,为进一步提高其转换精度,实现更精确控制,提出对ADC转换模块存在的增益误差和偏移误差采用加参考信号与编程算法结合的方法进行校正偿,给出了具体的校正方案。

并在F2812芯片上进行了验证。

实验结果表明,此方法起到了补偿误差的作用,能够大幅度提高转换精度。

1、ADC转换器的误差分析计算机测控系统在测量数据时不可避免的会有随机误差和系统误差,其中随机误差一般是由各种干扰引入的,可通过统计的方法在数据处理中消除,系统误差一般在数值上较大,对测量正确度影响较大,且不能在数据处理中消除,必须要找出来并通过一定的方法进行消除。

对于线性系统,常用的A/D转换器主要存在偏移误差和增益误差,这两种误差都属于系统误差。

首先我们介绍一下什么偏移误差?什么是增益误差?增益误差是指从负满量程转为正满量程输入时实际斜率与理想斜率之差。

偏移误差是指对AD转换器采用零伏差动输入时实际值与理想值之间的差异。

增益和偏移增益误差通常是AD转换器中主要的误差源。

为了减小增益误差和偏移误差,可采取检测其值,然后对其进行修正的方法。

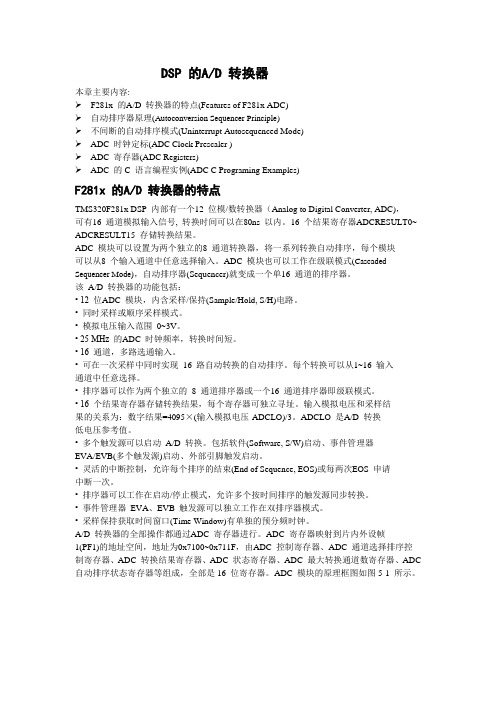

DSP 的A/D 转换器本章主要内容:➢ F281x 的A/D 转换器的特点(Features of F281x ADC)➢ 自动排序器原理(Autoconversion Sequencer Principle)➢ 不间断的自动排序模式(Uninterrupt Autosequenced Mode)➢ ADC 时钟定标(ADC Clock Prescaler )➢ ADC 寄存器(ADC Registers)➢ ADC 的C 语言编程实例(ADC C Programing Examples)F281x 的A/D 转换器的特点TMS320F281x DSP 内部有一个12 位模/数转换器(Analog to Digital Converter, ADC),可有16 通道模拟输入信号, 转换时间可以在80ns 以内。

16 个结果寄存器ADCRESULT0~ ADCRESULT15 存储转换结果。

ADC 模块可以设置为两个独立的8 通道转换器,将一系列转换自动排序,每个模块可以从8 个输入通道中任意选择输入。

ADC 模块也可以工作在级联模式(Cascaded Sequencer Mode),自动排序器(Sequencer)就变成一个单16 通道的排序器。

该A/D 转换器的功能包括:• 12 位ADC 模块,内含采样/保持(Sample/Hold, S/H)电路。

• 同时采样或顺序采样模式。

• 模拟电压输入范围0~3V。

• 25 MHz 的ADC 时钟频率,转换时间短。

• 16 通道,多路选通输入。

• 可在一次采样中同时实现16 路自动转换的自动排序。

每个转换可以从1~16 输入通道中任意选择。

• 排序器可以作为两个独立的8 通道排序器或一个16 通道排序器即级联模式。

• 16 个结果寄存器存储转换结果,每个寄存器可独立寻址。

输入模拟电压和采样结果的关系为:数字结果=4095×(输入模拟电压-ADCLO)/3。

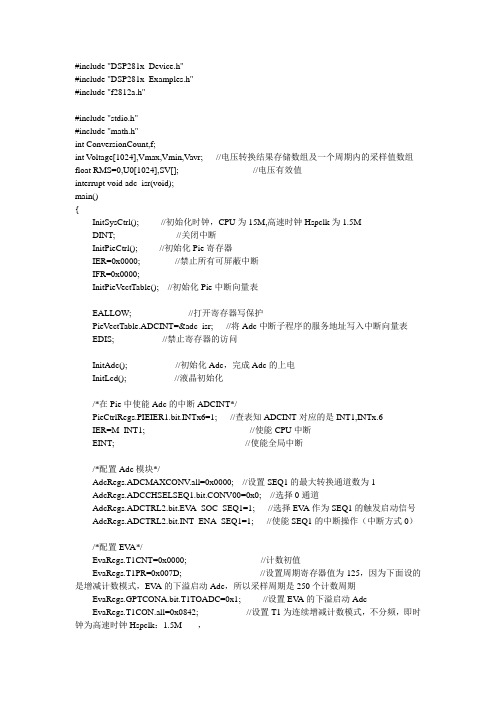

#include "DSP281x_Device.h"#include "DSP281x_Examples.h"#include "f2812a.h"#include "stdio.h"#include "math.h"int ConversionCount,f;int V oltage[1024],Vmax,Vmin,Vavr; //电压转换结果存储数组及一个周期内的采样值数组float RMS=0,U0[1024],SV[]; //电压有效值interrupt void adc_isr(void);main(){InitSysCtrl(); //初始化时钟,CPU为15M,高速时钟Hspclk为1.5MDINT; //关闭中断InitPieCtrl(); //初始化Pie寄存器IER=0x0000; //禁止所有可屏蔽中断IFR=0x0000;InitPieVectTable(); //初始化Pie中断向量表EALLOW; //打开寄存器写保护PieVectTable.ADCINT=&adc_isr; //将Adc中断子程序的服务地址写入中断向量表EDIS; //禁止寄存器的访问InitAdc(); //初始化Adc,完成Adc的上电InitLcd(); //液晶初始化/*在Pie中使能Adc的中断ADCINT*/PieCtrlRegs.PIEIER1.bit.INTx6=1; //查表知ADCINT对应的是INT1,INTx.6IER=M_INT1; //使能CPU中断EINT; //使能全局中断/*配置Adc模块*/AdcRegs.ADCMAXCONV.all=0x0000; //设置SEQ1的最大转换通道数为1AdcRegs.ADCCHSELSEQ1.bit.CONV00=0x0; //选择0通道AdcRegs.ADCTRL2.bit.EV A_SOC_SEQ1=1; //选择EV A作为SEQ1的触发启动信号AdcRegs.ADCTRL2.bit.INT_ENA_SEQ1=1; //使能SEQ1的中断操作(中断方式0)/*配置EVA*/EvaRegs.T1CNT=0x0000; //计数初值EvaRegs.T1PR=0x007D; //设置周期寄存器值为125,因为下面设的是增减计数模式,EV A的下溢启动Adc,所以采样周期是250个计数周期EvaRegs.GPTCONA.bit.T1TOADC=0x1; //设置EV A的下溢启动AdcEvaRegs.T1CON.all=0x0842; //设置T1为连续增减计数模式,不分频,即时钟为高速时钟Hspclk:1.5M ,ConversionCount=0;while(1) //等待中断{;}}interrupt void adc_isr(void){int i=0,j=0,flag=0; //flag作为遇到零点的标志V oltage[ConversionCount]=AdcRegs.ADCRESULT0>>4;U0[ConversionCount]=3.0*V oltage[ConversionCount]/4095;if(ConversionCount==1023) //如果采样点数达到了1024{PieCtrlRegs.PIEIER1.bit.INTx6=0; //禁止中断请求ConversionCount=0;/*求出1024个点中的最大最小值和中间值*/Vmax=V oltage[0];Vmin=V oltage[0];for(i=0;i<1024;i++){if(Vmax<V oltage[i])Vmax=V oltage[i]; //求出最大值if(Vmin>V oltage[i])Vmin=V oltage[i]; //求出最小值}Vavr=(Vmax-Vmin)/2; //求出中间值for(i=1;i<1024;i++){if((V oltage[i-1]<=Vavr)&&(V oltage[i]>=V avr)){flag++;}if(flag==1){SV[j]=U0[i]; //U0[i]就是对应的Voltage[i]的模拟值RMS+=SV[j]*SV[j];j++;}if(flag==2){i=1024;flag=0;}}RMS=sqrt(RMS/j);rg=(int)RMS;r1=((int)(RMS*10))%10;r2=((int)(RMS*100))%10;f=(1500000/250)/j;fb=f/100;fs=(f-fb*100)/10;fg=f-fb*100-fs*10;lcd_write_dy();lcd_write_pl();PieCtrlRegs.PIEIER1.bit.INTx6=1; //使能中断请求}else ConversionCount++;/*复位SEQ1,等待触发信号重启下次转换*/AdcRegs.ADCTRL2.bit.RST_SEQ1=1; //复位SEQ1AdcRegs.ADCST.bit.INT_SEQ1_CLR=1; //清除SEQ1的中断标志位PieCtrlRegs.PIEACK.all=PIEACK_GROUP1; //使能Adc模块的下次中断请求return;}。

DSP插件中英文对照SRCSRC是Sample Rate Convertor(采样率转换器)的缩写。

Intel在制定AC'97规范时,为了降低元件的成本,规定凡是符合AC'97规范的元件必定要经历一个音源的处理过程,即将所有的信号转换成统一的采样率进行传输。

它负责选择和控制所有由windows进入声卡的音源(包括由子卡和外置盒输入的音源)。

SRC里面有多路端口选择:FXBus0~31(SB为0~15)以及一些子卡和外置盒输入的音源。

其他的端口一般只在专业音频软件中才能见到。

使用时应用程序的输出端口要与SRC所设置的输入端口一一对应才能正确发声的。

如windows 系统默认以FXBus 0/1输出的,那么DSP里必须有一个SRC设置成FXBus 0/1才能接受系统的声音并发送给后面的处理。

一般我们会用不同端口来发不同的声音的,如系统用0/1、Foobar用4/5,那么DSP里就要调出两个SRC分别设置成0/1与4/5来管不同的声音。

(ADC,Analog-to-Digital Converter的缩写,指模/数转换器或者模拟/数字转换器。

真实世界的模拟信号,例如温度、压力、声音或者图像等,需要转换成更容易储存、处理和发射的数字形式。

模/数转换器可以实现这个功能,在各种不同的产品中都可以找到它的身影。

是负责选择和控制卡板上外部输入音源的插件(line in、mic等,子卡和外置盒输入的音源在SRC上选择)。

MX6 MX8 12路16路调音台!12路16路输入,1立体声母线,2编组,2辅助,12个红色输入端分别对应调音台IN1到IN6的6个推子。

8个蓝色的输出端口从上至下分别是立体声MIX母线,Rec立体声录音编组母线,立体声AUX1和立体声AUX2!每个通道都有3个开关分别是--—发送到Rec立体声录音编组母线,-—发送到立体声MIX母线,[E]通道开关,必须打开他才能激活通道。

每个通道的S1推子和S2推子是分别控制发送给立体声AUX辅助1和立体声AUX辅助2的音量。

DescriptionThis module allows 3-channel analog-to-digital conversion with programmable gains and offsets. The conversions are triggered on GP Timer 1 underflow (for 281x) or EPWM1 CNT_zero event (for 280x). The converted results represent load currents and DC-bus voltage in the inverter.1. GP Timer 1 is the time base for symmetrical Pulse-Width Modulation(for 281x) or Time Base of EPWM1 CNT_zero event (for 280x);2. For line current measurement, the analog inputs are the voltageacross resistors placed between the sources or emitters of low-side power devices and low-side DC rail; and3. For DC-bus voltage measurement, the analog input is the voltageacross resistor by means of voltage divider concept..AvailabilityThis 16-bit module is available in one interface format:1) The C interface versionModule Properties Type: Target Dependent, Application IndependentTarget Devices: x281x or x280xC Version File Names: f281xileg_vdc.c, f281xileg_vdc.h (for x281x) f280xileg_vdc.c, f280xileg_vdc.h (for x280x) IQmath library files for C: N/AItem C versionCommentsCode Size □ (x281x/x280x) 147/155 wordsData RAM 0 words • xDAIS readyNoXDAIS component No IALG layer not implemented Multiple instancesYesReentrancy Yes• Each pre-initialized ILEG2DCBUSMEAS structure consumes 15 words in the data memory□Code size mentioned here is the size of the init() and read() functionsC InterfaceC InterfaceObject DefinitionThe structure of ILEG2DCBUSMEAS object is defined by following structure definition typedef struct { int16 ImeasAGain; // Parameter: gain for Ia (Q13)int16 ImeasAOffset; // Parameter: offset for Ia (Q15)int16 ImeasA; // Output: measured Ia (Q15)int16 ImeasBGain; // Parameter: gain for Ib (Q13)int16 ImeasBOffset; // Parameter: offset for Ib (Q15)int16 ImeasB; // Output: measured Ib (Q15)int16 VdcMeasGain; // Parameter: gain for Vdc (Q13)int16 VdcMeasOffset; // Parameter: offset for Vdc (Q15)int16 VdcMeas; // Output: measured Vdc (Q15)int16 ImeasC; // Output: computed Ic (Q15)Uint16 ChSelect; // Parameter: ADC channel selectionvoid (*init)(); // Pointer to the init functionvoid (*read)(); // Pointer to the read function} ILEG2DCBUSMEAS;typedef ILEG2DCBUSMEAS *ILEG2DCBUSMEAS_handle;Item Name Description Format Range(Hex)Inputs ADCINx, ADCINy,ADCINz ADC pins in 281x device wherex,y,z correspond to the channelnumbers selected by ChSelectN/A 0-3VImeasA x th channel digital representationfor current I aQ15 8000-7FFFImeasB y th channel digital representationfor current I bQ15 8000-7FFF ImeasC Computing current I c Q158000-7FFF OutputsVdcMeas z th channel digital representationfor DC-bus voltage V dcQ15 8000-7FFFChSelect 16-bit ADC channel select formatcan be seen as:ChSelect = 0zyxh Q0 x,y,z are in between0h -> FhImeasAGain Gain for x th channel. Modify this ifdefault gain is not used.Q13 8000-7FFFImeasBGain Gainfory th channel. Modify this ifdefault gain is not used.Q13 8000-7FFFVdcMeasGain Gain for z th channel. Modify this ifdefault gain is not used.Q13 8000-7FFF ImeasAOffset Offsetforx th channel. Modify this ifdefault offset is not used.Q15 8000-7FFFImeasBOffset Offsetfory th channel. Modify this ifdefault offset is not used. Q15 8000-7FFFILEG2DCBUSMEASparameterVdcMeasOffset Offset for z th channel. Modify this ifdefault offset is not used.Q15 8000-7FFF Special Constants and Data typesILEG2DCBUSMEASThe module definition is created as a data type. This makes it convenient to instance an interface to the ILEG2DCBUSMEAS driver. To create multiple instances of the module simply declare variables of type ILEG2DCBUSMEAS.C InterfaceILEG2DCBUSMEAS_handleUser defined Data type of pointer to ILEG2DCBUSMEAS moduleILEG2DCBUSMEAS_DEFAULTSStructure symbolic constant to initialize ILEG2DCBUSMEAS module. This provides the initial values to the terminal variables as well as method pointers.Methodsvoid F281X_ileg2_dcbus_drv_init(ILEG2DCBUSMEAS *);void F281X_ileg2_dcbus_drv_read(ILEG2DCBUSMEAS *);void F280X_ileg2_dcbus_drv_init(ILEG2DCBUSMEAS *);void F280X_ileg2_dcbus_drv_read(ILEG2DCBUSMEAS *);This default definition of the object implements two methods – the initialization and the runtime read function for ILEG2DCBUSMEAS measurement. This is implemented by means of a function pointer, and the initializer sets this to F281X_ileg2_dcbus_drv_init and F281X_ileg2_dcbus_drv_read functions for x281x or F280X_ileg2_dcbus_drv_init and F280X_ileg2_dcbus_drv_read functions for x280x. The argument to this function is the address of the ILEG2DCBUSMEAS object.Module UsageInstantiationThe following example instances one ILEG2DCBUSMEAS objectILEG2DCBUSMEAS ilg2_vdc1;InitializationTo Instance pre-initialized objectsILEG2DCBUSMEAS ilg2_vdc1 = ILEG2DCBUSMEAS_DEFAULTS;Invoking the computation functionilg2_vdc1.init(&ilg2_vdc1);ilg2_vdc1.read(&ilg2_vdc1);ExampleThe following pseudo code provides the information about the module usage.main(){ilg2_vdc1.init(&ilg2_vdc1); // Call init function for ilg2_vdc1}C Interface void interrupt periodic_interrupt_isr(){ilg2_vdc1.read(&ilg2_vdc1); // Call read function for ilg2_vdc1Ias = _IQ15toIQ((int32)ilg2_vdc1.ImeasA); // Ias is in GLOBAL_QIbs = _IQ15toIQ((int32)ilg2_vdc1.ImeasB); // Ibs is in GLOBAL_QDC_bus = _IQ15toIQ((int32)ilg2_vdc1.VdcMeas); // DC_bus GLOBAL_Q}Technical BackgroundTechnical BackgroundThe ADCIN pins accepts the analog input signals (I a , I b , and V dc ) in the range of 0-3 volts for x28xx based DSP with ground referenced to 0 volt (VREFLO = 0).Consequently, before connecting these signals to ADCIN pins, the hardware adjustment by external op-amp circuits (for gain and offset adjustments) for these analog signals such that they represent according to the selected base quantities and the appropriate voltage range is required.Four output variables of the module (ImeasA, ImeasB, ImeasC, and VdcMeas) are computed after three ADC analog input signals are digitized as seen below:ImeasA = ImeasAGain*ADC_Ia_Q15 + ImeasAOffset ImeasB = ImeasBGain*ADC_Ib_Q15 + ImeasBOffset ImeasC = -(ImeasA + ImeasB)VdcMeas = VdcMeasGain*ADC_Vdc_Q15 + VdcMeasOffsetNote that ADC_Ix_Q15 (x=a,b) and ADC_Vdc_Q15 are already converted to Q15 number.Basically, the signals can be categorized into two main types: bipolar and unipolar signals. The AC currents (or AC voltages) are examples of bipolar signal and the DC-bus voltage is an example of unipolar signal.The input AC currents (I a , I b ) are typically sensed and re-scaled within the range of 0-3 volts for x28xx based DSP with the appropriate base current. Thus, the Q15-number conversion is necessary for the current measurements after they are digitized as seen in Figure 1.It is emphasized that the ADC unit is 12-bit resolution with left justified in the 16-bit ADC result register. Thus, the ADC output range is in between 0000h and FFF0h.external AC signalproper signalFigure 1: Q15-number conversion for current measurements (bipolar signal)For DC-bus voltage (V dc ), practically the input signal is already represented in the positive range only, so its digitized variable has to be rescaled corresponding to the Q15 number.Technical Background For better understanding, Figure 2 illustrates the Q15-number conversion for the DC-bus voltage measurement.Figure 2: Q15-number conversion for DC-bus voltage measurement (unipolar signal)In both cases of Q15-number conversion, the number is distorted a little bit about the maximum value (e.g., 7FF0h for bipolar and 7FF8h for unipolar at the maximum value of 7FFFh).。

ADC头文件与寄存器对应解读:struct ADCTRL1_BITS { // bits descriptionUint16 rsvd1:4; // 3:0 reservedUint16 SEQ_CASC:1; // 4 Cascaded sequencer mode 级联序列模式Uint16 SEQ_OVRD:1; // 5 Sequencer override 序列发生器覆盖Uint16 CONT_RUN:1; // 6 Continuous run 连续运行模式Uint16 CPS:1; // 7 ADC core clock pre-scalar ADC核心时钟分频Uint16 ACQ_PS:4; // 11:8 Acquisition window size采集窗口大小Uint16 SUSMOD:2; // 13:12 Emulation suspend mode仿真挂起模式Uint16 RESET:1; // 14 ADC reset ADC复位Uint16 rsvd2:1; // 15 reserved 保留};下面的联合体主要是为了解决对这个寄存器的控制,可以是整体赋值液可以是一位一位的赋值。

union ADCTRL1_REG {Uint16 all;struct ADCTRL1_BITS bit;};struct ADCTRL2_BITS { // bits descriptionUint16 EPWM_SOCB_SEQ2:1; // 0 EPWM compare B SOC mask for SEQ2 增强PWM比较器B作为SEQ2的启动转换标志Uint16 rsvd1:1; // 1 reservedUint16 INT_MOD_SEQ2:1; // 2 SEQ2 Interrupt mode SEQ2终端模式Uint16 INT_ENA_SEQ2:1; // 3 SEQ2 Interrupt enable SEQ2中断使能Uint16 rsvd2:1; // 4 reservedUint16 SOC_SEQ2:1; // 5 Start of conversion for SEQ2启动SEQ2转换Uint16 RST_SEQ2:1; // 6 Reset SEQ2 SEQ2复位Uint16 EXT_SOC_SEQ1:1; // 7 External start of conversion for SEQ1 序列1的外部转换启动Uint16 EPWM_SOCA_SEQ1:1; // 8 EPWM compare B SOC mask for SEQ1Uint16 rsvd3:1; // 9 reservedUint16 INT_MOD_SEQ1:1; // 10 SEQ1 Interrupt modeUint16 INT_ENA_SEQ1:1; // 11 SEQ1 Interrupt enableUint16 rsvd4:1; // 12 reservedUint16 SOC_SEQ1:1; // 13 Start of conversion trigger for SEQ1Uint16 RST_SEQ1:1; // 14 Restart sequencer 1Uint16 EPWM_SOCB_SEQ:1; // 15 EPWM compare B SOC enable };struct ADCASEQSR_BITS { // bits descriptionUint16 SEQ1_STATE:4; // 3:0 SEQ1 state 序列1的状态Uint16 SEQ2_STATE:3; // 6:4 SEQ2 state 序列2的状态Uint16 rsvd1:1; // 7 reservedUint16 SEQ_CNTR:4; // 11:8 Sequencing counter status 序列计数器状态Uint16 rsvd2:4; // 15:12 reserved};ADC最大转换信道数寄存器struct ADCMAXCONV_BITS { // bits descriptionUint16 MAX_CONV1:4; // 3:0 Max number of conversions 序列1最大转换通道数Uint16 MAX_CONV2:3; // 6:4 Max number of conversions 序列2最大转换通道数Uint16 rsvd1:9; // 15:7 reserved};控制寄存器3struct ADCTRL3_BITS { // bits descriptionUint16 SMODE_SEL:1; // 0 Sampling mode select 采样模式选择Uint16 ADCCLKPS:4; // 4:1 ADC core clock divider ADC时钟分频器Uint16 ADCPWDN:1; // 5 ADC powerdown ADC断电???Uint16 ADCBGRFDN:2; // 7:6 ADC bandgap/ref power down ADC 参考/带隙断电???Uint16 rsvd1:8; // 15:8 reserved};状态寄存器struct ADCST_BITS { // bits descriptionUint16 INT_SEQ1:1; // 0 SEQ1 Interrupt flag 序列1中断标志Uint16 INT_SEQ2:1; // 1 SEQ2 Interrupt flag 序列2中断标志Uint16 SEQ1_BSY:1; // 2 SEQ1 busy status 序列1忙标志Uint16 SEQ2_BSY:1; // 3 SEQ2 busy status 序列2忙标志Uint16 INT_SEQ1_CLR:1; // 4 SEQ1 Interrupt clear 清除序列1中断标志Uint16 INT_SEQ2_CLR:1; // 5 SEQ2 Interrupt clear 清除序列2中断标志Uint16 EOS_BUF1:1; // 6 End of sequence buffer1 序列缓冲器1结束Uint16 EOS_BUF2:1; // 7 End of sequence buffer2Uint16 rsvd1:8; // 15:8 reserved};struct ADCREFSEL_BITS { // bits descriptionUint16 rsvd1:14; // 13:0 reservedUint16 REF_SEL:2; // 15:14 Reference select 参考选择???};struct ADCOFFTRIM_BITS{ // bits descriptionint16 OFFSET_TRIM:9; // 8:0 Offset Trim 偏移微调???Uint16 rsvd1:7; // 15:9 reserved};。

PreliminaryTMS320x280x DSP 模数转换器(ADC)参考指南文献编号:ZHCU0042004年11月–修订2005年6月Preliminary内容目 (3)序 (7)1模数转换器(ADC) (11)1.1 (12)1.2 (14)1.2.1顺序采样模式 (15)1.2.2同步采样模式 (15)1.3不间断自动定序模式 (20)1.3.1序列发生器启动/停止模式(具有多个时序触发器的序列发生器启动/停止操作) (22)1.3.2同步采样模式 (24)1.3.3输入触发器说明 (24)1.3.4定序转换期间的中断操作 (25)1.4ADC时钟预分频器 (26)1.4.1ADC模块时钟和采样频率 (27)1.5低功率模式 (27)1.6 (28)1.7序列发生器覆盖功能 (28)1.8内部/外部参考电压选择 (28)1.9 (30)2ADC寄存器 (33)2.1ADC控制寄存器 (34)2.2最大转换信道数寄存器(ADCMAXCONV) (37)2.3自动定序状态寄存器(ADCASEQSR) (39)2.4ADC状态和标志寄存器(ADCST) (39)2.5ADC参考选择寄存器(ADCREFSEL) (40)2.6ADC偏移微调寄存器(ADCOFFTRIM) (41)2.7ADC输入信道选择定序控制寄存器 (41)2.8ADC转换结果缓冲寄存器(ADCRESULTn) (42)A修订历史记录 (45)Preliminary附图目录1-1ADC模块的结构图 (13)1-2顺序采样模式(SMODE=0) (15)1-3同步采样模式(SMODE=1) (15)1-4级联模式下自动定序的ADC结构图 (16)1-5带双序列发生器的自动定序的ADC结构图 (17)1-6不间断自动定序模式的流程图 (22)1-7ePWM触发器启动序列发生器的示例 (23)1-8定序转换期间的中断操作 (26)1-9ADC内核时钟和采样保持(S/H)时钟 (27)1-10到ADC的时钟链 (27)1-11外部参考的外部偏置 (29)1-12 (30)1-13采样0-V参考电压的理想代码分布 (31)2-1ADC控制寄存器1(ADCTRL1)(地址偏移00h) (34)2-2ADC控制寄存器2(ADCTRL2)(地址偏移01h) (35)2-3ADC控制寄存器3(ADCTRL3)(地址偏移18h) (37)2-4最大转换信道数寄存器(ADCMAXCONV)(偏移地址02h) (38)2-5自动定序状态寄存器(ADCASEQSR)(地址偏移07h) (39)2-6ADC状态和标志寄存器(ADCST)(地址偏移19h) (40)2-7ADC参考选择寄存器(ADCREFSEL)(地址偏移1Ch) (40)2-8ADC偏移微调寄存器(ADCOFFTRIM)(地址偏移1Dh) (41)2-9ADC输入信道选择定序控制寄存器(ADCCHSELSEQ1)(地址偏移03h) (41)2-10ADC输入信道选择定序控制寄存器(ADCCHSELSEQ2)(地址偏移04h) (41)2-11ADC输入信道选择定序控制寄存器(ADCCHSELSEQ3)(地址偏移05h) (41)2-12ADC输入信道选择定序控制寄存器(ADCCHSELSEQ4)(地址偏移06h) (42)2-13ADC转换结果缓冲寄存器(ADCRESULTn)-(地址0x7108-0x7117) (42)2-14ADC转换结果缓冲寄存器(ADCRESULTn)-(地址0x0B00-0x0B0F) (42)Preliminary附表目录1-1ADC寄存器 (13)1-2单一工作模式和级联工作模式比较 (18)1-3ADCCHSELSEQn寄存器的值(MAX_CONV1设置为6) (21)1-4ADCCHSELSEQn的值(MAX_CONV1设置为2) (23)1-5 (24)1-6输入触发器 (24)1-7到ADC的时钟链 (27)1-8 (27)2-1ADC控制寄存器1(ADCTRL1)字段说明 (34)2-2ADC控制寄存器2(ADCTRL2)字段说明 (35)2-3ADC控制寄存器3(ADCTRL3)字段说明 (37)2-4最大转换信道数寄存器(ADCMAXCONV)字段说明 (38)2-5各种转换数的MAX_CONV1的位选择 (38)2-6自动定序状态寄存器(ADCASEQSR)字段说明 (39)2-7活动序列发生器的状态 (39)2-8ADC状态和标志寄存器(ADCST)字段说明 (40)2-9ADC参考选择寄存器(ADCREFSEL)字段说明 (41)2-10ADC偏移微调寄存器(ADCOFFTRIM)字段说明 (41)2-11CONVnn位值和所选的ADC输入信道 (42)PreliminaryPreliminary序言ZHCU004–2004年11月–修订2005年6月请先阅读关于本手册本文档描述了TMS320x280x数字信号处理器(DSP)上可用的模数转换器(ADC)的功能和操作。

* 例程功能:利用中断定时器每隔一秒钟,从DSP28335的A0、A1口接收模拟信号,并转换为

数字信号存放在S a m p l e T a b l e1,S a m p l e T a b l e2中。

*

*/

#include""始化系统控制:PLL,WatchDog,启用外设时钟该示例函数可在文件中找到。

InitSysCtrl();

始化GPIO:该示例函数位于文件中,并说明如何将GPIO设置为默认状态。

始化所有器件外设:此功能可在中找到

InitAdc(); //ADC初始化设置

// ADC工作方式设置:

= ADC_SHCLK; // 设置采集窗的大小。

该控制位控制SOC脉冲的宽度,SOC脉冲信号的宽

度等于 ADCLK周期 *(ADC_SHCLK+1) = ADC_CKPS; // 核心时钟分频。

ADC模块时钟 = HSPCLK/2*ADC_CKPS = (1*2) =

= 1; // 建立级联序列方式

= 1; // 读取完转换序列后停止

= 1; // 使能排序覆盖

= 0x0; // 设置ADCINA0作为第一个变换

= 0x1; // 设置ADCINA1作为第一个变换

= 0x1; // 最大采集通道

// 第5步。

用户特定的代码,启用中断:

EINT; // 启用全局中断INTM

ERTM; // 启用全局实时中断DBGM

= 0x2000; // 启动SEQ1

}

interrupt void ISRTimer0(void)

{

while {} // 等待中断

= 1; //设置同步采样模式

= 1; //向该位写1,清除SEQ1中断标志位

SampleTable1=(>>4)); //取A0数据并记录在SampleTable1数组中

SampleTable2=(>>4)); //取A1数据并记录在SampleTable2数组中

//0x0001赋给12组中断ACKnowlwdge寄存器,对其全部清除,不接受其它中断

//定时到了指定时间,标志位置位,清除标志

//重载Timer0的定时数据

}。