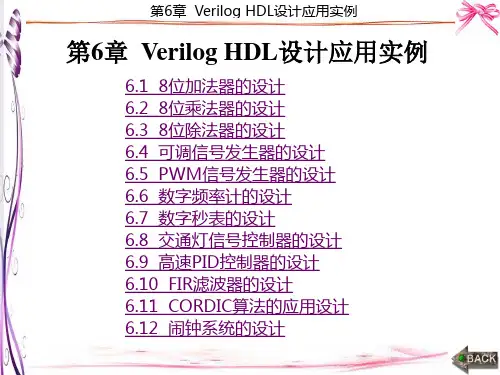

第6章 Verilog HDL设计进阶

- 格式:ppt

- 大小:1.29 MB

- 文档页数:8

VerilogHDL入门教程第一部分:Verilog HDL概述(约200字)Verilog HDL是一种硬件描述语言,用于描述和建模数字电路和系统。

它是一种被广泛使用的硬件设计语言,特别适合用于逻辑设计和验证。

Verilog HDL提供了一种形式化的方式来表示数字电路和系统的行为和结构,使得工程师可以更轻松地进行硬件设计和验证。

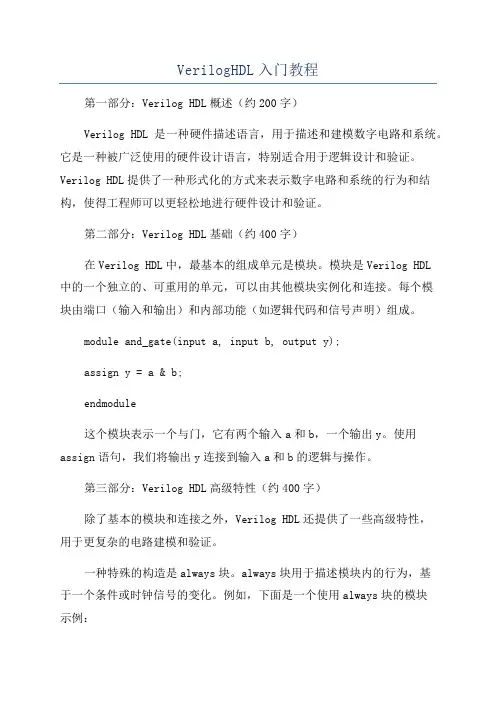

第二部分:Verilog HDL基础(约400字)在Verilog HDL中,最基本的组成单元是模块。

模块是Verilog HDL中的一个独立的、可重用的单元,可以由其他模块实例化和连接。

每个模块由端口(输入和输出)和内部功能(如逻辑代码和信号声明)组成。

module and_gate(input a, input b, output y);assign y = a & b;endmodule这个模块表示一个与门,它有两个输入a和b,一个输出y。

使用assign语句,我们将输出y连接到输入a和b的逻辑与操作。

第三部分:Verilog HDL高级特性(约400字)除了基本的模块和连接之外,Verilog HDL还提供了一些高级特性,用于更复杂的电路建模和验证。

一种特殊的构造是always块。

always块用于描述模块内的行为,基于一个条件或时钟信号的变化。

例如,下面是一个使用always块的模块示例:module counter(input clk, input enable, output reg count);if (enable)count = count + 1;endendmodule这个模块表示一个简单的计数器,在时钟上升沿时根据enable信号增加计数器的值。

Verilog HDL还支持层次化的建模,允许将模块层次化地组织起来,以便更好地管理和复用代码。

层次化建模通过使用模块的层次命名和连接来实现。

例如,我们可以将上面的计数器模块实例化为另一个模块,如下所示:module top_module(input clk, input enable, output reg count);countercounter_inst(.clk(clk), .enable(enable), .count(count));endmodule这个模块实例化了上面定义的计数器模块,并将其内部信号和端口连接到外部接口。

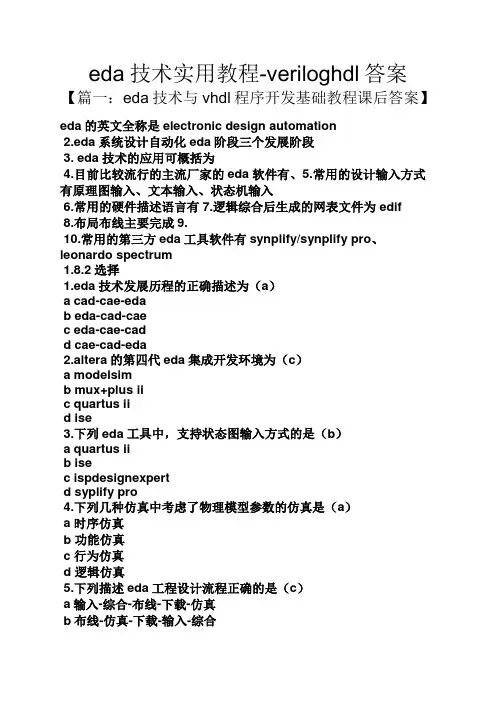

eda技术实用教程-veriloghdl答案【篇一:eda技术与vhdl程序开发基础教程课后答案】eda的英文全称是electronic design automation2.eda系统设计自动化eda阶段三个发展阶段3. eda技术的应用可概括为4.目前比较流行的主流厂家的eda软件有、5.常用的设计输入方式有原理图输入、文本输入、状态机输入6.常用的硬件描述语言有7.逻辑综合后生成的网表文件为 edif8.布局布线主要完成9.10.常用的第三方eda工具软件有synplify/synplify pro、leonardo spectrum1.8.2选择1.eda技术发展历程的正确描述为(a)a cad-cae-edab eda-cad-caec eda-cae-cadd cae-cad-eda2.altera的第四代eda集成开发环境为(c)a modelsimb mux+plus iic quartus iid ise3.下列eda工具中,支持状态图输入方式的是(b)a quartus iib isec ispdesignexpertd syplify pro4.下列几种仿真中考虑了物理模型参数的仿真是(a)a 时序仿真b 功能仿真c 行为仿真d 逻辑仿真5.下列描述eda工程设计流程正确的是(c)a输入-综合-布线-下载-仿真b布线-仿真-下载-输入-综合c输入-综合-布线-仿真-下载d输入-仿真-综合-布线-下载6.下列编程语言中不属于硬件描述语言的是(d)a vhdlb verilogc abeld php1.8.3问答1.结合本章学习的知识,简述什么是eda技术?谈谈自己对eda技术的认识?答:eda(electronic design automation)工程是现代电子信息工程领域中一门发展迅速的新技术。

2.简要介绍eda技术的发展历程?答:现代eda技术是20世纪90年代初从计算机辅助设计、辅助制造和辅助测试等工程概念发展而来的。

Verilog HDL程序设计教程红色:做后有错。

粉红色:有疑问。

紫色:第二次仍有错。

绿色:文字错误第1章EDA技术综述 1.1引言1.摩尔定律1.2EDA的发展阶段1.阶段1.3设计方法与设计技术1.两种设计思路2.IP的含义3. IP核的分类。

4. SOC的含义1.4EDA的实现1.实现方法第2章EDA设计软件与设计流程 2.2EDA的设计流程1(FPGA的设计流程 2(综合的定义与类型。

3(仿真的类型第3章Verilog HDL设计初步(P18) 3.2完整的Verilog HDL设计1. 4位全加器的和4位计数器的程序。

2. 4位全加器的仿真程序(1.时间头文件 2.模块名(没有参数)3.参数规定(端口、延时、时钟)4.调用测试对象 5.设置参数(所有的输入端口都应初始化赋值)6.显示设置)。

3.3Verilog模块基本结构剖析 1.端口定义注意事项。

2.逻辑功能定义的几种方式第4章Verilog HDL语言要素(P32)4.1词法1.verilog中的四种基本逻辑状态4.2数据类型1.连线型(Net Type)的特点2.寄存器型(Register Type):定义、与连线型区别(赋值、保值)3.Parameter的使用格式4.3寄存器和存储器1.寄存器定义格式和标矢性2.存储器:定义、格式、位区选择方法4.3运算符1.等式与全等式的区别2.位拼接运算符第5章Verilog HDL行为语句(P45)5.2 Verilog HDL中的过程语句1.always过程语句格式。

2.initial过程语句格式。

5.3 块语句1.块语句。

2.用begin—end产生周期为10的个单位时间的方波.3.用fork—join产生周期为10的个单位时间的方波5.4赋值语句1.分类。

2.阻塞赋值和非阻塞赋值的区别5.5条件语句1.例5.11(模为60的BCD码加法计数器)2.case语句的三种表达形式5.6循环语句1.Verilog HDL中4种类型循环语句。

VerilogHDL教程verilog hdl教程一、Verilog HDL概述二、Verilog HDL语法1.模块定义和端口声明模块是Verilog HDL的基本单元,用于描述电路的结构和行为。

以下是一个简单的模块定义和端口声明的例子:module adderinput wire [3:0] a,input wire [3:0] b,output wire [3:0] sum//模块内部的逻辑和信号声明//...endmodule2.信号声明和赋值wire [3:0] a;reg [3:0] b;assign a = 4'b0110;b<=a;end3.组合逻辑和时序逻辑组合逻辑通过组合逻辑操作(如AND,OR,XOR等)来描述电路的行为。

时序逻辑通过时钟沿的触发条件来描述电路的行为。

以下是组合逻辑和时序逻辑的例子://组合逻辑assign c = a & b;assign d = a ^ b;//时序逻辑if (reset) begine<=0;end else begine<=a+b;endend三、Verilog HDL用法1.模块实例化add4 adder_inst.a(a),.b(b),.sum(sum)2.仿真和验证Verilog HDL可以使用仿真工具进行仿真和验证。

常用的仿真工具包括ModelSim,Xilinx ISE和Cadence Incisive等。

仿真工具可以使用Verilog HDL代码来模拟和验证电路的功能和性能。

四、总结Verilog HDL是一种用于描述数字电路的硬件描述语言。

它提供了一种清晰,结构化的方式来描述电路的行为和结构。

通过模块化的设计和调试,Verilog HDL使设计人员能够更好地建模和分析复杂的电路。

它支持多种级别的抽象,如行为级,RTL级和门级,以满足不同层次的设计需求。

通过实例化已定义的模块和使用仿真工具,Verilog HDL可以方便地进行电路的仿真和验证。

Verilog_HDL教程

1.简介

Verilog HDL是由美国电气和电子工程师协会(IEEE)于1984年开

发的一种硬件描述语言。

它是一种面向数据流的语言,主要用于描述数字

逻辑电路的行为和结构。

Verilog HDL可以用于设计和仿真各种数字电路,如计算机处理器、存储器、控制逻辑和通信接口等。

2.基本语法

下面是Verilog HDL的基本语法元素:

2.1模块

模块是Verilog HDL中的最基本的构建单元。

每个模块都有一个名称

和一个端口列表。

端口可以是输入或输出,也可以是双向的。

2.2数据类型

2.3信号赋值

可以使用赋值运算符(=)将值赋给变量或信号。

还可以使用阻塞或

非阻塞赋值运算符来实现顺序或并发的赋值操作。

3.设计结构

4.运算符

5.仿真和验证

总结:

本教程简要介绍了Verilog HDL的基本语法和用法。

Verilog HDL是一种被广泛应用于数字电路设计的硬件描述语言。

通过学习本教程,您将能够开始使用Verilog HDL进行数字电路的设计和验证。