译码器实现逻辑电路

- 格式:ppt

- 大小:726.00 KB

- 文档页数:11

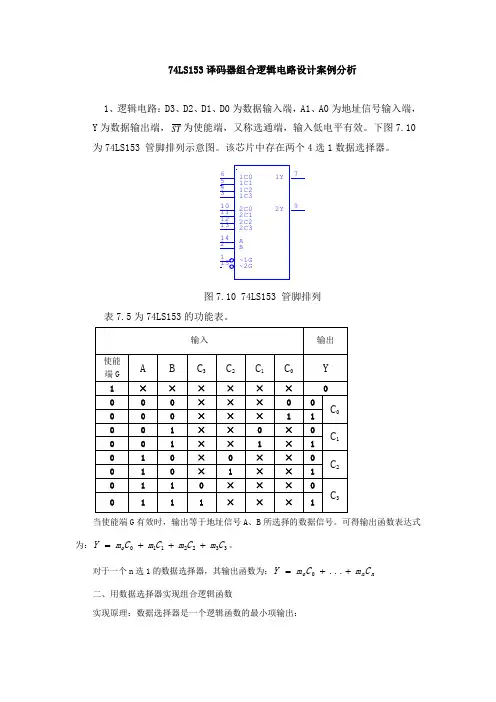

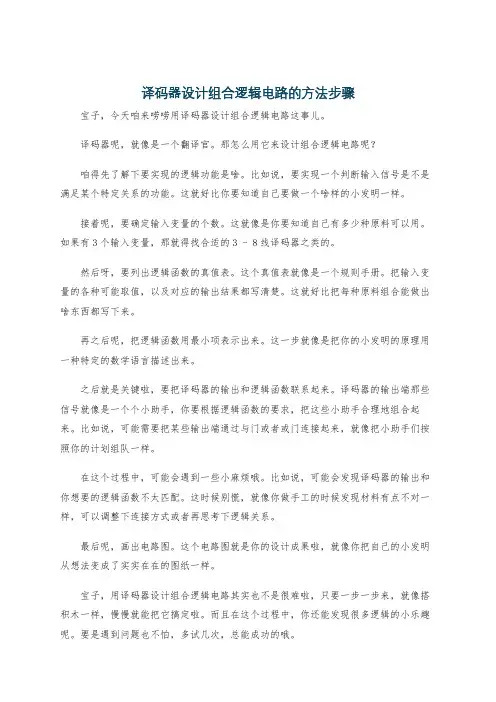

74LS153译码器组合逻辑电路设计案例分析1、逻辑电路:D3、D2、D1、D0为数据输入端,A1、A0为地址信号输入端,Y 为数据输出端,ST 为使能端,又称选通端,输入低电平有效。

下图7.10为74LS153 管脚排列示意图。

该芯片中存在两个4选1数据选择器。

2Y92C0102C1112C2122C313A 14B 2~1G 11Y71C061C151C241C33~2G15图7.10 74LS153 管脚排列表7.5为74LS153的功能表。

当使能端G 有效时,输出等于地址信号A 、B 所选择的数据信号。

可得输出函数表达式为:3322110C m C m C m C m Y o +++=。

对于一个n 选1的数据选择器,其输出函数为:n n o C m C m Y ++=...0 二、用数据选择器实现组合逻辑函数实现原理:数据选择器是一个逻辑函数的最小项输出:∑-===++=1200...n i ii n n o c m C m C m Y 而任何一个n 位变量的逻辑函数都可变换为最小项之和的标准式。

对照函数表达式和相应的数据选择器输出函数表达式,可以实现用数据选择器来表示逻辑函数。

实现步骤:(1)根据函数变量选择合适的数据选择器,一般变量个数n 个,选择2n 选1的数据选择器。

(2)将被表示的函数转换成标准与或表达式。

(3)写出选择的数据选择器的输出函数。

(4)对比两函数,使数据选择器的地址端和函数变量一一对应(高位对高位),表达式中出现的最小项相应的输入数据C 为1,否则为0。

(5)画逻辑电路图。

例:用数据选择器和门电路实现AC AB Y +=的组合逻辑电路。

(1) 选择数据选择器:选8选1数据选择器74LS151。

(2) 标准与或表达式756m m m ABC C B A C AB AC AB Y '+'+'=++=+=' (3)写出数据选择器输出函数776655443322110C m C m C m C m C m C m C m C m Y o +++++++=(4)对照上述两表达式,令A=A2,B=A1,C=A0,则n n m m '=,所以,C 0=C 1=C 2=C 3=C 4=0;C 5=C 6=C 7=1。

译码器设计组合逻辑电路的方法步骤宝子,今天咱来唠唠用译码器设计组合逻辑电路这事儿。

译码器呢,就像是一个翻译官。

那怎么用它来设计组合逻辑电路呢?咱得先了解下要实现的逻辑功能是啥。

比如说,要实现一个判断输入信号是不是满足某个特定关系的功能。

这就好比你要知道自己要做一个啥样的小发明一样。

接着呢,要确定输入变量的个数。

这就像是你要知道自己有多少种原料可以用。

如果有3个输入变量,那就得找合适的3 - 8线译码器之类的。

然后呀,要列出逻辑函数的真值表。

这个真值表就像是一个规则手册。

把输入变量的各种可能取值,以及对应的输出结果都写清楚。

这就好比把每种原料组合能做出啥东西都写下来。

再之后呢,把逻辑函数用最小项表示出来。

这一步就像是把你的小发明的原理用一种特定的数学语言描述出来。

之后就是关键啦,要把译码器的输出和逻辑函数联系起来。

译码器的输出端那些信号就像是一个个小助手,你要根据逻辑函数的要求,把这些小助手合理地组合起来。

比如说,可能需要把某些输出端通过与门或者或门连接起来,就像把小助手们按照你的计划组队一样。

在这个过程中,可能会遇到一些小麻烦哦。

比如说,可能会发现译码器的输出和你想要的逻辑函数不太匹配。

这时候别慌,就像你做手工的时候发现材料有点不对一样,可以调整下连接方式或者再思考下逻辑关系。

最后呢,画出电路图。

这个电路图就是你的设计成果啦,就像你把自己的小发明从想法变成了实实在在的图纸一样。

宝子,用译码器设计组合逻辑电路其实也不是很难啦,只要一步一步来,就像搭积木一样,慢慢就能把它搞定啦。

而且在这个过程中,你还能发现很多逻辑的小乐趣呢。

要是遇到问题也不怕,多试几次,总能成功的哦。

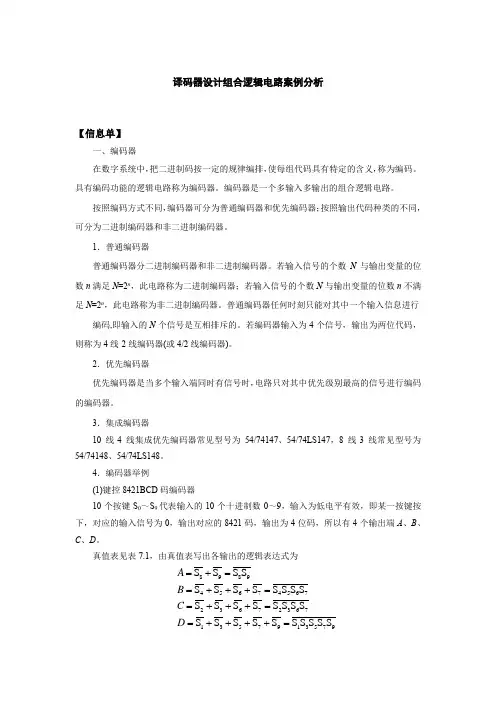

译码器设计组合逻辑电路案例分析【信息单】一、编码器在数字系统中,把二进制码按一定的规律编排,使每组代码具有特定的含义,称为编码。

具有编码功能的逻辑电路称为编码器。

编码器是一个多输入多输出的组合逻辑电路。

按照编码方式不同,编码器可分为普通编码器和优先编码器;按照输出代码种类的不同,可分为二进制编码器和非二进制编码器。

1.普通编码器普通编码器分二进制编码器和非二进制编码器。

若输入信号的个数N 与输出变量的位数n 满足N =2n ,此电路称为二进制编码器;若输入信号的个数N 与输出变量的位数n 不满足N =2n ,此电路称为非二进制编码器。

普通编码器任何时刻只能对其中一个输入信息进行编码,即输入的N 个信号是互相排斥的。

若编码器输入为4个信号,输出为两位代码,则称为4线-2线编码器(或4/2线编码器)。

2.优先编码器优先编码器是当多个输入端同时有信号时,电路只对其中优先级别最高的信号进行编码的编码器。

3.集成编码器10线-4线集成优先编码器常见型号为54/74147、54/74LS147,8线-3线常见型号为54/74148、54/74LS148。

4.编码器举例(1)键控8421BCD 码编码器10个按键S 0~S 9代表输入的10个十进制数0~9,输入为低电平有效,即某一按键按下,对应的输入信号为0,输出对应的8421码,输出为4位码,所以有4个输出端A 、B 、C 、D 。

真值表见表7.1,由真值表写出各输出的逻辑表达式为 9898S S S S =+=A76547654S S S S S S S S =+++=B 76327632S S S S S S S S =+++=C 9753197531S S S S S S S S S S =++++=D表7.1键控8421BCD 码编码器真值表(2)二进制编码器用n 位二进制代码对2n 个信号进行编码的电路称为二进制编码器。

3位二进制编码器有 8个输入端3个输出端,所以常称为8线—3线编码器,其功能真值表见表7.2,输入为高电平有效。

实验八译码器及其应用一、实验目的:1、掌握中规模集成译码器逻辑功能分析及测试方法;2、学会中规模集成译码器的连接使用方法;3、熟悉数码管的使用方法。

二、实验原理:1、译码器是一个多输入、多输出的组合逻辑电路。

它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。

译码器在数字系统中有着广泛的用途,不仅适用于代码的转换,终端的数字显示,而且还适用于数据分配,存储器寻址和组合控制信号等方面。

2、译码器可分为通用译码器和显示译码器两大类。

通用译码器又分为变量译码器和代码变换译码器。

(1)、变量译码器(又称二进制译码器),用以表示输入变量的状态,如2/4线译码器、3/8线译码器和4/16线译码器。

若有n个输入变量,则有2n个不同的状态组合,就有2n 个输出端供其使用。

而每一个输出状态所代表的函数就对应一个n变量的最小项表达式。

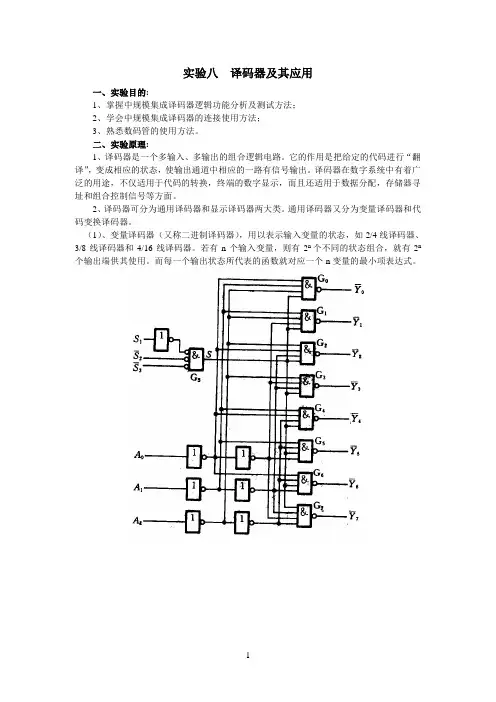

图8-1 3-8译码器74LS138逻辑图及列脚排列以3/8线译码器74LS138为例进行分析,图8-1(a)、(b)分别为其逻辑图和引脚排列图。

A2、A1、A0为地址输入端,Y0~Y7是译码器输出端,S1、S2、S3是使能端。

表8-1为74LS138功能表,当S1=1,S2+S3=0时,器件使能端有效,地址码所指定的输出端有信号(为0)输出,其它所有输出端均无信号(为1)输出。

当S1=0,S2+S3=X时或S1=X,S2+S3=1时,译码器被禁止,所有输出同时为1。

二进制译码器实际上也就是负脉冲输出的脉冲分配器。

若利用使能端中的一个输入端输入数据信息,器件就成为一个数据分配器(又称多路分配器),如图8-2所示。

若在S1输入端输入数据信息,S2=S3=0,地址码所对应的输出是S1数据信息的反码;若从S2输入端输入数据信息,令S1=1,S3=0,地址码所对应的输出就是S2端数据信息的原码。

若数据信息是时钟脉冲,则数据分配器便成为时钟脉冲分配器。

根据输入地址的不同组合译出唯一的地址,故可用作地址译码器。

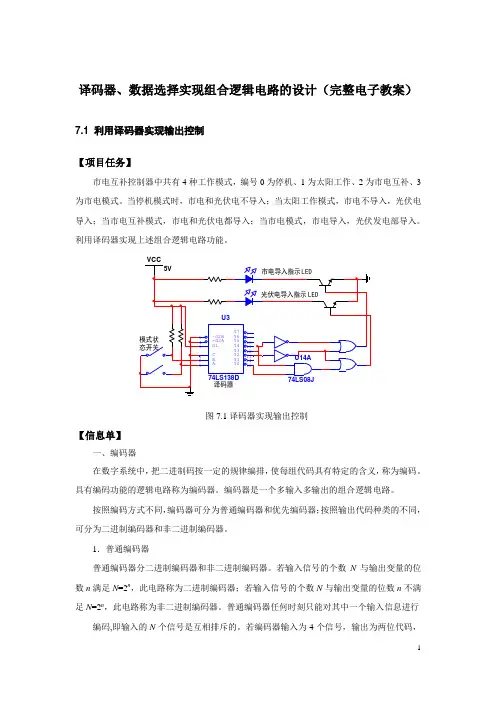

译码器、数据选择实现组合逻辑电路的设计(完整电子教案)7.1 利用译码器实现输出控制【项目任务】市电互补控制器中共有4种工作模式,编号0为停机、1为太阳工作、2为市电互补、3为市电模式。

当停机模式时,市电和光伏电不导入;当太阳工作模式,市电不导入,光伏电导入;当市电互补模式,市电和光伏电都导入;当市电模式,市电导入,光伏发电部导入。

利用译码器实现上述组合逻辑电路功能。

图7.1译码器实现输出控制【信息单】一、编码器在数字系统中,把二进制码按一定的规律编排,使每组代码具有特定的含义,称为编码。

具有编码功能的逻辑电路称为编码器。

编码器是一个多输入多输出的组合逻辑电路。

按照编码方式不同,编码器可分为普通编码器和优先编码器;按照输出代码种类的不同,可分为二进制编码器和非二进制编码器。

1.普通编码器普通编码器分二进制编码器和非二进制编码器。

若输入信号的个数N与输出变量的位数n满足N=2n,此电路称为二进制编码器;若输入信号的个数N与输出变量的位数n不满足N=2n,此电路称为非二进制编码器。

普通编码器任何时刻只能对其中一个输入信息进行编码,即输入的N个信号是互相排斥的。

若编码器输入为4个信号,输出为两位代码,则称为4线-2线编码器(或4/2线编码器)。

2.优先编码器优先编码器是当多个输入端同时有信号时,电路只对其中优先级别最高的信号进行编码的编码器。

3.集成编码器10线-4线集成优先编码器常见型号为54/74147、54/74LS147,8线-3线常见型号为54/74148、54/74LS148。

4.编码器举例(1)键控8421BCD 码编码器10个按键S 0~S 9代表输入的10个十进制数0~9,输入为低电平有效,即某一按键按下,对应的输入信号为0,输出对应的8421码,输出为4位码,所以有4个输出端A 、B 、C 、D 。

真值表见表7.1,由真值表写出各输出的逻辑表达式为 9898S S S S =+=A76547654S S S S S S S S =+++=B 76327632S S S S S S S S =+++=C 9753197531S S S S S S S S S S =++++=D表7.1键控8421BCD 码编码器真值表(2)二进制编码器用n 位二进制代码对2n 个信号进行编码的电路称为二进制编码器。

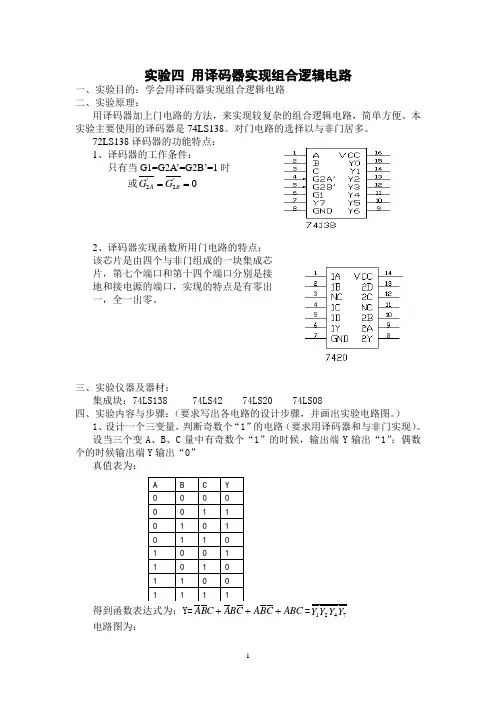

实验四 用译码器实现组合逻辑电路一、实验目的:学会用译码器实现组合逻辑电路 二、实验原理:用译码器加上门电路的方法,来实现较复杂的组合逻辑电路,简单方便。

本实验主要使用的译码器是74LS138。

对门电路的选择以与非门居多。

72LS138译码器的功能特点: 1、译码器的工作条件:只有当G1=G2A ’=G2B ’=1时或0'2'2==B A G G2、译码器实现函数所用门电路的特点:该芯片是由四个与非门组成的一块集成芯 片,第七个端口和第十四个端口分别是接 地和接电源的端口,实现的特点是有零出 一,全一出零。

三、实验仪器及器材:集成块:74LS138 74LS42 74LS20 74LS08 四、实验内容与步骤:(要求写出各电路的设计步骤,并画出实验电路图。

)1、设计一个三变量,判断奇数个“1”的电路(要求用译码器和与非门实现)。

设当三个变A 、B 、C 量中有奇数个“1”的时候,输出端Y 输出“1”;偶数个的时候输出端Y 输出“0”真值表为:得到函数表达式为:Y=ABC C B A C B A C B A +++=7421Y Y Y Y电路图为:些设备由和两台发电机供电,两台发电机的最大输出功率分别为10W 和30W ,要求设计一个逻辑电路以最节约能源的方式启、停发电机,来控制三台设备的运转、停止(要求用译码器和与非门、与门实现)。

设甲,乙分别为10W ,20W 的发电机;1为工作状态,0为不工作状态。

得到真值表为:得到函数表达式为:甲=ABC C B A C B A ++=742Y Y Y乙=ABC C AB C B A BC A C B A ++++=7631Y Y Y Y Y3、设计一个全加器(要求用译码器和与非门实现)。

Mi-1表示来自低位的进位(0表示无进位,1表示有进位);Ai 表示加数;Bi 表示被加数;Y 表示Ai+Bi 的和;N 表示向高位进位(0表示无进位,1表示有进位)。

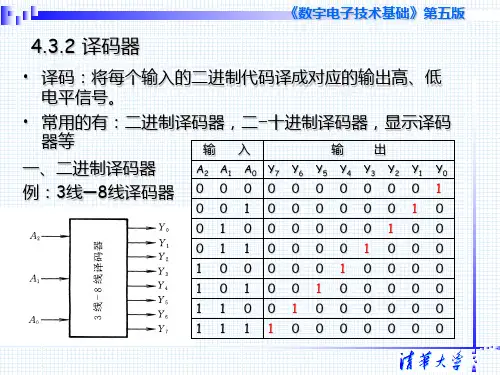

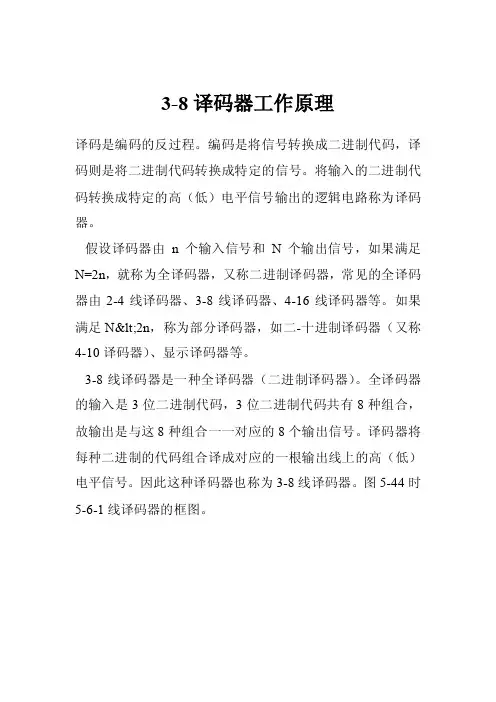

3-8译码器工作原理译码是编码的反过程。

编码是将信号转换成二进制代码,译码则是将二进制代码转换成特定的信号。

将输入的二进制代码转换成特定的高(低)电平信号输出的逻辑电路称为译码器。

假设译码器由n个输入信号和N个输出信号,如果满足N=2n,就称为全译码器,又称二进制译码器,常见的全译码器由2-4线译码器、3-8线译码器、4-16线译码器等。

如果满足N<2n,称为部分译码器,如二-十进制译码器(又称4-10译码器)、显示译码器等。

3-8线译码器是一种全译码器(二进制译码器)。

全译码器的输入是3位二进制代码,3位二进制代码共有8种组合,故输出是与这8种组合一一对应的8个输出信号。

译码器将每种二进制的代码组合译成对应的一根输出线上的高(低)电平信号。

因此这种译码器也称为3-8线译码器。

图5-44时5-6-1线译码器的框图。

图1 3-8线译码器框图根据3-8线译码器的逻辑功能可以列出它的逻辑真值表,如表1所示。

从表1中所示可以看出,输入信号的每一种组合对应着一个输出端的高电平信号,即输出端为高电平(1)时认为该输出端有输出信号。

当然,根据有需要也可以定义输出端为低电平(0)时认为该输出端有输入信号,此时称输出端低电平有效。

表1 3-8线译码器的逻辑真值表输入输出A2A1A0Y7Y6Y5Y3 Y2 Y1 Y00 0 0 0 0 0 0 0 0 0 10 0 1 00 0 0 0 1 00 1 0 0 0 0 0 0 1 0 00 10 0 0 0 1 0 0 01 0 0 0 0 0 1 0 0 0 00 1 0 0 1 0 0 0 0 01 1 0 0 1 0 0 0 0 01111根据真值表可以写出逻辑函数式为(1)根据逻辑函数式可以画出3-8线译码器的逻辑电路,如图2所示。

图2 3.8线译码器的逻辑电路图。

译码器的原理和应用1. 译码器的基本概念译码器是一种能够将输入的编码信号转换为特定输出的电子设备。

它通常用于数字系统中,用来解码输入信号并输出相应的控制信号。

译码器的主要功能是将输入信号解码为特定的输出信号,从而控制系统的工作。

译码器由输入端、译码逻辑和输出端组成。

2. 译码器的原理译码器的原理是基于布尔代数和逻辑电路的运算规则。

它使用不同的逻辑门实现对输入信号的解码。

常见的译码器有二进制译码器、BCD译码器和十进制译码器等。

2.1 二进制译码器二进制译码器是最基本的译码器类型。

它将输入的二进制编码转换为相应的输出信号。

常见的二进制译码器有2-4译码器、3-8译码器和4-16译码器等。

这些译码器通过将输入信号与特定的逻辑门进行组合,从而实现对输入信号的解码。

2.2 BCD译码器BCD译码器是将二进制编码转换为BCD码的译码器。

BCD码是一种用于表示十进制数字的编码形式。

BCD译码器通常用于将二进制信号转换为七段显示数码管所需的信号,从而实现数字显示。

2.3 十进制译码器十进制译码器是将二进制编码转换为十进制数字的译码器。

它通常使用BCD码或其他编码形式表示十进制数字,并将输入的二进制信号转换为对应的十进制数字。

3. 译码器的应用译码器在数字系统中有广泛的应用。

以下是一些常见的应用场景:3.1 数字系统的控制译码器通常用于数字系统的控制功能。

例如,它可以将输入的编码信号转换为特定的控制信号,来控制数字系统中的各个模块的工作。

通过不同的输入信号解码,译码器可以实现对数字系统的灵活控制。

3.2 数字显示译码器在数码管的控制中起着重要的作用。

它将输入的编码信号转换为七段数码管所需的信号,从而实现数字的显示。

3.3 键盘扫描译码器也可以用于键盘扫描。

通过将键盘上按键对应的编码信号解码,译码器可以判断用户按下的是哪一个按键,从而实现对键盘输入的处理。

3.4 时序控制译码器可以用于时序控制电路中。

通过将输入信号解码为相应的控制信号,译码器可以实现对时序控制电路的控制,例如时钟、定时器和计数器等。

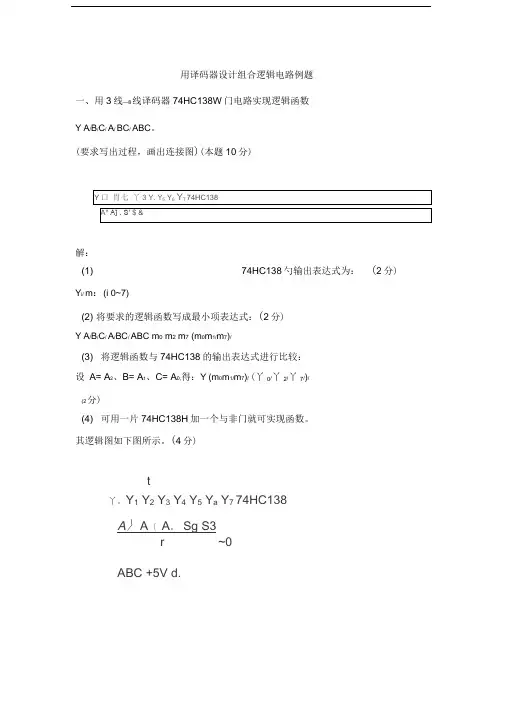

用译码器设计组合逻辑电路例题一、用3线—8线译码器74HC138W门电路实现逻辑函数Y A/B/C/ A/ BC/ ABC。

(要求写出过程,画出连接图)(本题10分)解:(1) 74HC138勺输出表达式为:(2分) Y i/ m:(i 0~7)(2) 将要求的逻辑函数写成最小项表达式:(2分)Y A/B/C/ A/BC/ ABC m0 m2 m7 (m0m1/m7)/(3) 将逻辑函数与74HC138的输出表达式进行比较:设A= A2、B= A1、C= A0,得:Y (m0m1/m7)/ (丫0/丫2/丫7/)/(2分)(4) 可用一片74HC138H加一个与非门就可实现函数。

其逻辑图如下图所示。

(4分)t丫。

Y1 Y2 Y3 Y4 Y5 Y a Y7 74HC138A〉A〔A。

Sg S3r ~0ABC +5V d.三、公司A 、8 C 三个股东,分别占有50% 30咧日20%勺股份,试用一片3线-8 线译码器74HC138^若干门电路设计一个三输入三输出的多数表决器, 用丁开会 时按股份大小记分输出通过、平■局和否决三种表决结果。

通过、平■局和否决,分 别用X 、Y 、Z 表示(股东赞成和输出结果均用1表示)。

(12分)(3)画连线图(4分)令 74HC138的地址码 A 2 A,A 1 B,A 0 CX AB /C ABC / ABC 74HC138 A- A* S 〔 Sg S3 == | 二 午 ABC +5Vm 5 m 6 m 7 (m 5m ;m 7),Y A /BC AB /C / ABC m 3 mu/ / / \ / (m 3m 4) Z A /B /C / A /B /C A /BC / m 0 m 1 m 2 (m 0m ;m ;)/解:(2)歹0写表达式(4四、某学校学生参加三门课程A、B、C的考试,根据课程学时不同,三门课程考试及格分别可得2、4、5分,不及格均为0分,若总得分大丁等丁7分,便可结业。

院系电子信息工程学院班级姓名学号实验名称38译码器实现组合逻辑电路实验日期一、实验目的1.掌握常用集成组合电路的应用;2.掌握译码器的工作原理和特点;3.熟悉集成门电路、译码器的逻辑功能和管脚排列。

二、实验器件1.数字电路实验箱2.集成电路:74LS00、74LS138三、实验原理译码器所谓译码,就是把代码的特定含义“翻译”出来的过程,而实现译码操作的电路称为译码器。

译码器可分为三类:变量译码器、码制变换译码器和显示译码器。

变量译码器又称二进制译码器,用以表示输入变量的状态。

对应于输入的每一组二进制代码,译码器都有确定的一条输出线有信号输出。

若有n个输入变量,则有2n个不同的组合状态,就有2n个输出端。

而每一个输出所代表的函数对应于n 个输入变量的最小项。

74LS138为3/8译码器,管脚图如图所示:其中:A2、A1、A0为地址输入端Y0-Y7 为输出端,低电平有效STA、STB、STC 为选通端74LS138功能表如表3-2所示,当STA=1,STB+STC=0时,执行正常的译码操作,地址码所指定的输出端有信号输出(低电平0),其它所有输出端均无信号输出(全为1)。

当STA=0,STB+STC=1,或STA=,STB+STC=1时,译码器被禁止,所以输出同时为1。

指导教师签名院系电子信息工程学院班级姓名学号实验名称38译码器实现组合逻辑电路实验日期三、设计电路,实现四、(1)逻辑电路图(2)原理图指导教师签名院系电子信息工程学院班级姓名学号实验名称38译码器实现组合逻辑电路实验日期(3)实物连接图五、电路功能验证ABC为0,Y为1 A为1,BC为0,Y为0 AB为0,B为1,Y为0指导教师签名院系电子信息工程学院班级姓名学号实验名称38译码器实现组合逻辑电路实验日期AB为0,C为1,Y为0 A为0,BC为1,Y为0 ABC为1,B为1AB为1,C为0,Y为1 AC为1,B为0,Y为0指导教师签名。

译码器应用设计实验报告引言译码器(Decoder)是数字电路中常用的逻辑电路之一,它实现了将输入数字码转换成输出端口的控制信号。

译码器被广泛应用于数字系统中,如计算机、通信、测控等领域。

通常情况下,译码器基于真值表或卡诺图设计,可以根据输入的不同编码方式,输出相应的解码结果。

本实验主要介绍译码器的应用设计。

通过实验,我们将学会如何使用译码器来实现数字系统的控制和数据处理任务。

本实验所涉及的译码器有BCD-7段译码器、数值译码器、时序译码器以及存储器译码器等。

实验器材1. 逻辑计算器2. 示波器3. 数字电路实验箱4. 5V直流电源5. 译码器(BCD-7段译码器、数值译码器、时序译码器和存储器译码器)6. LED数码管实验原理1. BCD-7段译码器BCD-7段译码器是将4位BCD码转换成7段数码管显示的译码器。

8个BCD码,分别对应着数字0~9和字母A~F,输出接到控制7个LED数码管的段选端口和1个公共阴极的位选端口。

2. 数值译码器数值译码器是将4位二进制数转换成BCD码的译码器。

通过数值译码器,可以将数字的二进制编码转换成BCD编码,从而实现数字的BCD码显示。

译码器输出接LED数码管的输入端口。

时序译码器是根据不同状态的时序信号,将输入的二进制数码转换成对应的控制信号的译码器。

将时序信号和数码信号分别输入至译码器的两个输入端口,译码器将输出对应的动作信号。

常用于时序控制电路的设计中。

4. 存储器译码器存储器译码器是将存储芯片中的地址码转换成控制芯片的输入信号的译码器。

存储芯片中的地址码分别对应着芯片的不同存储单元,译码器将地址码转换成控制信号,使控制芯片可以正确访问存储芯片中的数据。

实验设计实验步骤:(1)将BCD码8个输入引脚分别接到译码器的8个输入端口上。

(4)将5V直流电源连接到译码器和LED数码管上。

实验结果:输入BCD码0000~1111时,LED数码管正确显示相应的数字0~9和字母A~F。

GDOU-B-11-112广东海洋大学学生实验报告书(学生用表)实验名称课程名称课程号学院(系) 专业班级学生姓名学号实验地点实验日期实验2 组合逻辑电路——138芯片一、实验目的1、掌握中规模集成译码器的逻辑功能和使用方法2、熟悉数码管的使用二、实验原理译码器是一个多输入、多输出的组合逻辑电路。

它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。

译码器在数字系统中有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数据分配,存贮器寻址和组合控制信号等。

不同的功能可选用不同种类的译码器。

译码器可分为通用译码器和显示译码器两大类。

前者又分为变量译码器和代码变换译码器。

1、变量译码器(又称二进制译码器),用以表示输入变量的状态,如2线-4线、3线-8线和4线-16线译码器。

若有n个输入变量,则有2n个不同的组合状态,就有2n个输出端供其使用。

而每一个输出所代表的函数对应于n个输入变量的最小项。

以3线-8线译码器74LS138为例进行分析,图6-1(a)、(b)分别为其逻辑图及引脚排列。

其中 A2、A1、A0为地址输入端,0Y~7Y为译码输出端,S1、2S、3S为使能端。

表6-1为74LS138功能表当S1=1,2S+3S=0时,器件使能,地址码所指定的输出端有信号(为0)输出,其它所有输出端均无信号(全为1)输出。

当S1=0,2S+3S=X时,或 S1=X,2S+3S=1时,译码器被禁止,所有输出同时为1。

(a) (b)图6-1 3-8线译码器74LS138逻辑图及引脚排列表6-1件就成为一个数据分配器(又称多路分配器),如图6-2所示。

若在S1输入端输入数据信息,2S=3S=0,地址码所对应的输出是S1数据信息的反码;若从2S端输入数据信息,令S1=1、3S=0,地址码所对应的输出就是2S端数据信息的原码。

若数据信息是时钟脉冲,则数据分配器便成为时钟脉冲分配器。

一、实验目的与要求1.了解和正确使用MSI组合逻辑部件;2.掌握一般组合逻辑电路的特点及分析、设计方法;3. 学会对所设计的电路进行静态功能测试的方法;4. 观察组合逻辑电路的竞争冒险现象。

预习要求:(1)复习组合逻辑电路的分析与设计方法;(2)根据任务要求设计电路,并拟定试验方法;(3)熟悉所用芯片的逻辑功能、引脚功能和参数;(4)了解组合逻辑电路中竞争冒险现象的原因及消除方法。

(5)二、实验说明译码器是组合逻辑电路的一部分。

所谓译码就是不代码的特定含义“翻译”出来的过程,而实现译码操作的电路称为译码器。

译码器分成三类:1.二进制译码器:把二进制代码的各种状态,按照其原意翻译成对应输出信号的电路。

如中规模2线—4线译码器74LS139,3线—8线译码器74LS138等。

2.二—十进制译码器:把输入BCC码的十个代码译成十个高、低电平信号。

3.字符显示译码器:把数字、文字和符号的二进制编码翻译成人们习惯的形式并直观地显示出来的电路,如共阴极数码管译码驱动的74LS48(74LS248),共阳极数码管译码驱动的74LS49(74LS249)等。

三、实验设备1.RXB-1B数字电路实验箱2.器件74LS00 四2输入与非门74LS20 双4输入与非门74LS138 3线—8线译码器四、任务与步骤任务一:测试3线—8线译码器74LS138逻辑功能将一片3线—8线译码器74LS138插入RXB-1B数字电路实验箱的IC空插座中,按图3-15接线。

A0、A1、A2、STA、STB、STC端是输入端,分别接至数字电路实验箱的任意6个电平开关。

Y7、Y6、Y5、Y4、Y3、Y2、Y1、Y0输出端,分别接至数字电路实验箱的电平显示器的任意8个发光二极管的插孔8号引脚地接至RXB—IB型数字电路实验箱的电源“ ”,16号引脚+5V接至RXB-1B数字电路实验箱的电源“+5V”。

按表3-2中输入值设置电平开关状态,观察发光二极管(简称LED)的状态,并将结果填入表中。