复位设计中的结构性缺陷及解决方案

- 格式:doc

- 大小:293.00 KB

- 文档页数:13

结构缺陷整改建议一、检测结构安全性在开始整改之前,首先要对结构进行全面的安全性检测。

检测的内容应包括结构的完整性、支撑体系、承载能力等方面。

如果发现有任何安全问题,必须立即停止使用并进行修复。

二、补强结构薄弱点在检测过程中,如果发现结构的薄弱点,需要进行补强处理。

补强的方法可以根据具体情况选择,例如增加支撑结构、加固构件等。

补强后应重新检测结构的强度和稳定性。

三、修复结构裂缝如果结构存在裂缝,需要进行修复。

修复的方法应根据裂缝的大小和位置选择,例如灌浆、填补等。

修复后应重新检测结构的完整性。

四、更换破损结构件如果发现结构件破损严重,无法修复或更换,应立即更换新的结构件。

更换时应保证新件的质量和规格符合要求,并确保安装正确牢固。

五、增强结构抗震性能为了增强结构的抗震性能,可以在关键部位增加抗震装置,例如抗震支架等。

同时,应定期进行抗震性能检测和维护,确保结构的稳定性和安全性。

六、调整结构布局合理性如果结构的布局不合理,可能会影响其承载能力和稳定性。

因此,需要对结构布局进行调整,使其更加合理。

调整的内容可以包括改变支撑点位置、增加支撑结构等。

七、确保结构材料质量为了确保结构的长期安全使用,必须确保所使用的结构材料质量符合要求。

材料的质量直接影响结构的承载能力和耐久性,因此应严格把关材料的采购和使用。

八、提高结构耐久性为了提高结构的耐久性,可以采取一些措施,例如对结构进行防腐处理、定期进行保养和维护等。

同时,在设计时应充分考虑环境因素对结构的影响,选择耐久性强的材料和工艺。

九、规范施工操作流程为了避免因施工不当导致的结构缺陷,应规范施工操作流程。

施工时应严格按照设计图纸和施工规范进行,确保每个环节的质量和安全。

同时,应对施工人员进行培训和考核,提高其技能和责任心。

总之,针对结构缺陷的整改需要全面考虑结构和安全性能、补强和修复等方面的问题,并采取相应的措施进行整改。

同时,应加强管理和维护,确保结构的安全性和耐久性。

电路结构设计交接中的常见失误与对策摘要:伴随着制造工艺的进步,集成电路具有的制造成本越来越低,集成度越来越高,含有的应用范围也是越来越广泛。

伴随着制造工艺的提升使得集成电路的性能越来越高,不过也是带来了很多的问题。

由于CMOS器件特征尺寸以及内部联线宽度的逐渐减小,电源电压的降低以及频率的升高,使得集成电路对于各种噪声、串扰以及电磁干扰等越来越敏感,由于这些引发的瞬态故障对于芯片来说也是具有很大的威胁,既有可能导致错误的操作,这样很大的可能降低了集成电路的可靠性。

为此本文将对于电路结构设计交接中的常见失误与对策进行研究,希望对于今后根据电路设计人员画的PCB,及用户提供的产品外形图,设计内部结构有所帮助。

关键词:制造工艺集成电路PCB引言印制电路板从第一代的单面板、第二代的双面板,发展到了第三代的多层板。

现在市场上又已经出现第四代印制电路板,一般称其为“积层法电路板”、“高密度互联电路板”或“微过孔板”。

在组装工艺技术方面,印制电路板PCB产品已经走过三个阶段,即通孔插装用PCB、表面安装用PCB和芯片封装用PCB。

目前,多层印制电路板正朝着高精度、高密度、高性能、微孔化、薄型化和高层化方向迅猛发展,其应用范围已从工业用大型电子计算机、通信仪表、电气测量、国防尖端及航空、航天等工业部门迅速进入到民用电器及其相关产品,如移动电话、笔记本计算机、小型摄像机、储存卡,等等。

1印制电路板结构设计的一般原则1.1印制电路板的热设计由于印制电路板基材耐温能力和导热系数都比较低,铜箔的抗剥离强度随工作温度的升高而下降。

印制电路板的工作温度一般不能超过85℃。

主制板结构设计时,其散热主要有以下几种方法:均匀分布热负载、元器件装散热器,在印制板与元器件之间设置带状导热条、局部或全局强迫风冷。

1.2印制电路板的减振缓冲设计印制电路板是电子产品中电路元件和器件的支撑件,它提供电路元件和器件之间的电气连接。

为提高印制板的抗振、抗冲击性能,板上的负荷应合理分布以免产生过大的应力。

单片机复位电路设计与探讨单片机(MCU)在应用中,通常需要通过复位电路进行效率和功能的优化。

这一设计环节往往被称为MCU系统调试中极为重要的一步。

本文将探讨单片机复位电路的设计与实现,以便读者加深对MCU系统复位的理解。

复位是使一个单片机将所有的软件和硬件状态恢复到初始状态的一种方式。

当MCU遇到无法解决的异常或错误时,或因电源干扰等外部因素,都需要通过复位,使其回到一个稳定状态。

MCU复位电路通常由复位源和复位触发电路组成。

常见的复位源有手动复位电路,电源复位电路,看门狗复位电路等。

在实际设计中,一些MCU自带的复位电路往往满足不了实际应用所需的精度和可靠性,因此需要重新设计。

一个好的复位电路应该能够提供高精度、高灵敏度和高稳定性的复位保护,防止MCU失去控制和应用系统出现故障。

复位电路设计中需要注意的一些关键因素:1. 复位触发条件的选择:在设计复位时,需要根据应用场景的特点和实际需要选择合适的复位触发条件。

复位电路中的电路元件应选用高精度、低误差和高可靠性的元器件,以确保复位的精度和稳定性。

2. 复位信号处理的效果:复位电路一般是由多个电路元件构成的复合型电路,因此需要合理的排布和协调。

在实际设计中要根据MCU的特性,对复位信号进行处理和延时,确保复位电路的稳定性和可靠性。

3. 电源噪音对复位的影响:当出现电源波动或噪声时,复位电路可能产生误触发。

因此需要采用合适的电源滤波和隔离技术,以提高抗噪性和稳定性。

4. 硬件复位和软件复位的选择:硬件复位和软件复位的选择与实际应用情况和需要有关。

如在某些特殊的应用场合,硬件复位可能会带来实际效果的优化。

总而言之,MCU复位电路设计是整个系统设计中一个非常关键的环节。

合理选择复位源、设计合理的触发条件以及采用合理的电路元件进行复位信号处理,都是产生高精确度、高可靠性和高稳定性的复位电路的关键因素。

任何与MCU相关的设计中,复位电路的设计都是维护稳定运行和避免系统故障的关键步骤。

桥梁缺陷共性问题整改修复方案第一篇:桥梁缺陷共性问题整改修复方案桥梁交工检测缺陷共性问题整改修复方案一、梁体及T梁梁体非结构裂缝封闭处理1、对非预应力现浇箱梁及箱梁、T梁梁体不是梁底横向、腹板竖向和翼缘板纵向的裂缝,对裂缝宽度≤0.15mm的,采用封缝胶封闭处理;对裂缝宽度>0.15mm的,采用“毕可法”先灌注结构胶后,再横向加贴一层300 g/ m碳纤维布(垂直裂缝的方向)。

2、对翼缘板与腹板纵向裂缝,应分清对结构影响大小。

对结构影响不大的浅表裂缝,原则对裂缝宽度<0.1mm者,封缝胶封闭处理;≥0.1mm者采用“毕可法”注胶封闭处理。

3、对梁板结构裂缝粘贴碳纤维布原则,纤维布的长度应从裂缝尖端向外延伸各1米、宽度最小为0.5米(即裂缝两侧各向外延伸0.25米)。

对裂缝处于梁板底部的,应视病害大小加贴一至三层碳纤维布,T梁马蹄部分碳纤维布应横向包裹至与腹板交界处。

二、梁板局部砼掉块、空洞露筋、蜂窝露筋缺陷1、单块面积小于0.1m(对砼整体性影响较小)的。

对露筋进行除锈处理,清洁创口,并用结构胶进行填补。

2、单块面积大于0.1m。

对露筋进行除锈处理,清洁创口,用结构胶或环氧砂浆进行填补,并沿主筋方向加贴一层300g/ m碳纤维布。

三、梁板局部砼松散、空洞露波纹管缺陷1、清除松散砼后,内部无空洞、蜂窝的,对露筋进行除锈处理,清洁创口,用结构胶或环氧细石砼进行填补,并按以下的第3点要求加贴碳纤维布。

2、清除松散砼后,内部仍有空洞、蜂窝的,对露筋进行除锈处理,清洁创口,用结构胶进行填补,并预留注浆孔灌注结构胶封闭,最后按以下的第3点要求加贴碳纤维布。

须小心清除松散砼,特别是内部砼,以确保修复过程中结构安全。

3、贴碳纤维布原则及技术指标:清除松散砼后,缺陷宽度小等于0.5m的,沿波纹管方向加贴一层300 g/ m碳纤维布;清除松散砼后,缺陷宽度大于0.5m的或该缺陷边缘0.5m范围内有类似缺陷的,沿波纹管方向加贴三层300 g/ m碳纤维布(沿波纹管先纵后横再纵),原则碳纤维布四周超出处理范围,且不小于0.50m,对T梁漏波纹管者,贴碳纤维布应将马蹄部分横向包裹至顶。

监控芯片因电源问题引起异常复位的处理办法在单片机系统设计中,对系统的EMI、信号完整性、时序设计都能引起足够的重视;但对于电源完整性引起的地弹和电源反弹的问题,很多设计者还是认识得不清晰。

在单片机系统设计中,有时由于芯片自身缺陷或芯片之间接口驱动配合不当引起的系统不稳定,甚至不能工作的情况非常多。

下面通过对微处理器监控芯片MAX818在使用中出现异常复位的实例分析,说明由于电源完整性引起的系统工作不稳定现象。

1 系统描述图1为μP监控电路。

监控芯片MAX818具有电源低压监视、电池管理、RAM片选锁定及微处理器硬件看门狗功能。

电源低压监视是当系统电压低于芯片设定电压时,MAX818发出复位信号。

电池管理是当VCC高于电池VBATT时,OUT切换到VCC,电池处于浮充状态;当VCC低于VBATT时,OUT切换到VBATT,由电池供电。

RAM片选锁定用于上电或掉电时保护RAM中的数据不丢失且正确读写。

微处理器硬件看门狗的作用是当程序跑飞,喂狗信号WDI 得不到服务时,芯片发出复位信号,复位系统。

WDI信号悬空时,MAX818自动发出复位信号的功能禁止。

系统RAM片选信号由CPU的地址线,控制线经EPLD译码后输出接到MAX818的CEIN,经MAX818输出脚CEOUT接到RAM片选CE上。

RAM的供电电源由MAX818的OUT输出引脚提供。

2 系统异常复位现象及分析解决在单片机系统调试过程中,将监控芯片MAX818的看门狗清除引脚WDI悬空,使MAX818的复位功能禁止,且程序处于仿真状态,这时系统软硬件一切功能正常。

仿真调试完毕,将程序写入Flash中让其运行,系统总是不停地复位、重启。

MAX818的复位脚不停地发出复位信号,用示波器观察的波形如图2所示。

将WDI悬空重新仿真,系统正常;将WDI悬空,写入Flash,系统正常。

分析认为是MAX818自己在发出复位信号。

理论上能引起MAX818复位的原因有以下2点:①超过1.6s,MAX818引脚(6)WDI没有喂狗信号,能引起复位;②系统电源低于MAX818电源电压设定值4.65V,能引起复位。

阻容复位电路中几个需要注意的问题C-DesignNov 16 2008声明本文为作者原创作品,公开发布在本人主页上。

本文仅供学习参考之用,未经作者书面许可,不得用于商业目的或出版。

欢迎其他网站转载本文档,但应保证其所有部分的完整性。

C-DesignNov 16 2008阻容复位电路中几个需要注意的问题阻容复位电路是常用的单片机复位电路,他利用电容充电过程实现复位所需要的信号电平和延迟时间,以完成单片机“上电复位”的需要。

图①给出了常见的51单片机阻容复位电路,不过这个电路是有缺陷的。

图①第一个缺陷在于:当电源供应中断后,电容上所存储的电能需要通过电阻R1缓慢释放,若电源在短时间内重复开关,将导致复位电路无法正确动作。

图②给出了一种解决方案:在电阻R1两端并联一个开关二极管。

当电源供应中断后,二极管将为电容提供一个快速的放电通道(如图中箭头所示)。

第二个缺陷是:在复位过程中,电容上的电压将缓慢变化。

这是由阻容电路的特性决定的,但是这个信号对于作为数字器件的单片机来说却是非常糟糕的。

当然在大部分时候,这样的复位电路已经可以工作了,但考虑到方案的完善性,我们给出了图③所示的电路。

图② 充电电流放电电流图③改进的方案使用施密特输入的非门74HC14对阻容复位电路输出信号进行整形,施密特门的特性是可以接受缓慢变化的输入信号,并将他们整形为理想的数字信号。

需要注意的是,由于非门将信号的极性颠倒,电阻和电容的位置应该互换,图中的开关S1用于手动复位。

这已经是一个比较完善的复位电路了。

与阻容复位相比,更加专业可靠的复位方案是使用专门的“复位芯片”如常见的MAX809、MAX810等(见图④),这种芯片只有3个引脚:电源、地和复位信号输出,使用起来非常方便。

他们可以监视电源电压的波动并在欠压时给出复位信号。

一般来说,在简单的产品中,阻容复位电路可以工作得很好,但是在讲求可靠性的场合,复位芯片就是首选。

图④四川 江海波。

台式机复位故障检修台式机复位故障检修复位(Reset)是主板上各个元件工作的重要条件之一,因此,复位电路也是主板上故障频发的部份之一,在这一章里咱们针对复位电路的各类故障来进行分析和讲解。

使大家能初步掌握复位电路故障的维修方式。

复位电路的故障可以分为全板无复位、CPU 无复位、其它无复位这三种。

5.1 全板无复位故障的维修5.1.1 全板无复位故障的现象全板无复位指的就是主板上的关键复位点上的复位信号都为低电平,这种情况下,复位信号视为无效。

对于具体的测量位置,在第3 章中关于复位故障的现象的描述中,已经作了大致的介绍。

咱们可以通过量测相应的故障点来肯定主板是不是处于全板无复位的情况。

另外,咱们也可以观察DEBUG 上的指示灯的情况来做判断,拿咱们常利用的DEBUG 卡来讲,正常情况下主板加电以后,复位灯指示灯也是闪一下后就熄灭,若是复位指示灯处于长亮的状态,则说明PCI 槽上的复位信号为低电平,即PCI 无复位。

(需要注意的是,有的DEBUG 卡由于设计上的原因,复位灯长亮才为正常,如维修工具市场上常见的俄罗斯诊断卡,在正避免出现判断错误)5.1.2 全板无复位故障的维修方式在对全板无复位的主板进行维修之前,咱们先来了解一下复位产生的流程,如图5-1 所示,在这个复位电路流程中,当ATX电源正常输出出12V、5V、3.3V等电源后,就会由ATX的电源插头发出一个PWR_OK信号别离到南桥,与此同时,12V 或5V 的电压输出到CPU 供电电路,当CPU 的Vcore 供电顺利产生后会产生一个VRM_GD 信号。

而且ATX 上的电压通过相应MOS 管转换后输送给北桥,北桥的工作电压正常后,北桥也会发出一个CHIP_GD 的信号。

当PWR_OK、VRM_GD、CHIP_GD 这三个信号传送到南桥,通知南桥各部份的电压都OK 以后,南桥通过内部的逻辑运算,发出PCIRST#信号(最大体的复位信号)到7414 或7407 的门电路,通过门电路处置后,分化为PCIRST#1、PCIRST#2、IDERST# PCIRST#1 用来复位I/O、1394、网卡、AGP、北桥、FWH BIOS。

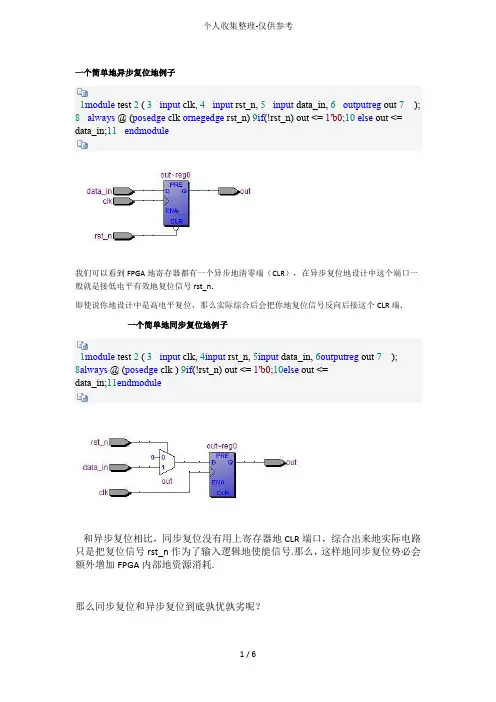

一个简单地异步复位地例子1module test 2 ( 3input clk, 4input rst_n, 5input data_in, 6outputreg out 7); 8always @ (posedge clk ornegedge rst_n) 9if(!rst_n) out <= 1'b0;10else out <= data_in;11endmodule我们可以看到FPGA地寄存器都有一个异步地清零端(CLR),在异步复位地设计中这个端口一般就是接低电平有效地复位信号rst_n.即使说你地设计中是高电平复位,那么实际综合后会把你地复位信号反向后接这个CLR端.一个简单地同步复位地例子1module test 2 ( 3input clk, 4input rst_n, 5input data_in, 6outputreg out 7);8always @ (posedge clk ) 9if(!rst_n) out <= 1'b0;10else out <=data_in;11endmodule p1Ean。

和异步复位相比,同步复位没有用上寄存器地CLR端口,综合出来地实际电路只是把复位信号rst_n作为了输入逻辑地使能信号.那么,这样地同步复位势必会额外增加FPGA内部地资源消耗.那么同步复位和异步复位到底孰优孰劣呢?只能说,各有优缺点.同步复位地好在于它只在时钟信号clk地上升沿触发进行系统是否复位地判断,这降低了亚稳态出现地概率;它地不好上面也说了,在于它需要消耗更多地器件资源,这是我们不希望看到地.FPGA地寄存器有支持异步复位专用地端口,采用异步复位地端口无需额外增加器件资源地消耗,但是异步复位也存在着隐患.异步时钟域地亚稳态问题同样地存在与异步复位信号和系统时钟信号之间.再看下面一个两级寄存器异步复位地例子1module test 2 ( 3input clk, 4input rst_n, 5input a, 6outputreg c 7); 8 9regb;10always @ (posedge clk ornegedge rst_n)11if(!rst_n) b <= 1'b0;12else b <=a;1314always @ (posedge clk ornegedge rst_n)15if(!rst_n) c <= 1'b0;16else c <= b; 1718endmodule5PCzV。

单片机系统中复位电路的可靠性分析与设计首先,在分析复位电路可靠性之前,有必要了解复位电路的基本原理。

复位电路的主要功能是在系统通电或特定条件发生时将单片机的复位引脚拉低一段时间,使单片机按照预定的状态重新启动,从而保证系统正常运行。

常见的复位电路包括普通复位电路、功率上复位电路、看门狗复位电路等。

复位电路可靠性的分析主要从以下几个方面入手:1.电源稳定性:复位电路的工作依赖于电源的稳定性。

如果电源波动较大,可能会导致复位信号不稳定,引起系统复位异常。

因此,建议在设计中增加稳压电路、滤波电路等措施,确保电源的稳定性和纹波小。

2.噪声干扰:单片机工作环境中存在各种噪声,如电磁干扰、射频干扰等,这些干扰可能导致复位电路误触发或失效。

为了解决这一问题,可以采用屏蔽措施、使用滤波电路或选择抗干扰能力较强的电路器件等。

3.瞬态故障:在系统工作过程中,可能会出现瞬态故障,例如电源电压的瞬间下降、电流的瞬间增加等,这些瞬态故障可能会导致单片机复位异常。

为了提高复位电路的可靠性,可以选择具有快速响应速度的复位电路器件,以及增加滤波电路等。

4.可靠性设计:在复位电路的设计中,还需要考虑电路的可靠性和容错性。

可以采用多级复位电路设计、冗余复位电路设计等方式,以提高系统的容错能力。

在设计复位电路时,需要根据具体应用场景的需求,选择合适的复位电路方案和元器件。

例如,在高可靠性要求场景下,可以选择使用看门狗复位电路,它可以根据系统的状态监测,自动产生复位信号;在对复位速度有较高要求的场景下,可以采用功率上复位电路,它可以在电源波动瞬间产生复位信号。

综上所述,单片机系统中复位电路的可靠性对整个系统的正常运行起着至关重要的作用。

在设计中,需要考虑电源稳定性、噪声干扰、瞬态故障等因素,并采取相应的设计措施,以提高复位电路的可靠性。

此外,根据具体应用场景的需求选择合适的复位电路方案和元器件也是提高可靠性的重要手段。

单片机系统中复位电路的可靠性分析与设计复位电路在单片机系统中起到重要的作用,它负责在系统发生各种故障或不正常情况时将系统带到安全状态,并重新初始化系统的各个部分。

因此,复位电路具有关键的可靠性要求。

本文将对复位电路的可靠性进行分析,并提出一种设计方法。

首先,我们来分析复位电路的可靠性。

复位电路通常由一个复位信号源、一个复位信号处理器和一个复位信号分发器组成。

可靠性问题主要涉及到复位信号源的稳定性、复位信号处理器的准确性和复位信号分发器的可靠性。

复位信号源的稳定性是保证系统能够正确进入复位状态的关键。

复位信号源通常包括一个或多个用于检测系统状态的感应器,这些感应器可能受到环境变化、电磁干扰等因素的影响,从而导致复位信号的误触发或未触发。

因此,在设计复位信号源时,需要考虑这些因素,并采取措施来减小其影响。

例如,可以使用滤波器来滤除环境噪声,或者使用冗余电路来增加可靠性。

复位信号处理器的准确性是保证系统能够正确处理复位信号的关键。

复位信号处理器通常包括一个或多个逻辑电路和一个时钟源。

逻辑电路可能存在故障或时钟信号可能出现不稳定或漂移,从而导致复位信号的处理错误。

因此,在设计复位信号处理器时,需要选择可靠的逻辑电路和时钟源,并采取措施来检测和纠正故障。

例如,可以使用冗余逻辑电路来增加可靠性,或者使用故障检测和纠正技术来提高容错性。

复位信号分发器的可靠性是保证系统能够正确接收复位信号的关键。

复位信号分发器通常包括一个或多个缓冲器和一个或多个开关电路。

缓冲器可能存在故障或开关电路可能出现打开或关闭错误,从而导致复位信号的传输错误。

因此,在设计复位信号分发器时,需要选择可靠的缓冲器和开关电路,并采取措施来检测和纠正故障。

例如,可以使用冗余缓冲器和开关电路来增加可靠性,或者使用故障检测和纠正技术来提高容错性。

在设计复位电路时,还需要考虑电源稳定性、电路布局和材料选择等因素。

电源稳定性是保证各个部分正常运行的基础,需要选择稳定的电源和适当的电源降噪电路。

单片机复位种类和故障外部复位(External Reset)它是影响时钟模块和所有内部电路,属于同步复位,但外部Reset引脚为逻辑低电平。

在引脚变为低电平后,CPU的复位控制逻辑单元确认复位状态直到Reset释放。

复位控制逻辑保持复位低电平状态,在额外512个时钟周期内。

因为当复位引脚为低电平时与MCU执行复位命令是相互冲突的,因此复位引脚必须保证520时间周期内低电平才能保证外部复位被外部总线辨识出来。

上电复位(Power-on reset)它是由外部总线产生的一种异步复位。

单片机在电源电压VDD小于大约2.5V的时候复位,只要VDD电压不超过这个阈值,单片机就仍然保持复位状态。

电压跌落的时间大概在纳米级(如果一旦出现了,马上会复位)。

因此监测上电复位不能单片机内部,因为小于这个电压单片机逻辑功能。

低电压复位(Low-Voltage Reset)它是部分单片级内部监控器形成的异步复位,单片机电压小于一定触发值时,单片机开始复位。

低电压的复位电平是和供电电压相关的,会有一个波动:软件复位(Software Reset)它是由软件看门狗定时器超时引起的一个异步复位。

如果要开启软件复位,必须要注意设置软件内部寄存器,使之有效。

这个功能主要是用来防止程序跑飞。

双总线故障复位(Double Bus Fault Reset)它是由双总线错误监视器产生的异步复位,它是总线错误的特殊状态会导致中止异常处理。

时钟丢失复位(Loss of Clock Reset)它在参考时钟子模块消失的时候产生的同步复位。

如果要使该复位有效,需要设置寄存器SYNCR。

关于更详细的外部Reset的资料可以这样描述(51单片机):为了确保良好的外部复位和上电复位,复位脉冲宽度必须足够宽,我们要考虑以下两个参数来确定复位脉冲宽度:tosc:振荡器才可达到Vih1或Vil1电压的时间。

tvddrise:电压VDD由10上升至90%的时间。

产品结构设计缺陷及改良方法集粹1. 结构优化装配工艺及结构可靠性在我们的结构设计目标中,除了保证结构的功能外,简化我们的装配工艺和保证结构的可靠性也是结构设计需要考虑的重要方面。

案例i).设计要求和背景:悬臂梁能轻松装配进轴孔,并且能够承受一定的拉力而不掉出来。

我们先来看一下常见的两个设计方案。

对于方案1,显然可以变形的部位长度偏短,变形比较困难所以导致装配比较难,而且装配的过程中很容易会给零件造成永久性损坏。

而对于方案2,因为开了一条通槽,使得发生变形的部分长度大为增加,从而使得在装配过程中变形比较容易,换言之就是装配比较容易,但也正因为通槽的存在,装配好之后轴的受力稍大便会因两侧的变形而造成脱落。

方案1:装配困难且容易损坏零件方案2:装配容易但容易脱落通过上面两个方案的分析,我们知道我们的设计要点实际上是如何实现变形的单方向。

也就是说我们的设计应该使得在装配过程中的变形比较容易而在装配好之后自然受力的情况下不容易发生变形;根据这个要求我们作出了下面的设计改良,实际生产应用中也得到了很好的效果。

改良方案:装配容易而不容易脱落2. 结构优化装配及拆卸工艺简化并优化成品的装配及拆卸工艺,实际就可以达到减少产品成本,提高生产效率的一个方式。

案例i).设计要求和背景:副零件要能轻松压入ABS零件中,并且可以容易取出以更换副零件。

卡勾的高度5.0mm因为空间的问题不能再增加。

上图也是通常的设计方案,但对这个设计方法,缺点是很明显的。

因为卡勾的高度限制,强行压入副零件会比较困难,并且在压入过程中容易对ABS零件造成损坏。

对于需要多次更换而进行的装配更会因疲劳而造成永久性损坏。

针对以上问,我们采用了U型搭勾的方式来实现单向自然变形。

实际证明装配简单而固定性好。

案例ii).设计要求:装配方法简单。

分析:两件东西通过一个长螺柱装配,但涉及到三个孔的对齐问题,并且中间部分的通孔长度比较长,导致在实际装配的过程中比较难对正装配孔影响装配效率。

一、引言在设计过程中,我们难免会遇到一些拙劣的设计。

这些设计可能因为各种原因而存在缺陷,如功能不完善、用户体验不佳、视觉效果差等。

为了提高设计质量,及时发现并解决问题,本文将对拙劣设计进行总结,并提出相应的改进措施。

二、拙劣设计的表现形式1. 功能不完善(1)界面布局不合理,导致操作不便。

(2)功能缺失,无法满足用户需求。

(3)操作逻辑混乱,难以理解。

2. 用户体验不佳(1)交互设计不合理,操作繁琐。

(2)界面元素过于复杂,难以识别。

(3)反馈信息不及时,无法让用户了解操作结果。

3. 视觉效果差(1)颜色搭配不合理,视觉效果不佳。

(2)图标设计简单,缺乏创意。

(3)字体选择不当,影响阅读体验。

三、拙劣设计的成因分析1. 设计人员缺乏经验(1)对设计规范和标准了解不足。

(2)对用户需求把握不准确。

2. 项目时间紧张(1)设计周期短,导致设计时间不足。

(2)需求变更频繁,影响设计进度。

3. 缺乏沟通与协作(1)设计师与产品经理、开发人员沟通不畅。

(2)设计团队内部缺乏协作,导致设计方案不完善。

四、改进措施1. 加强设计团队建设(1)招聘有经验的设计师,提高团队整体水平。

(2)定期组织培训,提升设计师的专业素养。

2. 优化设计流程(1)明确设计规范和标准,提高设计质量。

(2)加强与产品经理、开发人员的沟通,确保需求明确。

3. 注重用户体验(1)进行用户调研,了解用户需求。

(2)优化交互设计,提高操作便捷性。

4. 提升视觉效果(1)学习优秀设计案例,提高审美水平。

(2)关注色彩搭配、图标设计等方面,提升视觉效果。

五、总结拙劣设计是影响产品品质的重要因素,我们应认真对待并加以改进。

通过加强设计团队建设、优化设计流程、注重用户体验和提升视觉效果等方面,提高设计质量,为用户提供更好的产品。

在今后的工作中,我们要不断总结经验,提高自己的设计能力,为我国设计事业贡献力量。

随着数字化设计和SoC的日益复杂,复位架构也变得非常复杂。

在实施如此复杂的架构时,设计人员往往会犯一些低级错误,这些错误可能会导致亚稳态、干扰或其他系统功能故障。

本文讨论了一些复位设计的基本的结构性问题。

在每个问题的最后,都提出了一些解决方案。

复位域交叉问题1. 问题在一个连续设计中,如果源寄存器的异步复位不同于目标寄存器的复位,并且在起点寄存器的复位断言过程中目标寄存器的数据输入发生异步变化,那么该路径将被视为异步路径,尽管源寄存器和目标寄存器都位于同一个时钟域,在源寄存器的复位断言过程中可能导致目标寄存器出现亚稳态。

这被称为复位域交叉,其中启动和捕捉触发的复位是不同的。

在这种情况下,C寄存器和A寄存器的起点异步复位断言是不同的。

在C寄存器复位断言过程中而A触发器没有复位,如果A寄存器的输入端有一些有效数据交易,那么C寄存器的起点异步复位断言引起的异步变更可能导致目标A寄存器发生时序违规,从而可能产生亚稳态。

图1:复位域交叉问题在上面的时序图中,当有一些有效数据交易通过C1进行时,rst_c_b获得断言,导致C1发生异步改变,w.r.t clk从而使QC1进入亚稳态,这可能导致设计发生功能故障。

2. 解决方案* 使用异步复位、不可复位触发器或D1触发器POR.* 如果复位源rst_c_b是同步的,那么则认为来自C_CLR --> Q的用于从rst_c_b_reg-->C_CLR-->C_Q1-->C1-->A_D进行设置保持检查的时序弧能够避免设计亚稳态。

然而,通常在默认情况下C_CLR-->Q时序弧在库中不启用,需要在定时分析过程中明确启用。

* 在目的地(A)使用双触发器同步器,以避免设计中发生亚稳态传播。

然而,设计人员应确保安装两个触发器引入的延迟不会影响预期功能。

由于组合环路导致复位源干扰1. 问题在SoC 中,全局系统复位在设备中组合了软件或硬件生成的各种复位源。

LVD复位、看门狗复位、调试复位、软件复位、时钟丢失复位是导致全局系统复位断言的一些示例。

然而,如果由于任何复位源导致的全局复位断言是完全异步的,且复位发生源逻辑被全局复位清零,那么设计中会产生组合环路,这会在该复位源产生干扰。

组合路径的传播延迟会根据不同的流程、电压或温度以及干扰范围而不同。

如果设计中使用了组合信元用于复位断言和去断言,那么也会导致模拟中出现紊乱情况。

这被视为设计人员的非常低级的错误。

图2:复位源干扰(基本问题)在上图中,当复位源SW_Q断言时,会导致rst_b断言,这是全局复位。

现在,如果全局复位本身被用于清除“SW_Q” 复位断言,那么会在设计中在SW_Q输出和全局复位时产生干扰。

此外,在模拟中,这会导致紊乱情况,因为复位源断言试图通过该组合逻辑去断言。

然而,如果复位源(SW_Q)在复位状态机(触发器的SET/CLR输入)为全局复位断言被异步使用,那么复位干扰可能能够复位整个系统(通过断言全局复位),因为全局系统复位去断言不仅仅与复位源去断言相关。

当该复位源(有干扰)被同步使用或在触发器D输入使用的情况下可能依然有一个问题。

干扰范围可能无法在至少一个周期内保持稳定,因此这不会被目标触发器捕获。

此外,该复位源不能被用作任何电路的时钟(除了脉冲捕捉电路),因为它可能违反时钟宽度。

图3:复位源干扰(问题2)在上图中,复位源SW_Q将出现干扰。

虽然如果复位源SW_Q的干扰在某个触发器被捕捉作为复位事件状态(在S)或用于其他目的,全局复位输出(rst_b)都没有干扰,但它将导致时序违反/亚稳态,或根本不可能被捕获。

2. 解决方案* 设计人员永远都不应犯下上述(图2)低级错误。

* 如果复位实现如图3所示,那么设计人员应保证复位源(在该示例中为SW_Q)总是在触发器的SET/CLR输入使用,而不在D或CLK使用。

* 解决这个问题的最好的方法是在复位状态机中使用之前注册该复位源。

虽然它将导致时钟依靠全局复位断言,但是无论如何,如果没有时钟,该内部复位(SW_Q)都不会断言。

请参见图4.图4:解决方案1此外,用户也可以扩展SW_Q断言,然后再在设计中使用它,复位断言与时钟无关。

请参见图5.图5:解决方案2复位路径的组合逻辑1. 问题(I)如果组合逻辑输入大约在同一时间发生变化,那么使用复位路径中的组合逻辑可能产生干扰,这可能在设计中触发虚假复位。

下面是一个RTL代码,它会在设计中意外复位。

assign module_a_rstb = !((slave_addr[7:0]==8'h02 & write_enable & (wdata[7:0]==00)) always @(posedge clk or negedge module_rst_b)if(!module_rst_b) data_q <= 1'b0;else data_q <= data_d;在上面的示例中,slave_addr,write_enable和wdata改变它们的值w.r.t system clock,使用静态时序分析,设计人员可以保证在目标触发器的设置时间窗口之前这些信号在一个时钟周期内的稳定性。

然而,在该示例中,这些信号直接用作触发器的异步清零输入。

因此,即使在特定的时间slave_addr[7:0]在逻辑上将其值从“00000110”改为“01100000”,但由于组合逻辑的传播延迟(净延迟和信元延迟)它可以用一个序列“00000110 --> 00000010 --> 00000000 --> 01000000 --> 01100000”生成过渡。

在这段时间里,salve_addr为“00000010”,如果wdata[7:0]始终为零且“write_enable” 已经被断言,那么它将在module_rst_b创建一个无用脉冲,从而导致虚假复位。

图6:复位路径的组合逻辑2. 解决方案首先注册组合输出,然后再将其用作复位源(如图7所示)。

图7:复位路径的组合逻辑解决方案3. 问题(II)在上面的示例中,复位路径的组合逻辑解决方案并不完善。

如果组合逻辑输入大约在同一时间发生变化,那么它可能在设计中触发虚假复位。

然而,如果组合逻辑的输入信号变化相互排斥,那么它可能不会引起任何设计问题。

例如,测试模式和功能模式相互排斥。

因此复位路径的测试复用是有效的设计实践。

然而,对于某些情况,变化相互排斥的静态信号或信号可能会导致设计出现虚假复位触发。

下面的示例描述了此类设计可能出现问题。

图8:复位路径的组合逻辑(问题2).在上面的示例中,多路复用结构用于复位路径,同时进行RTL编码。

其中“mode” 是一个控制信号,不频繁改变,而mode0_rst_b和mode_1_rst_b是两个复位事件,然而在合成RTL时,在门控级它被分解成不同的复杂的组合(And-Or-Invert[AOI])信元。

虽然在逻辑上它相当于一个多路复用器,但由于不同的信元和净延迟,每当信号“mode”从1-->0变化时,final_rst_b都会产生干扰。

4. 解决方案* 在合成过程中在复位路径保留多路复用结构,因为多路复用结构与其他组合逻辑相比易于产生干扰。

MUX Pragma可以在编码RTL时使用,这将有助于合成工具在复位路径中保留任何多路复用器。

设计中的同步复位问题1. 问题(I)在许多地方,设计人员在时钟方面喜欢同步复位设计。

原因可能是为了节省一些芯片面积(带有异步复位输入的触发器比任何不可复位触发器都大)或让系统与时钟完全同步,也可能有一些其他原因。

对于此类设计,当复位源被断言时需要向设计的触发器提供时钟,否则,这些触发器可能会在一段时间内都不进行初始化。

但当该模块被插入一个系统时,系统设计人员可能选择在复位阶段禁用其时钟(如果在一开始不需要激活该模块),以节省整个系统的动态功耗。

因此,该模块甚至在复位去断言后一段时间内都不进行初始化。

如果该模块的任何输出直接在系统中使用,那么将捕获未初始化和未知的值(X),这可能会导致系统功能故障。

图9:同步复位问题时序图2. 解决方案在复位阶段启用该模块的时钟且持续最短的时间,使该模块内的所有触发器都在复位过程中被初始化。

当系统复位被去断言时,模块输出不会有任何未初始化的值。

图10:同步复位问题已解决3. 问题(II)在时钟域交叉路径使用两个触发同步器是常见做法。

然而,有时设计人员对这些触发器使用同步复位。

相同的RTL代码是always @(posedge clk )if(!sync_rst_b) beginsync1 <= 1'b0; sync2 <= 1'b0 ;endelse beginsync1 <= async_in; sync2 <= sync1end在硬件中进行了RTL合成后,上面的代码会在双触发器同步器的同步链中引入组合逻辑,这会带来风险,并缩短sync2触发器输入进入亚稳态的时间。

图11:同步复位问题22. 解决方案可用以下方式编写RTL代码,以避免同步链的组合逻辑。

always @(posedge clk )if(!sync_rst_b) beginsync1 <= 1'b0;endelse beginsync1 <= async_in; sync2 <= sync1end在上面的代码中,对sync2触发器不使用复位,因此在同步链中不会实现组合信元。

然而,需要注意sync2需要一个额外的周期才能复位,这不应导致设计出现任何问题。

冗余复位同步器引起的问题1. 问题在使用多个异步时钟的设计中,设计人员需要确保在目标寄存器使用的时钟方面,异步复位的同步去断言,否则可能导致目标触发器发生时序违反,从而产生亚稳态。

复位同步器被用来复位去断言,与目标时钟域同步。

然而,只有在系统复位去断言过程中有目标时钟时才会发生复位去断言时序违反。

如果在复位去断言时没有时钟,那么便不会有任何时序违反。

因此,在设计多时钟域模块时,设计人员可以让编译时间选项绕过该模块中的那些复位同步器,并让系统集成商根据对该模块的时钟可用性决定是否需要使用复位同步器。

此外,如果系统时钟和异步时钟比非常高,冗余同步器甚至会造成设计功能性问题。

下面描述了这个问题。

图12:冗余同步器的问题在上面的设计中,去断言与sys clk同步的系统复位被馈送到(mod_clk域)的复位同步器,然后在mod_clk域逻辑中使用该复位。

让我们假定sys clk : mod_clk的时钟频率比大于6:1.默认不启用mod_clk,以节省动态功率。

当用户想要启用mod_clk域逻辑的功能时,便启用该时钟。