STM32F103引脚功能定义

- 格式:pdf

- 大小:461.98 KB

- 文档页数:12

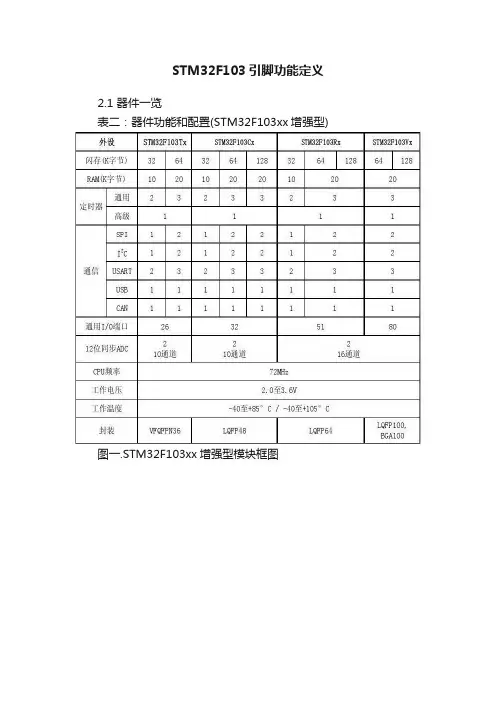

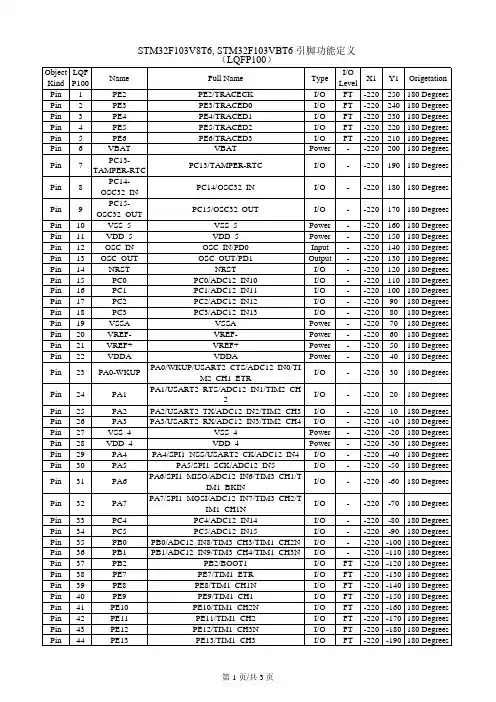

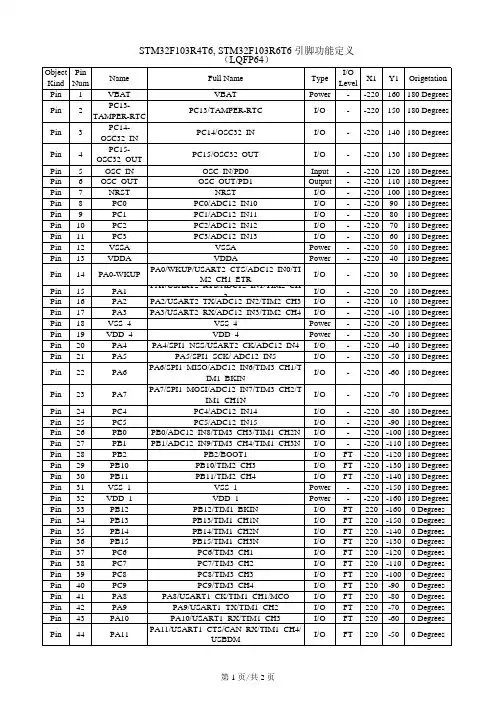

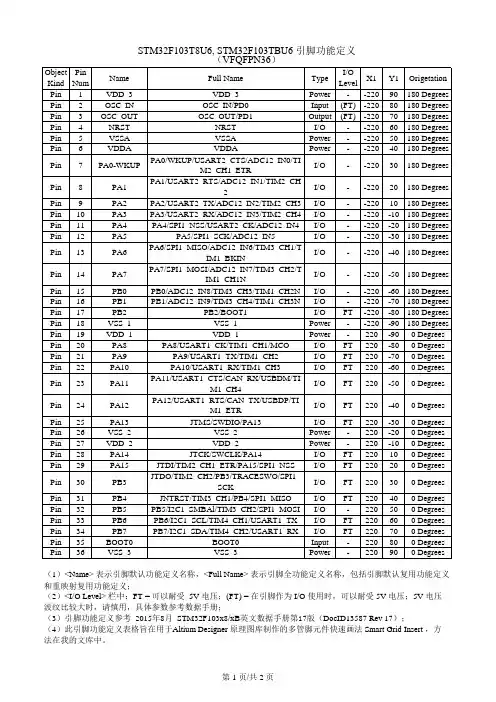

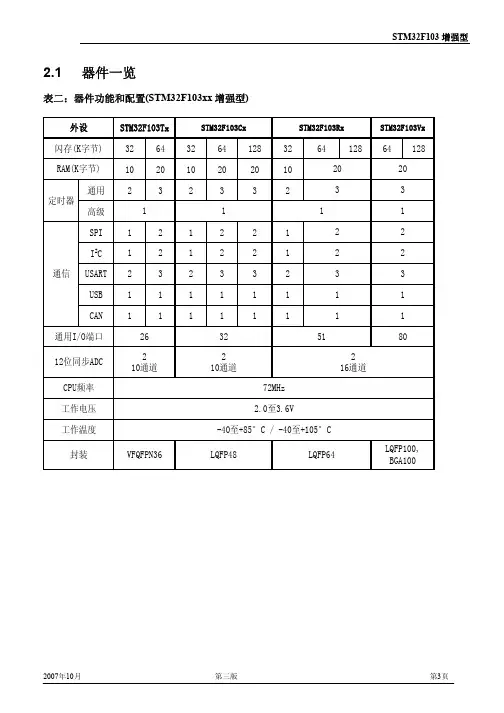

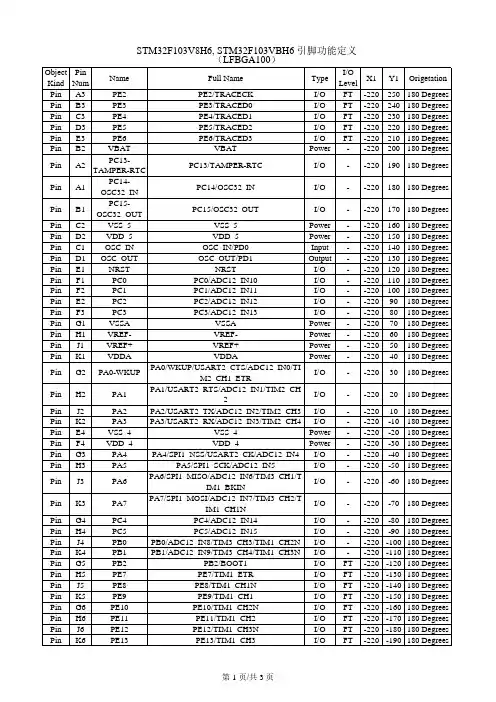

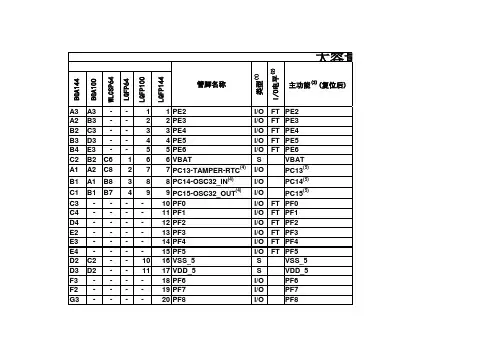

STM32F103引脚功能定义2.1 器件一览表二:器件功能和配置(STM32F103xx增强型)图一.STM32F103xx增强型模块框图工作温度=-40至+105°C (结温达125°C) AF: I/O口上的其他功能3管脚定义图二.STM32F103xx增强型VFQFPN36管脚图四.STM32F103xx增强型LQFP64管脚表三. 管脚定义表三.管脚定义(续)注:1. I :输入, O:输出, S:电源, HiZ:高阻2. FT:兼容5V3. 其中部分功能仅在部分型号芯片中支持,具体信息请参考表2。

4. PC13,PC14和PC15引脚通过电源开关进行供电,因此这三个引脚作为输出引脚时有以下限制:9作为输出脚时只能工作在2MHz模式下9最大驱动负载为30pF9同一时间,三个引脚中只有一个引脚能作为输出引脚。

5. 仅在内嵌大等于64K Flash的型号中支持此类功能。

6. VFQFPN36封装的2号,3号引脚和LQFP48,LQFP64封装的5号,6号引脚在芯片复位后默认配置为OSC_IN和OSC_OUT功能脚。

软件可以重新设置这两个引脚为PD0和PD1功能脚。

但对于LQFP100封装,由于PD0和PD1为固有的功能脚,因此没有必要再由软件进行设置。

更多详细信息请参考STM32F10xxx参考手册的复用功能I/O章节和调试设置章节。

PD0和PD1作为输出引脚只能工作在50MHz模式下。

7. 此类复用功能能够由软件配置到其他引脚上,详细信息请参考STM32F10xxx参考手册的复用功能I/O章节和调试设置章节。

4存储器映像图七存储器图5电气特性请参考英文版数据手册6封装参数请参考英文版数据手册7订货代码表四. 订货代码型号闪存存储器K字节SRAM存储器K字节封装STM32F103C6T6 32 10STM32F103C8T6 64 20STM32F103CBT6 128 20LQFP48STM32F103R6T6 32 10STM32F103R8T6 64 20STM32F103RBT6 128 20LQFP64STM32F103V8T6 64 20STM32F103VBT6 128 20LQFP100STM32F103V8H6 64 20STM32F103VBH6 128 20LFBGA100STM32F103T6U6 32 6STM32F103T8U6 64 10VFQFPN367.1 后续的产品系列后续的STM32F103xx增强型系列产品将会有更广泛的型号选择,芯片将会有更大的封装尺寸并内嵌多达512KB的Flash和48KB的SRAM。

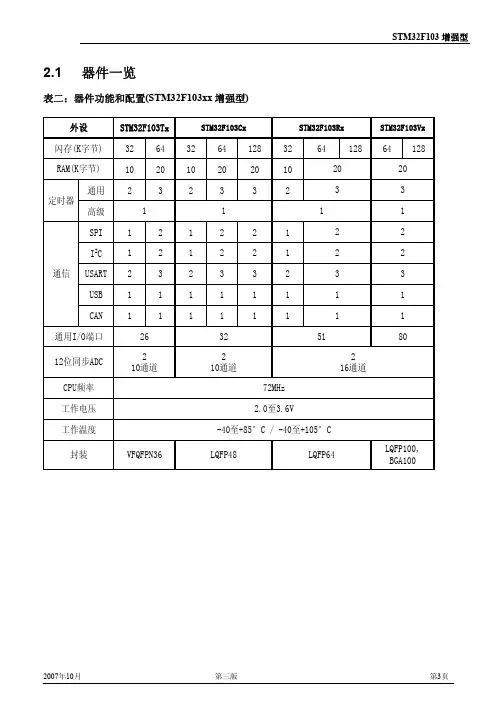

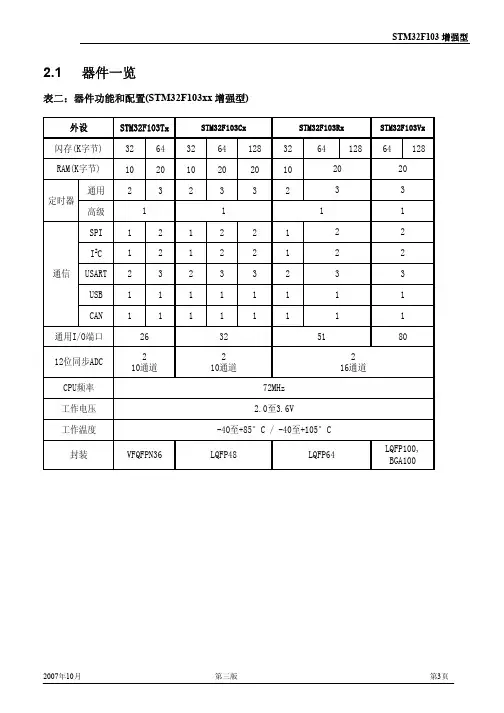

2.1 器件一览表二:器件功能和配置(STM32F103xx增强型)图一.STM32F103xx增强型模块框图工作温度=-40至+105°C (结温达125°C) AF: I/O口上的其他功能3管脚定义图二.STM32F103xx增强型VFQFPN36管脚图四.STM32F103xx增强型LQFP64管脚表三. 管脚定义表三.管脚定义(续)注:1. I :输入, O:输出, S:电源, HiZ:高阻2. FT:兼容5V3. 其中部分功能仅在部分型号芯片中支持,具体信息请参考表2。

4. PC13,PC14和PC15引脚通过电源开关进行供电,因此这三个引脚作为输出引脚时有以下限制:9作为输出脚时只能工作在2MHz模式下9最大驱动负载为30pF9同一时间,三个引脚中只有一个引脚能作为输出引脚。

5. 仅在内嵌大等于64K Flash的型号中支持此类功能。

6. VFQFPN36封装的2号,3号引脚和LQFP48,LQFP64封装的5号,6号引脚在芯片复位后默认配置为OSC_IN和OSC_OUT功能脚。

软件可以重新设置这两个引脚为PD0和PD1功能脚。

但对于LQFP100封装,由于PD0和PD1为固有的功能脚,因此没有必要再由软件进行设置。

更多详细信息请参考STM32F10xxx参考手册的复用功能I/O章节和调试设置章节。

PD0和PD1作为输出引脚只能工作在50MHz模式下。

7. 此类复用功能能够由软件配置到其他引脚上,详细信息请参考STM32F10xxx参考手册的复用功能I/O章节和调试设置章节。

4存储器映像图七存储器图5电气特性请参考英文版数据手册6封装参数请参考英文版数据手册7订货代码表四. 订货代码型号闪存存储器K字节SRAM存储器K字节封装STM32F103C6T6 32 10STM32F103C8T6 64 20STM32F103CBT6 128 20LQFP48STM32F103R6T6 32 10STM32F103R8T6 64 20STM32F103RBT6 128 20LQFP64STM32F103V8T6 64 20STM32F103VBT6 128 20LQFP100STM32F103V8H6 64 20STM32F103VBH6 128 20LFBGA100STM32F103T6U6 32 6STM32F103T8U6 64 10VFQFPN367.1 后续的产品系列后续的STM32F103xx增强型系列产品将会有更广泛的型号选择,芯片将会有更大的封装尺寸并内嵌多达512KB的Flash和48KB的SRAM。

STM32F103R4T6, STM32F103R6T6 引脚功能定义Pin 45PA12PA12/USART1_RTS/CAN_TX/TIM1_ETR/USBDPI/O FT 220-400 Degrees Pin 46PA13JTMS/SWDIO/PA13I/O FT 220-300 Degrees Pin 47VSS_2VSS_2Power -220-200 Degrees Pin 48VDD_2VDD_2Power -220-100 Degrees Pin 49PA14JTCK/SWCLK/PA14I/O FT 220100 Degrees Pin 50PA15JTDI/TIM2_CH1_ETR/PA15/SPI1_NSSI/O FT 220200 Degrees Pin 51PC10PC10I/O FT 220300 Degrees Pin 52PC11PC11I/O FT 220400 Degrees Pin 53PC12PC12I/O FT 220500 Degrees Pin 54PD2PD2/TIM3_ETRI/O FT 220600 Degrees Pin 55PB3JTDO/TIM2_CH2/PB3/TRACESWO I/O FT 220700 Degrees Pin 56PB4NJTRST/TIM3_CH1/PB4/SPI1_MISO I/O FT 220800 Degrees Pin 57PB5PB5/I2C1_SMBA/TIM3_CH2/SPI1_MOSII/O -220900 Degrees Pin 58PB6PB6/I2C1_SCL/USART1_TX I/O FT 2201000 Degrees Pin 59PB7PB7/I2C1_SDA/USART1_RXI/O FT 2201100 Degrees Pin 60BOOT0BOOT0Input -2201200 Degrees Pin 61PB8PB8/I2C1_SCL/CAN_RX I/O FT 2201300 Degrees Pin 62PB9PB9/I2C1_SDA /CAN_TXI/O FT 2201400 Degrees Pin 63VSS_3VSS_3Power -2201500 Degrees Pin64VDD_3VDD_3Power-2201600 Degrees(1)<Name> 表示引脚默认功能定义名称,<Full Name> 表示引脚全功能定义名称,包括引脚默认复用功能定义和重映射复用功能定义;(2)<I/O Level> 栏中:FT = 可以耐受 5V 电压;5V 电压波纹比较大时,请慎用,具体参数参考数据手册;(3)引脚功能定义参考 2015年6月 STM32F103x4/x6英文数据手册第7版(DocID15060 Rev 7);(4)此引脚功能定义表格旨在用于Altium Designer 原理图库制作的多管脚元件快速画法 Smart Grid Insert ,方法在我的文库中。

2.1 器件一览表二:器件功能和配置(STM32F103xx增强型)图一.STM32F103xx增强型模块框图工作温度=-40至+105°C (结温达125°C) AF: I/O口上的其他功能3管脚定义图二.STM32F103xx增强型VFQFPN36管脚图四.STM32F103xx增强型LQFP64管脚表三. 管脚定义表三.管脚定义(续)注:1. I :输入, O:输出, S:电源, HiZ:高阻2. FT:兼容5V3. 其中部分功能仅在部分型号芯片中支持,具体信息请参考表2。

4. PC13,PC14和PC15引脚通过电源开关进行供电,因此这三个引脚作为输出引脚时有以下限制:9作为输出脚时只能工作在2MHz模式下9最大驱动负载为30pF9同一时间,三个引脚中只有一个引脚能作为输出引脚。

5. 仅在内嵌大等于64K Flash的型号中支持此类功能。

6. VFQFPN36封装的2号,3号引脚和LQFP48,LQFP64封装的5号,6号引脚在芯片复位后默认配置为OSC_IN和OSC_OUT功能脚。

软件可以重新设置这两个引脚为PD0和PD1功能脚。

但对于LQFP100封装,由于PD0和PD1为固有的功能脚,因此没有必要再由软件进行设置。

更多详细信息请参考STM32F10xxx参考手册的复用功能I/O章节和调试设置章节。

PD0和PD1作为输出引脚只能工作在50MHz模式下。

7. 此类复用功能能够由软件配置到其他引脚上,详细信息请参考STM32F10xxx参考手册的复用功能I/O章节和调试设置章节。

4存储器映像图七存储器图5电气特性请参考英文版数据手册6封装参数请参考英文版数据手册7订货代码表四. 订货代码型号闪存存储器K字节SRAM存储器K字节封装STM32F103C6T6 32 10STM32F103C8T6 64 20STM32F103CBT6 128 20LQFP48STM32F103R6T6 32 10STM32F103R8T6 64 20STM32F103RBT6 128 20LQFP64STM32F103V8T6 64 20STM32F103VBT6 128 20LQFP100STM32F103V8H6 64 20STM32F103VBH6 128 20LFBGA100STM32F103T6U6 32 6STM32F103T8U6 64 10VFQFPN367.1 后续的产品系列后续的STM32F103xx增强型系列产品将会有更广泛的型号选择,芯片将会有更大的封装尺寸并内嵌多达512KB的Flash和48KB的SRAM。

STM32F103RCT6引脚功能及使用脚号引脚名称主功能默认复用重定义备注1VBAT VBAT----说明1 2PC13-TAMPER-RTC PC13TAMPER-RTC--说明3 3PC14-OSC32_IN PC14OSC32_IN--说明3 4PC15-OSC32_OUT PC15OSC32_OUT--说明3 5OSC_IN OSC_IN--CAN_RX晶振6OSC_OUT OSC_OUT--CAN_TX晶振7NRST NRST----复位8PC0PC0ADC123_IN10--ADC 9PC1PC1ADC123_IN11--ADC 10PC2PC2ADC123_IN12--ADC 11PC3PC3ADC123_IN13--ADC 12VSSA VSSA----模拟地13VDDA VDDA----模拟电14PA0-WKUP PA0WKUP--说明4 USART2_CTS说明5 ADC123_IN0TIM2_CH1_ETR说明6 TIM5_CH1TIM8_ETR15PA1PA1USART2_RTS--ADC123_IN1TIM2_CH2TIM5_CH216PA2PA2USART2_TX--ADC123_IN2TIM2_CH3TIM5_CH317PA3PA3USART2_RX--ADC123_IN3TIM2_CH4TIM5_CH418VSS_4VSS_4----数字地19VDD_4VDD_4----数字电20PA4PA4USART2_CK--ADC12_IN4SPI1_NSSDAC_OUT121PA5PA5ADC12_IN5--SPI1_SCKDAC_OUT222PA6PA6ADC12_IN6TIM1_BKIN TIM3_CH1TIM8_BKINSPI1_MISO23PA7PA7ADC12_IN7TIM1_CH1N TIM3_CH2TIM8_CH1NSPI1_MOSI24PC4PC4ADC12_IN14--25PC5PC5ADC12_IN15--26PB0PB0ADC12_IN8TIM1_CH2N TIM3_CH3TIM8_CH2N27PB1PB1ADC12_IN9TIM1_CH3N TIM3_CH4TIM8_CH3N28PB2PB2----BOOT129PB10PB10USART3_TXTIM2_CH3 I2C2_SCL30PB11PB11USART3_RXTIM2_CH4 I2C2_SDA31VSS_1VSS_1----数字地32VDD_1VDD_1----数字电33PB12PB12USART3_CK--TIM1_BKINSPI2_NSS说明7 I2C2_SMBAI2S2_WS34PB13PB13USART3_CTS--TIM1_CH1NSPI2_SCKI2S2_CK35PB14PB14USART3_RTS--TIM1_CH2NSPI2_MISO36PB15PB15TIM1_CH3N--SPI2_MOSII2S2_SD37PC6PC6TIM8_CH1TIM3_CH1I2S2_MCKSDIO_D6说明838PC7PC7TIM8_CH2NTIM3_CH2 I2S3_MCKSDIO_D739PC8PC8TIM8_CH3NTIM3_CH3 SDIO_D040PC9PC9TIM8_CH4TIM3_CH4 SDIO_D141PA8PA8USART1_CK--TIM1_CH1MCO42PA9PA9USART1_TX--TIM1_CH243PA10PA10USART1_RX--TIM1_CH344PA11PA11USART1_CTS--TIM1_CH4USBDMCAN_RX45PA12PA12USART1_RTS--TIM1_ETRUSBDPCAN_TX46PA13JTMS--PA13 SWDIO47VSS_2VSS_2----数字地48VDD_2VDD_2----数字电49PA14JTCK--PA14SWCLK50PA15JTDI SPI3_NSS PA15I2S3_WSTIM2_CH1_ETRSPI1_NSS51PC10PC10UART4_TX USART3_TXSDIO_D252PC11PC11UART4_RX USART3_RXSDIO_D353PC12PC12UART5_TX USART3_CKSDIO_CK54PD2PD2UART5_RX--TIM3_ETRSDIO_CMD55PB3JTDO SPI3_SCKPB3TIM2_CH2 I2S3_CKSPI1_SCKTRACESWO56PB4NJTRST SPI3_MISOPB4 TIM3_CH1 SPI1_MISO57PB5PB5SPI3_MOSI TIM3_CH2 I2C1_SMBASPI1_MOSI I2S3_SD58PB6PB6TIM4_CH1USART1_TXI2C1_SCL59PB7PB7TIM4_CH2USART1_RXI2C1_SDA60BOOT0BOOT0----61PB8PB8TIM4_CH3I2C1_SCL SDIO_D4CAN_RX62PB9PB9TIM4_CH4I2C1_SDA SDIO_D5CAN_TX63VSS_3VSS_3----数字地64VDD_3VDD_3--数字电说明:1)VBAT:VBAT给RTC和备份区域供电,目的是在VDD断电时保证相关区域的数据内容有效,一般连接到外部电池。

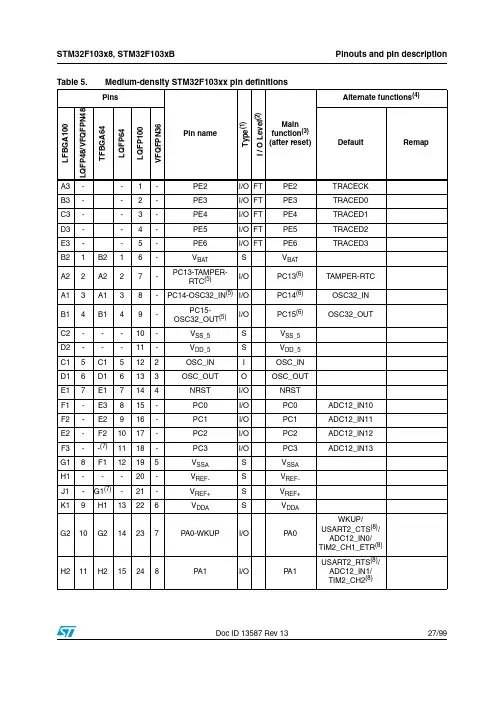

Doc ID 13587 Rev 1327/99Table 5.Medium-density STM32F103xx pin definitionsPinsPin nameT y p e (1)I / O L e v e l (2)Main function (3) (after reset)Alternate functions (4)L F B G A 100L Q F P 48/V F Q F P N 48T F B G A 64L Q F P 64L Q F P 100V F Q F P N 36Default RemapA3--1-PE2I/O FT PE2TRACECK B3--2-PE3I/O FT PE3TRACED0C3--3-PE4I/O FT PE4TRACED1D3--4-PE5I/O FT PE5TRACED2E3--5-PE6I/O FT PE6TRACED3B21B216-V BATS V BAT A22A227-PC13-TAMPER-RTC (5)I/OPC13(6)TAMPER-RTC A13A138-PC14-OSC32_IN (5)I/O PC14(6)OSC32_IN B14B149-PC15-OSC32_OUT (5)I/O PC15(6)OSC32_OUTC2---10-V SS_5S V SS_5D2---11-V DD_5S V DD_5C15C15122OSC_IN I OSC_IN D16D16133OSC_OUT O OSC_OUT E17E17144NRST I/O NRST F1-E3815-PC0I/O PC0ADC12_IN10 F2-E2916-PC1I/O PC1ADC12_IN11 E2-F21017-PC2I/O PC2ADC12_IN12 F3--(7)1118-PC3I/O PC3ADC12_IN13G18F112195V SSA S V SSA H1---20-V REF-S V REF-J1-G1(7)-21-V REF+S V REF+K19H113226V DDA SV DDA G210G214237P A0-WKUPI/OP A0WKUP/USART2_CTS (8)/ADC12_IN0/TIM2_CH1_ETR (8)H211H215248P A1I/O P A1USART2_RTS (8)/ADC12_IN1/ TIM2_CH2(8)28/99 Doc ID 13587 Rev 13J212F316259P A2I/O P A2USART2_TX (8)/ADC12_IN2/ TIM2_CH3(8)K213G3172610P A3I/O P A3USART2_RX (8)/ADC12_IN3/TIM2_CH4(8)E4-C21827-V SS_4S V SS_4F4-D21928-V DD_4S V DD_4G314H3202911P A4I/OP A4SPI1_NSS (8)/ USART2_CK (8)/ ADC12_IN4 H315F4213012P A5I/O P A5SPI1_SCK (8)/ ADC12_IN5 J316G4223113P A6I/O P A6SPI1_MISO (8)/ADC12_IN6/TIM3_CH1(8)TIM1_BKINK317H4233214P A7I/O P A7SPI1_MOSI (8)/ADC12_IN7/TIM3_CH2(8)TIM1_CH1NG4-H52433PC4I/O PC4ADC12_IN14 H4-H62534PC5I/O PC5ADC12_IN15 J418F5263515PB0I/O PB0ADC12_IN8/TIM3_CH3(8)TIM1_CH2N K419G5273616PB1I/OPB1ADC12_IN9/TIM3_CH4(8)TIM1_CH3N G520G6283717PB2I/O FT PB2/BOOT1H5---38-PE7I/O FT PE7TIM1_ETR J5---39-PE8I/O FT PE8TIM1_CH1N K5---40-PE9I/O FT PE9TIM1_CH1G6---41-PE10I/O FT PE10TIM1_CH2N H6---42-PE11I/O FT PE11TIM1_CH2J6---43-PE12I/O FT PE12TIM1_CH3N K6---44-PE13I/O FT PE13TIM1_CH3G7---45-PE14I/O FTPE14TIM1_CH4Table 5.Medium-density STM32F103xx pin definitions (continued)PinsPin nameT y p e (1)I / O L e v e l (2)Main function (3) (after reset)Alternate functions (4)L F B G A 100L Q F P 48/V F Q F P N 48T F B G A 64L Q F P 64L Q F P 100V F Q F P N 36Default RemapDoc ID 13587 Rev 1329/99H7---46-PE15I/O FT PE15TIM1_BKIN J721G72947-PB10I/O FT PB10I2C2_SCL/USART3_TX (8)TIM2_CH3K722H73048-PB11I/O FT PB11I2C2_SDA/ USART3_RX (8)TIM2_CH4E723D6314918V SS_1S V SS_1F724E6325019V DD_1SV DD_1K825H83351-PB12I/O FTPB12SPI2_NSS/I2C2_SMBAl/USART3_CK (8)/TIM1_BKIN (8)J826G83452-PB13I/O FT PB13SPI2_SCK/USART3_CTS (8)/TIM1_CH1N (8)H827F83553-PB14I/O FT PB14SPI2_MISO/ USART3_RTS (8) TIM1_CH2N (8)G828F73654-PB15I/O FT PB15SPI2_MOSI/TIM1_CH3N (8)K9---55-PD8I/O FT PD8USART3_TX J9---56-PD9I/O FT PD9USART3_RX H9---57-PD10I/O FT PD10USART3_CK G9---58-PD11I/O FT PD11USART3_CTS K10---59-PD12I/O FT PD12TIM4_CH1 / USART3_RTS J10---60-PD13I/O FT PD13TIM4_CH2H10---61-PD14I/O FT PD14TIM4_CH3G10---62-PD15I/O FT PD15TIM4_CH4F10-F63763-PC6I/O FT PC6TIM3_CH1E10E73864-PC7I/O FT PC7TIM3_CH2F9E83965-PC8I/O FT PC8TIM3_CH3E9-D84066-PC9I/O FT PC9TIM3_CH4D929D7416720P A8I/O FTP A8USART1_CK/TIM1_CH1(8)/MCOTable 5.Medium-density STM32F103xx pin definitions (continued)PinsPin nameT y p e (1)I / O L e v e l (2)Main function (3) (after reset)Alternate functions (4)L F B G A 100L Q F P 48/V F Q F P N 48T F B G A 64L Q F P 64L Q F P 100V F Q F P N 36Default Remap30/99 Doc ID 13587 Rev 13C930C7426821P A9I/O FT P A9USART1_TX (8)/ TIM1_CH2(8)D1031C6436922P A10I/O FTP A10USART1_RX (8)/ TIM1_CH3(8)C1032C8447023P A11I/O FT P A11USART1_CTS/ CANRX (8)/ USBDM TIM1_CH4(8)B1033B8457124P A12I/O FT P A12USART1_RTS/ CANTX (8) //USBDP TIM1_ETR (8)A1034A8467225P A13I/O FT JTMS/SWDIO P A13F8---73-Not connectedE635D5477426V SS_2S V SS_2F636E5487527V DD_2SV DD_2A937A7497628P A14I/O FT JTCK/SWCLK P A14A838A6507729P A15I/O FT JTDI TIM2_CH1_ETR/ P A15 /SPI1_NSS B9-B75178PC10I/O FT PC10USART3_TX B8-B65279PC11I/O FT PC11USART3_RX C8-C55380PC12I/O FT PC12USART3_CK D85C15812PD0I/O FTOSC_IN (9)CANRX E86D16823PD1I/O FT OSC_OUT (9)CANTXB7B55483-PD2I/O FT PD2TIM3_ETRC7---84-PD3I/O FT PD3USART2_CTS D7---85-PD4I/O FT PD4USART2_RTS B6---86-PD5I/O FT PD5USART2_TX C6---87-PD6I/O FT PD6USART2_RX D6---88-PD7I/O FT PD7USART2_CK A739A5558930PB3I/O FTJTDOTIM2_CH2 / PB3 TRACESWO SPI1_SCK A640A4569031PB4I/O FT JNTRSTTIM3_CH1/ PB4/ SPI1_MISOTable 5.Medium-density STM32F103xx pin definitions (continued)PinsPin nameT y p e (1)I / O L e v e l (2)Main function (3) (after reset)Alternate functions (4)L F B G A 100L Q F P 48/V F Q F P N 48T F B G A 64L Q F P 64L Q F P 100V F Q F P N 36Default RemapDoc ID 13587 Rev 1331/99C541C4579132PB5I/O PB5I2C1_SMBAl TIM3_CH2 / SPI1_MOSI B542D3589233PB6I/O FT PB6I2C1_SCL (8)/TIM4_CH1(8)USART1_TX A543C3599334PB7I/O FT PB7I2C1_SDA (8)/TIM4_CH2(8)USART1_RXD544B4609435BOOT0I BOOT0B445B36195-PB8I/O FT PB8TIM4_CH3(8)I2C1_SCL / CANRX A446A36296-PB9I/O FT PB9TIM4_CH4(8)I2C1_SDA/CANTXD4---97-PE0I/O FT PE0TIM4_ETRC4---98-PE1I/O FT PE1E547D4639936V SS_3S V SS_3F548E4641001V DD_3SV DD_31.I = input, O = output, S = supply.2.FT = 5 V tolerant.3.Function availability depends on the chosen device. For devices having reduced peripheral counts, it is always the lowernumber of peripheral that is included. For example, if a device has only one SPI and two USARTs, they will be called SPI1 and USART1 & USART2, respectively. Refer to Table 2 on page 10.4.If several peripherals share the same I/O pin, to avoid conflict between these alternate functions only one peripheral shouldbe enabled at a time through the peripheral clock enable bit (in the corresponding RCC peripheral clock enable register).5.PC13, PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current(3mA), the use of GPIOs PC13 to PC15 in output mode is limited: the speed should not exceed 2 MHz with a maximum load of 30 pF and these IOs must not be used as a current source (e.g. to drive an LED).6.Main function after the first backup domain power-up. Later on, it depends on the contents of the Backup registers evenafter reset (because these registers are not reset by the main reset). For details on how to manage these IOs, refer to the Battery backup domain and BKP register description sections in the STM32F10xxx reference manual, available from the STMicroelectronics website: .7.Unlike in the LQFP64 package, there is no PC3 in the TFBGA64 package. The V REF+ functionality is provided instead.8.This alternate function can be remapped by software to some other port pins (if available on the used package). For moredetails, refer to the Alternate function I/O and debug configuration section in the STM32F10xxx reference manual, available from the STMicroelectronics website: .9.The pins number 2 and 3 in the VFQFPN36 package, 5 and 6 in the LQFP48 and LQFP64 packages, and C1 and C2 in theTFBGA64 package are configured as OSC_IN/OSC_OUT after reset, however the functionality of PD0 and PD1 can be remapped by software on these pins. For the LQFP100 package, PD0 and PD1 are available by default, so there is no need for remapping. For more details, refer to the Alternate function I/O and debug configuration section in the STM32F10xxx reference manual.The use of PD0 and PD1 in output mode is limited as they can only be used at 50 MHz in output mode.Table 5.Medium-density STM32F103xx pin definitions (continued)PinsPin nameT y p e (1)I / O L e v e l (2)Main function (3) (after reset)Alternate functions (4)L F B G A 100L Q F P 48/V F Q F P N 48T F B G A 64L Q F P 64L Q F P 100V F Q F P N 36Default Remap。

(3mA)。

因此这三个引脚作为输出引脚时有以

5. 这些引脚在备份区域第一次上电时处于主功能状态下,之后即使复位,这些引脚的状态由备份区域寄存器控制(这些寄存器不会被主复位册的电池备份区域和BKP寄存器的相关章节。

6. 与LQFP64的封装不同,在WLCSP封装上没有PC3,但提供了VREF+引脚。

7. 此类复用功能能够由软件配置到其他引脚上(如果相应的封装型号有此引脚),详细信息请参考STM32F10xxx参考手册的复用功能I/O章节

8.LQFP64封装的引脚5和引脚6在芯片复位后默认配置为OSC_IN和OSC_OUT功能脚。

软件可以重新设置这两个引脚为PD0和PD1功能。

的功能引脚,因此没有必要再由软件进行重映像设置。

更多详细信息请参考STM32F10xxx参考手册的复用功能I/O章节和调试设置章节。

9.LPFP64封装的产品,没有FSMC功能。

STM32F103电路引脚功能定义及部分参考电路设计STM32F103各引脚(LQFP64)功能定义NOTE:1.供电⽅案●VDD = 2.0⾄3.6 V:⽤于I / O的外部电源和内部稳压器,通过VDD引脚从外部提供。

●VSSA,VDDA = 2.0⾄3.6 V:⽤于ADC,DAC,复位模块,RC和PLL(当ADC或DAC模块使⽤,施加到VDDA的最⼩电压为2.4 V), VDDA和VSSA必须分别连接到VDD和VSS。

●VBAT = 1.8⾄3.6 V:当不存在VDD时,⽤于RTC,外部时钟32 kHz振荡器和备⽤寄存器(通过电源开关)。

从上图可知:每个VDD各接⼀个100nF陶瓷电容,其中VDD3需要再接⼀个4.7uF的钽电容;VDDA:接10nF陶瓷电容+1uF钽电容;VREF+:可接VDDA,也可接外部参考源,此时也需要接10nF陶瓷电容+1uF钽电容;2.通信接⼝1.I2C总线STM32F103提供两个I2C总线接⼝,作为从机时,⽀持7/10位寻址模式和7位双寻址模式,I2C 总线配置可由DMA控制器提供服务。

2.SPI接⼝在全双⼯和单⼯通信模式下,从机和主机模式下,提供三个SPI接⼝能够以18Mbit/s速率通信,所有SPI接⼝配置均可由DMA控制器提供服务。

3.I2S接⼝I2S(Inter-IC Sound)是飞利浦公司针对数字⾳频设备(如CD播放器、数码⾳效处理器、数字电视⾳响系统)之间的⾳频数据传输⽽制定的⼀种总线标准。

它采⽤了独⽴的导线传输时钟与数据信号的设计,通过将数据和时钟信号分离,避免了因时差诱发的失真,为⽤户节省了购买抵抗⾳频抖动的专业设备的费⽤。

标准的I2S总线电缆是由3根串⾏导线组成的:1根是时分多路复⽤(简称TDM)数据线;1根是字选择线;1根是时钟线。

STM32F103提供两个I2S总线接⼝(与SPI2和SPI3复⽤),⾳频采样频率⽀持8KHz⾄48kHz。

芯片编号和引脚说明

STM32F103xx是一个完整的系列,其成员之间是完全地脚对脚兼容,软件和功能上也兼容,STM32F10x系列单片机芯片编号说明如图B.7所示。

图B.7 STM32F10x系列单片机芯片编号说明图

STM32F103x4和STM32F103x6被归为小容量产品,STM32F103x8和STM32F103xB 被归为中等容量产品,STM32F103xC、STM32F103xD和STM32F103xE被归为大容量产品。

全系列脚对脚、外设及软件具有高度的兼容性。

这种全兼容性带来的好处是:电路设计不用作任何修改,可以根据应用和成本的需要,使用不同存储容量系列的微控制器,为用户在产品开发中提供了更大的自由度。

同时,STM32F103xx增强型产品与现有的STM32F101xx 基本型和STM32F102xx USB基本型产品也全兼容。

STM32F10x系列单片机外设配置如表B.4所示。

在第一章列举了中小容量的STM32F103xx系列单片机的外设资源,表B.5是大容量STM32F10x系列单片机外设资源。

中小容量的STM32F10x单片机引脚功能如表B.6

所示。

表B.4 STM32F10x系列单片机外设配置表

表B.5 STM32F103xx增强型微控制器(大容量)各系列的外设资源

表B.6 中小容量的STM32F10x系列单片机引脚功能表

表B.6 中小容量的STM32F10x系列单片机引脚功能表(续)

表B.6 中小容量的STM32F10x系列单片机引脚功能表(续)

注:带有标注1的表示:这些功能只在Flash容量大于32K字节产品中。

2.1 器件一览

表二:器件功能和配置(STM32F103xx增强型)

图一.STM32F103xx增强型模块框图

工作温度=-40至+105°C (结温达125°C) AF: I/O口上的其他功能

3管脚定义

图二.STM32F103xx增强型VFQFPN36管脚

图四.STM32F103xx增强型LQFP64管脚

表三. 管脚定义

表三.管脚定义(续)

注:

1. I :输入, O:输出, S:电源, HiZ:高阻

2. FT:兼容5V

3. 其中部分功能仅在部分型号芯片中支持,具体信息请参考表2。

4. PC13,PC14和PC15引脚通过电源开关进行供电,因此这三个引脚作为输出引脚时有以下限制:

9作为输出脚时只能工作在2MHz模式下

9最大驱动负载为30pF

9同一时间,三个引脚中只有一个引脚能作为输出引脚。

5. 仅在内嵌大等于64K Flash的型号中支持此类功能。

6. VFQFPN36封装的2号,3号引脚和LQFP48,LQFP64封装的5号,6号引脚在芯片复位后默认配置为

OSC_IN和OSC_OUT功能脚。

软件可以重新设置这两个引脚为PD0和PD1功能脚。

但对于LQFP100封装,由于PD0和PD1为固有的功能脚,因此没有必要再由软件进行设置。

更多详细信息请参考STM32F10xxx参考手册的复用功能I/O章节和调试设置章节。

PD0和PD1作为输出引脚只能工作在50MHz模式下。

7. 此类复用功能能够由软件配置到其他引脚上,详细信息请参考STM32F10xxx参考手册的复用功能I/O

章节和调试设置章节。

4存储器映像

图七存储器图

5电气特性

请参考英文版数据手册6封装参数

请参考英文版数据手册7订货代码

表四. 订货代码

型号闪存存储器

K字节SRAM存储器

K字节

封装

STM32F103C6T6 32 10

STM32F103C8T6 64 20

STM32F103CBT6 128 20

LQFP48

STM32F103R6T6 32 10

STM32F103R8T6 64 20

STM32F103RBT6 128 20

LQFP64

STM32F103V8T6 64 20

STM32F103VBT6 128 20

LQFP100

STM32F103V8H6 64 20

STM32F103VBH6 128 20

LFBGA100

STM32F103T6U6 32 6

STM32F103T8U6 64 10

VFQFPN36

7.1 后续的产品系列

后续的STM32F103xx增强型系列产品将会有更广泛的型号选择,芯片将会有更大的封装尺寸并内嵌多达512KB的Flash和48KB的SRAM。

同时,后续产品会提供EMI,SDIO,I2S,DAC,更多的定时器和USARTS接口功能。

8版本历史

请参考英文版数据手册。