一种高速数据采集记录装置的设计

- 格式:doc

- 大小:27.00 KB

- 文档页数:4

基于FPGA的高速数据采集系统设计随着科学技术的不断进步,数据采集系统在许多领域都发挥着重要作用。

为了满足高速数据采集的需求,基于现场可编程门阵列(FPGA)的高速数据采集系统设计应运而生。

本文将介绍这一系统的设计原理和关键技术。

首先,我们需要了解FPGA的基本原理。

FPGA是一种可编程的硬件设备,可以根据需要重新配置其内部逻辑电路。

这使得FPGA在数据采集系统中具有极大的灵活性和可扩展性。

与传统的数据采集系统相比,基于FPGA的系统可以实现更高的采样率和更低的延迟。

基于FPGA的高速数据采集系统设计主要包括以下几个关键技术。

首先是模数转换(ADC)技术。

ADC是将连续的模拟信号转换为数字信号的关键环节。

在高速数据采集系统中,需要使用高速、高精度的ADC来保证数据的准确性和完整性。

其次是FPGA内部逻辑电路的设计。

为了实现高速数据采集,需要设计高效的数据处理逻辑电路。

这些电路可以实现数据的实时处理、存储和传输等功能。

同时,还需要考虑电路的时序约束和资源分配等问题,以确保系统的稳定性和可靠性。

另外,时钟同步技术也是高速数据采集系统设计的重要内容。

在高速数据采集过程中,各个模块需要保持同步,以确保数据的准确性。

因此,需要设计合理的时钟同步方案,保证各个模块在同一个时钟周期内完成数据的采样和处理。

最后,还需要考虑系统的接口和通信问题。

基于FPGA的高速数据采集系统通常需要与其他设备进行数据交互,如计算机、存储设备等。

因此,需要设计合适的接口和通信协议,实现数据的传输和存储。

综上所述,基于FPGA的高速数据采集系统设计涉及多个关键技术,包括ADC技术、FPGA内部逻辑电路设计、时钟同步技术以及接口和通信问题。

通过合理的设计和优化,可以实现高速、高精度的数据采集,满足现代科学研究和工程应用的需求。

这将为各个领域的数据采集工作带来巨大的便利和发展空间。

一种高速CCD数据采集系统的设计作者:刘爽王浩龙再川郭强来源:《现代电子技术》2008年第14期摘要:CCD相机的数据采集是设计实时高分辨率CCD摄像机的瓶颈,1394协议具有高的传输速率,同时在其基础上发展而来的1394b协议,最高的传输速率可以达到32 Gb/s。

设计基于1394传输协议的数据采集系统,该系统具有高的传输速率,可以有效地解决该瓶颈,同时为设计1394b传输系统奠定了基础。

介绍该采集系统的框架图、MCU软件设计流程以及WDM驱动开发等。

经测试,系统工作稳定。

关键词:等时传输;异步传输;TSB12LV32;WDM驱动模型;(1School of Optoelectronic Information,University of Electronic Science and Technology ofAbstract:The data acquisition is the bottleneck in the design of the real[CD2]time and high speed CCD cameraHigh transmission speed is defined in 1394 protocol,and 32 Gb/s is defined in 1394b protocol which comes from 1394 protocolThe system in acquisition based on 1394 is designed in this paper and the system which lays a foundation for the system in acquisition based on 1394b has high speedThe Framework of this system,the flow chart of MCU and development of WDM is givenKeywords:isochronous transaction;asynchronous transaction;TSB12LV32;WDM drive1 引言随着数字技术的进步与发展,对于数据传输的高速率性和时实性提出了很高的要求,IEEE1394协议的出现,很好地解决了该问题。

高精度数据采集系统的设计及性能分析现代工业生产过程中往往需要涉及大量的监测和控制,而高精度数据采集系统的设计和性能分析就是为了满足这种需求而诞生的。

本文将介绍高精度数据采集系统的设计和性能分析的相关技术及应用,同时分析这些技术的应用场景和性能优劣,希望能够对读者有所帮助。

一、高精度数据采集系统的组成高精度数据采集系统是由多个部件组成的复杂系统,其中主要包括传感器、信号调理器、数据采集卡、数据处理软件等。

下面详细介绍这些部件的作用及原理:1. 传感器传感器是高精度数据采集系统中最核心的组成部分之一。

它的作用是将测量对象的物理量转换为电信号输出,常见的传感器包括温度传感器、压力传感器、角度传感器、力传感器等。

不同类型的传感器在测量的物理量和范围上存在差异,同时也有不同的转换方式和输出形式。

2. 信号调理器信号调理器是传感器信号处理的核心,主要负责将传感器输出的信号进行放大、滤波、线性化等处理,使其适合于数据采集卡进行数字化转换。

信号调理器的设计将直接影响系统的稳定性和精度。

3. 数据采集卡数据采集卡是高精度数据采集系统中另一个重要的组成部分,它起到将模拟信号转换成数字信号的作用。

数据采集卡的数字化转换精度和采样率将直接影响采集系统的精度。

4. 数据处理软件数据处理软件是高精度数据采集系统中最后一道关键工序的组成部分。

它的作用是将数据从数据采集卡中读取,并将其经过校准、滤波、标定、控制等算法处理,最终输出给用户需要的数据。

数据处理软件应当具有友好的用户界面、高效的运算能力和稳定的运行性能。

二、高精度数据采集系统的应用场景高精度数据采集系统的应用场景十分广泛,主要包括以下几个领域:1. 工业控制众所周知,现代工厂生产过程需要各种各样的传感器和数据采集设备,以保证产品质量和生产效率。

高精度数据采集系统可以应用于无污染的检测、高速电机控制、发电温度观测、高分辨率精细控制等技术领域。

2. 航空雷达航空雷达数据采集系统需要在高速行动的飞机上进行复杂的数据采集和传输,并要求精度高、稳定性好、机动性强、重量轻等特点。

高速多通道数据采集传输系统的设计*赵忠凯,尹达,刘海朝【摘要】摘要:设计了一种基于FPGA与DSP的高速多通道实时数据采集传输系统。

该系统通过FPGA实现对时钟、ADC、DSP等芯片的功能配置,采集数据由FPGA预处理后通过EMIF接口传送至DSP,并完成后续的复杂信号处理。

该系统最高数据采集速率可达500 MSPS,FPGA与DSP之间可实现高速率的数据传输。

实际测试结果表明,该系统实现了多通道数据的实时同步采集、传输与处理,数据采集达到较高性能,能够满足当前复杂电磁环境下精确制导雷达数据处理分析的需求。

【期刊名称】火力与指挥控制【年(卷),期】2015(000)012【总页数】5【关键词】多通道,高速数据采集,EMIF,FPGA&DSP0 引言当前电磁信号环境越来越复杂,电磁信号密度已达到百万量级[1],这就要求雷达信号识别处理系统必须具备快速、准确识别威胁的能力,能够为之后作战提供及时可靠的信息。

随着一些新算法的出现,信号处理复杂度越来越高,动态范围也要求越来越大,信号的通道数也越来越多,因此,多通道信号的采集处理已成为当前雷达数字接收机的发展趋势。

传统的信号采集和传输方法已不能完全满足当前复杂电磁威胁环境下信号处理机对处理数据的要求[2],必须应用更精确更高速的采集系统,保证电子战环境中的主动权,所以对雷达信号高速多通道采集传输系统的研究具有重大且深远的意义。

FPGA具有强大的数据并行处理能力,能够满足高速ADC的数据处理要求,非常适合作为本系统的逻辑控制核心。

高性能多核DSP的高速运算能力使其适合选作复杂算法的主处理芯片[3]。

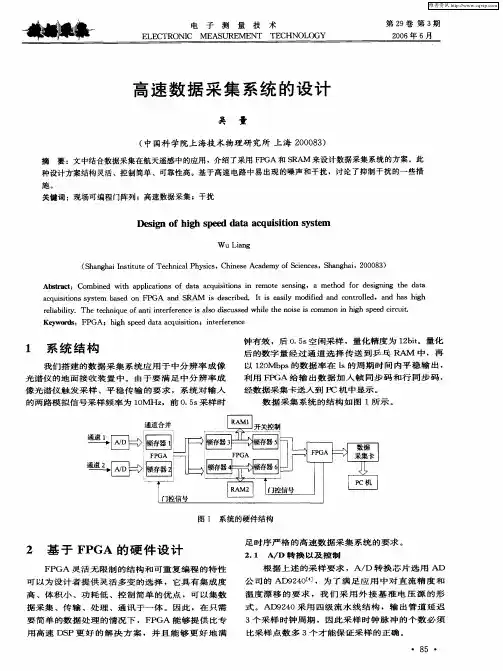

1 系统总体方案雷达信号高速多通道数据采集传输系统总体框图如图1所示。

设计中所选用的ADC芯片数据转换速率最高可达500 MSPS。

FPGA芯片选择Altera公司Stratix III系列的EP3SL200F1152C2,DSP芯片选择TI公司的TMS320C6678。

高速数据采集与实时处理系统的设计与实现随着科技不断发展,数据在我们生活中的地位越来越重要。

特别是在工业自动化领域中,高速数据采集和实时处理系统的需求越来越大。

本文将介绍高速数据采集与实时处理系统的设计与实现。

本文主要包括以下几个方面:1. 高速数据采集系统的设计与实现2. 实时数据处理系统的设计与实现3. 系统的测试和性能优化1. 高速数据采集系统的设计与实现高速数据采集是指突破常用采集速度,进行数据采集和传输的一种技术。

在工业自动化控制中,电子元器件的响应速度非常快,因此需要实时采集数据才能更好地对工控设备进行控制和实现数据分析。

以下是高速数据采集系统的设计和实现步骤:1.1 选型硬件和软件首先需要选定采集设备和软件。

在选定硬件时需考虑采集速度、采集量、输入接口以及多通道采集等因素。

对于实时控制系统,应选用高速、稳定且可靠的硬件设备。

软件方面,根据硬件的选择,选用适当的驱动程序。

1.2 电路设计由于需要保证采集器的稳定性和可靠性,因此电路设计十分重要。

在设计电路时,需要特别注意信号放大放大电路的设计和噪声干扰的屏蔽。

在信号传输过程中,信号放大电路应具有高增益,同时应能有效地屏蔽来自外部线路的噪声干扰。

1.3 布线设计由于布线和绝缘的设计将直接影响采集数据的稳定性和准确性,因此需要采用专业的设计技术和规范,确保系统数据的稳定。

1.4 系统调试系统调试是整个设计过程中最重要的环节之一。

在进行系统调试时,应逐一对硬件设备和软件进行测试和校准。

检查系统的分辨率是否满足要求,数据采集是否准确和稳定,软件编程是否准确等等。

只有经过严格的测试和校准,才能确保实时数据采集的准确性和稳定性。

2. 实时数据处理系统的设计与实现2.1 数据处理系统的选择在设计实时数据处理系统时,选择合适的数据处理系统非常重要。

根据实际需要,选择处理器和软件。

处理器的性能要足够强大,以处理高速实时数据。

软件也要适应处理器,为系统提供有效、快速和准确的数据处理。

一种高速数据采集记录装置的设计作者:侯泽雄沈小林姜旭刚来源:《电子世界》2013年第14期【摘要】文章介绍了一种基于Flash的高速数据采集记录装置的实现方案;文中采用了Flash高速存储技术与FPGA的二级缓冲技术,提高了存储速度,突破存储芯片的瓶颈,成功实现了数据存储速率与传输速率完美的匹配;同时通过设计合理的电路降低了存储模块的功耗,利用可靠的通信协议,有效保证了信号数据的可靠接收和存储。

【关键词】数据记录仪;Flash;高速存储1.系统方案设计本文设计的数据记录系统由以下几部分组成:两台完全相同的数据记录仪、一个地面综合测试台、上位机、配套软件以及配套电缆。

主要用于记录由雷达系统产生的视频回波、图像及遥测三路LVDS高速信号。

系统工作时,由雷达系统首先发来启动记录信号,使已处于采集状态的两台记录仪同时工作,二者互为备份。

地面测试台产生的模拟信号供记录仪存储,同时可以控制记录仪进入不同的工作状态,通过内置的USB接口读取记录仪的数据;上位机通过USB电缆与地面测试台相接,对回读的数据进行分析,同时验证记录仪是否正常工作。

2.系统硬件设计该系统采用隔离变压器隔离接收三路LVDS数据,使得隔离前后的电路没有电气连接特性,然后再将隔离后的信号传送给存储模块;经过存储模块的均衡、解串后传给FPGA中心控制器,最后存入两片Flash中。

遥测系统输出的三路数据都有各自的启动记录信号。

当记录仪接收到启动控制信号,开始记录对应路的数据,并存储到相应的存储模块中。

飞行试验完毕后,可以利用备用读数电缆,将各个存储模块中数据通过测试台上传至上位机中进行分析,以便对记录仪的存储功能进行验证。

在飞行模式下记录仪的供电由雷达系统完成。

记录仪由三个存储模块和一个接口模块组成。

存储模块主要接收遥测系统的视频回波、图像及遥测三路LVDS信号,并对其中的有效数据进行实时存储。

该模块主要包括以下几个部分:中心逻辑控制芯片FPGA、配置芯片PROM、LVDS电缆均衡器、LVDS解串芯片、存储芯片Flash、电源模块以及60MHz晶振等[1]。

基于FPGA的多通道高速数据采集系统设计共3篇基于FPGA的多通道高速数据采集系统设计1随着现代科技的高速发展,各种高速数据的采集变得越来越重要。

而基于FPGA的多通道高速数据采集系统因具有高速、高精度和高可靠性等优点,逐渐受到了越来越多人的关注和青睐。

本篇文章将围绕这一课题,对基于FPGA的多通道高速数据采集系统进行设计和探讨。

1、FPGA的基础知识介绍FPGA(Field-Programmable Gate Array)是可重构的数字电路,可在不使用芯片的新版本的情况下重新编程。

FPGA具有各种不同规模的可用逻辑单元数,可以根据需要进行定制化配置。

FPGA可以根据需要配置每个逻辑单元,并使用活动配置存储器从而实现功能的完整性、高速度和多样化的应用领域。

2、多通道高速数据采集系统的设计在高速数据采集领域中,多通道采集是非常常见的需求。

多通道采集系统通常由高速采集模块、ADC芯片、DSP芯片等核心部件组成。

在本文中,我们将会采用 Analog Devices(ADI)公司的AD7699高速ADC和Xilinx(赛灵思)公司的Kintex-7 FPGA,来设计多通道高速数据采集系统。

2.1系统架构设计系统架构是设计一个多通道高速数据采集系统的第一步。

本系统的架构由两个主要芯片组成,分别为高速的ADC模块和FPGA模块。

其中ADC模块负责将模拟信号转换为数字信号,而FPGA模块则负责将数据处理为人类可以处理的数据。

2.2模块设计由于本系统是多通道高速数据采集系统,所以我们需要设计多个模块来完成数据采集任务。

在本系统中,每个模块包含一个ADC芯片和一个FPGA芯片,用于处理和存储采集的数据。

ADC 芯片可以通过串行接口将数据传递给FPGA芯片,FPGA芯片则可以将数据存储在DDR3内存中。

2.3信号采集与处理对于多通道高速数据采集系统,信号的采集与处理是至关重要的。

因此我们需要谨慎设计。

在本系统中,每个通道的采样速率可以达到1MSPS,采样精度为16位。

技术创新《微计算机信息》2012年第28卷第10期120元/年邮局订阅号:82-946《现场总线技术应用200例》嵌入式与SOC一种便携式高速数据采集器的研究实现Realization of a portable High-speed Test Device(中储发展股份有限公司)张珂ZHANG Ke摘要:文中阐述了一种新的数据采集设备的设计实现方案,该方案基于热插拔技术和可编程设计理念,可通过参数的在线配置满足不同应用场合的测试需求,满足在系统可靠性,易用性,通用性和可移植性方面的要求。

关健字:FPGA;USB;FIFO;控制器中图分类号:TP 275文献标识码:AAbstract:The paper raised a novelty scheme to realize a new data test device.Based on USB and FPGA technique,The system could adjust to various testing needs via parameter configured on software.The scheme utilized module method and did a lot of study to make the system reliable,friendly,adjustable and transplantable.Key Words:FPGA;USB;FIFO;controller文章编号:1008-0570(2012)10-0212-021引言生产实践中往往需要掌握生产环节的参数,如储运企业需要对储运现场中的物资品种、类型、型号、等级、数量等数据进行动态地跟踪采集。

运用测量技术对有关参数进行实时采集、自动存储、即时显示、即时反馈、自动处理、自动传输等可以保证现场采集数据的真实、有效、实时、可用,缩短盘点周期和盘点时间,实现不停业盘点,减少现场操作失误。

图2 8路数据高速采集波形图

采集得到数字信号再通过电光调制转换成光信号,加载到光纤

通信网络中,最终通过光纤通信网络传输回主控制系统中。

图1 高速采集模块方案

高速数据采集系统的基本原理是将模拟量信号通过传感器将

携带信息的物理量转化成电压量,然后由ADC转换模块将模拟电

量变为数字电压量,最终进行数据的传输、存储以及相应的处

理。

在本高速采集系统中,由AV R与CPL D共同控制完成,对采集

①作者简介: 张伯超,男,2003年毕业于太原理工大学,就职于中国联合网络通信有限公司太原市分公司,

科技创新导报Science and Technology Innovation Herald

Copyright©博看网 . All Rights Reserved.。

一种高速数据采集记录装置的设计

【摘要】文章介绍了一种基于Flash的高速数据采集记录装置的实现方案;文中采用了Flash高速存储技术与FPGA的二级缓冲技术,提高了存储速度,突破存储芯片的瓶颈,成功实现了数据存储速率与传输速率完美的匹配;同时通过设计合理的电路降低了存储模块的功耗,利用可靠的通信协议,有效保证了信号数据的可靠接收和存储。

【关键词】数据记录仪;Flash;高速存储

1.系统方案设计

本文设计的数据记录系统由以下几部分组成:两台完全相同的数据记录仪、一个地面综合测试台、上位机、配套软件以及配套电缆。

主要用于记录由雷达系统产生的视频回波、图像及遥测三路LVDS高速信号。

系统工作时,由雷达系统首先发来启动记录信号,使已处于采集状态的两台记录仪同时工作,二者互为备份。

地面测试台产生的模拟信号供记录仪存储,同时可以控制记录仪进入不同的工作状态,通过内置的USB接口读取记录仪的数据;上位机通过USB电缆与地面测试台相接,对回读的数据进行分析,同时验证记录仪是否正常工作。

2.系统硬件设计

该系统采用隔离变压器隔离接收三路LVDS数据,使得隔离前后的电路没有电气连接特性,然后再将隔离后的信号传送给存储模块;经过存储模块的均衡、解串后传给FPGA中心控制器,最后存入两片Flash中。

遥测系统输出的三路数据都有各自的启动记录信号。

当记录仪接收到启动控制信号,开始记录对应路的数据,并存储到相应的存储模块中。

飞行试验完毕后,可以利用备用读数电缆,将各个存储模块中数据通过测试台上传至上位机中进行分析,以便对记录仪的存储功能进行验证。

在飞行模式下记录仪的供电由雷达系统完成。

记录仪由三个存储模块和一个接口模块组成。

存储模块主要接收遥测系统的视频回波、图像及遥测三路LVDS信号,并对其中的有效数据进行实时存储。

该模块主要包括以下几个部分:中心逻辑控制芯片FPGA、配置芯片PROM、LVDS 电缆均衡器、LVDS解串芯片、存储芯片Flash、电源模块以及60MHz晶振等[1]。

如图2.1所示:

接口模块主要包括LVDS高速读数接口、RS-422长线接口、视频及图像遥测雷达信号输入接口、各个存储模块的LVDS输入接口以及数据上传和指令下发接口。

高速读数接口与地面测试台主控卡的相应接口连接,通过LVDS接口高速读取其中的数据;422长线接口通过双绞线电缆与地面测试台连接,主要实现记录仪与地面测试台之间的通信。

3.系统逻辑设计

3.1 Flash高速存储技术设计

由于Flash是基于页读写、块擦除的工作模式[2],在对其进行读、写以及擦除操作都需要一定的等待时间,通过建立无效块列表,有效地提高了读写速率[3]。

由FPGA内部时序控制转换将生成的4K并行数据轮流写入两片Flash中,单片Flash采用交替双平面页编程方式,存储速率能够达到29.85MB/s。

采用两片Flash进行存储,从时间上看两个数据流同时流入两片Flash中,相当于数据总线增加了一倍,实现数据存储速率能够达到单片Flash存储速率的两倍,即有效数据存储率为59.7MB/s,大于有效数据的传输速率59MB/s,能够保证对每路数据源的可靠存储。

3.2 存储模块逻辑设计

LVDS数据流可以直接按字节方式分离并存储,该方式虽然可以降低FPGA 内部资源的消耗,但是加大了对存储数据恢复的复杂程度,并其中一路存储时出现丢数,容易影响到另一路数据的存储,造成数据结构的紊乱,导致存储数据无法恢复。

因此采用FPGA内部双口RAM资源,实现8Kbyte数据的缓冲,之后增加两个4K双口RAM,构成了二级缓冲。

对于单路的I/P/Q信号,数据在60M 的时钟下写入一级缓冲(8K)中,当判断写入数据大于7106后,以60M的速率连续读取4096个数据给二级缓冲A,同时控制Flash(A)模块对二级缓冲A 中的数据进行判断,当写入数据大于10个后,以30M的速率连续读取4096个并写入Flash(A)中;当再次判断一级缓冲(8K)中读写地址差值大于7106后,同样以60M的速率连续读取4096个数据,并写入二级缓冲B,当控制Flash(B)模块判断二级缓冲B中数据大于10个后,同样以30M的速率读取4096个后写满Flash(B)中的一页。

上述操作交替进行,实现LVDS数据流中的有效数据轮流有序地存入两片Flash中。

存储模块内部实现两级缓冲的逻辑原理框图见图:

4.系统可靠性设计

记录仪的正常工作离不开其可靠性设计。

若电路设计的不合理,记录仪的工作性能得不到保障,严重时会损坏设备,可见电路的可靠性设计[4]是记录仪正常运行的首要保障。

4.1 降低存储模块功耗的可靠性设计

存储模块的供电经过电源芯片进行电压转换,给存储模块内部芯片供电。

在未灌封之前进行多次常温测试发现,工作时电源芯片和XC3S200表面温度较高,而且由于对记录仪小体积的要求,要求内部芯片焊接很集中;而且记录仪在高空试验环境中会受到高冲击、高过载的影响,必须对记录仪存储模块进行灌封,增加抗冲击能力。

为了解决上述问题,降低消耗在存储模块电源芯片本身的功耗。

下面对存储模块进行温度测试试验。

为了获得存储单元灌封后的内部温度,我们

使用热电偶对内部多点进行测量,实时显示温度。

在试验一和试验二中,我们选定以下七个点,试验三中增加了中壳体外壁一点。

通过以上设计的试验可以看出,当存储模块的供电电源输入为3.6V左右时,测试各点的温度都所有下降,在芯片正常工作范围内,且存储模块在长达十几小时的高温环境中仍能正常工作,说明存储模块输入电源采用3.6V供电的可靠性。

4.2 记录仪通信的可靠性设计

在整个存储设备中,RS-422传输协议主要实现记录仪与测试台之间的通信功能,控制记录仪的工作状态,另外,还可以完成记录仪的长线读数功能。

数据是以串行差分形式传输,测试台主控卡向记录仪下发传输命令的长度都是以6个字节为基本单位,其中,前两个字节为固定帧头“55H”、“AAH”;第3个字节为命令长度,为固定的“02H”;第4、5个字节为命令字,针对不同的命令会有对应的命令字;第6个字节是校验和,大小等于两个命令字的和。

记录仪也采用相同的命令格式进行返回命令的上传[5]。

为保证控制指令传输的可靠性,数据校验是必不可少的,因此,我们在协议中设计了校验码。

同时,协议中还设计了命令信号从测试台、接口板、存储板、接口板,最后返回测试台指令反馈机制,增强了系统对错误命令的识别能力,提高了系统执行命令的抗干扰能力。

5.结论

文中研究的高速数据记录仪设备采用了双片选、双平面交替编程进行数据存储,并通过FPGA内部的二级缓冲技术,使得记录仪的总体写入速度加倍,采用合理的电路降低存储模块的功耗,利用可靠的通信协议,有效保证了信号数据的可靠接收和存储,完全满足设计的高速存储要求。

目前该系统通过了高低温、振动、冲击及电磁兼容等环境试验,能够满足实际的工程要求。

参考文献

[1]Gyu Sang Choi,Byung-Won On.Study of the performance impact of a cache buffer in solid-state disks[J].Microproc-essors and Microsystems,2011,35(3):359-369.

[2]高怡祯.基于闪存的星载大容量存储器的研究和实现[J].电子技术应用,2003,8:75-78.

[3]Jeong-Uk Kang,Jin-Soo Kim,Chanik Park,Hyoungjun Park,Joonwon Lee.A multi-channel architecture for high-performance NAND flash-based storage system[J].Journal of Systems Architecture,2007,52(9):644-658.

[4]李煊,丁为.常用设备串口通信协议及其应用[J].自动化仪表,2011,32

(10):82-86.。