第10章VHDL有限状态机设计2015

- 格式:ppt

- 大小:2.09 MB

- 文档页数:6

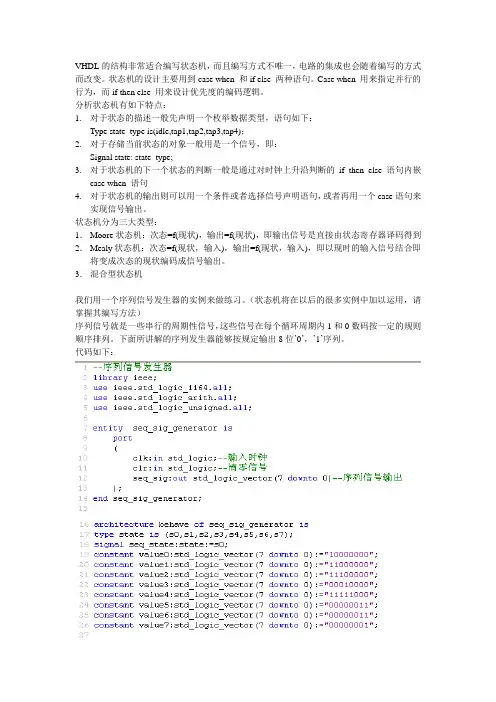

VHDL的结构非常适合编写状态机,而且编写方式不唯一,电路的集成也会随着编写的方式而改变。

状态机的设计主要用到case when 和if else 两种语句。

Case when 用来指定并行的行为,而if then else 用来设计优先度的编码逻辑。

分析状态机有如下特点:1.对于状态的描述一般先声明一个枚举数据类型,语句如下:Type state_type is(idle,tap1,tap2,tap3,tap4);2.对于存储当前状态的对象一般用是一个信号,即:Signal state: state_type;3.对于状态机的下一个状态的判断一般是通过对时钟上升沿判断的if then else 语句内嵌case when 语句4.对于状态机的输出则可以用一个条件或者选择信号声明语句,或者再用一个case语句来实现信号输出。

状态机分为三大类型:1.Moore状态机:次态=f(现状),输出=f(现状),即输出信号是直接由状态寄存器译码得到2.Mealy状态机:次态=f(现状,输入),输出=f(现状,输入),即以现时的输入信号结合即将变成次态的现状编码成信号输出。

3.混合型状态机我们用一个序列信号发生器的实例来做练习。

(状态机将在以后的很多实例中加以运用,请掌握其编写方法)序列信号就是一些串行的周期性信号,这些信号在每个循环周期内1和0数码按一定的规则顺序排列。

下面所讲解的序列发生器能够按规定输出8位’0’,’1’序列。

代码如下:逐行解释:10:清零复位信号,高电平复位清零。

12:序列信号输出。

因为是8位的端口,但序列信号是串行的,所以相当于有8路的序列信号,任取一位端口就是一个序列信号输出。

17:用type声明一种枚举类型。

共8中状态,每个状态都对应唯一的一种输出,至于在什么状态输出什么信号则由程序决定。

18:定义一个state类型信号量,其初始的状态为s0。

19-26:用constant定义一些常量,这些常量将作为在不同状态时的输出信号。

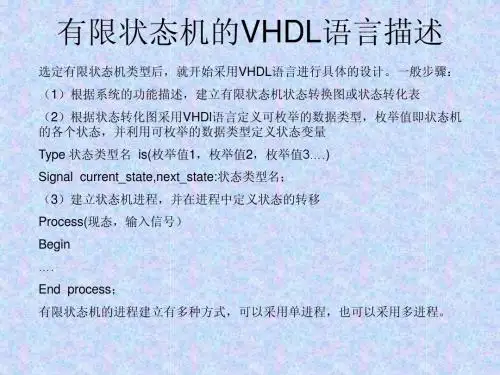

用VHDL设计有限状态机的方法现代数字系统的设计一般都采用自顶向下的模块化设计方法。

即从整个系统的功能出发,将系统分割成若干功能模块。

在自顶向下划分的过程中,最重要的是将系统或子系统按计算机组成结构那样划分成控制器和若干个受控制的功能模块。

受控部分通常是设计者们所熟悉的各种功能电路,设计较为容易。

主要任务是设计控制器,而其控制功能可以用有限状态机来实现。

因而有必要深入探讨有限状态机的设计方法。

1 状态机设计的一般方法 传统的设计方法是首先绘制出控制器的状态利用VHDL设计状态机,不需要进行繁琐的状态分配、绘制状态表和化简次态方程。

设计者不必使用卡诺(1)根据系统要求确定状态数量、状态转移的条件和各状态输出信号的赋值,并画出状态转移(2)按照状态转移(3)利用EDA工具对状态机的功能进行仿真验证。

下面以离心机定时顺序控制器的设计为例,说明状态机的设计方法。

2 定时顺序控制状态机的设计 在化工生产中,离心机用于固、液分离的工艺流程,如系统工作方式如下:当系统处于初始状态或复位信号reset有效时,系统处于复位状态。

按下自动工作键C0,系统进入加料工序并开始自动控制离心机的运行。

以加水工序为例,首先在加水预置数状态(water_ld)时,状态机输出信号FO,开启加水电磁阀及指示灯,同时输出信号G控制选通加水时间预置数,在LD1信号的控制下,将预置数送入COUNTER1。

此时ENA1=1,J=1,使计数器为减计数状态。

然后,在下一个时钟周期进入加水工作状态(water),并开始减计时。

当计时为零时,计数器发出借位信号R1作为此工序结束的信号送入状态机,使其转入。

《VHDL语言程序设计》课程教学大纲课程简介课程简介:本课程为软件工程专业嵌入式专业方向的专业课,是开发基于FPGA/CPLD嵌入式系统的必备基础。

主要内容包括FPGA/CPLD目标器件的结构和工作原理、EDA技术和工作流程、VHDL基础知识、VHDL实用方法和设计深入、原理图输入法、LPM宏功能模块实用方法、状态机设计以及EDA优化设计。

目的是为后续课程的学习和嵌入式系统的设计作必须的基础准备。

课程大纲一、课程的性质与任务:本课程是软件工程专业的专业方向课程。

教学任务主要包括使学生了解EDA技术的工作流程,正确使用开发平台,掌握以VHDL为代表的硬件描述语言的基本知识、编程实用方法和工程设计方法,掌握原理图设计法、状态机设计法,能够正确使用IP Core和LPM等宏功能模块。

本课程是软件工程专业嵌入式专业方向的第一门专业方向课,是后续课程的必备基础,具有较重要的地位。

二、课程的目的与基本要求:本课程涉及到的学科基础知识面广,要求软硬件兼备,需要较好的学科基础。

通过本课程的学习,最终达到能够设计基于FPGA/CPLD的ASIC,并能进行EDA优化的目的。

三、面向专业:软件工程四、先修课程:《计算系统基础》五、本课程与其它课程的联系:本课程的先行课程是计算系统基础。

服务的主要后续课程包括基于FPGA的嵌入式软件开发、基于ARM的嵌入式软件开发等。

六、教学内容安排、要求、学时分配及作业:第一章概述(2学时)1.1 EDA技术及其发展(C)1.2 硬件描述语言硬件描述语言种类、自顶向下设计方法、EDA工程设计流程。

(A)1.3 面向FPGA/CPLD的开发流程设计输入、分析综合、布局布线、仿真、下载和硬件测试。

(A)1.4 IP Core 及EDA技术发展趋势。

(C)第二章 FPGA硬件特性与编程技术(8学时)2.1 PLD发展历程及其分类(c)2.2 低密度PLD工作原理PROM、PLA、PAL、GAL。

自动售货机控制系统VHDL有限状态机实现1 引言有限状态机FSM(Finite State Machine)及其设计技术是实用数字系统设计中实现高效率、高可靠逻辑控制的重要途径。

传统的状态机设计方法需进行繁琐的状态分配、绘制状态表、化简次态方程等,而利用VHDL可以避免这些繁琐的过程,直接利用状态转换图进行状态机的描述,所有的状态均可表达为CASE_WHEN结构中的一条CASE语句,而状态的转移则通过IF_THEN_ELsE语句实现。

此外,与VHDL的其它描述方式相比,状态机的VHDL表述丰富多样,程序层次分明,结构清晰,易读易懂;在排错、修改和模块移植方面也有其独到的特点。

2 自动售货机控制系统的实现2.1 自动售货机功能描述及控制系统组成设计一个自动售货机的逻辑控制电路。

它有两个投币口分别为一元投币口和五角投币口,假设每次只能投入一枚一元或五角硬币,投入一元五角硬币后机器自动给出一瓶矿泉水,投入两元硬币后,在给出一瓶矿泉水的同时找回一枚五角的硬币。

图1为自动售货机控制系统方框图,由投币信号处理模块和功能控制模块组成。

2.2 自动售货机控制功能的状态描述取投币信号为输入逻辑变量,投入一枚一元硬币时用A=1表示,未投入时A=0。

投入一枚五角硬币用B=1表示,未投入时B=0。

给出矿泉水和找钱为两个输出变量,分别用Z和Y表示,给出矿泉水时Z=1,不给时Z=0,找回一枚五角硬币时Y=1,不找时Y=0。

根据上面的功能描述,可用三个状态S0,S1,S2表示,未投币前的初始状态为S0,投入五角硬币以后为S1,投入一元硬币后(包括投入一枚一元硬币和投入两枚五角硬币的情况)为S2,再投入一枚五角硬币后电路返回S0,同时输出为Z=1,Y=0;如果投入的是一枚一元硬币,则电路也应能返回S0,同时输出为Z=1,Y=1。

根据上面的分析可得到状态转换图如图2所示。

2.3 自动售货机功能控制模块的VHDL实现根据图2所示的状态转换图,用VHDL语言中的CASE_WHEN结构和IF_THEN_ELSE语句实现控制功能,源程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY shj_ctrl ISPORT(A,B:IN STD_LOGIC;clk:IN STD_LOGIC;Z,Y:OUT STD_LOGIC);END shj_ctrlARCHITECTURE beha OF shi_ctrl ISTYPE states IS(S0,S1,S2);SIGNAL state:states;SIGNAL X:STD_LOGIC_VECTOR(1 DOWNTO 0);BEGINX<=A&B;PROCESS(x,state)BEGINIF rising_edge(clk) THENCASE state ISWHEN S0=>Z<='0';Y<='0';IF(X="01")THENstate<=s1;ELSIF(X="10")THENstate<=s2;ELSEstate<=s0;END IF;WHEN S1=>Z<='0';Y<='0';IF(X="01")THENstate<=s2;ELSIF(X="10")THENstate<=S0;Z<='1';Y<='0';ELSEstate<=s1;END IF;WHEN S2=>Z<='0';Y<='0';IF(X="01")THENstate<=S0;Z<='1';Y<='0';ELSIF(X="10")THENstate<=s0;Z<='1';Y<='1';ELSEstate<=s2;END IF;END CASE;END IF;END PROCESS;END beha;c上面程序中,A、B分别为一元硬币和五角硬币驱动信号,Z为矿泉水输出信号,Y为找钱输出信号。

一.设计功能与要求:要求设计一个序列检测器,检测序列为1110010。

序列检测器用于检测一组或由二进制码组成的脉冲序列信号,在数字通信中有着广泛的应用。

当序列检测器连续收到一组串行二进制码后,如果这组码与检测器中预先设置的码相同,则输出1,否则输出0。

由于这种检测的关键在于正确码的收到必须是连续的,这就要求检测器必须记住前一次的正确码及正确序列,直到在连续的监测中所收到的每一位码都与预置的对应码相同。

在监测过程中,任何一位不相等都将回到初始状态重新开始监测。

二、设计思路在状态连续变化的数字系统设计中,采用状态机的设计思想有利于提高设计效率,增加程序的可读性,减少错误的发生几率。

同时,状态机的设计方法也是数字系统中一种常用的设计方法,其输出仅仅是当前状态值的函数,并且在时钟上升沿到来时才发生变化。

本实验要从一串二进制码中检测出一个已预置的7位二进制码(1110010),每增加一位二进制相当于增加一个状态,用7个状态可以实现。

一、原理图说明如上图中所示,S1——S8这八个状态之间按照一定的规则进行转换,下一个状态是S1——S8之中的哪个状态,由当前状态和输入条件(0或1)决定。

三、程序代码--Sequence Detector--Check the sequence 1110010library ieee;use ieee.std_logic_1164.all;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity check_state1 isport(clk,clr:in std_logic;din:in std_logic;z:out std_logic);end entity;architecture behavior of check_state1 istype state_type is (s1,s2,s3,s4,s5,s6,s7,s8);signal state:state_type:=s1;beginprocess(clk,clr,state,din)beginif clr='1' thenz<='0';state<=s1;elsif clk'event and clk='1' thencase state iswhen s1 => z<='0';if din='1' thenstate<=s2;end if;when s2 => z<='0';if din='1' thenstate<=s3;elsestate<=s1;end if;when s3 => z<='0';if din='1' thenstate<=s4;elsestate<=s1;end if;when s4 => z<='0';if din='0' thenstate<=s5;elsestate<=s4;end if;when s5 => z<='0';if din='0' thenstate<=s6;elsestate<=s2;end if;when s6 => z<='0';if din='1' thenstate<=s7;elsestate<=s1;end if;when s7 => z<='0';if din='0' thenstate<=s8;elsestate<=s3;end if;when s8 => z<='1';if din='0' thenstate<=s1;elsestate<=s2;end if;end case;end if;end process;end;三、执行结果生成状态图仿真结果当输入的连续7位二进制数据的序列位1110010的时候输出Z=1,其他状态时输出是0。