实验二半加器全加器

- 格式:ppt

- 大小:381.50 KB

- 文档页数:3

《数字电子技术B》实验报告班级:姓名学号:实验二组合逻辑电路(半加器、全加器)一、实验目的1.掌握组合逻辑电路的功能测试。

2.验证半加器和全加器的逻辑功能。

3.学会二进制数的运算规律。

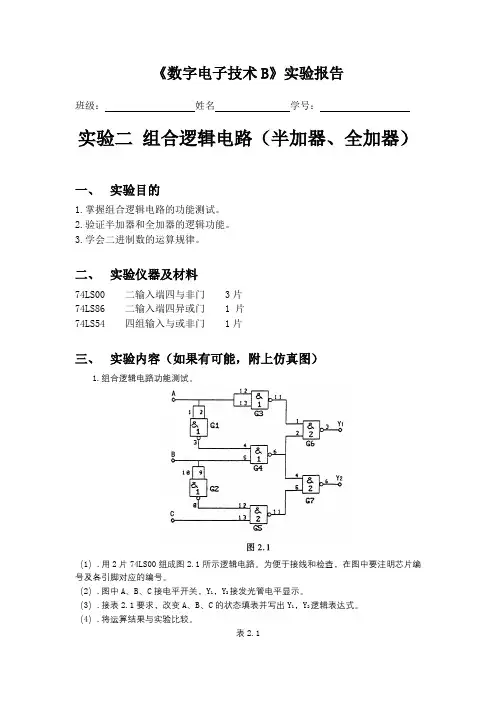

二、实验仪器及材料74LS00 二输入端四与非门 3片74LS86 二输入端四异或门 1 片74LS54 四组输入与或非门 1片三、实验内容(如果有可能,附上仿真图)1.组合逻辑电路功能测试。

(1).用2片74LS00组成图2.1所示逻辑电路。

为便于接线和检查,在图中要注明芯片编号及各引脚对应的编号。

(2).图中A、B、C接电平开关,Y1,Y2接发光管电平显示。

(3).接表2.1要求,改变A、B、C的状态填表并写出Y1,Y2逻辑表达式。

(4).将运算结果与实验比较。

表2.1Y1=A+B Y2=(A’*B)+(B’*C)2.测试用异或门(74LS86)和与非门组成的半加器的逻辑功能。

根据半加器的逻辑表达式可知,半加器Y是A、B的异或,而进位Z是A、B相与,故半加器可有一个集成异或门和二个与非门组成如图2.2。

图2.2(1).在实验仪上用异或门和与门接成以上电路。

A、B接电平开关K,Y,Z接电平显示。

(2).按表2.2要求改变A、B状态,填表。

表2.23.(1).写出图2.3电路的逻辑表达式。

(2).根据逻辑表达式列真值表。

表2.3(5)按原理图选择与非门并接线进行测试,将测试结果记入表2.4,并与上表进行比较看逻辑功能是否一致。

4. 测试用异或、与或和非门组成的全加器的逻辑功能。

全加器可以用两个半加器和两个与门一个或门组成,在实验中,常用一块双异或门、一个与或非门和一个与非门实现。

(1).画出用异或门、与或非门和非门实现全加器的逻辑电路图,写出逻辑表达式。

(2).找出异或门、与或非门和与门器件按自己画出的图接线。

接线时注意与或非门中不用的与门输入端接地。

(3).当输入端A i、B i及C i-1为下列情况时,用万用表测量S i和C i的电位并将其转为逻辑状态填入下表。

班级姓名学号实验二组合电路设计一、实验目的(1)验证组合逻辑电路的功能(2)掌握组合逻辑电路的分析方法(3)掌握用SSI小规模集成器件设计组合逻辑电路的方法(4)了解组合逻辑电路集中竞争冒险的分析和消除方法二、实验设备数字电路实验箱,数字万用表,74LS00, 74LS86三、实验原理1 •组合逻辑概念通常逻辑电路可分为组合逻辑电路和时序逻辑电路两大类。

组合逻辑电路又称组合电路,组合电路的输出只决定于当时的外部输入情况,与电路的过去状态无关。

因此,组合电路的特点是无“记忆性”。

在组成上组合电路的特点是由各种门电路连接而成,而且连接中没有反馈线存在。

所以各种功能的门电路就是简单的组合逻辑电路。

组合电路的输入信号和输出信号往往不只一个,其功能描述方法通常有函数表达式、真值表,卡诺图和逻辑图等几种。

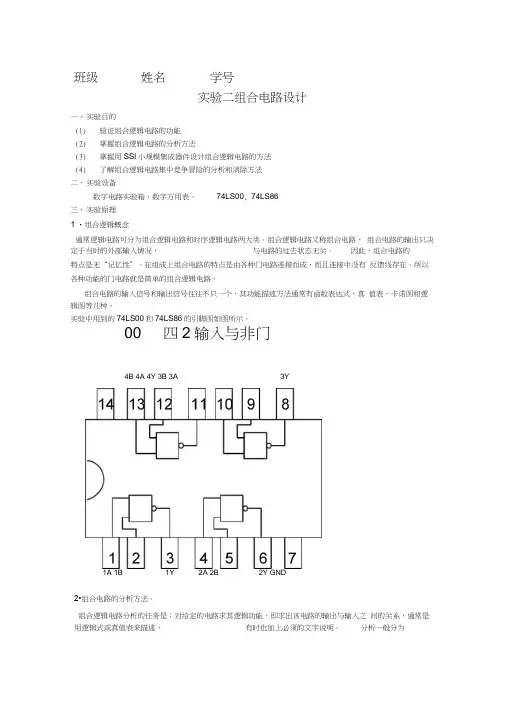

实验中用到的74LS00和74LS86的引脚图如图所示。

00 四2输入与非门4B 4A 4Y 3B 3A 3Y1A 1B 1Y 2A 2B 2Y GND2•组合电路的分析方法。

组合逻辑电路分析的任务是:对给定的电路求其逻辑功能,即求出该电路的输出与输入之间的关系,通常是用逻辑式或真值表来描述,有时也加上必须的文字说明。

分析一般分为(1)由逻辑图写出输出端的逻辑表达式,简历输入和输出之间的关系。

(2)列出真值表。

(3)根据对真值表的分析,确定电路功能。

3•组合逻辑电路的设计方法。

组合逻辑电路设计的任务是:由给定的功能要求,设计出相应的逻辑电路。

一般设计的逻辑电路的过程如图(1)通过对给定问题的分心,获得真值表。

在分析中要特别注意实际问题如何抽象为几个输入变量和几个输出变量直接的逻辑关系问题,其输出变量之间是否存在约束关系,从而过得真值表或简化真值表。

(2)通过卡诺图化简或逻辑代数化简得出最简与或表达式,必要时进行逻辑式的变更,最后画出逻辑图。

(3)根据最简逻辑表达式得到逻辑电路图。

四•实验内容。

1•分析,测试半加器的逻辑功能。

实验二半加器和全加器及其应用一、实验目的1.掌握全加器和半加器的逻辑功能。

2.熟悉集成加法器的使用。

3.了解算数运算电路的结构。

二、实验设备1.数字电路试验箱;2.74LS00,74SL86。

三、实验原理半加器(m =0半加,m=1为半减)能实现两个一位二进制数的算术加法及向高位进位,而不考虑低位进位的逻辑电路。

它有两个输入端,两个输出端。

半加器电路是指对两个输入数据位进行加法,输出一个结果位和高位的进位,不考虑输入数据的进位的加法器电路。

是实现两个一位二进制数的加法运算电路。

数据输入A 被加数、B加数,数据输出S和数(半加和)、进位C0。

同理,能对两个1位二进制数进行相减不考虑低位来的借位求得差及借位的逻辑电路称为半减器.设减数和被减数分别用A和B,表示差用S,表示向高位的借位用C0。

全加器,全减器(m =0为全加,m=1为全减)全加器是实现两个一位二进制数及低位来的进位数相加(即将三个一位二进制数相加),求得和数及向高位进位的逻辑电路。

根据全加器功能,其真值表如下表所示。

表中A及B分别代表被加数及加数,C1是低位来的进位,S代表相加后得到的和位,C0代表向高位的进位。

图中C1是进位输入端,C0是进位输出端。

同理,能对两个1位二进制数进行相减并考虑低位来的借位求得差及借位的逻辑电路称为全减器.设减数和被减数分别用A和B表示低位来的借位用C1,表示差用S,表示向高位的借位用C0。

四、实验内容实验一、实现半加器,半减器,当M为0时实现逻辑变量A、B的半加功能,当M为1时实现逻辑变量A、B的半减功能。

实验二、实现全加器,全减器,当M为0时实现逻辑变量A、B的全加功能,C i为进位值。

当M为1时实现逻辑变量A、B的全减功能,C i为借位值。

五、实验数据1实现半加、半减器(1)真值表(2)卡诺图S的卡诺图:S=A⊕B(3)C0的卡诺图S=B (M⊕A)2实现全加器(1)真值表S的卡诺图:S=A⊕(B⊕C)C0的卡诺图:C0=BC i+(B⊕C)(M⊕A)六.实验电路图及仿真半加半减的实现全加全减的实现七.实验心得通过本次实验,我将理论知识以及实践知识相结合,进一步了解到74LS00,74SL86芯片的原理,并提升了自己的实际动手能力。

《数字电路与逻辑设计实验》实验报告实验名称:组合逻辑电路(半加器全加器及逻辑运算)实验器材(芯片类型及数量)7400 二输入端四与非门,7486 二输入端四异或门,7454 四组输入与或非门一、实验原理1、组合逻辑电路的分析方法:(1)从输入到输出,逐步获取逻辑表达式(2)简化逻辑表达式(3)填写真值表(4)通过真值表总结出该电路的功能(5)选择芯片型号,绘制电路图,测试并验证之前的分析是否正确2、组合逻辑电路的设计方法:(1)根据实际逻辑问题的因果关系,定义输入输出变量的逻辑状态(2)根据设计要求,按逻辑功能列出真值表,填写卡诺图(3)通过卡诺图或真值表得到逻辑表达式(4)根据逻辑方程式画出图表,进行功能试验二、实验内容及原理图1、完成与非门、异或门、与或非门逻辑功能测试。

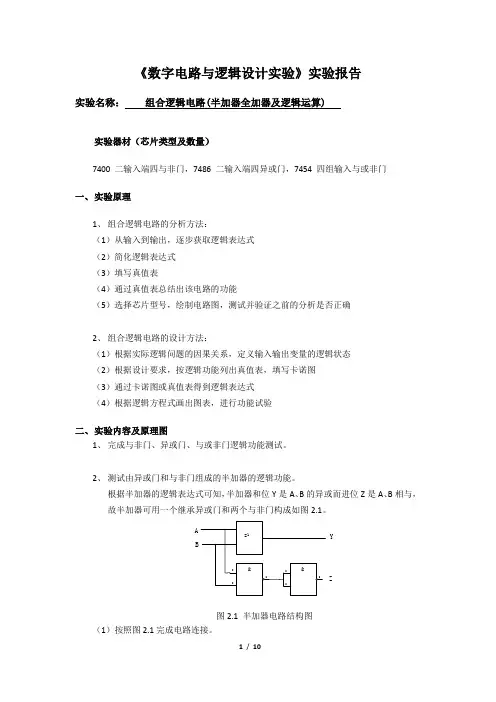

2、测试由异或门和与非门组成的半加器的逻辑功能。

根据半加器的逻辑表达式可知,半加器和位Y是A、B的异或而进位Z是A、B相与,故半加器可用一个继承异或门和两个与非门构成如图2.1。

AYBZ图2.1 半加器电路结构图(1)按照图2.1完成电路连接。

(2)按照表2.1改变A 、B 状态,并填表。

3、 测试全加器的逻辑功能。

SiG9CiA iB iC i-1图2.2 全加器电路结构图(1)写出图2.2的逻辑功能表达式(Y S i C i ) Y = Ai ⊕ Bi Si = Ai ⊕ Bi ⊕ Ci -1 Ci = AiBi + (Ai ⊕ Bi) Ci -1 (2)根据逻辑功能表达式列出真值表(3)按原理图选择与非门并接线测试,将结果记入表2.2。

4、 用异或、与或非门和与非门实现全加器的逻辑功能。

全加器可以用两个半加器和两个与门一个或门组成,在实验中,常用一块双异或门、一个与或非门和一个与非门实现。

(1)画出用异或门、与或非门和非门实现全加器的逻辑电路图,写出逻辑表达式。

Y = Ai ⊕ Bi Si = Ai ⊕ Bi ⊕ Ci -1 Ci = AiBi + (Ai ⊕ Bi) Ci -1(2)找出异或门、与或非门和与非门器件按自己画的图接线。

实验三运算电路(半加器、全加器及逻辑运算)一、实验目的1、掌握组合逻辑电路的功能测试。

2、验证半加器全加器的逻辑功能。

3、学会二进制的运算规律。

二、实验仪器及器件1、元器件:74LS00 二输入端四与非门 3 片74LS86 二输入端四异或门 1 片三、预习要求1、预习组合逻辑电路的分析方法;2、预习用与非门和异或门构成的半加器、全加器的工作原理;3、预习二进制数的运算。

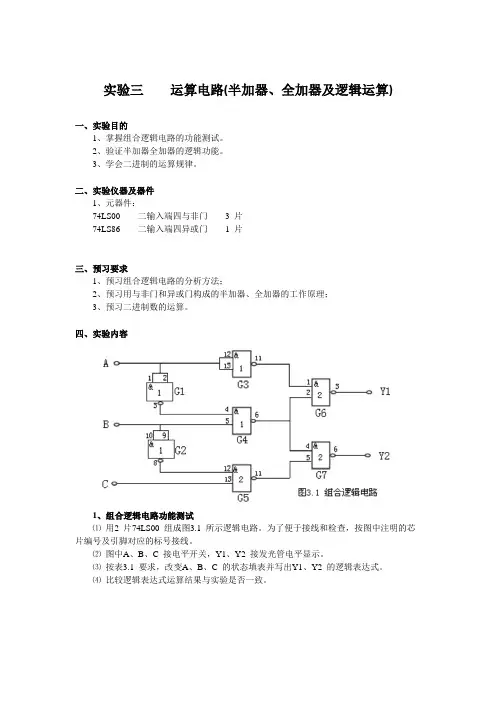

四、实验内容1、组合逻辑电路功能测试⑴用2 片74LS00 组成图3.1 所示逻辑电路。

为了便于接线和检查,按图中注明的芯片编号及引脚对应的标号接线。

⑵图中A、B、C 接电平开关,Y1、Y2 接发光管电平显示。

⑶按表3.1 要求,改变A、B、C 的状态填表并写出Y1、Y2 的逻辑表达式。

⑷比较逻辑表达式运算结果与实验是否一致。

2、测试用异或门(74LS86)和与非门组成的半加器的逻辑功能根据半加器的逻辑表达式可知,半加器Y 是A、B 的异或,而进位Z 是A、B 相与,故半加器可用一个集成异或门和二个与非门组成如图3.2。

⑴在实验箱上用异或门和与非门接成以上电路。

A、B 接电平开关、Y、Z 接电平显示。

⑵按表3.2 要求改变A、B 状态,将实验结果填表。

3、测试全加器的逻辑功能。

⑴写出图3.3 电路的逻辑表达式;⑵根据逻辑表达式列出真值表;⑶根据真值表画出函数Si、Ci 的卡诺图。

Y = A’B+AB’Z =C X1 =A’B+C’+ABX2 =A’B’+AB+C X3 =A’B+AB’+C’S i =A’B’C+A’BC’+AB’C+ABCC i =AC+AB+BC⑷填写表3.3 各点状态。

⑸按照原理图选择与非门,接线进行测试。

将结果记录在表3.4 中,并与表3.3 数据进行比较,看逻辑功能是否一致。

4、测试用异或、与或和非门组成的全加器的逻辑功能⑴画出用异或门、与或非门和非门实现全加器的逻辑电路图,写出逻辑表达式。

⑵用上述三块逻辑电路器件按自己画出接线图。

组合逻辑电路实验(半加器全加器及逻辑运算)一、实验目的1、掌握组合逻辑电路的功能测试。

2、验证半加器和全加器的逻辑功能。

3、学会二进制数的运算规律。

二、实验原理数字电路分为组合逻辑电路和时序逻辑电路两类。

任意时刻电路的输出信号仅取决于该时刻的输入信号,而与信号输入前电路所处的状态无关,这种电路叫做组合逻辑电路。

分析一个组合电路,一般从输出开始,逐级写出逻辑表达式,然后利用公式或卡诺图等方法进行化简,得到仅含有输入信号的最简输出逻辑函数表达式,由此得到该电路的逻辑功能。

两个一位二进制数相加,叫做半加,实现半加操作的电路称为半加器。

两个一位二进制数相加的真值表见表5-1,表中Si表示半加和,Ci表示向高位的进位,Ai、Bi表示两个加数。

表5-1 半加器真值表从二进制数加法的角度看,表中只考虑了两个加数本身,没有考虑低位来的进位,这也就是半加一词的由来。

由表5-1可直接写出半加器的逻辑表达式: 、Ci=AiBi由逻辑表达式可知,半加器的半加和Si是Ai、Bi的异或,而进Si=AiBi AiBi位Ci 是Ai 、Bi 相与,故半加器可用一个集成异或门和一个与门组成。

两个同位的加数和来自低位的进位三者相加,这种加法运算就是全加,实现全加运算的电路叫做全加器。

如果用Ai 、Bi 分别表示A 、B 两个多位二进制数的第i 位,1i C -表示低位(第i-1位)来的进位,则根据全加运算的规则可列出真值表如表5-2。

表5-2 全加器的真值表利用卡诺图可求出Si 、Ci 的简化函数表达式:i i i i-1i i i i i i S =A B C C =(A B )C +A B ⊕⊕⊕可见,全加器可用两个异或门和一个与或门组成。

如果将数据表达式进行一些变换,半加器还可以用异或门、与非门等元器件组成多种形式的电路(见图5-2,图5-3)。

三、实验仪器及材料 器件:74LS00 二输入端四与非门 3片 74LA86 二输入端四异或门 1片 74LS54 四组输入与或非门 1片四、预习要求1、预习组合逻辑电路的分析方法。

二进制半加器和全加器在数字电路中,二进制半加器和全加器是两个重要的组合逻辑电路。

它们被广泛应用于计算机系统和其他数字电路中,用于实现二进制数的加法运算。

本文将分别介绍二进制半加器和全加器的原理、功能和应用。

一、二进制半加器二进制半加器是一种简单的逻辑电路,用于实现两个二进制位的加法运算。

它由两个输入端和两个输出端组成,分别为两个二进制数的位相加结果和进位输出。

半加器的输入可以是0或1,输出也可以是0或1。

半加器的原理很简单,它通过逻辑门电路实现两个输入位的异或运算,得到位相加的结果;同时,通过与门电路实现两个输入位的与运算,得到进位输出。

具体电路图如下所示:输入A --|-------|______输入B --|-------| ||异或门 |------- 输出S|与门 |------- 输出C|||半加器的功能是将两个二进制位相加,得到位相加结果和进位输出。

例如,输入A为1,输入B为0,则输出S为1,输出C为0。

半加器的应用场景比较有限,主要用于实现较简单的二进制加法运算,例如在寄存器和加法器中的应用。

二、全加器全加器是一种更为复杂的逻辑电路,用于实现三个二进制位的加法运算。

它由三个输入端和两个输出端组成,分别为三个二进制数的位相加结果和进位输出。

全加器的输入和输出也可以是0或1。

全加器的原理是在半加器的基础上进行扩展,它通过组合多个半加器的输入和输出,实现三个二进制位的加法运算。

具体电路图如下所示:______输入A --|-------| |______ |输入B --|-------| |______ |输入C --|-------| ||异或门 |------- 输出S|与门 |------- 输出C|||全加器的功能是将三个二进制位相加,得到位相加结果和进位输出。

例如,输入A为1,输入B为1,输入C为0,则输出S为0,输出C为1。

全加器的应用场景更加广泛,可以用于实现任意长度的二进制加法运算,例如在算术逻辑单元(ALU)和加法器中的应用。

北京邮电大学世纪学院<通信工程系数字电路实验>实验报告实验名称:VHDL半加器与全加器的设计与验证实验班级:姓名:专业:学号:实验室:实验组别:实验时间:审阅教师:评定成绩:实验题目基于 VHDL 的半加器与全加器的设计与验证实验一、实验目的1、学习 Quartus II 软件的使用;2、VHDL 半加器的设计与验证实验;3、VHDL 全加器的设计与验证实验;4、掌握模块的 VHDL 调用;5、学习基于 VHDL 的数字电路的设计。

二、预习内容1、VHDL 语言的基本结构;2、VHDL 语言的数据类型和运算操作符;3、VHDL 语言的主要描述语句;三、实验内容本实验主要运用 Quartus II 软件进行 VHDL 电路设计;内容一、VHDL 半加器的设计,包括电路设计并进行时序仿真验证,然后将电路设计进行实际电路的验证;内容二、VHDL 全加器的设计,在VHDL 程序中调用生成的半加器图形符号完成全加器设计,时序仿真验证后,将全加器电路进行实际电路的验证;本实验的重点和难点是 VHDL 语言的使用1、VHDL 半加器电路的设计2、VHDL 半加器电路的时序验证3、VHDL 全加器电路的设计4、全加器电路的时序验证四、实验结果分析对所设计的半加器电路、全加器电路进行实际电路的验证。

分析:五、思考题1、在采用 Quartus II 软件进行 VHDL 电路设计中,工程名、实体名、结构体名如何选取,实体名、结构体名是否可以任意选取,为什么?2、一个完整的 VHDL 语言程序通常包含那几部分?3、VHDL 结构体有那三种描述方式?六、总结。

实验⼆组合逻辑电路(半加器、全加器)

实验⼆组合逻辑电路(半加器、全加器)

⼀、实验⽬的:

1.加深理解组合逻辑电路的特点和⼀般分析⽅法;

2.熟悉组合逻辑电路的设计⽅法;

3.验证半加器、全加器的功能。

⼆、实验仪器、设备、元器件:

1.数字逻辑电路实验仪 1台

2.四2输⼊与⾮门74LS00芯⽚ 1⽚

3.四2输⼊异或门74LS86芯⽚ 1⽚

4.六反向器74LS04芯⽚ 1⽚

5.⽰波器或万⽤表

三、预习要求:

1.复习组合逻辑电路的分析和设计⽅法;

2.复习半加器、全加器的⼯作原理;

3.根据设计任务要求,设计组合逻辑电路,画出逻辑图。

四、实验内容和步骤:

1.测试半加器的逻辑功能

根据图2.1所⽰连接好电路。

输⼊A、B端分别接两个逻辑电平开关,输出端S、C接颜⾊不同的发光⼆极管。

观察当输⼊端A、B电平变化时,输出端S、C电平指⽰器的状态。

验证逻辑状态并填表。

图2.1由与⾮门组成的半加器电路表 2.1 逻辑真值表

写出逻辑表达式:Ci= C = 2.测试全加器的逻辑功能

1

- -

1

C1

2

3

A

74LS00 4

5

6

B

74LS00 1

2

3

A

74LS86 4

5

6

B

74LS86 8

9

10

C

74LS00 B

A

Ci-1

Si

Ci。

《数字电子技术》组合逻辑电路(半加器全加器及逻辑运算)一、实验目的1、掌握组合逻辑电路的功能测试。

2、验证半加器和全加器的逻辑功能。

3、学会二进制数的运算规律。

二、实验原理数字电路分为组合逻辑电路和时序逻辑电路两类。

任意时刻电路的输出信号仅取决于该时刻的输入信号,而与信号输入前电路所处的状态无关,这种电路叫做组合逻辑电路。

分析一个组合电路,一般从输出开始,逐级写出逻辑表达式,然后利用公式或卡诺图等方法进行化简,得到仅含有输入信号的最简输出逻辑函数表达式,由此得到该电路的逻辑功能。

两个一位二进制数相加,叫做半加,实现半加操作的电路称为半加器。

两个一位二进制数相加的真值表见表5-1,表中Si 表示半加和,Ci 表示向高位的进位,Ai 、Bi 表示两个加数。

表5-1 半加器真值表从二进制数加法的角度看,表中只考虑了两个加数本身,没有考虑低位来的进位,这也就是半加一词的由来。

由表5-1可直接写出半加器的逻辑表达式:Si=AiBi AiBi +、Ci=AiBi 由逻辑表达式可知,半加器的半加和Si 是Ai 、Bi 的异或,而进位Ci 是Ai 、Bi 相与,故半加器可用一个集成异或门和一个与门组成。

两个同位的加数和来自低位的进位三者相加,这种加法运算就是全加,实现全加运算的电路叫做全加器。

如果用Ai 、Bi 分别表示A 、B 两个多位二进制数的第i 位,1i C -表示低位(第i-1位)来的进位,则根据全加运算的规则可列出真值表如表5-2。

表5-2 全加器的真值表利用卡诺图可求出Si 、Ci 的简化函数表达式:i i i i-1i i i i i i S =A B C C =(A B )C +A B ⊕⊕⊕可见,全加器可用两个异或门和一个与或门组成。

如果将数据表达式进行一些变换,半加器还可以用异或门、与非门等元器件组成多种形式的电路(见图5-2,图5-3)。

三、实验仪器及材料器件:74LS00 二输入端四与非门 3片74LA86 二输入端四异或门 1片74LS54 四组输入与或非门 1片四、预习要求1、预习组合逻辑电路的分析方法。