第七章 电容版图设计

- 格式:ppt

- 大小:5.25 MB

- 文档页数:50

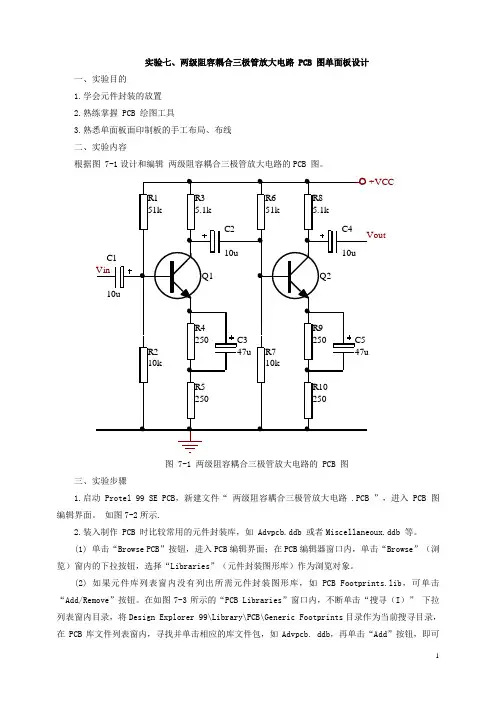

实验七、两级阻容耦合三极管放大电路 PCB 图单面板设计一、实验目的1.学会元件封装的放置2.熟练掌握 PCB 绘图工具3.熟悉单面板面印制板的手工布局、布线二、实验内容根据图 7-1设计和编辑两级阻容耦合三极管放大电路的PCB 图。

+VCC图 7-1 两级阻容耦合三极管放大电路的 PCB 图三、实验步骤1.启动 Protel 99 SE PCB,新建文件“ 两级阻容耦合三极管放大电路.PCB ”,进入 PCB 图编辑界面。

如图7-2所示.2.装入制作 PCB 时比较常用的元件封装库,如 Advpcb.ddb 或者Miscellaneoux.ddb 等。

(1) 单击“Browse PCB”按钮,进入PCB编辑界面;在PCB编辑器窗口内,单击“Browse”(浏览)窗内的下拉按钮,选择“Libraries”(元件封装图形库)作为浏览对象。

(2) 如果元件库列表窗内没有列出所需元件封装图形库,如PCB Footprints.lib,可单击“Add/Remove”按钮。

在如图7-3所示的“PCB Libraries”窗口内,不断单击“搜寻(I)” 下拉列表窗内目录,将Design Explorer 99\Library\PCB\Generic Footprints目录作为当前搜寻目录,在PCB库文件列表窗内,寻找并单击相应的库文件包,如Advpcb. ddb,再单击“Add”按钮,即可将指定图形库文件加入到元件封装图形库列表中,然后再单击“OK”按钮,退出如图7-3所示的“PCB Libraries”窗口。

图7-2 PCB编辑界面3.放置元件封装及其他一些实体,并设置元件属性、调整元件位置。

表 9 给出了该电路所需元件的封装形式、标号及所属元件库。

在PCB编辑器中,放置元件的操作过程如下:图7-3 PCB库文件列表窗(1) 单击“放置”工具栏内的“放置元件”工具,在如图7-4所示“Place Component”的窗口内,直接输入元件的封装形式、序号和注释信息。

和响应速度之间折衷考虑,相位裕度越大,系统越稳定,但是响应速度变慢。

这里取相位裕度为60度。

同样的,这两个环路参数是估计出来的,在实际电路中仍然需要多次考虑。

最后根据上面的两个环路参数,利用第二章第六节的公式2-22到2-24可以计算出低通滤波器的电阻和电容的值大约为:R2=12K,C2=138PF,CI=1IPF。

根据以上估算的参数可以将锁相环系统的幅频和相频特性曲线画出,如图4.2所示。

图4-2PLL的幅频与相频特性曲线4.3锁相环系统级模型4.3.1Matlab构造数学模型Mauab是MathWorks公司开发的具有强大科学运算功能的数学工具,其中的软件包--Simulink是专门用于数学建模的工具。

通过建立锁相环系统的线性模型,如图4—3所示,分别建立环路中每个模块的传输函数,然后设置输入输出点。

该线性模型不仅可以分析系统的冲击响应和阶跃响应,还可以分析零极点与波特图。

冲击响应和阶越响应的模拟结果如图4-4所示,此模型可以很方便的修改参数,仿真速度非常快,模拟结果也非常直观,对于理解二阶系统的特性非常有帮助。

t№啦*血瞻呻目删e,ra口aap蝌m鼬rtrartim'哥缸眦h恤啪蚓of恤VCO图4-3Matlab建立PLL的线性模型图4—4PLL的阶跃响应与冲击响应4.3.2VerilogA构造行为级模型VerilogA语言是Verilog硬件描述语言的扩展,主要用来描述模拟系统的结构和行为,包括电子,机械,流体力学和热力学系统等㈣。

下面给出VerilogA描述锁相环的行为级模型,并应用Mica进行仿真。

首先,以电阻的行为级模型为例,简单的说明一下VerilogA语言的特点和应用。

、include“disciplines.”’’include“constants.h,’moduleres(a,b);inouta,b;electricala,b;parameterrealR21.O:analogbeginI(a,b)<+V(a,b)/R;//Altemative:V(a,b)<+I(a,b)4R;第五章锁相环电路设计及模拟第五章锁相环电路设计及模拟5.1整体设计本章主要是关于锁相环的晶体管级电路的设计,不但详细的分析了电路的结构,而且给出了模拟结构及相关的解释。

MOSFET是现代数字集成电路的核心器件。

MOSFET剖面图•MOSFET与半导体表面及半导体-绝缘层界面性质密切相关。

•MOSFET的核心部分是MOS(MIS)结构。

2半导体表面以及半导体-绝缘层界面性质;表面电场效应(是MOSFEF工作的基础);MOS结构C-V特性。

4由于晶格周期性在表面处中断而出现的局(定)域于表面附近的电子态——表面态禁带中的电子态数等于表面原子数,表面原子面密度∼1015/cm 2,所以表面能级准连续地分布在禁带中。

总之,表面态起因于周期场在表面处中断;空间上定域于晶体表面;能级位于禁带中。

7.1.1 表面态§7.1 半导体表面和Si -SiO 2界面界面性质。

量级;离子。

界面态起源于界面处的。

界面态和表面态性质相似:位于Si-SiO101214151617达到最大且基本不变;19变化引起数量很大的2122V。

FB2324包括两部分:;V不很大s很小。

27对交流小信号ΔVQ n完全跟上ΔV g变化。

32scC-V是非平衡的瞬态特性333435若栅压V g 为一由V 1(积累)到V 2(强反型)的阶跃电压,则V =V 2下电容随时间的变化曲线称为MOS 电容的C -t 特性。

由MOS 电容的C -t 特性可求耗尽层少子寿命τ和表面复合速度S 。

,取“−”号,取“+”号i FB归一化平带电容与氧化层厚度及衬底掺杂浓度的关系。

贴片电容设计方法贴片电容是电子电路中常见的一种元件,用于存储和释放电能。

在设计贴片电容时,需要考虑许多因素,如尺寸、电容值、工作频率等。

以下是关于贴片电容设计方法的50条详细描述:1. 尺寸选择:要根据电路板的尺寸和电路设计的要求选择合适尺寸的贴片电容。

一般来说,尺寸可以从几毫米到几厘米不等。

2. 工作电压:根据电路的工作电压要求,选择贴片电容的额定工作电压,保证电容元件在工作时不会因电压过高而失效。

3. 电容值选择:根据电路的需求,选择合适的电容值。

可以通过相关公式计算得到,也可以根据经验进行选择。

4. 频率响应:考虑电路的工作频率范围,选择合适的贴片电容以保证其在整个频率范围内都能正常工作。

5. 负载能力:考虑电路中贴片电容的负载能力,尤其是在高频应用中,需要选择具有较高负载能力的贴片电容。

6. 温度特性:考虑贴片电容在不同温度下的特性表现,选择具有良好温度特性的元件以保证电路的稳定性。

7. 介质选择:根据电路环境和要求选择合适的介质材料,如陶瓷、聚合物等。

8. 焊接方式:考虑贴片电容的焊接方式,选择适合的焊接工艺,如表面贴装焊接(SMT)或插入式焊接。

9. 焊接温度曲线:确保在焊接过程中遵循贴片电容的温度曲线,控制好焊接温度和时间,避免因焊接过程导致元件损坏。

10. 电容降压:在大电压条件下,考虑电容的降压率,选择具有较低降压率的贴片电容。

11. 电磁干扰:在设计中考虑贴片电容的抑制电磁干扰的能力,以保证电路的稳定性和可靠性。

12. 电流承受能力:考虑电容的电流承受能力,选择能够满足电路需求的贴片电容。

13. 选择器件:根据上述要求,筛选出符合设计要求的贴片电容,可以参考厂家提供的参数和性能表。

14. 地线布线:布局设计时要注意贴片电容与地线之间的布线,尽量减小布线长度,提高抗干扰能力。

15. 避免共模干扰:在布线过程中,尽量将贴片电容与信号线相邻,并保持一定距离,避免共模干扰。

16. 避免温度过高:在布局设计时,避免将贴片电容安排在高温元件附近,以免影响其性能和寿命。

第7章集成电路版图设计• 版图是集成电路设计者将设计并模拟优化后的电路转化成的一系列几何图形,它包含了集成电路尺寸大小、各层拓扑定义等有关器件的所有物理信息。

• 集成电路制造厂家根据这些信息来制造掩膜。

根据复杂程度,不同工艺需要的一套掩膜可能有几到几十层。

一层掩膜对应一种工艺制造中的一道或数道工艺。

掩膜上的图形对应着芯片上器件或连接物理层的尺寸。

因此,版图上的几何尺寸与芯片上物理层尺寸直接相关。

• 由于器件的物理特性和工艺限制,芯片上物理层的尺寸对版图的设计有特定的规则,这些规则是集成电路制造厂家根据自己的工艺特点而制定的。

因此不同的工艺,就有不同的设计规则。

1• 版图设计准则:—匹配—抗干扰—寄生的优化—可靠性• 设计者只有得到了厂家提供的规则以后,才能开始设计。

严格遵守设计规则可以极大的避免由于短路、断路造成的电路失效、容差及寄生效应引起的性能恶化。

版图在设计的过程中要进行定期的检查,避免错误的积累而导致难以修改。

很多集成电路的设计软件都有设计版图的功能。

2集成电路版图设计与工具7.1 7.2工艺流程版图几何设计规则7.3 7.4 7.5 7.6 7.7版图图元版图设计准则电学设计规则与布线芯片的版图布局版图设计的注意事项37.1工艺流程版图中的工艺层通常是版图设计者定义工艺的抽象工艺层,它们并不一一对应于芯片制造时所需要的掩膜层。

芯片制造时所需要的掩膜层是由抽象工艺层给出的版图数据经过逻辑操作(“与”、“或”、“取反”)获得。

4沟道长/ m 金属布线层数多晶硅布线层数电源电压/v 阈值电压31级环形振荡器频率/MHz 0.3532 3.3W/LNMOS PMOS 196.170.6/0.40.54-0.773.6/0.40.58-0.76TSMC 的0.35μmCMOS 基本特征沟道尺寸和对应的电源电压、电路布局图中金属布线层及其性能参数MOSIS 对应TSMC 0.35 mCMOS 工艺定义的全部工艺层5上华0.6um DPDM CMOS 工艺拓扑设计N-wellactive P+ implantN+ implant poly1metal1contactviametal2poly2High Resistor• 芯片加工:从版图到裸片制加7.2版图几何设计规则版工是一种多层平面“印刷”和叠加过程,但中间是否会带来误差?6所设计的版图:7加工后得到的实际芯片集成电路的制造必然受到工艺技术水平的限制和器件物理参数的制约。

电容的模型、选型、容值计算与PCB布局布线1电容结构及模型1.1模型电容的基本公式是:式(1)显示,减小电容器极板之间的距离(d)和增加极板的截面积(A)将增加电容器的电容量。

1.2寄生参数与阻抗的频率特性电容通常存在等效串联电阻(ESR)和等效串联电感(ESL)二个寄生参数。

图2是电容器在不同工作频率下的阻抗(Zc)。

1.2.1降低去耦电容ESL的方法去耦电容的ESL是由于内部流动的电流引起的,使用多个去耦电容并联的方式可以降低电容的ESL影响,而且将两个去耦电容以相反走向放置在一起,从而使它们的内部电流引起的磁通量相互抵消,能进一步降低ESL。

(此方法适用于任何数目的去耦电容,注意不要侵犯DELL公司的专利)1.3不同电容的参数特性电解电容器一般都有很大的电容量和很大的等效串联电感。

由于它的谐振频率很低,对低频信号通过较好,而对高频信号,表现出较强的电感性,阻抗较大,所以只能使用在低频滤波上。

同时,大电容还可以起到局部电荷池的作用,可以减少局部干扰通过电源耦合出去。

钽电容器一般都有较大电容量和较小等效串联电感,因而它的谐振频率会高于电解电容器,并能使用在中高频滤波上。

瓷片电容器电容量和等效串联电感一般都很小,因而它的谐振频率远高于电解电容器和钽电容器,所以能使用在高频滤波和旁路电路上。

由于小电容量瓷片电容器的谐振频率会比大电容量瓷片电容器的谐振频率要高,因此,在选择旁路电容时不能光选用电容值过高的瓷片电容器。

1.4电容并联改善特性为了改善电容的高频特性,多个不同特性的电容器可以并联起来使用。

图 3 是多个不同特性的电容器并联后阻抗改善的效果。

1.4.1电容并联时注意封装在为每个电容选择封装类型时必须谨慎。

通常BOM表中会规定所有的无源元器件都要选用相同的尺寸,如都用0805电容。

图10为三只电容并联后的阻抗与频率关系。

由于每只电容采用相同的封装,故它们的高频响应相同。

实际上,这就抵消了更小电容的采用!相反,封装尺寸应该随同电容值一起微缩,见图11。