数字电子技术基础总复习要点

- 格式:doc

- 大小:38.00 KB

- 文档页数:3

数制和编码先介绍常见的十进制数,然后介绍二进制、十六进制,再介绍各进制数的相互转换,最后讲述十进制的二进制编码形式.一、十进制数:按照进位方式进行计数的制度称进位计数制.进位计数制中有两个基本要素:基数和权值.十进制数的基数是10(0~9),权值是10i(i是数字所处位置的序号)。

特点是逢10进1。

例:(567.8)10=5×102+6×101+7×100+8×10-1二、二进制数:计算机内部使用的数值符号只有两个:0和1。

外界的各种信息(数字、符号、图像)到了计算机内部都由0、1两个数字组成。

二进制数的基数是2,权值是2i,特点是逢2进1。

例:(101101。

1)2=1×25+0×24+1×23+1×22+0×21+1×20+1×2—1=32+8+4+1+0。

5=45.5三、十六进制数:二进制数的缺点是位数多,不易书写和记忆,为此我们常采取十六进制数。

十六进制数的基数是16(0~9,A~F),位权是16i。

特点是逢十六进一。

例:(2B.A)16=2×16+11×1+10/16=(43.625)104B7+84C=(D03)16四、数制转换:1.任意R进制数转换成十进制数:只需将其按权展开的多项式求和.例:(11011。

01)2=1×24+1×23+0×22+1×21+1×20+0×2—1+1×2—2=(27.25)10(FC)16=15×161+12×160=(252)102。

十进制数转换成二进制数:分为整数部分和小数部分。

整数部分采取“除基取余法”:将要转换的十进制整数除以2,取余数作为二进制整数的最低位K0,将商继续除以2,再取商的余数作为次低位K1,这样不断除,直到商为0,最后的余数作为二进制整数的最高位Kn。

1 数字电子技术基础知识1.1 学习要求(1)了解数字电路的特点以及数制和编码的概念。

(2)掌握逻辑代数的基本运算法则、基本公式、基本定理和化简方法。

(3)能够熟练地运用真值表、逻辑表达式、波形图和逻辑图表示逻辑函数,并会利用卡诺图化简逻辑函数。

1.2 学习指导本章重点:(1)逻辑函数各种表示方法之间的相互转换。

(2)逻辑函数的化简及变换。

本章难点:(1)逻辑函数各种表示方法之间的相互转换。

(2)逻辑函数的化简及变换。

本章考点:(1)逻辑函数各种表示方法之间的相互转换。

(2)逻辑函数的化简及变换。

1.2.1 数字电路概述1.数字信号与数字电路在数值上和时间上均连续的信号称为模拟信号,对模拟信号进行传输、处理的电子线路称为模拟电路。

在数值上和时间上均不连续的信号称为数字信号,对数字信号进行传输、处理的电子线路称为数字电路。

数字电路的特点:(1)输入和输出信号均为脉冲信号,一般高电平用1表示,低电平用0表示。

(2)电子元件工作在开关状态,即要么饱和,要么截止。

(3)研究的目标是输入与输出之间的逻辑关系,而不是大小和相位关系。

(4)研究的工具是逻辑代数和二进制计数法。

2.数制及其转换(1)数制基数和权:一种数制所具有的数码个数称为该数制的基数,该数制的数中不同位置上数码的单位数值称为该数制的位权或权。

十进制:基数为10,采用的10个数码为0~9,进位规则为“逢十进一”,从个位起各位的权分别为100、101、102、…10n -1。

二进制:基数为2,只有0和1两个数码,进位规则为“逢二进一”,从个位起各位的权分别为20、21、22、…2n -1。

16进制:基数为16,采用的16个数码为0~9、A~F ,进位规则为“逢十六进一”,从个位起各位的权分别为160、161、162、…16n -1。

(2)数制之间的转换其他进制转换为十进制:采用多项式求和法,即将其他进制的数根据基数和权展开为多项式,求出该多项式的和,即得相应的十进制数。

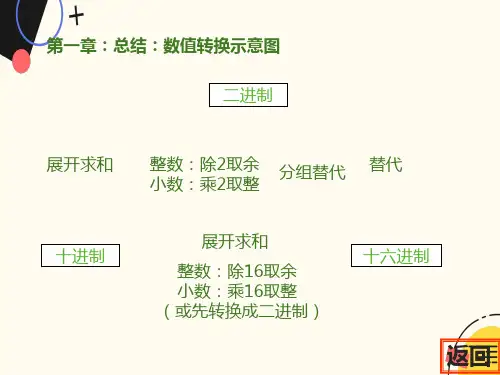

"数字电子技术"重要知识点汇总一、主要知识点总结和要求1.数制、编码其及转换:要求:能熟练在10进制、2进制、8进制、16进制、8421BCD、格雷码之间进展相互转换。

举例1:〔37.25〕10= ( )2= ( )16= ( )8421BCD解:〔37.25〕10= ( 100101.01 )2= ( 25.4 )16= ( 00110111.00100101 )8421BCD 2.逻辑门电路:(1)根本概念1〕数字电路中晶体管作为开关使用时,是指它的工作状态处于饱和状态和截止状态。

2〕TTL门电路典型高电平为3.6 V,典型低电平为0.3 V。

3〕OC门和OD门具有线与功能。

4〕三态门电路的特点、逻辑功能和应用。

高阻态、高电平、低电平。

5〕门电路参数:噪声容限V NH或V NL、扇出系数N o、平均传输时间t pd。

要求:掌握八种逻辑门电路的逻辑功能;掌握OC门和OD门,三态门电路的逻辑功能;能根据输入信号画出各种逻辑门电路的输出波形。

举例2:画出以下电路的输出波形。

解:由逻辑图写出表达式为:C+==,则输出Y见上。

+Y+AABBC3.根本逻辑运算的特点:与运算:见零为零,全1为1;或运算:见1为1,全零为零;与非运算:见零为1,全1为零;或非运算:见1为零,全零为1;异或运算:相异为1,一样为零;同或运算:一样为1,相异为零;非运算:零变 1, 1 变零;要求:熟练应用上述逻辑运算。

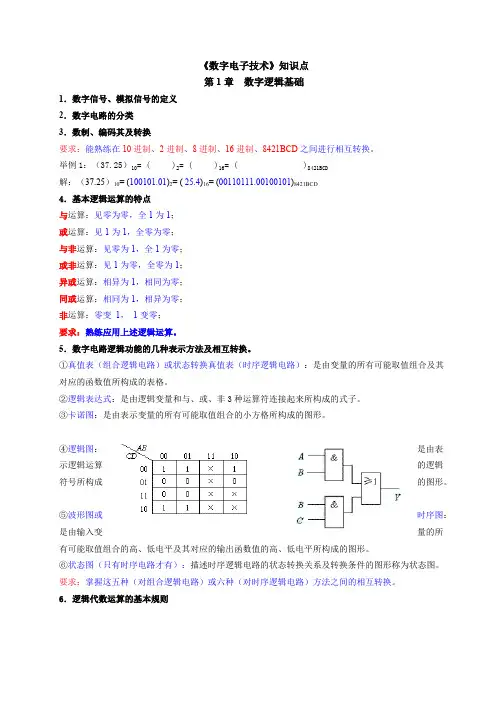

4. 数字电路逻辑功能的几种表示方法及相互转换。

①真值表〔组合逻辑电路〕或状态转换真值表〔时序逻辑电路〕:是由变量的所有可能取值组合及其对应的函数值所构成的表格。

②逻辑表达式:是由逻辑变量和与、或、非3种运算符连接起来所构成的式子。

③卡诺图:是由表示变量的所有可能取值组合的小方格所构成的图形。

④逻辑图:是由表示逻辑运算的逻辑符号所构成的图形。

⑤波形图或时序图:是由输入变量的所有可能取值组合的高、低电平及其对应的输出函数值的高、低电平所构成的图形。

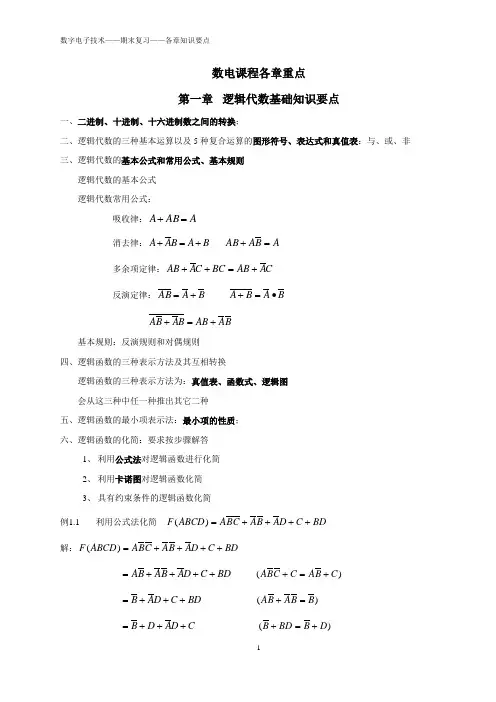

数电课程各章重点 第一章 逻辑代数基础知识要点一、二进制、十进制、十六进制数之间的转换;二、逻辑代数的三种基本运算以及5种复合运算的图形符号、表达式和真值表:与、或、非 三、逻辑代数的基本公式和常用公式、基本规则逻辑代数的基本公式 逻辑代数常用公式:吸收律:A AB A =+消去律:B A B A A +=+ A B A AB =+ 多余项定律:C A AB BC C A AB +=++ 反演定律:B A AB += B A B A •=+ B A AB B A B A +=+ 基本规则:反演规则和对偶规则 四、逻辑函数的三种表示方法及其互相转换逻辑函数的三种表示方法为:真值表、函数式、逻辑图 会从这三种中任一种推出其它二种五、逻辑函数的最小项表示法:最小项的性质; 六、逻辑函数的化简:要求按步骤解答1、 利用公式法对逻辑函数进行化简2、 利用卡诺图对逻辑函数化简3、 具有约束条件的逻辑函数化简 例1.1利用公式法化简 BD C D A B A C B A ABCD F ++++=)(解:BD C D A B A C B A ABCD F ++++=)(BD C D A B A B A ++++= )(C B A C C B A +=+ BD C D A B +++= )(B B A B A =+ C D A D B +++= )(D B BD B +=+C D B ++= )(D D A D =+ 例1.2 利用卡诺图化简逻辑函数 ∑=)107653()(、、、、m ABCD Y 约束条件为∑8)4210(、、、、m 解:函数Y 的卡诺图如下:00 01 11 1000011110AB CD111×11××××D B A Y +=第二章 门电路知识要点一、三极管开、关状态1、饱和、截止条件:截止:T be V V <, 饱和:βCSBS B I I i =>2、反相器饱和、截止判断 二、基本门电路及其逻辑符号与门、或非门、非门、与非门、OC 门、三态门、异或; 传输门、OC/OD 门及三态门的应用 三、门电路的外特性1、输入端电阻特性:对TTL 门电路而言,输入端通过电阻接地或低电平时,由于输入电流流过该电阻,会在电阻上产生压降,当电阻大于开门电阻时,相当于逻辑高电平。

数制和编码先介绍常见的十进制数,然后介绍二进制、十六进制,再介绍各进制数的相互转换,最后讲述十进制的二进制编码形式。

一、十进制数:按照进位方式进行计数的制度称进位计数制。

进位计数制中有两个基本要素:基数和权值。

十进制数的基数是10(0~9),权值是10i(i是数字所处位置的序号)。

特点是逢10进1。

例:(567.8)10=5×102+6×101+7×100+8×10-1二、二进制数:计算机内部使用的数值符号只有两个:0和1。

外界的各种信息(数字、符号、图像)到了计算机内部都由0、1两个数字组成。

二进制数的基数是2,权值是2i,特点是逢2进1。

例:(101101.1)2=1×25+0×24+1×23+1×22+0×21+1×20+1×2-1=32+8+4+1+0.5=45.5三、十六进制数:二进制数的缺点是位数多,不易书写和记忆,为此我们常采取十六进制数.十六进制数的基数是16(0~9,A~F),位权是16i。

特点是逢十六进一。

页脚内容1例:(2B.A)16=2×16+11×1+10/16=(43.625)104B7+84C=(D03)16四、数制转换:1.任意R进制数转换成十进制数:只需将其按权展开的多项式求和。

例:(11011.01)2=1×24+1×23+0×22+1×21+1×20+0×2-1+1×2-2=(27.25)10(FC)16=15×161+12×160=(252)102.十进制数转换成二进制数:分为整数部分和小数部分。

整数部分采取“除基取余法”:将要转换的十进制整数除以2,取余数作为二进制整数的最低位K0,将商继续除以2,再取商的余数作为次低位K1,这样不断除,直到商为0,最后的余数作为二进制整数的最高位Kn。

《数字电子技术》知识点第1章 数字逻辑基础1.数字信号、模拟信号的定义2.数字电路的分类3.数制、编码其及转换要求:能熟练在10进制、2进制、8进制、16进制、8421BCD 之间进行相互转换。

举例1:(37.25)10= ( )2= ( )16= ( )8421BCD 解:(37.25)10= (100101.01)2= ( 25.4)16= (00110111.00100101)8421BCD 4.基本逻辑运算的特点与运算:见零为零,全1为1;或运算:见1为1,全零为零;与非运算:见零为1,全1为零;或非运算:见1为零,全零为1;异或运算:相异为1,相同为零;同或运算:相同为1,相异为零;非运算:零变 1, 1变零;要求:熟练应用上述逻辑运算。

5.数字电路逻辑功能的几种表示方法及相互转换。

①真值表(组合逻辑电路)或状态转换真值表(时序逻辑电路):是由变量的所有可能取值组合及其对应的函数值所构成的表格。

②逻辑表达式:是由逻辑变量和与、或、非3种运算符连接起来所构成的式子。

③卡诺图:是由表示变量的所有可能取值组合的小方格所构成的图形。

④逻辑图:是由表示逻辑运算的逻辑符号所构成的图形。

⑤波形图或时序图:是由输入变量的所有可能取值组合的高、低电平及其对应的输出函数值的高、低电平所构成的图形。

⑥状态图(只有时序电路才有):描述时序逻辑电路的状态转换关系及转换条件的图形称为状态图。

要求:掌握这五种(对组合逻辑电路)或六种(对时序逻辑电路)方法之间的相互转换。

6.逻辑代数运算的基本规则①反演规则:对于任何一个逻辑表达式Y ,如果将表达式中的所有“·”换成“+”,“+”换成“·”,“0”换成“1”,“1”换成“0”,原变量换成反变量,反变量换成原变量,那么所得到的表达式就是函数Y 的反函数Y (或称补函数)。

这个规则称为反演规则。

②对偶规则:对于任何一个逻辑表达式Y ,如果将表达式中的所有“·”换成“+”,“+”换成“·”,“0”换成“1”,“1”换成“0”,而变量保持不变,则可得到的一个新的函数表达式Y ',Y '称为函Y 的对偶函数。

数字电子技术基础总复习要点一、填空题第一章1、变化规律在时间上与数量上都就是离散就是信号称为数字信号。

2、变化规律在时间或数值上就是连续的信号称为模拟信号。

3、不同数制间的转换。

4、反码、补码的运算。

5、8421码中每一位的权就是固定不变的,它属于恒权代码。

6、格雷码的最大优点就在于它相邻两个代码之间只有一位发生变化。

第二章1、逻辑代数的基本运算有与、或、非三种。

2、只有决定事物结果的全部条件同时具备时,结果才发生。

这种因果关系称为逻辑与,或称逻辑相乘。

3、在决定事物结果的诸条件中只要有任何一个满足,结果就会发生。

这种因果关系称为逻辑或,也称逻辑相加。

4、只要条件具备了,结果便不会发生;而条件不具备时,结果一定发生。

这种因果关系称为逻辑非,也称逻辑求反。

5、逻辑代数的基本运算有重叠律、互补律、结合律、分配律、反演律、还原律等。

举例说明。

6、对偶表达式的书写。

7、逻辑该函数的表示方法有:真值表、逻辑函数式、逻辑图、波形图、卡诺图、硬件描述语言等。

8、在n变量逻辑函数中,若m为包含n个因子的乘积项,而且这n个变量均以原变量或反变量的形式在m中出现一次,则称m为该组变量的最小项。

9、 n变量的最小项应有2n个。

10、最小项的重要性质有:①在输入变量的任何取值下必有一个最小项,而且仅有一个最小项的值为1;②全体最小项之与为1;③任意两个最小项的乘积为0;④具有相邻性的两个最小项之与可以合并成一项并消去一对因子。

11、若两个最小项只有一个因子不同,则称这两个最小项具有相邻性。

12、逻辑函数形式之间的变换。

(与或式—与非式—或非式--与或非式等)13、化简逻辑函数常用的方法有:公式化简法、卡诺图化简法、Q-M法等。

14、公式化简法经常使用的方法有:并项法、吸收法、消项法、消因子法、配项法等。

15、卡诺图化简法的步骤有:①将函数化为最小项之与的形式;②画出表示该逻辑函数的卡诺图;③找出可以合并的最小项;④选取化简后的乘积项。

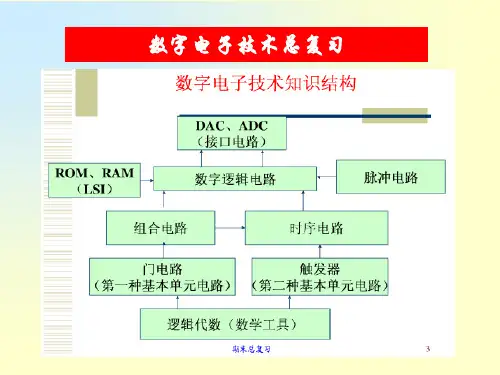

数电知识点总结(整理版).doc数电知识点总结(整理版)一、引言数字电子技术是电子工程领域的一个重要分支,它涉及使用数字信号处理电子设备中的信息。

本文档旨在总结数字电子学的核心知识点,以帮助学生和专业人士复习和掌握这一领域的基础。

二、数字逻辑基础数字信号数字信号是离散的,可以是二进制(0和1)或多电平信号。

逻辑门基本的逻辑门包括与门(AND)、或门(OR)、非门(NOT)、异或门(XOR)和同或门(NAND)。

逻辑运算逻辑运算是数字电路中的基本操作,包括布尔代数和逻辑表达式的简化。

三、组合逻辑电路多输入逻辑门如四输入与门、或门,以及更复杂的逻辑功能。

编码器和解码器编码器将输入信号转换为二进制代码,解码器则相反。

加法器用于执行二进制加法运算的电路。

比较器比较两个二进制数的大小。

四、时序逻辑电路触发器基本的存储单元,可以存储一位二进制信息。

寄存器由多个触发器组成的电路,用于存储多位二进制信息。

计数器用于计数事件的时序电路。

移位寄存器可以按顺序移动存储的数据。

五、存储器RAM(随机存取存储器)可以读写的数据存储器。

ROM(只读存储器)存储固定数据的存储器,内容在制造时写入。

PROM(可编程ROM)用户可以编程的只读存储器。

EEPROM(电可擦可编程ROM)可以通过电信号擦除和重新编程的存储器。

六、数字系统设计设计流程包括需求分析、逻辑设计、电路设计、仿真、实现和测试。

硬件描述语言如VHDL和Verilog,用于设计和模拟数字电路。

仿真工具用于在实际硬件实现之前测试电路设计的工具。

七、数字信号处理采样将模拟信号转换为数字信号的过程。

量化将连续的信号值转换为有限数量的离散值。

编码将采样和量化后的信号转换为数字代码。

八、数模转换和模数转换数模转换器(DAC)将数字信号转换为模拟信号的设备。

模数转换器(ADC)将模拟信号转换为数字信号的设备。

九、数字通信基础调制在发送端,将数字信号转换为适合传输的形式。

解调在接收端,将接收到的信号转换回原始的数字信号。

数字电子技术基础总复习要点

一、填空题

第一章

1、变化规律在时间上和数量上都是离散是信号称为数字信号。

2、变化规律在时间或数值上是连续的信号称为模拟信号。

3、不同数制间的转换。

4、反码、补码的运算。

5、8421码中每一位的权是固定不变的,它属于恒权代码。

6、格雷码的最大优点就在于它相邻两个代码之间只有一位发生变化。

第二章

1、逻辑代数的基本运算有与、或、非三种。

2、只有决定事物结果的全部条件同时具备时,结果才发生。

这种因果关系称

为逻辑与,或称逻辑相乘。

3、在决定事物结果的诸条件中只要有任何一个满足,结果就会发生。

这种因

果关系称为逻辑或,也称逻辑相加。

4、只要条件具备了,结果便不会发生;而条件不具备时,结果一定发生。

这

种因果关系称为逻辑非,也称逻辑求反。

5、逻辑代数的基本运算有重叠律、互补律、结合律、分配律、反演律、还原

律等。

举例说明。

6、对偶表达式的书写。

7、逻辑该函数的表示方法有:真值表、逻辑函数式、逻辑图、波形图、卡诺

图、硬件描述语言等。

8、在n变量逻辑函数中,若m为包含n个因子的乘积项,而且这n个变量均

以原变量或反变量的形式在m中出现一次,则称m为该组变量的最小项。

9、n变量的最小项应有2n个。

10、最小项的重要性质有:①在输入变量的任何取值下必有一个最小项,而且

仅有一个最小项的值为1;②全体最小项之和为1;③任意两个最小项的乘积为0;④具有相邻性的两个最小项之和可以合并成一项并消去一对因子。

11、若两个最小项只有一个因子不同,则称这两个最小项具有相邻性。

12、逻辑函数形式之间的变换。

(与或式—与非式—或非式--与或非式等)

13、化简逻辑函数常用的方法有:公式化简法、卡诺图化简法、Q-M法等。

14、公式化简法经常使用的方法有:并项法、吸收法、消项法、消因子法、配

项法等。

15、卡诺图化简法的步骤有:①将函数化为最小项之和的形式;②画出表示该

逻辑函数的卡诺图;③找出可以合并的最小项;④选取化简后的乘积项。

16、卡诺图法化简逻辑函数选取化简后的乘积项的选取原则是:①乘积项应包

含函数式中所有的最小项;②所用的乘积项数目最少;③每个乘积项包含的因子最少。

第三章

1、用以实现基本逻辑运算和复合逻辑运算的单元电路称为门电路。

2、CMOS电路在使用时应注意以下几点:①输入电路要采用静电防护;②输

入电路要采取过流保护;③电路锁定效应的防护。

3、COMS电路的静电防护应注意以下几点:①采用金属屏蔽层包装;②无静

电操作;③不用的输入端不能悬空。

4、CMOS电路的输入电路过流保护措施有:①信号源内阻太低时,在输入端

与信号源之间串接保护电阻;②输入端接有大电容时,在输入端与电容之间接入保护电阻;③输入端接长线时,在门电路的输入端接入保护电阻。

5、目前,应用最广泛的集成门电路有CMOS和TTL两大类。

6、集成门电路的外特性包含两个内容:①逻辑功能,即输入输出之间的逻辑

关系;②外部的电气特性,包括电压传输特性、输入特性、输出特性和动态特性等。

第四章

1、根据逻辑功能的不同特点,可以将数字电路分成两大类,一类称为组合逻

辑电路,另一类称为时序逻辑电路。

2、组合逻辑电路在逻辑功能上的共同特点是:任意时刻的输出仅仅取决于该

时刻的输入,与电路原来的状态无关。

3、组合逻辑电路在电路结构上的特点是:只包含门电路,而没有存储(记忆)

单元。

4、组合逻辑电路的分析步骤为:①根据逻辑图,逐级写出输入输入关系的逻

辑函数表达式;②利用公式法或卡诺图法化简逻辑函数;③将逻辑函数式转换为真值表的形式;④判明逻辑电路的逻辑功能。

5、设计组合逻辑电路,就是根据给定的实际逻辑问题,求出实现这一逻辑功

能的最简逻辑电路。

所谓最简就是指:电路所用的器件数最少、器件的种类最少、而且器件间的连线也最少。

6、组合逻辑电路的设计步骤为:①进行逻辑抽象,列真值表;②将真值表转

换为逻辑函数表达式,并加以化简;③选定器件类型;④将逻辑函数变换为适当的形式;⑤画逻辑电路图;⑥工艺设计。

7、常用的组合逻辑电路包括编码器、译码器、数据选择器、数值比较器、加

法器、函数发生器、奇偶校验器、奇偶发生器等

8、门电路的两个输入信号同时向相反的逻辑电平跳变的现象称为竞争。

有竞

争现象时不一定都会产生尖峰脉冲。

9、由于竞争而在电路输出端可能产生尖峰脉冲的现象就称为竞争-冒险。

10、消除竞争-冒险现象的方法有:接入滤波电容、引入选通脉冲、修改逻辑

设计。

第五章

1、能够存储1位二值信号的基本单元电路统称为触发器。

2、触发器必须具备以下两个基本特点:①具有两个能自行保持的稳定状态;

②在触发信号的操作下,根据不同的输入信号可以置1或0状态。

3、由于电路结构形式的不同,触发信号的触发方式分为:电平触发、脉冲触

发、边沿触发三种。

4、根据触发器逻辑功能的不同,触发器分为:SR触发器、JK触发器、D触

发器、T触发器等。

5、电平触发方式的特点是:①只有当CLK变为有效电平时,触发器才能接受

输入信号,并按照输入信号将触发器的输出置成相应的状态;②在CLK=1的全部时间里,S和R状态的变化都可能引起输出状态的改变。

6、脉冲触发方式的特点是:①触发器的翻转分两步动作。

第一步,在CLK=1

期间主触发器接收输入信号,从触发器不动;第二步,CLK边沿到来时从

触发器按照主触发器的状态翻转;②在CLK=1的全部时间里输入信号都将对主触发器起控制作用。

7、SR触发器的特性表为:(00维持、01置0、10置1、11不定)。

8、SR触发器的特性方程为:Q*=S+R’Q,SR=0

9、SR触发器的状态转换图为:

10、JK触发器的特性表为:(00维持、01置0、10置1、11翻转)。

11、JK触发器的特性方程为:Q*=JQ’+K’Q。

12、JK触发器的状态转换图为:

13、T触发器的特性表为:(0维持、1翻转)。

14、T触发器的特性方程为:Q*=TQ’+T’Q。

15、T触发器的状态转换图为:

16、D触发器的特性表为:(0置0、1置1)。

17、D触发器的特性方程为:Q*=D。

18、D触发器的状态转换图为:

第六章①②③④⑤⑥

1、任一时刻的输出信号不仅取决于当时的输入信号,而且还取决于电路原来

的状态。

具备这种逻辑功能特点的电路称为时序逻辑电路。

2、时序电路在电路结构上有两个显著的特点:第一,时序电路通常包含组合

电路和存储电路两个组成部分,而存储电路是必不可少的;第二,存储电路的输出状态必须反馈到组合电路的输入端,与输入信号一起,共同决定组合逻辑电路的输出。

3、时序电路中有分同步时序电路和异步时序电路。

在同步时序电路中,所有

触发器状态的变化都是在同一时钟信号操作下同时发生的。

而在异步时序电路中,触发器状态的变化不是同时发生的。

4、时序电路的逻辑功能可以用输出方程、驱动方程和状态方程全面描述。

5、分析同步时序电路一般按如下步骤进行:①从给定的逻辑图中写出每个触

发器的驱动方程;②将得到的这些驱动方程代入相应触发器的特性方程,得出每个触发器的状态方程,从而得到,由这些状态方程组成的整个时序电路的状态方程组;③根据逻辑图写出电路的输出方程。

二、综合题(类型)

1、逻辑函数的恒等式证明

2、用卡诺图化简逻辑函数。

3、逻辑图、输出函数表达式、波形图、卡诺图、真值表之间的互换。

4、组合逻辑电路的分析。

(也可以是其中某1-2个步骤)

5、组合逻辑电路的设计。

(也可以是其中某1-2个步骤)

6、8-3线编码器的扩展。

(p.171例题4.3.1)

7、3-8线译码器的扩展。

(p.177例题4.3.2)

8、用3-8译码器和门电路产生多输出逻辑函数(p.212习题4.12)

9、根据输入信号波形图和CLK波形图,画触发器输入波形图。

(习题5.8、

5.9、5.11、5.16、5.26等)

10、时序逻辑电路的状态转换表与状态转换图的互换。

11、时序逻辑电路的分析。

(p.346习题6.2、6.3、6.5、6.12、6.17)。