第三章 C6000流水线3

- 格式:pdf

- 大小:611.44 KB

- 文档页数:10

2-1 2012.1主讲教师:任海鹏1. 8088CPU结构和240DSP流水线 2. C6000系列DSP的CPU结构 3. C6000系列DSP的公共指令集 4. C6713浮点运算指令 5. C6000系列DSP的流水线操作 6. 中断结构和中断响应《DSP原理及应用》 2 任海鹏8088CPU结构Execution Unit and Bus Interface Unit《DSP原理及应用》3任海鹏8088CPU结构8088CPU由两个部分构成。

Execution Unit包括ALU,它负责指令的执行。

Bus Interface Unit负责与存储器和I/O的接口。

两部分操作各自独立进行。

《DSP原理及应用》4任海鹏8088CPU结构与一般8位 微处理器相比, 指令队列缓冲器 是8088设计上的 独特之处。

zCPU的工作 1、取指令 2、取数据 3、计算 4、存数据5 任海鹏《DSP原理及应用》8088CPU结构一般8位微处理器指令执行过程。

取指 执行 取指 执行 … 取指有了指令队列缓冲器8088可以这样执行指令。

取指 执行 取指 执行 取指 执行这样执行提高了 总线的利用效率。

只要指令不要求进行存储器或I/O访问,BIU就可以 读入指令,直到指令队列满。

《DSP原理及应用》 6 任海鹏8088CPU结构由8088微机原理我们可以得到关于微处理器的以 下基本概念:}微处理器通过中央算术逻辑单元进行数据计算; }可以通过一系列程序(指令)控制CPU完成一个完整功能; }微处理器计算过程中需要从程序存储器读程序,以便知道下一步的操作; }执行一个指令的操作时可能需要从数据存储器读入操作源数 据; }指令执行的结果可能要存入数据存储器; }程序和数据的读取以及数据的存储都要用BIU;《DSP原理及应用》 7 任海鹏240 DSP流水线《DSP原理及应用》8任海鹏240 DSP流水线z总线结构和接口方式}总线结构是计算机体系结构中的基本结构——传送数据和地址的通道; }总线结构提供了一种标准的接口方式——所有满足标准 的设备都可以挂接; }总线的传输方向是双向的,使用时要避免冲突——采用 时序控制; }总线的性能可以从响应速度,位宽,负载能力等几个方 面来衡量;《DSP原理及应用》9任海鹏240 DSP流水线z总线时序1、总线的时序一般分为四个独立的阶段: instruction-fetch, instruction-decode, operand-fe tch, and instruction execute. 2、单一地址总线和单一数据总线结构:在任意一个时钟 周期内只能有一条指令被执行; 3、提高处理速度:1)提高主频;2)加宽数据位宽; 3)采用多总线;《DSP原理及应用》10任海鹏240 DSP流水线z240DSP的内部总线结构(Enhanced Harvard Architecture)}PAB(Program Address Bus)为程序存储器的读、写提供地址}DRAB(Data-Read Address Bus)为读数据存储器的操作提供地址}DWAB(Data-Write Address Bus)为向数据存储器写的操作提供地址240 DSP流水线z DSP的内部总线结构(Enhanced Harvard Architecture)}PRDB(Program Read Bus)从程序存储器向CPU传送指令、立即数和表信息}DRDB(Data-Read Bus)从数据存储器向中央算术逻辑单元、辅助寄存器算术单元传送数据}DWEB(Data-Write Bus)向程序存储器和数据存储器传送数据240 DSP流水线DSP总线结构图240 DSP流水线z 流水线操作}指令的流水线处理由一系列发生在一条指令执行过程中的总线操作组成}4个独立的阶段:取指(instruction-fetch)、译码(in struction-decode)、取操作数(operand-fetch)和执行指令(instruction execute)各阶段使用不同的}指令执行不同阶段的总线操作取指——程序地址总线,程序读数据总线;资源互不冲突,可以并行!!译码——在CPU译码电路内完成不需要总线操作;取操作数——数据读地址总线,数据读数据总线;执行——算术逻辑单元,数据写地址和数据写数据总线。

读书破万卷下笔如有神一、TI公司DSP分类及代表产品简介TI的DSP经过完善的测试出厂时,都是以TMS320为前缀。

在众多款型DSP中,TI把市场销量好和前景看好的DSP归为三大系列而大力推广,TI也称之为三个平台。

TMS320C6000平台,包含定点C62x和C64x以及浮点C67x。

其追求的是至高性能,最近新推出的芯片速度高达1GHZ,适合宽带网络、图像、影像、雷达等处理应用。

TMS320C5000 平台,包含代码兼容的定点C54x和C55x。

其提供性能、外围设备、小型封装和电源效率的优化组合,适合便携式上网、语音处理及对功耗有严格要求的地方。

DSP的传统设计往往是采取主从式结构:在一块电路板上,DSP做从机,负责数字信号处理运算;外加一块嵌入式微处理器做主机,来完成输入、控制、显示等其他功能。

为此,TI专门推出了一款双核处理器OMAP,包含有一个ARM和一个C5000系列DSP,OMAP处理器把主从式设计在芯片级上合二为一,一个典型的应用实例为诺基亚手机。

TMS320C2000 平台,包含16位C24xx和32位C28xx的定点DSP。

C24xx系列市场销量很好,而对C28xx系列,TI认为很有市场潜力而大力推广。

C2000针对控制领域做了优化配置,集成了了众多的外设,适合逆变器、马达、机器人、数控机床、电力等应用领域。

另外,OMAP 系列:OMAP 处理器集成ARM 的命令及控制功能,另外还提供DSP 的低功耗,实时信号处理能力,最适合移动上网设备和多媒体家电。

其他系列的DSP 曾经有过风光,但现在都非TI 主推产品了,除了C3X 系列外,其他基本处于淘汰阶段,如:C3X 的浮点系列:C30,C31,C32 C2X 和C5X 系列:C20,C25,C50, 每个系列的DSP 都有其主要应用领域。

二、简述实时信号处理的含义。

要求在限定的时间内将采集的数据在现场处理完成并得到一定的结果,即信号处理的时间要小于或者等于下一批数据输入时间,有时甚至要求在特定的时间、地点来完成信号处理。

C6000系列DSP体系结构介绍C6000 体系结构和汇编语言远见品质General DSP System Block DiagramInternal MemoryInternal BusesExternal MemoryCentral Processing UnitP E R I P H E R A L S远见品质C6000 CPU ArchitectureVLIW, Very Long Instruction word远见品质C6201/04/05 片内存储器远见品质C6701片内存储器远见品质C64x 片内2级存储器C64的 L1D的存储体结构:8×32bit 。

(32B) L1D行:64B。

共128组(4K字)远见品质程序员角度的DSP结构:存储器的层次片外存储器片内存储器数据寄存器处理单元远见品质C62xx CPU Core远见品质C67xx CPU Core远见品质C64xx CPU Core远见品质u u u u u u u u u u u u u一条C6000的指令和其机器码C6000: ADD .D2 B5,B4,B4 ADD (.D2 or.D1) src2,src1,dst1 00000010000101001000100001000010 000 0 00100 00101 00100 010000 10000 1 0 (1) (2) (3) (4) (5) (6)(7)(8)(9)(1) 条件寄存器: A1,A2,B0~2; C64添加A0 (2) z,指定条件寄存器的判断条件 (3) dst,目的 (4) src2,源2 (5) src1, 源1 (6) 操作码:设定唯一指令的码,sint,2个源和目标都为有符号整数且功能单元为D时的操作码就是010000 ; (7) 固定值 (8) s,选择A边寄存器还是B边寄存器 (9) p,是否并行远见品质对比:8086的ADD指令8086/8088 一条指令长1~6字节 8086 ADD CX,DX CX和DX相加放到CX 000000 0 1 11 001 010;寻址方式和立即数,这里没有ADD (1) (2) (3) (4)(5)(1)0 reg为目的,(2)1 字处理(8086的字为16bit), 表示操作的是CX,DX不是 CL,DL。

2-2 2013.1主讲教师:任海鹏1. 8088CPU结构和240DSP流水线 2. C6000系列DSP的CPU结构 3. C6000系列DSP的指令基础 4. C6000系列DSP的流水线操作 5. 中断结构和中断响应《DSP原理及应用》2任海鹏z概述 z寻址方式和数据访问指令 zSOP操作举例《DSP原理及应用》3任海鹏SOP操作举例zSOP的实现SOP是许多DSP算法的关键 组件。

这里写出SOP算法, 来学习C6000的程序的基本 结构。

Y = ∑ an * xnn = 1N= a1 * x1 + a2 * x2 +... + aN * xN此算法需要两个基本操作: : 1)乘 2)加 因此,需要2个基本指令。

《DSP原理及应用》4任海鹏SOP操作举例zSOP的实现乘法的实现Y = ∑ an * xnn = 1N= a1 * x1 + a2 * x2 +... + aN * xNa1乘x1用如下汇编语言 指令实现: 该指令由称为“.M”的乘法 器单元执行。

《DSP原理及应用》5任海鹏zSOP的实现Y = ∑ an * xn40注意: 16位×16位产生32位积; 32位×32位产生64位积;n = 1= a1 * x1 + a2 * x2 +... + aN * xN由.M单元硬件完成乘法操作:《DSP原理及应用》6任海鹏zSOP的实现Y = ∑ an * xnn = 140.M= a1 * x1 + a2 * x2 +... + aN * xN由.M单元硬件完成乘法 操作:《DSP原理及应用》7任海鹏zSOP的实现Y = ∑ an * xnn = 140.M .?= a1 * x1 + a2 * x2 +... + aN * xN由.L单元硬件完成加法 操作:《DSP原理及应用》8任海鹏zSOP的实现Y = ∑ an * xnn = 140.M .L像 C6000 这 样 的 RISC 处 理器使用寄存器保持操作数。

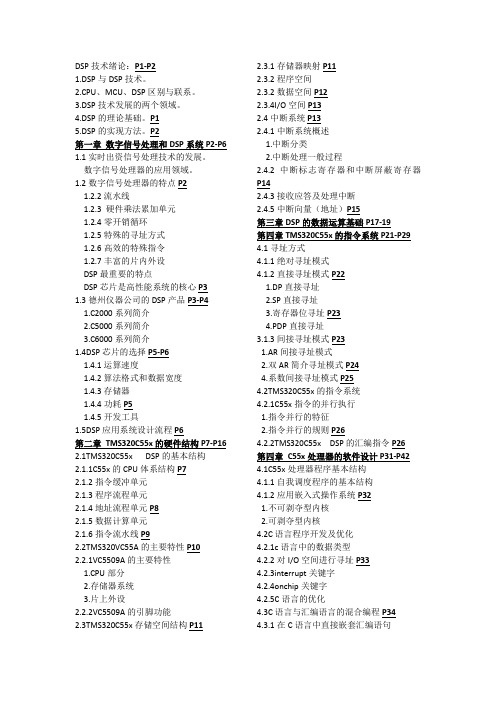

DSP技术绪论:P1-P21.DSP与DSP技术。

2.CPU、MCU、DSP区别与联系。

3.DSP技术发展的两个领域。

4.DSP的理论基础。

P15.DSP的实现方法。

P2第一章数字信号处理和DSP系统P2-P6 1.1实时出资信号处理技术的发展。

数字信号处理器的应用领域。

1.2数字信号处理器的特点P21.2.2流水线1.2.3 硬件乘法累加单元1.2.4零开销循环1.2.5特殊的寻址方式1.2.6高效的特殊指令1.2.7丰富的片内外设DSP最重要的特点DSP芯片是高性能系统的核心P31.3德州仪器公司的DSP产品P3-P41.C2000系列简介2.C5000系列简介3.C6000系列简介1.4DSP芯片的选择P5-P61.4.1运算速度1.4.2算法格式和数据宽度1.4.3存储器1.4.4功耗P51.4.5开发工具1.5DSP应用系统设计流程P6第二章TMS320C55x的硬件结构P7-P16 2.1TMS320C55x DSP的基本结构2.1.1C55x的CPU体系结构P72.1.2指令缓冲单元2.1.3程序流程单元2.1.4地址流程单元P82.1.5数据计算单元2.1.6指令流水线P92.2TMS320VC55A的主要特性P102.2.1VC5509A的主要特性1.CPU部分2.存储器系统3.片上外设2.2.2VC5509A的引脚功能2.3TMS320C55x存储空间结构P11 2.3.1存储器映射P112.3.2程序空间2.3.2数据空间P122.3.4I/O空间P132.4中断系统P132.4.1中断系统概述1.中断分类2.中断处理一般过程2.4.2中断标志寄存器和中断屏蔽寄存器P142.4.3接收应答及处理中断2.4.5中断向量(地址)P15第三章DSP的数据运算基础P17-19第四章TMS320C55x的指令系统P21-P29 4.1寻址方式4.1.1绝对寻址模式4.1.2直接寻址模式P221.DP直接寻址2.SP直接寻址3.寄存器位寻址P234.PDP直接寻址3.1.3间接寻址模式P231.AR间接寻址模式2.双AR简介寻址模式P244.系数间接寻址模式P254.2TMS320C55x的指令系统4.2.1C55x指令的并行执行1.指令并行的特征2.指令并行的规则P264.2.2TMS320C55x DSP的汇编指令P26第四章C55x处理器的软件设计P31-P42 4.1C55x处理器程序基本结构4.1.1自我调度程序的基本结构4.1.2应用嵌入式操作系统P321.不可剥夺型内核2.可剥夺型内核4.2C语言程序开发及优化4.2.1c语言中的数据类型4.2.2对I/O空间进行寻址P334.2.3interrupt关键字4.2.4onchip关键字4.2.5C语言的优化4.3C语言与汇编语言的混合编程P344.3.1在C语言中直接嵌套汇编语句4.3.2C语言调用汇编模块的接口1.C/C++中的寄存器规则2.函数调用规则P353.被调用函数的响应4.C/C++与汇编语言的接口P364.4公共目标文件格式——COFF4.4.1COFF文件中的段P374.4通用目标文件格式P374.4.1C/C++和汇编语言中段的分配4.4.2寄存器模式设置P381.小存储器模式2.大存储器模式3.C/C++系统堆栈4.动态内存分配P395.结构的对齐4.4.3 链接命令文件4.5汇编源程序的编辑、汇编和链接过程P39 4.5.1编辑4.5.2汇编器1.汇编器的功能2.汇编器的调用3.列表文件P404.5.3连接器1.连接器的功能2.连接器的调用3.多个文件的链接P40-P414.6C55x处理器的数字信号处理库和图像、视频处理库P414.6.1C55x的数字信号处理库4.6.2C55x的图像、视频处理库P42第五章TMS32C55Xde 片内集成外设开发及测试P43-P735.1C55x片内外设与芯片支持库简介1.时钟与定时器2.外部设备链接接口3.信号采集4.通信接口5.其他外设5.2时钟发生器P445.2.1时钟模式寄存器5.2.2工作模式P451.旁路模式2.锁定模式5.2.3CLKOUT输出5.2.4使用方法1.省点2.DSP复位3.失锁5.2.5使用方法及实例5.2.6时钟发生器的调试5.3通用定时器P465.3.1结构框图5.3.2工作原理5.3.3使用方法P471.初始化定时器2.停止/启动定时器3.DSP复位5.3.4通用定时器的应用5.3.4通用定时器的调试P485.4外部存储器接口5.4.1功能与作用5.4.2外部寄存器接口硬件连接与配置P491.异步存储器接口2.同步突发静态存储器P513.同步突发动态存储器P525.4.3外部寄存器接口的软件设置P545.5主机接口(EHPI)P555.5.1EHPI接口的非复用连接方式5.5.2EHPI接口的复用连接方式P565.5.3EHPI口的寄存器5.6多通道缓冲串口McBSP P575.6.1概述5.6.2组成框图5.6.3采样率发生器1.采样率发生器的输出时钟和桢同步信号P582.同步5.6.4多通道选择1.接收多通道选择P592.发送多通道选择5.6.5异常处理1.接收数据溢出2.同步桢同步信号错误3.发送数据重写4.发送寄存器空P605.发送帧同步脉冲错误5.6.6MCBSP寄存器1.收发通道寄存器2.时钟和帧同步寄存器(1)串口控制寄存器(2)收发控制寄存器P61(3)采样率发生寄存器(4)引脚控制寄存器3.多通道选择寄存器P62(1)通道控制寄存器(2)收发通道使能寄存器5.6.7多通道缓冲串口的应用5.6.8MCBSP串口的测试P641.DSP内部链接测试2.外部设备连接测试5.7通道输入/输出端口GPIO P655.7.1GPIO概述5.7.2上电模式设定5.7.3驱动程序开发P665.7.4通用输入/输出GPIO的测试1.输入口测试2.输出口测试5.8DMA控制器5.8.1概述5.8.2通道和端口P675.8.3HPI的配置5.8.4DMA传输配置P681.数据传输单位2.数据打包3.端口4.数据源和目的地址5.8.5DMA控制器的寄存器1.DMA全局控制寄存器P692.DMA通道控制寄存器3.源和目的参数寄存器4.起始地址寄存器P50【我标错了实际应该是P70】5.单元索引寄存器和桢索引寄存器5.8.6使用方法及实例5.9I²C总线P515.9.1I²C总线简介1. I²C总线数据传输P522.仲裁3.时钟产生和同步P534. I²C模块的终端和DMA同步事件5. I²C模块的禁止与使能5.9.2I²C寄存器5.9.3 I²C模块的使用5.10通用串行总线(USB)P545.10.1通用串行总线简介5.11.2USB的DMA控制器P551.主机-DMA模式P56B模块的中断5.10.3USB模块的寄存器1.DMA内容寄存器P572.通用端点描述寄存器3.控制端点描述寄存器P584.中断寄存器P595.11.4USB模块的应用5.11模块转换器(ADC)P605.11.1模数转换器结构和时序5.11.2模数转换器的寄存器P615.11.3使用方法及实例P625.12实时时钟(RTC)5.12.1基本结构P635.12.2内部寄存器5.12.3应用P645.13看门狗定时器(Watchdog)P655.13.1工作方式5.13.2寄存器说明5.13.3应用P665.14一步串口(UART)P665.14.1基本结构1.异步串口发送部分P672.异步串口接收部分3.波特率产生器4.异步串口的中断申请与DMA事件的产生P685.FIFO工作模式6.供电和仿真P695.14.2异步串口寄存器1.接收缓冲寄存器(URRBR)P702.发送保持寄存器(URTHR)3.分频数锁存寄存器(URDLL和URDLM)4.中断使能寄存器(URIER)5.中断标志寄存器(URIIR)6.FIFO控制寄存器(URFCR)P717.线路控制寄存器(URLCR)8.循环模式控制寄存器(URMCR)P729.线路状态寄存器(URLSR)10.供电和仿真控制寄存器(URPECR)P735.14.3异步串口的应用P73第七章TMS320C55X硬件设计实例p75-P93 7.1DSP最小系统设计7.1.1C55x的电源设计7.1.2复位电路设计P767.1.3时钟电路设计P777.1.4JTAG接口电路设计7.1.5程序加载部分1.并行外部存储器(EMIF)加载P782.标准串口加载p793.串行外设接口(SPI)加载p804.EHPI口加载程序P817.2A/D与D/A设计P827.2.1串行多路A/D设计P837.2.2高速并行A/D设计P857.2.3并行D/A设计P867.3C55X在语音系统中的应用P877.4C55x在软件无线电中的应用P89第八章TMS320C55X软件设计实例P95-P1138.1卷积算法8.1.1卷积算法8.1.2卷积算法的MATLAB实现8.1.3卷积算法的DSP实现8.2有限冲击响应滤波器的特点和结构P97 8.2.1有限冲击响应滤波器的特点和结构8.2.2MATLAB设计8.2.3DSP实现P988.3无线冲击响应滤波器(IIR)的实现8.3.1无线冲击响应滤波器的结构8.3.2无线冲击响应滤波器的MATLAB设计P998.3.3DSP实现8.4快速傅里叶变换(FFT)P1018.4.1快速傅里叶变换(FFT)算法8.4.2DSP实现8.5语音信号编码解码(G.711)P1038.5.1语音信号编码解码原理1.G.711语音编码标准2.PCM编码3.A律压扩标准8.5.语音信号编码解码的DSP实现P104 8.6数字图像的锐化8.7Viterbi译码P106 CCS集成开发环境p115-P123 S集成开发环境简介1.1CCS安装及设置(1)CCS2.0系统的安装(2)系统配置(3)系统启动1.2CCS的窗口、菜单和工具条1)CCS的窗口2)CCS的菜单P1163)CCS的工具栏1.3CCS的工程管理1)典型工程文件记录的信息2)创建和管理工程1.4调试1.5通用扩展语音GEL p117S应用举例S仿真P1204.DSP/BIOS简介P123。

一、DSP入门培训第一章DSP芯片基本结构与特点1 DSP简介1.1 什么是DSP?1.2 为什么要使用DSP?1.3 DSP芯片的发展简史2 DSP芯片的基本结构2.1 DSP的结构特征2.2 DSP与MCU、PC的区别3 TMS320系列DSP产品介绍3.1 C2000系列3.2 C5000系列3.3 C6000系列4 DSP的学习建议第二章DSP2407引脚与内部结构1、DSP2407引脚与内部结构2、TI公司的DSP命名规则3、DSP2407内部包含哪些成分?4、CPU结构5、存储器及存储空间配置第三章DSP最小系统介绍3.1DSP最小系统电源结构与要求3.2晶体振荡器电路3.3JTAG接口3.4片外存储器扩展3.5最小系统其他引脚处理与说明3.6最小系统摸板第一章DSP芯片基本结构与特点1、DSP简介1.1 什么是DSP?从20世纪60年代数字信号处理理论的崛起,到20世纪80年代数字信号处理器的产生,DSP 芯片和技术飞速发展.如今已广泛应用在社会各领域,如汽车,数码相机,MP3和手机都是日常生活中DSP的典型应用.1.2 为什么要使用DSP?传统的信号处理是用电阻、电容、电感、二极管、三极管等分立元件完成的,在模拟电路中不能完全消除误差;而在数字信号处理器中,我们用逻辑电平1、0来表示电路中电压的状态,实时运行和存储数据不存在误差,且工作稳定,可靠。

1.3 DSP芯片的发展简史⑴C2000系列芯片的发展简史在C2000系列中,TI公司最早推出的是16位定点产品,其中TMS320F240是1996年推出的C/F24x系列中第一款带有Flash的DSP.运算速度高达20MIPS.之后TI公司先后推出主频为30MHz的LF/LC240x系列和主频为40MHz的LF/LC240xA系列.★其中C/F24x系列和LF/LC240x系列这2个子系列合称为C24xx系列.在C24xx系列的基础上,推出了F/C281x系列.⑵C2000 DSP的分类比较相同系列中的所有芯片,都有相同的CPU结构,区别在于片内存储器容量大小和片内外设种类的多少不同. C24xx系列中,LF2407A片内存储器容量最大,片内外设最多.⑶F/C281x系列功能简介TMS320X281x是TI公司推出的C2000系列中新一代32位定点数字信号处理芯片.该系列芯片每秒可以执行1.5亿次指令(150MIPS),与TMS320F24x/LF240x的源代码和部分功能相兼容,进一步扩大了TMS320C2000的应用范围.⑷F/C281x与C240x内核的比较F/C281x系列的DSP内核称之为C28x,与此对应,C240x系列的DSP内核称之为C2Xlp. C28x 兼容了C2Xlp.当AMODE=1时, C28x与C2Xlp工作方式完全一样,只不过寻址范围从16位增加到了32位;当AMODE=0时, C28x工作在崭新的模式下.C28x与C2Xlp的主要区别2、DSP芯片的基本结构2.1 DSP的结构特征1) 专用硬件乘法器在通用微处理器件中,乘法是由软件实现的.它实际上是由时钟控制的一连串的<移位-加法>操作,乘法操作需要100个左右的时钟周期.而用DSP来处理,可以使乘法运算在一个单指令周期内完成.2) 采用总线哈拂结构传统的微处理器采用的是冯诺依曼结构:统一的程序和数据空间,共享的程序和数据总线.而DSP采用的总线哈拂结构,可在一个时钟周期内同时读取程序和存取操作,速度大为提高.3)流水线在CPU内,每条指令的执行分为取指,解码和执行3个阶段.流水线处理使得若干条指令的不同执行阶段并行执行,从而提高程序的执行速度.2.2 DSP与MCU、PC的区别MCU的速度较慢;CPU体积较大,功耗较高。

本科毕业论文(科研训练、毕业设计)题目:DSP 图像处理算法的实现-III姓名:翁彬彬学院:信息技术与科学学院系:电子工程系专业:电子信息工程专业年级:2004学号:04140059指导教师(校内):杨涛职称:教授指导教师(校外):职称:2008 年 5 月20 日1摘要本文研究的是基于TI 公司DSP 硬件平台的数字图像处理技术。

考虑到可移植性,采用C 语言编写代码。

采用空域法设计图像处理的算法,所涉及运算包括卷积,相关,中值滤波等。

由于图像处理要处理大量的数据,需用DSP 处理器来提高效率。

TMS320C6000 系列DSP 是TI 公司最新推出的一种并行处理的数字信号处理器,其特有的代码优化器也使得C 优化更加方便。

我们根据TMS320C6000 系列的结构特点,对C 代码进行一系列优化,例如:选用适当的编译器选项,内联函数的使用,字处理技术,打开循环,流水线技术,线性汇编等一系列方法对C 代码进行优化,从而极大地提高了数字图像处理的工作效率。

关键字数字图像处理TMS320C6000 系列DSP C 语言优化Abstract: In this thesis, based on the DSP hardware platform of TI Co., the algorithms of digital image processing were studied. C language was used to program these algorithms for the purpose of maximizing the portability of program modules. These algorithms, which include convolutions, correlations and medium filters, were designed based on spatial patterns. To make real-time image processing possible, DSP processors are used to process the massive data in images. The TMS320C6000 DSPs from TI Co. are parallel digital image processors, of which the C-complier makes the compilation and optimization of C-codes seamless and highly efficient. The C-code optimization was highly improved based on the unique designing features of TMS320C6000 series, such as proper choices of compiling options, the utility of intrinsics, the word processing technology, loop opening, pipeline technologies, linear assembly and etc.Keywords: Digital image processing technology TMS320C6000 C code optimization2目录:引言 (4)第一章数字图像处理的基本知识 (4)1.1 数字图像处理简述 (4)1.2 几种处理算法 (4)第二章TMS320C6000DSP芯片的特点 (6)2.1 数字信号处理器的特点………………………………………… ..62.2 TMS320C6000 的硬件结构简介 (7)2.3 TMS320C6000 指令系统................................................10.第三章基于TMS320C6000DSP系列的代码优化 (11)3.1 第一个阶段代码优化 (11)3.2 第二个阶段代码优化 (13)3.3 第三个阶段代码优化 (17)第四章对所编C代码进行优化处理 (20)4.1 小循环的打开 (20)4.2 较大循环的打开 (21)结论 (22)致谢语 (24)参考文献 (24)3随着计算机技术的发展,数字图像处理技术以其广阔的应用领域,受到人们越来越多的关注,本次实验是以DSP 为平台,对数字图像处理系统进行仿真。