74LS164(IO扩展)中文资料

- 格式:doc

- 大小:162.61 KB

- 文档页数:3

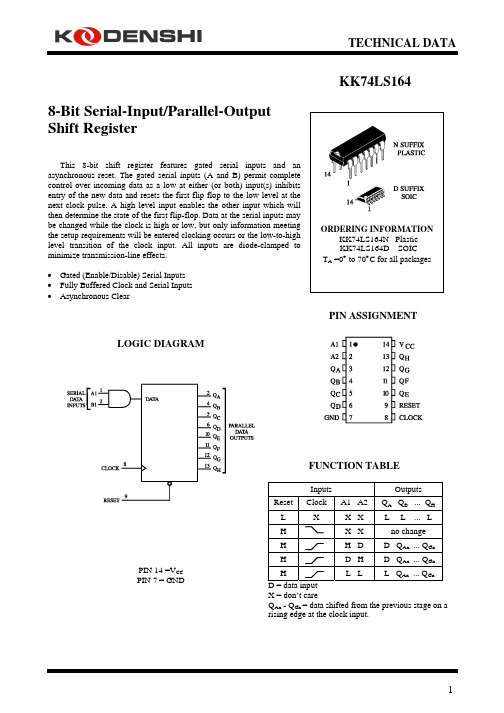

TECHNICAL DATAKK 74LS1648-Bit Serial-Input/Parallel-Output Shift RegisterThis 8-bit shift register features gated serial inputs and an asynchronous reset. The gated serial inputs (A and B) permit complete control over incoming data as a low at either (or both) input(s) inhibits entry of the new data and resets the first flip flop to the low level at the next clock pulse. A high level input enables the other input which will then determine the state of the first flip-flop. Data at the serial inputs may be changed while the clock is high or low, but only information meeting the setup requirements will be entered clocking occurs or the low-to-high level transition of the clock input. All inputs are diode-clamped to minimize transmission-line effects.• Gated (Enable/Disable) Serial Inputs • Fully Buffered Clock and Serial Inputs • Asynchronous ClearPIN ASSIGNMENTFUNCTION TABLEX = don’t careQ An - Q Gn = data shifted from the previous stage on a rising edge at the clock input.LOGIC DIAGRAMPIN 14 =V CC PIN 7 = GNDMAXIMUM RATINGS*Unit Symbol Parameter ValueV CC Supply Voltage 7.0 VV IN Input Voltage 7.0 VV OUT Output Voltage 5.5 VTstg Storage Temperature Range -65 to +150 °C*Maximum Ratings are those values beyond which damage to the device may occur.Functional operation should be restricted to the Recommended Operating Conditions.RECOMMENDED OPERATING CONDITIONSUnit Symbol Parameter MinMax V CC Supply Voltage 4.75 5.25 VV IH High Level Input Voltage 2.0 VV IL Low Level Input Voltage 0.8 VI OH High Level Output Current -0.4 mAI OL Low Level Output Current 8.0 mAT A Ambient Temperature Range 0 +70 °Cf clock Clock Frequency 0 25 MHzt su Setup Time, A1 or A2 to Clock 15 nst h Hold Time, Clock to A1 or A2 5 nst w Pulse Width, Clock 20 nst w Pulse Width, Reset 20 nst rec Recovery Time 5 nsDC ELECTRICAL CHARACTERISTICS over full operating conditionsLimitGuaranteedUnitMax Symbol Parameter TestConditions MinV IK Input Clamp Voltage V CC = min, I IN = -18 mA -1.5 VV OH High Level Output Voltage V CC = min, I OH = -0.4 mA 2.7 VV OL Low Level Output Voltage V CC = min, I OL = 4 mA 0.4 VV CC = min, I OL = 8 mA 0.5I IH High Level Input Current V CC = max, V IN = 2.7 V 20 mAV CC = max, V IN = 7.0 V 0.1 mAI IL Low Level Input Current V CC = max, V IN = 0.4 V -0.4 mA-20 -100 mAI O Output Short Circuit Current V CC = max, V O = 0 V(Noote 1)I CC Supply Current V CC = max (Note 2) 27 mANote 1: Not more than one output should be shorted at a time, and duration should not exceed one second.Note 2: I CC is measured with outputs open, serial inputs grouned, the clock input at 2.4 V, and a momentary ground,then 4.5 V applied.AC ELECTRICAL CHARACTERISTICS (T A=25°C, V CC = 5.0 V, C L = 15 pF, R L = 2 kΩ, t r =15ns, t f = 6.0 ns)UnitMax Symbol Parameter Mint PLH Propagation Delay Time, Clock to Q 27 nst PHL Propagation Delay Time, Clock to Q 32 nst PHL Propagation Delay Time, Reset to Q 36 nst su Setup Time, A1 or A2 to Clock 15 nst h Hold Time, Clock to A1 or A2 5 nst w Pulse Width, Clock 20 nst w Pulse Width, Reset 20 nsFigure 1. Switching Waveforms Figure 2. Switching WaveformsNOTES A.C L includes probe and jig capacitance.B. All diodes are 1N916 or 1N3064.Figure 3. Switching Waveform Figure 4. Test CircuitTIMING DIAGRAM。

74LS164(IO扩展)中⽂资料

164 为8 位移位寄存器,其主要电特性的典型值如下:

54/74164 185mW 54/74LS164 80mW

当清除端(CLEAR)为低电平时,输出端(QA-QH)均为低电平。

串⾏数据输⼊端(A,B)可控制数据。

当A、B任意⼀个为低电平,则禁⽌新数据输⼊,在时钟端(CLOCK)脉冲上升沿作⽤下Q0 为低电平。

当A、B 有⼀个为⾼电平,则另⼀个就允许输⼊数据,并在CLOCK 上升沿作⽤下决定Q0 的状态。

引脚功能:

CLOCK :时钟输⼊端

CLEAR:同步清除输⼊端(低电平有效)

A,B :串⾏数据输⼊端

QA-QH:输出端

图1 74LS164封装图

图2 74LS164 内部逻辑图

极限值

电源电压7V

输⼊电压……… 5.5V

⼯作环境温度

54164………… -55~125℃

74164………… -0~70℃

储存温度……-65℃~150℃

图3 真值表

H-⾼电平L-低电平X-任意电平

↑-低到⾼电平跳变

QA0,QB0,QH0 -规定的稳态条件建⽴前的电平

QAn,QGn -时钟最近的↑前的电平

图4 时序图

建议操作条件

符号参数最⼩值典型值最⼤值单位VCC 电源电压 4.75 5 5.25 V VIH 输⼊⾼电平电压ViH 2 --V

电⽓特性

动态特性(TA=25℃)。

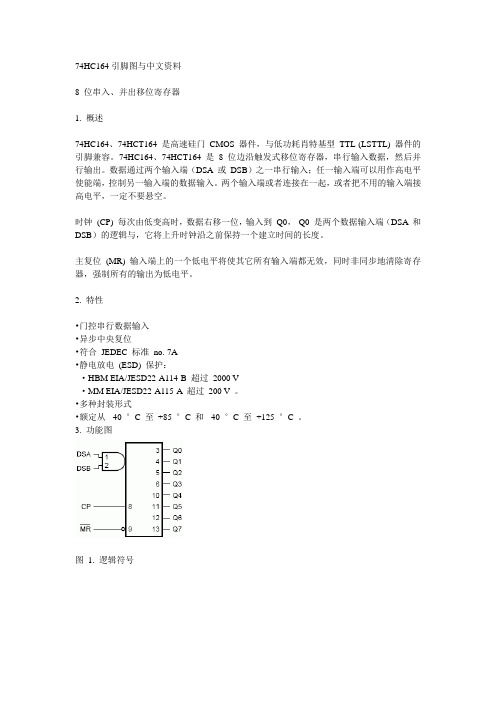

74HC164引脚图与中文资料8 位串入、并出移位寄存器1. 概述74HC164、74HCT164 是高速硅门CMOS 器件,与低功耗肖特基型TTL (LSTTL) 器件的引脚兼容。

74HC164、74HCT164 是8 位边沿触发式移位寄存器,串行输入数据,然后并行输出。

数据通过两个输入端(DSA 或DSB)之一串行输入;任一输入端可以用作高电平使能端,控制另一输入端的数据输入。

两个输入端或者连接在一起,或者把不用的输入端接高电平,一定不要悬空。

时钟(CP) 每次由低变高时,数据右移一位,输入到Q0,Q0 是两个数据输入端(DSA 和DSB)的逻辑与,它将上升时钟沿之前保持一个建立时间的长度。

主复位(MR) 输入端上的一个低电平将使其它所有输入端都无效,同时非同步地清除寄存器,强制所有的输出为低电平。

2. 特性•门控串行数据输入•异步中央复位•符合JEDEC 标准no. 7A•静电放电(ESD) 保护:·HBM EIA/JESD22-A114-B 超过2000 V·MM EIA/JESD22-A115-A 超过200 V 。

•多种封装形式•额定从-40 °C 至+85 °C 和-40 °C 至+125 °C 。

3. 功能图图1. 逻辑符号图2. IEC 逻辑符号图3. 逻辑图图4. 功能图4. 引脚信息图5. DIP14、SO14、SSOP14 和TSSOP14 封装的引脚配置引脚说明符号引脚说明DSA 1 数据输入DSB 1 数据输入Q0~Q3 3~6 输出GND 7 地(0 V)CP 8 时钟输入(低电平到高电平边沿触发)/M/R 9 中央复位输入(低电平有效)Q4~Q7 10~13 输出VCC 14 正电源罗亩的笔记74HC164英文资料参考链接:/news/2008-12/8713.htm74HC164中文资料参数时间:2009-06-19 17:49:09 来源:资料室作者:SN54HC164,/SN74HC164是8位移位寄存器,当其中一个(或二个)选通串行输入端的低电平禁止进入新数据,并把第一个触发器在下一个时钟脉冲来后复位到低电平时,门控串行输入端(A 和B)可完全控制输入数据。

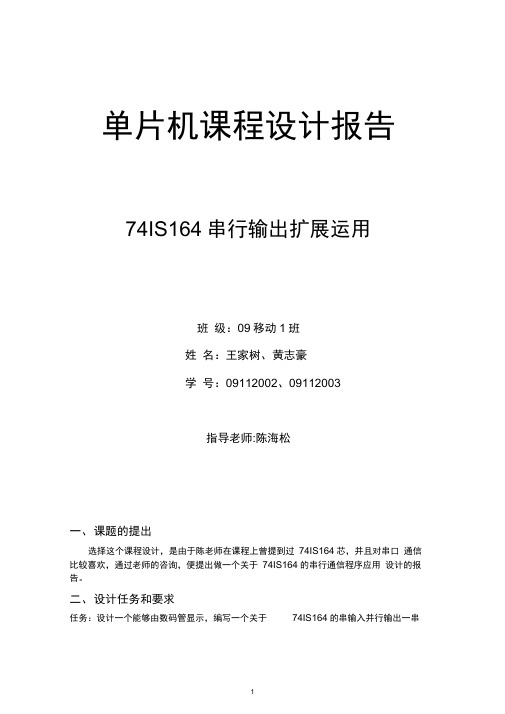

单片机课程设计报告74IS164串行输出扩展运用班级:09移动1班姓名:王家树、黄志豪学号:09112002、09112003指导老师:陈海松一、课题的提出选择这个课程设计,是由于陈老师在课程上曾提到过74IS164芯,并且对串口通信比较喜欢,通过老师的咨询,便提出做一个关于74IS164的串行通信程序应用设计的报告。

二、设计任务和要求任务:设计一个能够由数码管显示,编写一个关于74IS164的串输入并行输出一串数字。

要求:利用单片机的并行串行I/O 口,利用C 语言中的指针函数,编写一段好用 又简洁的设计代码。

三、设计方案的论证1首先从参考文献中可以查到 54/74164是8位移位寄存器(串行输入,并行输 出),是8位边沿触发式移位寄存器,串行输入数据,然后并行输出。

数据通 过两个输入端(DSA或DSB )之一串行输入;任一输入端可以用作高电平使能端, 控制另一输入端的数据输入。

时钟(CP )每次由低变高时,数据右移一位,输入 到QO , Q0是两个数据输入端(DSA 和DSB )的逻辑与,它将上升时钟沿之前保 持一个建立时间的长度。

主复位(MR )输入端上的一个低电平将使其它所有输入 端都无效,同时非同步地清除寄存器,强制所有的输出为低电平。

2、功能图图1.逻辑符号CP3 斗 5£©10—11□12 —□13&1D34S610111213SRGS四、硬件资源及其分配关键元件:89C51芯片,74IS164芯片、数码管、复位电路主要用到的硬件:P3 口、数码管、串行输出输入口;硬件分配:1•串行输出输入口(单片机51的10、11脚)分别接第一个74IS164的8脚1、2 脚,第二第三第四第五第六个进行级联;2. 74IS164的9脚复位端接高电平;3. 每个数码管(a b、c、d、e、f、g)接74ls164 并行输出口(3、4、5、6、10、11、12、13);五、硬件图:1£_:29Jfl-:31XTAL1PO.O/ADO P0.1/AD1 P0.2/AD2 XTAL2P03/AD3 P0.4/AD4 P0.5/AD6 P0.6/AD6 RSTP0.7/AD7 P2.0/A8 P2.1/A9 P2 2fA103E J —11: 35—11: 33 ■ ^12;PSEN ALE EAP2.3fA11 P2.4JA1 2 P25fA13 P2.6fA1 4P2.7JA1524丄—il丄士士丄土012345671 1 .1 1- 1 1 P3.0/RXD P3 1HXD P3.2flNTg P3.3/iNTT P3.4/T0 P3.5/T1 P3.6/WRP3.7/RD10 叫1 仁 txq_L2:…_L2 _L£ _L^ _LZ ARl^FlI P=ni^ri I FDhRy (AT89C51 控制) 弓RGB 1 1 n-LM-iMH〜L -13I-Lit ■BU11*lag(74IS164 级联)(整图分布)六、主程序:1第一次编写的程序 #in elude <reg51.h>#define _DISP_LED_h__void Disp_LED(unsigned int *key_num); void DelayNS(unsigned int dly); void main() {int nu mb[6]={1,5,8,3,1,2}; Disp_LED( nu mb); DelayNS(20);}void Disp_LED(u nsig ned int *key_ num) { 一 一Un sig ned char code LED_Val[]={0x03,0x9f,0x25,0x0d,0x99,0x49,0x41,0x1f,0x01,0x09};//0-9 un sig ned char data nu m[6];un sig ned char k; num[ 0]=*key_ num; nu m[1]=*(key_num+1); nu m[2]=*(key_num+2); nu m[3]=*(key_num+3); num[ 4]=*(key_ nu m+4); nu m[5]=*(key_ nu m+5);for(k=0;k<=5;k++)R&Trarr HF rrpul- PI .i fu 卜M E t-ii t-ii hlviwoe- I «.IMi j MdtiiJ RMfiaES L IW I T科出片3■治 时」靳I ■:皿2HHMli■梓Fi.imA »(-*nr frutfTT利丄砒[F-J^Ti MMffir 科.WT F JI fwT 蛋=1玉 4.■IK5-IiRCFlE^terLHiJiM-h■■>i・m ・・』■ h dI■>1I J aIfa■ hdI■I I.■b■・■!■3 I■ ■ ■":'^^1° -!:- ■■I - '1 v :n-fSI ^rMI ^r|5| nrf"| fr-|EI 訂={:I ;;::』:; Lfllj : ;; I J HJ :: IJWI--》25 ___ r-k£吐ID|聊IJ^L»>■^fTi^i^O4*84SBUF=LED_Val[ nu m[5-k]]; while(TI==O);TI=O;}}void DelayNS(u nsig ned int dly){int i,j;for(i=0;i<10000;i++) for(j=0;j<dly;j++);}2、第二次自学的头文件编写的程序:〃Disp_LED.c 主程序#in clude <reg51.h>#in clude "DISP_LED.h"void main(){int numb[6]={1,5,8,3,1,2};Disp_LED( nu mb); DelayNS(20);}〃DISP_LED.h 自编头文件#ifndef __DISP_LED_h__ #defi ne __DISP_LED_h__ void Disp_LED(u nsig ned int *key_ nu m); void DelayNS(u nsig ned int dly);/*函数名称:Disp_LED函数功能:数码管显示输入参数:key_num*/void Disp_LED(u nsig ned int *key_ num) { 一一un sig ned char code LED_Val[]={0x03,0x9f,0x25,0x0d,0x99,0x49,0x41,0x1f,0x01,0x09};//0-9un sig ned char data nu m[6];un sig ned char k;num[ 0]=*key_ num;nu m[1]=*(key_num+1);nu m[2]=*(key_num+2);nu m[3]=*(key_num+3);num[ 4]=*(key_ nu m+4);nu m[5]=*(key_ nu m+5);for(k=0;k<=5;k++){SBUF=LED_Val[ nu m[5-k]];while(TI==0);TI=0;}}/*函数名称:DelayNS 函数功能:延时程序输入参数:dly 返回信息:无*/void DelayNS(u nsig ned int dly) {int i,j; for(i=0;i<10000;i++) for(j=0;j<dly;j++);} #en dif七、调试运行1、按照电路图将电路用protues仿真。

查看文章74HC164引脚图与中文资料2010-01-25 15:048 位串入、并出移位寄存器1. 概述74HC164、74HCT164 是高速硅门 CMOS 器件,与低功耗肖特基型 TTL (LSTTL) 器件的引脚兼容。

74HC164、74HCT164 是 8 位边沿触发式移位寄存器,串行输入数据,然后并行输出。

数据通过两个输入端(DSA 或 DSB)之一串行输入;任一输入端可以用作高电平使能端,控制另一输入端的数据输入。

两个输入端或者连接在一起,或者把不用的输入端接高电平,一定不要悬空。

时钟 (CP) 每次由低变高时,数据右移一位,输入到 Q0, Q0 是两个数据输入端(DSA 和 DSB)的逻辑与,它将上升时钟沿之前保持一个建立时间的长度。

主复位 (MR) 输入端上的一个低电平将使其它所有输入端都无效,同时非同步地清除寄存器,强制所有的输出为低电平。

2. 特性门控串行数据输入异步中央复位符合 JEDEC 标准 no. 7A静电放电 (ESD) 保护:·HBM EIA/JESD22-A114-B 超过 2000 V·MM EIA/JESD22-A115-A 超过 200 V 。

多种封装形式额定从 -40 °C 至+85 °C 和 -40 °C 至+125 °C 。

3. 功能图图 1. 逻辑符号图 2. IEC 逻辑符号图 3. 逻辑图图 4. 功能图4. 引脚信息图 5. DIP14、SO14、SSOP14 和 TSSOP14 封装的引脚配置引脚说明符号引脚说明DSA 1 数据输入DSB 1 数据输入Q0~Q3 3~6 输出GND 7 地 (0 V)CP 8 时钟输入(低电平到高电平边沿触发)/M/R 9 中央复位输入(低电平有效)Q4~Q7 10~13 输出VCC 14 正电源罗亩的笔记74HC164英文资料temp_08121617411733.rar74HC164中文资料temp_08121617428539.rar阅读:次参考链接:/news/2008-12/8713.htm。

74HC164中文资料参数SN54HC164,/SN74HC164是8位移位存放器,当其中一个〔或二个〕选通串行输入端的低电平禁止进入新数据,并把第一个触发器在下一个时钟脉冲来后复位到低电平时,门控串行输入端〔A 和B〕可完全控制输入数据。

一个高电平输入后就使另一个输入端赋能,这个输入就决定了第一个触发器的状态。

虽然不管时钟处于高电平或低电平时,串行输入端的数据都可以被改变,但只有满足建立条件的信息才能被输入。

时钟控制发生在时钟输入由低电平到高电平的跃变上。

为了减小传输线效应,所有输入端均采用二极管钳位。

功能表:Inputs输入Outputs输出CLR CLK A B QA QB ...QHL X X X L L LH L X X QA0QB0QH0H↑H H H QAn QGnH↑L X L QAn QGnH↑X L L QAn QGnH=高电平〔稳定态〕 L=低电平〔稳定态〕×=不定↑=从低电平转换到高电平QA0…QH0=在稳定态输入条件建立前QA…QH 的相应电平QAn…QHn=在最近的时钟输入条件〔↑〕建立前QA…QH 的相应电平,表示移位一位文档文档图1 逻辑图〔正逻辑〕图2 引脚图 Absolute Maximum Ratings 绝对最大额定值 Supply voltage range, 电源电压X 围 VCC–0.5 V to 7V Input clamp current, 输入钳位电流 IIK (VI < 0 or VI > VCC) (see Note 1) ±20 mA Output clamp current,输出钳位电流 IOK (VO < 0 or VO > VCC) (see Note 1) ±20 mA Continuous output current,连续输出电流 IO (VO = 0 to VCC) ±25 mA Continuous current through 连续通过电流 VCC or GND±50 mA 封装热阻 thermal impedance, θJA (see Note 2):D 封装86℃/W N 封装 80℃/W NS 封装 76℃/W PW 封装113℃/WDC SPECIFICATIONS直流电气规格表:DC SPECIFICATIONS直流电气规格〔续〕文档IOH=–4mA 4.5 V---6 V---VOL 输出低电平电压VI=VIHorVILIOL=20μA2 V---V4.5 V---6 V---IOL = 4mA 4.5 V---6 V---II 输入漏电流VI = VCC or 0 6 V-±±100-±1000-±1000nA ICC 静态电源电流VI = VCC or 0,IO = 0 6 V--8-160-80μACi 电容-2V to6V-310-10-10pF图3 参数测量信息文档图4 typical clear, shift, and clear sequence典型去除、移位和去除时序应用电路:文档文档图5 LCD驱动电路图6 LED驱动电路文档文档文档文档word文档。

移位寄存器的串行扩展(74hc164)1. 74HC16474HC164是比较典型的移位寄存器,该移位寄存器有一个数据输入端口、一个时钟信号端口和八个输出端口。

如图1所示。

当时钟信号从低电平变为高电平的时候将输出一个数据到输出端D0,当时钟第二次由低电平变为高电平的时候将输出第二个数据到D0,而第一个数据将转移到D1端口。

依此类推,每一个时钟周期中都有一个串行数据输出到D0,而其他的数据则不断往高位移动直到所有数据传输结束。

如果不再有时钟周期输入,则这些数据将暂存在输出端。

如果需要有更多的输出端口,可以把多个74HC164串联起来用。

串联的方法如图2所示。

在上图的串联电路中,左边的锁存器D7与右边锁存器的串行数据输入端连接,当左边的锁存器D0~D7数据全部输出以后,再输入一个串行信号,左边锁存器D7数据将作为右边锁存器的输入数据并从右边锁存器D0端输出,从而实现了多个字节数据的移位锁存。

这样利用74HC164就实现了串行数据到并行数据的转换。

注意到在上面的两个图中,无论输出什么长度的数据,所需要的输入信号都只有两个,一个是串行数据输入,另一个是锁存器的时钟信号输入。

如果我们把这两个输入端口连接到单片机的两个输出端口上,其中单片机的一个端口串行输出数据,另一个端口输出时钟信号以便控制串行数据的锁存方式,那么我们就只需要两个单片机端口几乎实现任意数量的并口输出。

2. 8051串口方式0的工作原理与时序图3 串口方式0的时序8051串口方式0的时序如图所示,RXD(P3.0)为数据端,TXD(P3.1)为同步移位脉冲端,每次串行发送、接收8位数据(一帧),低位在先。

时钟为Fosc/12。

(1)发送执行任何一条MOV SUBF,#data指令时,启动内部串行发送允许,SEND置高电平,随后在TXD同步移位时钟的作用下,将数据data从RXD端移位输出。

一帧数据发送完毕时,内部发送中断请求TI有效。

要再次发送一帧时,须用软件清TI。

1. 74LS00 TTL 2输入端四与非门2. 74LS01 TTL 集电极开路2输入端四与非门3. 74LS02 TTL 2输入端四或非门4. 74LS03 TTL 集电极开路2输入端四与非门5. 74LS04 TTL 六反相器6. 74LS05 TTL 集电极开路六反相器7. 74LS06 TTL 集电极开路六反相高压驱动器8. 74LS07 TTL 集电极开路六正相高压驱动器9. 74LS08 TTL 2输入端四与门10. 74LS09 TTL 集电极开路2输入端四与门11. 74LS10 TTL 3输入端3与非门12. 74LS107 TTL 带清除主从双J-K触发器13. 74LS109 TTL 带预置清除正触发双J-K触发器14. 74LS11 TTL 3输入端3与门15. 74LS112 TTL 带预置清除负触发双J-K触发器16. 74LS12 TTL 开路输出3输入端三与非门17. 74LS121 TTL 单稳态多谐振荡器18. 74LS122 TTL 可再触发单稳态多谐振荡器19. 74LS123 TTL 双可再触发单稳态多谐振荡器20. 74LS125 TTL 三态输出高有效四总线缓冲门21. 74LS126 TTL 三态输出低有效四总线缓冲门22. 74LS13 TTL 4输入端双与非施密特触发器23. 74LS132 TTL 2输入端四与非施密特触发器24. 74LS133 TTL 13输入端与非门25. 74LS136 TTL 四异或门26. 74LS138 TTL 3-8线译码器/复工器27. 74LS139 TTL 双2-4线译码器/复工器28. 74LS14 TTL 六反相施密特触发器29. 74LS145 TTL BCD—十进制译码/驱动器30. 74LS15 TTL 开路输出3输入端三与门31. 74LS150 TTL 16选1数据选择/多路开关32. 74LS151 TTL 8选1数据选择器33. 74LS153 TTL 双4选1数据选择器34. 74LS154 TTL 4线—16线译码器35. 74LS155 TTL 图腾柱输出译码器/分配器36. 74LS156 TTL 开路输出译码器/分配器37. 74LS157 TTL 同相输出四2选1数据选择器38. 74LS158 TTL 反相输出四2选1数据选择器39. 74LS16 TTL 开路输出六反相缓冲/驱动器40. 74LS160 TTL 可预置BCD异步清除计数器41. 74LS161 TTL 可予制四位二进制异步清除计数器42. 74LS162 TTL 可预置BCD同步清除计数器43. 74LS163 TTL 可予制四位二进制同步清除计数器44. 74LS164 TTL 八位串行入/并行输出移位寄存器45. 74LS165 TTL 八位并行入/串行输出移位寄存器46. 74LS166 TTL 八位并入/串出移位寄存器47. 74LS169 TTL 二进制四位加/减同步计数器48. 74LS17 TTL 开路输出六同相缓冲/驱动器49. 74LS170 TTL 开路输出4×4寄存器堆50. 74LS173 TTL 三态输出四位D型寄存器51. 74LS174 TTL 带公共时钟和复位六D触发器52. 74LS175 TTL 带公共时钟和复位四D触发器53. 74LS180 TTL 9位奇数/偶数发生器/校验器54. 74LS181 TTL 算术逻辑单元/函数发生器55. 74LS185 TTL 二进制—BCD代码转换器56. 74LS190 TTL BCD同步加/减计数器57. 74LS191 TTL 二进制同步可逆计数器58. 74LS192 TTL 可预置BCD双时钟可逆计数器59. 74LS193 TTL 可预置四位二进制双时钟可逆计数器60. 74LS194 TTL 四位双向通用移位寄存器61. 74LS195 TTL 四位并行通道移位寄存器62. 74LS196 TTL 十进制/二-十进制可预置计数锁存器63. 74LS197 TTL 二进制可预置锁存器/计数器64. 74LS20 TTL 4输入端双与非门65. 74LS21 TTL 4输入端双与门66. 74LS22 TTL 开路输出4输入端双与非门67. 74LS221 TTL 双/单稳态多谐振荡器68. 74LS240 TTL 八反相三态缓冲器/线驱动器69. 74LS241 TTL 八同相三态缓冲器/线驱动器70. 74LS243 TTL 四同相三态总线收发器71. 74LS244 TTL 八同相三态缓冲器/线驱动器72. 74LS245 TTL 八同相三态总线收发器73. 74LS247 TTL BCD—7段15V输出译码/驱动器74. 74LS248 TTL BCD—7段译码/升压输出驱动器75. 74LS249 TTL BCD—7段译码/开路输出驱动器76. 74LS251 TTL 三态输出8选1数据选择器/复工器77. 74LS253 TTL 三态输出双4选1数据选择器/复工器78. 74LS256 TTL 双四位可寻址锁存器79. 74LS257 TTL 三态原码四2选1数据选择器/复工器80. 74LS258 TTL 三态反码四2选1数据选择器/复工器81. 74LS259 TTL 八位可寻址锁存器/3-8线译码器82. 74LS26 TTL 2输入端高压接口四与非门83. 74LS260 TTL 5输入端双或非门84. 74LS266 TTL 2输入端四异或非门85. 74LS27 TTL 3输入端三或非门86. 74LS273 TTL 带公共时钟复位八D触发器87. 74LS279 TTL 四图腾柱输出S-R锁存器88. 74LS28 TTL 2输入端四或非门缓冲器89. 74LS283 TTL 4位二进制全加器90. 74LS290 TTL 二/五分频十进制计数器91. 74LS293 TTL 二/八分频四位二进制计数器92. 74LS295 TTL 四位双向通用移位寄存器93. 74LS298 TTL 四2输入多路带存贮开关94. 74LS299 TTL 三态输出八位通用移位寄存器95. 74LS30 TTL 8输入端与非门96. 74LS32 TTL 2输入端四或门97. 74LS322 TTL 带符号扩展端八位移位寄存器98. 74LS323 TTL 三态输出八位双向移位/存贮寄存器99. 74LS33 TTL 开路输出2输入端四或非缓冲器100. 74LS347 TTL BCD—7段译码器/驱动器101. 74LS352 TTL 双4选1数据选择器/复工器102. 74LS353 TTL 三态输出双4选1数据选择器/复工器103. 74LS365 TTL 门使能输入三态输出六同相线驱动器104. 74LS365 TTL 门使能输入三态输出六同相线驱动器105. 74LS366 TTL 门使能输入三态输出六反相线驱动器106. 74LS367 TTL 4/2线使能输入三态六同相线驱动器107. 74LS368 TTL 4/2线使能输入三态六反相线驱动器108. 74LS37 TTL 开路输出2输入端四与非缓冲器109. 74LS373 TTL 三态同相八D锁存器110. 74LS374 TTL 三态反相八D锁存器111. 74LS375 TTL 4位双稳态锁存器112. 74LS377 TTL 单边输出公共使能八D锁存器113. 74LS378 TTL 单边输出公共使能六D锁存器114. 74LS379 TTL 双边输出公共使能四D锁存器115. 74LS38 TTL 开路输出2输入端四与非缓冲器116. 74LS380 TTL 多功能八进制寄存器117. 74LS39 TTL 开路输出2输入端四与非缓冲器118. 74LS390 TTL 双十进制计数器119. 74LS393 TTL 双四位二进制计数器120. 74LS40 TTL 4输入端双与非缓冲器121. 74LS42 TTL BCD—十进制代码转换器122. 74LS352 TTL 双4选1数据选择器/复工器123. 74LS353 TTL 三态输出双4选1数据选择器/复工器124. 74LS365 TTL 门使能输入三态输出六同相线驱动器125. 74LS366 TTL 门使能输入三态输出六反相线驱动器126. 74LS367 TTL 4/2线使能输入三态六同相线驱动器127. 74LS368 TTL 4/2线使能输入三态六反相线驱动器128. 74LS37 TTL 开路输出2输入端四与非缓冲器129. 74LS373 TTL 三态同相八D锁存器130. 74LS374 TTL 三态反相八D锁存器131. 74LS375 TTL 4位双稳态锁存器132. 74LS377 TTL 单边输出公共使能八D锁存器133. 74LS378 TTL 单边输出公共使能六D锁存器134. 74LS379 TTL 双边输出公共使能四D锁存器135. 74LS38 TTL 开路输出2输入端四与非缓冲器136. 74LS380 TTL 多功能八进制寄存器137. 74LS39 TTL 开路输出2输入端四与非缓冲器138. 74LS390 TTL 双十进制计数器139. 74LS393 TTL 双四位二进制计数器140. 74LS40 TTL 4输入端双与非缓冲器141. 74LS42 TTL BCD—十进制代码转换器142. 74LS447 TTL BCD—7段译码器/驱动器143. 74LS45 TTL BCD—十进制代码转换/驱动器144. 74LS450 TTL 16:1多路转接复用器多工器145. 74LS451 TTL 双8:1多路转接复用器多工器146. 74LS453 TTL 四4:1多路转接复用器多工器147. 74LS46 TTL BCD—7段低有效译码/驱动器148. 74LS460 TTL 十位比较器149. 74LS461 TTL 八进制计数器150. 74LS465 TTL 三态同相2与使能端八总线缓冲器151. 74LS466 TTL 三态反相2与使能八总线缓冲器152. 74LS467 TTL 三态同相2使能端八总线缓冲器153. 74LS468 TTL 三态反相2使能端八总线缓冲器154. 74LS469 TTL 八位双向计数器155. 74LS47 TTL BCD—7段高有效译码/驱动器156. 74LS48 TTL BCD—7段译码器/内部上拉输出驱动157. 74LS490 TTL 双十进制计数器158. 74LS491 TTL 十位计数器159. 74LS498 TTL 八进制移位寄存器160. 74LS50 TTL 2-3/2-2输入端双与或非门161. 74LS502 TTL 八位逐次逼近寄存器162. 74LS503 TTL 八位逐次逼近寄存器163. 74LS51 TTL 2-3/2-2输入端双与或非门164. 74LS533 TTL 三态反相八D锁存器165. 74LS534 TTL 三态反相八D锁存器166. 74LS54 TTL 四路输入与或非门167. 74LS540 TTL 八位三态反相输出总线缓冲器168. 74LS55 TTL 4输入端二路输入与或非门169. 74LS563 TTL 八位三态反相输出触发器170. 74LS564 TTL 八位三态反相输出D触发器171. 74LS573 TTL 八位三态输出触发器172. 74LS574 TTL 八位三态输出D触发器173. 74LS645 TTL 三态输出八同相总线传送接收器174. 74LS670 TTL 三态输出4×4寄存器堆175. 74LS73 TTL 带清除负触发双J-K触发器176. 74LS74 TTL 带置位复位正触发双D触发器177. 74LS76 TTL 带预置清除双J-K触发器178. 74LS83 TTL 四位二进制快速进位全加器179. 74LS85 TTL 四位数字比较器180. 74LS86 TTL 2输入端四异或门181. 74LS90 TTL 可二/五分频十进制计数器182. 74LS93 TTL 可二/八分频二进制计数器183. 74LS95 TTL 四位并行输入\\输出移位寄存器184. 74LS97 TTL 6位同步二进制乘法器。

74HC164中文资料参数

SN54HC164,/SN74HC164是8位移位寄存器,当其中一个(或二个)选通串行输入端的低电平禁止进入新数据,并把第一个触发器在下一个时钟脉冲来后复位到低电平时,门控串行输入端(A 和B)可完全控制输入数据。

一个高电平输入后就使另一个输入端赋能,这个输入就决定了第一个触发器的状态。

虽然不管时钟处于高电平或低电平时,串行输入端的数据都可以被改变,但只有满足建立条件的信息才能被输入。

时钟控制发生在时钟输入由低电平到高电平的跃变上。

为了减小传输线效应,所有输入端均采用二极管钳位。

功能表:

H=高电平(稳定态) L=低电平(稳定态)×=不定↑=从低电平转换到高电平

QA0…QH0=在稳定态输入条件建立前QA…QH 的相应电平

QAn…QHn=在最近的时钟输入条件(↑)建立前QA…QH 的相应电平,表示移位一位

图1 逻辑图(正逻辑)

图2 引脚图

Absolute Maximum Ratings绝对最大额定值

DC SPECIFICATIONS直流电气规格表:

DC SPECIFICATIONS直流电气规格(续)

图3 参数测量信息

图4 typical clear, shift, and clear sequence典型清除、移位和清除时序应用电路:

图5 LCD驱动电路

图6 LED驱动电路

图7 4位数码显示电路

图8 倾角测量电路。

164 为8 位移位寄存器,其主要电特性的典型值如下:

54/74164 185mW 54/74LS164 80mW

当清除端(CLEAR)为低电平时,输出端(QA-QH)均为低电平。

串行数据输入端(A,B)可控制数据。

当A、B任意一个为低电平,则禁止新数据输入,在时钟端(CLOCK)脉冲上升沿作用下Q0 为低电平。

当A、B 有一个为高电平,则另一个就允许输入数据,并在CLOCK 上升沿作用下决定Q0 的状态。

引脚功能:

CLOCK :时钟输入端

CLEAR:同步清除输入端(低电平有效)

A,B :串行数据输入端

QA-QH:输出端

图1 74LS164封装图

图2 74LS164 内部逻辑图

极限值

电源电压7V

输入电压……… 5.5V

工作环境温度

54164………… -55~125℃

74164………… -0~70℃

储存温度……-65℃~150℃

图3 真值表

H-高电平L-低电平X-任意电平

↑-低到高电平跳变

QA0,QB0,QH0 -规定的稳态条件建立前的电平

QAn,QGn -时钟最近的↑前的电平

图4 时序图

建议操作条件

符号参数最小值典型值最大值单位VCC 电源电压 4.75 5 5.25 V VIH 输入高电平电压ViH 2 --V

电气特性

动态特性(TA=25℃)。