EEPROM电路设计原理与工艺分析

- 格式:pdf

- 大小:491.31 KB

- 文档页数:3

EEPROM⼯作原理透彻详解EEPROM(Electrically Erasable Programmable read only memory)即电可擦可编程只读存储器,是⼀种掉电后数据不丢失(不挥发)存储芯⽚。

EERPOM的基本结构有⼏种,这⾥讲解⽐较常⽤的FLOTOX管结构,如下图所⽰:FLOTOX(Floating Gate Tunneling Oxide)MOS管即浮栅隧道氧化层晶体管,它是在标准CMOS⼯艺的基础上衍⽣的技术。

如上图所⽰,在传统的MOS管控制栅下插⼊⼀层多晶硅浮栅,浮栅周围的氧化层与绝缘层将其与各电极相互隔离,这些氧化物的电阻⾮常⾼,⽽且电⼦从浮栅的导带向周围氧化物导带的移动需要克服较⾼的势叠,因此,浮栅中的电⼦泄漏速度很慢,在⾮热平衡的亚稳态下可保持数⼗年。

浮栅延长区的下⽅有个薄氧区⼩窗⼝,在外加强电场的作⽤下漏极与浮栅之间可以进⾏双向电⼦流动,继⽽达到对存储单元的“擦除”与“写⼊”操作。

为强调浮栅周围氧化物的绝缘效果,我们把绝缘层去掉,如下图所⽰,其中的“电⼦”就是我们需要存储的数据:其原理图符号如下所⽰:我们通常利⽤F-N隧道效应(Fowler-Nordheim tunneling)对EEPROM存储单元进⾏“擦除”或“写⼊”操作,简单地说,即FLOTOX管的控制栅极与漏极在强电场的作⽤下(正向或负向),浮栅中的电⼦获得⾜够的能量后,穿过⼆氧化硅层的禁带到达导带,这样电⼦可⾃由向衬底移动(具体细节可⾃⾏参考相关资料,此处不赘述)。

对EEPROM存储单元进⾏“擦除”操作,就是将电⼦注⼊到浮栅中的过程(不要将此处的“擦除”操作与FLASH存储单元中的“擦除”操作弄反了,具体参考FLASH对应⽂章),如下图所⽰:如上图所⽰,将FLOTOX管的源极与漏极接地,⽽控制栅极接⾼压(不⼩于12V),浮栅与漏极之间形成正向强电场,电⼦从漏极通过隧道氧化层进⼊浮栅。

为防⽌存储单元“擦除”(或“写⼊”操作)对其它单元产⽣影响,每个FLOTOX管均与⼀个选通管配对(按照制造⼯艺可分为N管与P管,这⾥我们以N管为例进⾏讲解,P管是类似的),前者就是存储电⼦的单元,⽽后者⽤来选择相应的存储单元的控制位,这种结构导致单位存储⾯积⽐较⼤,因此,EEPROM存储芯⽚的容量通常都不会很⼤。

EEPROM电路设计规范1范围本标准对室内EEPROM电路的电路原理,各器件的参数计算选择,相关技术要求和实际使用中的有关问题进行了阐述。

本标准适用于家用空调国内事业部空调产品的EEPROM电路的设计。

2定义无3总述家用空调的机型比较多,同一款机型经常会共用一套主控板,由于各种机型的参数不一样,所以把该机型的参数写入EEPROM内部,上电时读入主芯片,以及开机工作时写入数据。

具体用途可参考“EEPROM读写程序设计指引”。

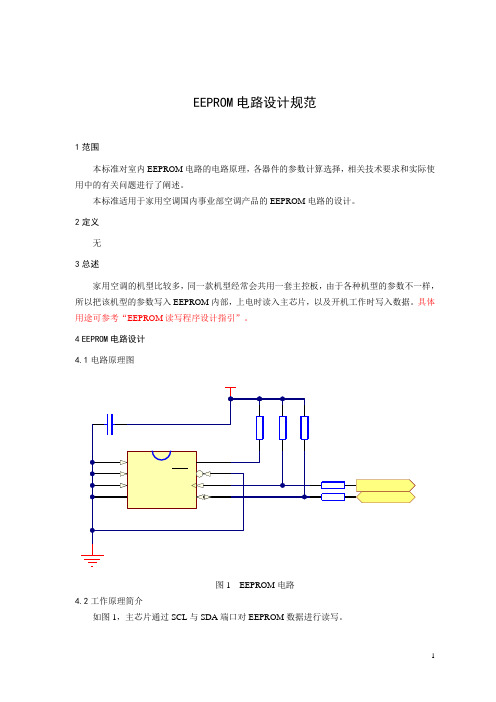

4EEPROM电路设计4.1电路原理图图1 EEPROM电路4.2工作原理简介如图1,主芯片通过SCL与SDA端口对EEPROM数据进行读写。

芯片24C04介绍:图2 24C04芯片管脚图1~3脚:EEPROM地址选择;单个EEPROM时:1~3脚接地;2个EEPROM时:如下图3,IC16第1,第3管脚接地,第2管脚接VCC,IC17第2,第3管脚接地,第1管脚接VCC;图3 2个EEPROM电路(变频室外341EEPROM电路)4脚:电源地端口;5脚:与主芯片通信数据端口;6脚:与主芯片通信时钟端口;7脚:EEPROM写入控制端口,当为“1”时芯片写入禁止,硬件电路上直接接到VCC端;当为“0”时芯片写入使能,硬件电路上直接接地,对于MCU程序自带掉电记忆功能机型需要注意;8脚:电源输入端口,工作电压:ST:2.5v~5.5v;ATMEL:1.8V~5.5v,具体参考芯片功能书。

4.3各元件的作用及元件的选择EEPROM选择:由于变频机室外同时使用2个到EEPROM,必须对EEPROM地址进行设置,所以要求24C04芯片的地址端可供设置,则必须使用ST、A TMEL品牌;上拉电阻R9,R10:如果主芯片对SCL与SDA是开漏输出口,则必须接上拉,上拉电阻阻值根据主芯片可承受的灌电流而定,一般可选用1/6W,10K欧的碳膜电阻或者0805封装的贴片电阻,精度5%以上;室外板341电路EEPROM可选用1/6W,1K欧的碳膜电阻或者0805封装的贴片电阻,精度5%以上;如果主芯片不是使用开漏输出口,则R9,R10可免去;限流电阻R6,R7:由于SCL与SDA上拉高电平,为防止大电流灌入主芯片,故接小电阻限流。

《数字集成电路基础》作业答案第一次作业1、查询典型的TTL与CMOS系列标准电路各自的VIH、VIL、VOH和VOL,注明资料出处。

2、简述摩尔定律的内涵,如何引领国际半导体工艺的发展。

第二次作业1、说明CMOS电路的Latch Up效应;请画出示意图并简要说明其产生原因;并简述消除“Latch-up”效应的方法。

答:在单阱工艺的MOS器件中(P阱为例),由于NMOS管源与衬底组成PN结,而PMOS 管的源与衬底也构成一个PN结,两个PN结串联组成PNPN结构,即两个寄生三极管(NPN 和PNP),一旦有因素使得寄生三极管有一个微弱导通,两者的正反馈使得电流积聚增加,产生自锁现象。

影响:产生自锁后,如果电源能提供足够大的电流,则由于电流过大,电路将被烧毁。

消除“Latch-up”效应的方法:版图设计时:为减小寄生电阻Rs和Rw,版图设计时采用双阱工艺、多增加电源和地接触孔数目,加粗电源线和地线,对接触进行合理规划布局,减小有害的电位梯度;工艺设计时:降低寄生三极管的电流放大倍数:以N阱CMOS为例,为降低两晶体管的放大倍数,有效提高抗自锁的能力,注意扩散浓度的控制。

为减小寄生PNP管的寄生电阻Rs,可在高浓度硅上外延低浓度硅作为衬底,抑制自锁效应。

工艺上采用深阱扩散增加基区宽度可以有效降低寄生NPN管的放大倍数;具体应用时:使用时尽量避免各种串扰的引入,注意输出电流不易过大。

2、什么是器件的亚阈值特性,对器件有什么影响?答:器件的亚阈值特性是指在分析MOSFET时,当Vgs<Vth时MOS器件仍然有一个弱的反型层存在,漏源电流Id并非是无限小,而是与Vgs呈现指数关系,这种效应称作亚阈值效应。

影响:亚阈值导电会导致较大的功率损耗,在大型电路中,如内存中,其信息能量损耗可能使存储信息改变,使电路不能正常工作。

3、什么叫做亚阈值导电效应?并简单画出logI D-V GS特性曲线。

答:GS在分析MOSFET时,我们一直假设:当V GS下降到低于V TH时器件会突然关断。

数字电路总结知识点一、基本原理数字电路是以二进制形式表示信息的电路,它由数字信号和逻辑元件组成。

数字信号是由禄电平、高电平表示的信号,逻辑元件是由逻辑门组成的。

数字电路的设计和分析都是以逻辑门为基础的。

逻辑门是用来执行逻辑函数的元件,比如“与”门、“或”门、“非”门等。

数字电路的基本原理主要包括二进制数制、布尔代数、卡诺图、逻辑函数和逻辑运算等内容。

二进制数制是数字电路中最常用的数制形式,它使用0和1表示数字。

布尔代数是描述逻辑运算的理论基础,它包括基本逻辑运算、逻辑运算规则、逻辑函数、逻辑表达式等内容。

卡诺图是用于简化逻辑函数的图形化方法,它可以简化逻辑函数的表达式,以便进一步分析和设计数字电路。

二、逻辑门逻辑门是数字电路的基本元件,它用来执行逻辑函数。

常见的逻辑门包括与门、或门、非门、异或门、与非门、或非门等。

这些逻辑门都有特定的逻辑功能和真值表,它们可以用于组合成复杂的逻辑电路。

逻辑门的特点有两个,一个是具有特定的逻辑功能,另一个是可以实现逻辑函数。

逻辑门的逻辑功能对应着二进制操作的逻辑运算,它可以实现逻辑的“与”、“或”、“非”、“异或”等功能。

逻辑门的实现是通过逻辑元件的布局和连接来完成的,比如用传输门和与门实现一个或门。

三、组合逻辑电路组合逻辑电路是由逻辑门组成的电路,它执行逻辑函数,但没有存储元件。

组合逻辑电路的特点是对输入信号的变化立即做出响应,并且输出信号仅依赖于当前的输入信号。

常见的组合逻辑电路包括加法器、减法器、多路选择器、译码器等。

加法器是一个重要的组合逻辑电路,它用来执行加法运算。

有半加器、全加器和多位加法器等不同类型的加法器,它们可以实现不同精度的加法运算。

减法器是用来执行减法运算的组合逻辑电路,它可以实现数的减法运算。

多路选择器是一个多输入、单输出的组合逻辑电路,它根据控制信号选择其中的一个输入信号输出到输出端。

译码器是用来将二进制码转换成其它码制的组合逻辑电路,它可以将二进制数码转换成BCD码、七段码等。

一、 简介本应用笔记介绍了GIANTEC 的34系列EEPROM 在应用设计上所需要注意的一些事项。

主要内容包括以下几个方面: 电源供应及复位; 节电设计; 输入输出线路配置; Write Cycle 的检测; 写保护的应用; 34TSC02温度传感器应用; 数据吞吐量; 典型应用的原理图; PCB Layout 的注意事项; 软件的参考设计。

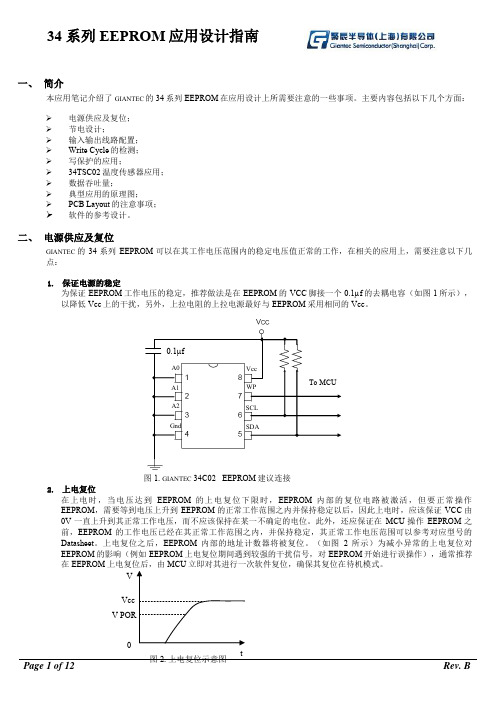

二、 电源供应及复位GIANTEC 的34系列EEPROM 可以在其工作电压范围内的稳定电压值正常的工作,在相关的应用上,需要注意以下几点:1. 保证电源的稳定为保证EEPROM 工作电压的稳定,推荐做法是在EEPROM 的VCC 脚接一个0.1μf 的去耦电容(如图1所示),以降低Vcc 上的干扰,另外,上拉电阻的上拉电源最好与EEPROM 采用相同的Vcc 。

图1. GIANTEC 34C02 EEPROM 建议连接2. 上电复位在上电时,当电压达到EEPROM 的上电复位下限时,EEPROM 内部的复位电路被激活,但要正常操作EEPROM ,需要等到电压上升到EEPROM 的正常工作范围之内并保持稳定以后,因此上电时,应该保证VCC 由0V 一直上升到其正常工作电压,而不应该保持在某一不确定的电位。

此外,还应保证在MCU 操作EEPROM 之前,EEPROM 的工作电压已经在其正常工作范围之内,并保持稳定,其正常工作电压范围可以参考对应型号的Datasheet 。

上电复位之后,EEPROM 内部的地址计数器将被复位。

(如图2所示)为减小异常的上电复位对EEPROM 的影响(例如EEPROM 上电复位期间遇到较强的干扰信号,对EEPROM 开始进行误操作),通常推荐在EEPROMV tSCLSDA Gnd VccWP / A0 A1A2 0.1μf3. 掉电复位掉电复位的效果与上电复位基本相同,但意外的掉电将会对EEPROM 的正常操作产生一定的影响,因此在实际应用中,还需要注意下面所列的几种情况:1) 掉电电压大于MCU 的电压下限,小于EEPROM 的电压下限,此时EEPROM 可能会发生掉电复位,但MCU仍可以照常工作(如图3所示)。

常用串行EEPROM的编程应用EEPROM是"Electrically Erasable Programmable Read-only"(电可擦写可编程只读存储器)的缩写,EEPROM在正常情况下和EPROM一样,可以在掉电的情况下保存数据,所不同的是它可以在特定引脚上施加特定电压或使用特定的总线擦写命令就可以在在线的情况下方便完成数据的擦除和写入,这使EEPROM被用于广阔的的消费者范围,如:汽车、电信、医疗、工业和个人计算机相关的市场,主要用于存储个人数据和配置/调整数据。

EEPROM又分并行EEPROM和串行EEPROM,并行EEPROM器件虽然有很快的读写的速度,但要使用很多的电路引脚。

串行EEPROM器件功能上和并行EEPROM基本相同,提供更少的引脚数、更小的封装、更低的电压和更低的功耗,是现在使用的非易失性存储器中灵活性最高的类型。

串行EEPROM按总线分,常用的有I2C,SPI,Microwire总线。

本文将介绍这三种总线连接单片机的编程方法。

I2C总线I2C总线(Inter Integrated Circuit内部集成电路总线)是两线式串行总线,仅需要时钟和数据两根线就可以进行数据传输,仅需要占用微处理器的2个IO引脚,使用时十分方便。

I2C总线还可以在同一总线上挂多个器件,每个器件可以有自己的器件地址,读写操作时需要先发送器件地址,该地址的器件得到确认后便执行相应的操作,而在同一总线上的其它器件不做响应,称之为器件寻址,这个原理就像我们打电话的原理相当。

I2C总线产生80年代,由PHLIPS 公司开发,早期多用于音频和视频设备,如今I2C总线的器件和设备已多不胜数。

最常见的采用I2C总线的EEPROM也已被广泛使用于各种家电、工业及通信设备中,主要用于保存设备所需要的配置数据、采集数据及程序等。

生产I2C总线EEPROM的厂商很多,如ATMEL、Microchip公司,它们都是以24来开头命名芯片型号,最常用就是24C系列。

• 118•本文设计了一种应用于EEPROM的片内高压电荷泵电路。

该电路基于Dickson电荷泵结构,用二极管连接的nMOS管代替二极管,通过加入预充管并提高最高输出电压以减少电压上升时间,在3.3V电源电压下得到最高21V的输出电压。

该电路基于SMIC 0.18um 2P4M 工艺设计,由cadence软件仿真实现。

随着社会的进步,物联网的蓬勃发展,半导体存储技术迎来了黄金时期。

其中,EEPROM (电可擦可编程只读存储器)因其接口少、功耗低、存储可靠、价格低廉等优点,在非易失性半导体存储器件领域发挥着重要作用。

然而,EEPROM 进行擦写操作所需的电压在15V 以上,远高于芯片工作的电源电压,因此需要额外的片内升压电路来保证EEPROM 的正常工作。

电荷泵作为一种常用的升压电路,其基本原理是利用电荷在电容器上的积累效应产生高于电源电压或负电压的电路。

相较于传统开关电容式升压电路,电荷泵电路有着功耗低,面积小,易于集成等优点,因此普遍应用于串口通信,EEPROM ,动态随机读写等领域。

多数电荷泵结构都基于Dickson 电荷泵,传统Dickson 电荷泵使用二极管传导电荷,但是为了便于片内集成,目前主流Dickson 电荷泵都会使用栅极与漏极短接的nMOS 晶体管代替二极管。

但是随着电压的升高,体效应会导致MOS 管的阈值电压的升高,电荷泵的输出电压会因此降低。

通过增加电荷泵级数得到目标电压,会导致电荷泵效率降低,升压速度变慢。

针对以上问题,本文设计了一种改进型Dickson 电荷泵,以保证电荷泵在较短的升压时间和较高的效率下得到高压。

1 传统Dickson电荷泵工作原理传统Dickson 电荷泵结构如图1所示,其中C1,C2~Cn 为充电电容,CL 为负载电容;CLK 与CLK_是不交叠且反向的时钟信号,幅值一般为电源电压;M1,M2~Mn 是二极管连接的nMOS 管,衬底均接地。

电路启动后,电源Vin 通过M1对C1充电,直到C1两端电压为VDD-Vth 后停止充电,Vth 为nMOS 管阈值电压(忽略体效应)。

微 处 理 机M I CROPROCE SSORSEEP ROM 电路设计原理与工艺分析刘丽娜,程显侠,刘宝娟(中国电子科技集团公司第四十七研究所,沈阳110032)摘 要:EEPROM (electrica lly erasable ,prog ra mm ab le ,read-only m e m ory),是一种电可擦除可编程只读存储器电路,它具有易于使用、价格低廉等特点。

由于它的可编程特性,加上能以非常低的成本获得,因此,几乎在每一种电子产品中都可见到EEPROM 的身影,是目前业界使用最普遍的非易失性存储器之一。

介绍了EEPROM 电路的设计原理与生产工艺,并对其中的关键技术进行了分析。

关键词:可擦除;可编程;存储器中图分类号:TN 47文献标识码:B文章编号:1002-2279(2008)03-0037-02The Anal ysis of Theory and T echn i cs of EEPROM C ircu itLIU L i-na ,C HENG X ian-x ia ,LIU Bao-juan(T he 47th Research Instit ute of Ch i na E lectronics T echnology Group Corporation ,Shenyang 110032,Ch i na)Abstract :EEPROM (e lectrica ll y erasab le ,progra mm able ,read -on l y m e m ory ),is a m e m oryc ircuit of e lectric erasable and read -on ly .It is prone to use and its price is cheap .Because of its progra mm ab le and cheap cos,t it is a l m ost used in each kind of e l e ctronic produc.t It is universal one o f nonvo latile m e m ory used i n se m iconductor fie l d no w .The arti c le introduces EEPROM electrocircuit 's desig n princ i p le and production craf,t m eanwh ile ananlyzes its pivo tal techniquei n si d e .K ey w ords :E rasable ;Prog ra mm ab le ;M e m ory1 引 言存储器是一种能存放数据和程序的器件,是计算机的主要部件,在许多电子设备中,它是必不可少的。

存储芯片是I C 市场的支柱产品,也是用量最多的VLSI 器件。

随着集成电路技术的飞速发展,存储芯片的集成度、容量、可靠性得到了很大的提高,EEPRO M 制造技术也进一步成熟,由于EEPROM 存储器可以用电学方法在线将存储内容一次全部擦除,或者按字节擦除,然后再重新写入,与EPROM 相比,其存储单元所需的写入和擦除的能量低,擦写和读取的速度快,而且能在线擦写。

另外,新一代的EEPRO M 已将编程所需的高电压发生器由片外置入片内,所以芯片只需单电源供电,因而广泛应用于整机及通讯系统中。

2 EEPROM 设计原理2.1 EEPRO M 的分类目前,市场上的EEPROM 主要有串行接口EEPROM 和并行接口EEPROM 两种产品。

2.1.1 串行接口EEPROM串行接口EEPROM 是目前使用的非易失性存储器中灵活性最高的类型。

与其它NVM 比较,串行接口EEPROM 器件提供更少的引脚数,更小的封装,更低的电压和更低的功耗。

串行接口的EEPROM 被用于电子行业的各个领域,包括汽车,电信,医疗,工业和个人计算机等相关市场。

主要用于存储个人优先数据和配置/调整数据。

其主要的内部结构如图1所示。

其管脚说明如表1所示。

表1 串行接口EEPROM 管脚说明A 0-A1地址输入端口SDA 双向串行数据端口SCL 串行时钟输入端口W P 写保护端口NC悬空端口作者简介:刘丽娜(1979-),女,辽宁省锦州市人,学士,助工,主研方向:计算机及电路设计。

收稿日期:2007-06-19第3期2008年6月No .3Jun.,2008图1 串行接口EEPROM 结构框图2.1.2 并行接口EEPROM并行接口EEPROM 是非易失性数据存储器系列中具有高度灵活性的成员。

并行EEPROM 的特点是编程时间长,数据保留时间长和高可靠的实现以字节或扇区为单位的存储数据的更新,并且比串行接口协议更快。

并行接口EEPROM 被广泛地使用,包括电信、航空电子和军事应用。

其主要的内部结构如图2所示。

图2 并行接口EEPROM 结构框图其管脚说明如表2所示。

表2 并行接口EEPROM 管脚说明引出端号符号功能12、11、10、9、8、7、6、5、27、26、23、25、4、28、29、3、2A 0~A 16地址(I)13、14、15、17、18、19、20、21I O /0~I O /7数据端口(I /O ) 22CE片选允许(I) 24OE 输出允许(I) 31W E 写允许(I)32V DD 电源 16V SS 地 10、30NC悬空端综上所述:串行接口EEPROM 与并行接口EEPRO M 在结构和工作方式上区别很大,但是,其设计原理基本相同。

我们将以并行接口EEPROM 为例,介绍其设计原理及设计中需要注意的问题。

2.2 EEPROM 的设计EEPROM 电路的设计主要包括存储单元电路的设计和外围电路的设计,外围电路主要包括片上高压产生电路,高压调整电路,高灵敏度放大器电路,锁存器电路,编程电路,擦除电路,命令译码电路、数据转换电路,时序产生、控制电路,输入、输出电路。

存储单元电路的设计是EEPROM 电路设计中最重要的部分,它关系到电路的工作方式,电路的稳定性,更是外围电路设计的基础,设计时应考虑以下几点:(1)根据存储单元的工作特性及版图面积的大小,确定阵列的布局,定义存储单元的访问地址。

(2)合理计算存储单元各引出端的负载,位线的漏电流和写/擦电流值等。

(3)与存储单元相连的高压管,特别是传输管,在传输过程中应尽量使高压无损失。

(4)增添适量的冗余单元可以提高芯片可靠性,延长芯片使用寿命。

外围电路的设计主要包括:(1)高压产生电路的设计EEPROM 存储器写操作的质量和加在存储单元上的高压密切相关,0和1两个状态的阈值电压差值也由该高压控制,同时读出时间、数据的保持能力以及保持时间都受该高压的影响。

因此,设计时在保证效率和速度的前提下,要提供足够大的输出电压和输出电流,并且输出电压的波动要小。

(2)读取电路的设计读取电路中,灵敏放大器的预充电流必须不受任何阻滞,所以,位线译码器件的尺寸不能太小,否则它的有效电阻会限制速度。

此外,读出速度还受字线充放电速度的影响。

3 EEPROM 工艺分析由于EEPRO M 电路含有存储单元和高压电路,给工艺带来一定的难度。

所以在工艺加工时要严格控制工艺质量,如氧化层质量、多晶硅的光刻与腐蚀、注入的能量与剂量等,调整工艺参数,如开启电压、源漏击穿电压等,尽可能从工艺上消除器件的不稳定因素。

3.1 超薄Si O 2介质生长技术S i O 2介质的性能直接影响到EEPRO M 电路的耐久性和保持性,S i O 2介质厚度及质量是EEPROM 工艺的关键,减小隧道氧化层的厚度可提高编程电压,提高电路的编程效率,(下转第42页)验证[5]。

软硬件协同验证主要验证软件能否在期望的硬件电路上正确运行,即验证软件与硬件之间的接口能否正常工作。

验证的方法是用V eril o g 、C 和汇编语言建模,搭建验证平台,将测试程序通过编译器生成二进制文件,导入存储器模型中,如图3所示。

两个子系统有各自的编译器,可以实现对外部空间存取的真实模拟,包括指令和数据的存储空间映射等完全与微处理器实际的执行情况一致。

系统通过E M C 读入并执行目标代码,产生期望的系统行为。

仿真过程中监控器实时监测系统的行为。

图3 软硬件协同原理FPGA 原型验证是ASI C 验证中的关键环节,现有资源是V irtex -II 的XC2V6000FF1152型号FPGA 器件。

本设计规模庞大,一个FPGA 器件无法装下整个系统,需把整个设计划分为两个部分,下载到两个FPGA 器件中。

如图1中虚线所示,虚线框以内的部分做为一个整体,综合布局布线后生成比特流文件下载到一个FPGA 器件里,虚线框以外的部分做为另一个整体生成比特流文件下载到第二个FPGA 器件里。

在FPGA 的硬件平台上通过大量应用程序对设计进行在线调试,验证了设计功能的正确性。

4 结束语本文给出的异构型双核平台的RTL 代码全部用Verilog 建模,搭建了验证平台,通过软硬件协同验证和FPGA 原型验证的方法验证了功能的正确性,采用S M I C 0.18 m C MOS 工艺进行逻辑综合,规模为232.4万等效门,系统工作频率为100MH z 。

参考文献:[1] 黄光奇,周兴铭.单芯片多处理器的性能优势[J].计算机工程与科学,2001,23(1):35-38.[2] 蒋江,张民选.多处理器芯片体系结构研究[J].微电子学与计算机,1998(4):1-6.[3] AM BATM specificati on[S].R ev isi on 2.0,1999-05.[4] Jan i ck Bergeron .W R I T I NG T ESTBEN C HES :functiona lver ifi cati on o f HDL m ode ls[M ].KLUW ER ACADE M I C PU BL IS H ERS ,Boston D ordrechtl L ondon ,2000.[5] Y uM i ngyan ,X i e X ue j un ,W ang Ji nx iang ,e t a.l Parte rre :an A pp licati on-G enera l SoC P l a tfor m [C ].Internationa l Conference on A SIC ,Be iji ng ,Ch i na ,2003.(上接第38页)但在减小隧道氧化层厚度的同时要考虑到直接隧道效应电荷泄漏限制及工艺加工难度的要求,因而在工艺中采用提高氧化温度、稀释氧化等方法,严格控制生长速率,从而获得理想的高质、超薄S i O 2介质层,确保器件具有良好的保持特性和较高的编程/擦除次数。