福州大学集成电路应用实验二-参考模板

- 格式:doc

- 大小:308.50 KB

- 文档页数:6

西安邮电大学集成电路版图设计实验报告学号:XXX姓名:XX班级:微电子XX日期:20XX目录实验一、反相器电路的版图验证1)反相器电路2)反相器电路前仿真3)反相器电路版图说明4)反相器电路版图DRC验证5)反相器电路版图LVS验证6)反相器电路版图提取寄生参数7)反相器电路版图后仿真8)小结实验二、电阻负载共源放大器版图验证9)电阻负载共源放大器电路10)电阻负载共源放大器电路前仿真11)电阻负载共源放大器电路版图说明12)电阻负载共源放大器电路版图DRC验证13)电阻负载共源放大器电路版图LVS验证14)电阻负载共源放大器电路版图提取寄生参数15)电阻负载共源放大器电路版图后仿真16)小结实验一、反相器电路的版图验证1、反相器电路反相器电路由一个PMOS、NPOS管,输入输出端、地、电源端和SUB 端构成,其中VDD接PMOS管源端和衬底,地接NMOS管的漏端,输入端接两MOS管栅极,输出端接两MOS管漏端,SUB端单独引出,搭建好的反相器电路如图1所示。

图1 反相器原理图2、反相器电路前仿真通过工具栏的Design-Create Cellview-From Cellview将反相器电路转化为symbol,和schemetic保存在相同的cell中。

然后重新创建一个cell,插入之前创建好的反相器symbol,插入电感、电容、信号源、地等搭建一个前仿真电路,此处最好在输入输出网络上打上text,以便显示波形时方便观察,如图2所示。

图2 前仿真电路图反相器的输入端设置为方波信号,设置合适的高低电平、脉冲周期、上升时间、下降时间,将频率设置为参数变量F,选择瞬态分析,设置变量值为100KHZ,仿真时间为20u,然后进行仿真,如果仿真结果很密集而不清晰可以右键框选图形放大,如图3所示。

图3 前仿真结果3、反相器电路版图说明打开之前搭建好的反相器电路,通过Tools-Design Synthesis-Laout XL新建一个同cell目录下的Laout文件,在原理图上选中两个MOS管后在Laout中选择Create-Pick From Schematic从原理图中调入两个器件的版图模型。

班级:XX姓名:XXX学号:XXXXXX指导老师:XXX实验日期:XXXX年XX月XX日一、实验目的1. 理解集成电路的基本组成和工作原理。

2. 掌握基本的集成电路设计方法,包括原理图设计、版图设计、仿真分析等。

3. 学习使用集成电路设计软件,如Cadence、LTspice等。

4. 通过实验加深对集成电路理论知识的理解,提高动手能力和问题解决能力。

二、实验内容本次实验主要包括以下内容:1. 原理图设计:使用Cadence软件绘制一个简单的CMOS反相器原理图。

2. 版图设计:根据原理图,使用Cadence软件进行版图设计,并生成GDSII文件。

3. 仿真分析:使用LTspice软件对设计的反相器进行仿真分析,测试其性能指标。

4. 版图与原理图匹配:使用Cadence软件进行版图与原理图的匹配,确保设计正确无误。

三、实验步骤1. 原理图设计:- 打开Cadence软件,选择原理图设计模块。

- 根据反相器原理,绘制相应的电路符号,包括NMOS和PMOS晶体管、电阻和电容等。

- 设置各个元件的参数,如晶体管的尺寸、电阻和电容的值等。

- 完成原理图设计后,保存文件。

2. 版图设计:- 打开Cadence软件,选择版图设计模块。

- 根据原理图,绘制晶体管、电阻和电容的版图。

- 设置版图规则,如最小线宽、最小间距等。

- 完成版图设计后,生成GDSII文件。

3. 仿真分析:- 打开LTspice软件,选择仿真模块。

- 将GDSII文件导入LTspice,生成对应的原理图。

- 设置仿真参数,如输入电压、仿真时间等。

- 运行仿真,观察反相器的输出波形、传输特性和功耗等性能指标。

4. 版图与原理图匹配:- 打开Cadence软件,选择版图与原理图匹配模块。

- 将原理图和版图导入匹配模块。

- 进行版图与原理图的匹配,检查是否存在错误或不一致之处。

- 修正错误,确保版图与原理图完全一致。

四、实验结果与分析1. 原理图设计:- 成功绘制了一个简单的CMOS反相器原理图,包括NMOS和PMOS晶体管、电阻和电容等元件。

实验1——积分器和微分器(μA741)【实验目的】(1)学会用集成运放设计积分器和微分器,熟悉电路原理和元件参数的计算。

(2)熟悉积分器和微分器的特点、性能,并会应用。

【实验仪器】•万用表,示波器,信号发生器,•“集成电路原理及应用”实验箱【实验原理】1. μA741芯片简介•μA741是第二代集成运放的典型代表•是采用硅外延平面工艺制作的单片式高增益运放。

•其特点是:•采用频率内补偿•具有短路保护功能•具有失调电压调整能力•具有很高的输入差模电压和共模电压范围•无阻塞现象,功耗较低,电源电压适应范围较宽•有很宽的输入共模电压范围,不会在使用中出现“阻塞”•在诸如积分电路、求和电路及一般的反馈放大电路中使用,均不需外加补偿电容。

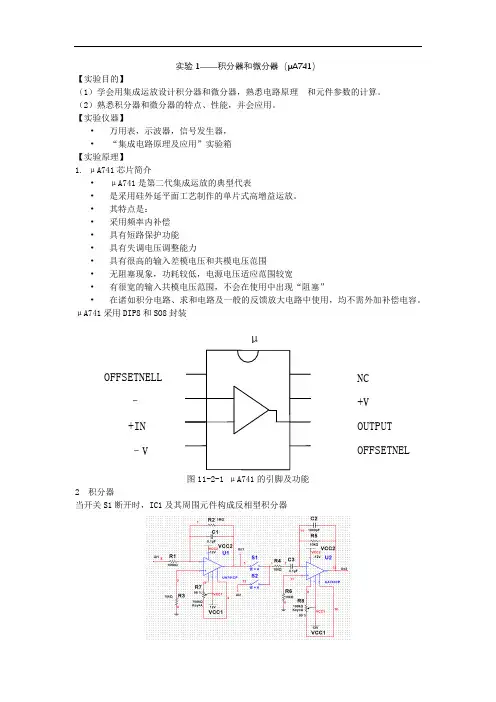

μA741采用DIP8和SO8封装图11-2-1 μA741的引脚及功能2 积分器当开关S1断开时,IC1及其周围元件构成反相型积分器+IN–OFFSETNELLμOFFSETNEL –VNC+VOUTPUT• 积分器• 广泛应用于扫描电路、A/D 转换和模拟运算等方面。

其输出电压和输入电压的积分成线性关系。

• 输出电压与输入电压的关系为tt u C R t u )d (1)(i111o1⎰-=3 微分器当开关S1断开、S2闭合时,IC2及其周围元件构成反相型微分器。

图11-2-2 积分器和微分器电路原理图• 微分器• 其输出电压和输入电压的微分成线性关系,广泛应用于波形变换和模拟运算等方面。

• 输出电压与输入电压的关系为t u C R t u t d d )()(i225o2-=4 积分器和微分器当开关S2断开、S1闭合时,IC1、IC2及其周围元件构成积分器和微分器。

图11-2-2 积分器和微分器电路原理图【实验内容】1. 电路设计与仿真•参照图11-2-2设计积分器和微分器。

•用Multisim 软件对积分器和微分器电路进行仿真。

2. 积分器(1)将开关S1断开。

集成电路实验报告第一篇:集成电路实验报告集成电路实验报告班级:姓名:学号:指导老师:实验一:反相器的设计及反相器环的分析一、实验目的1、学习及掌握cadence图形输入及仿真方法;2、掌握基本反相器的原理与设计方法;3、掌握反相器电压传输特性曲线VTC的测试方法;4、分析电压传输特性曲线,确定五个关键电压VOH、VOL、VIH、VIL、VTH。

二、实验内容本次实验主要是利用 cadence 软件来设计一基本反相器(inverter),并利用仿真工具Analog Artist(Spectre)来测试反相器的电压传输特性曲线(VTC,Voltage transfer characteristic curves),并分析其五个关键电压:输出高电平VOH、输出低电平VOL、输入高电平VIH、输入低电平VIL、阈值电压 VTH。

三、实验步骤1.在cadence环境中绘制的反相器原理图如图所示。

2.在Analog Environment中,对反相器进行瞬态分析(tran),仿真时间设置为4ns。

其输入输出波形如图所示。

分开查看:分析:反相器的输出波形在由低跳变到高和由高跳变到底时都会出现尖脉冲,而不是直接跳变。

其主要原因是由于MOS管栅极和漏极上存在覆盖电容,在输出信号变化时,由于电容储存的电荷不能发生突变,所以在信号跳变时覆盖电容仍会发生充放电现象,进而产生了如图所示的尖脉冲。

3.测试反相器的电压传输特性曲线,采用的是直流分析(DC),我们把输入信号修改为5V直流电源,如图所示。

4.然后对该直流电源从0V到5V进行线性扫描,进而得到电压传输特性曲线如图所示。

5.为反相器创建symbol,并调用连成反相器环,如图。

6.测量延时,对环形振荡器进行瞬态分析,仿真时间为4ns,bcd 节点的输出波形如图所示。

7.测量上升延时和下降延时。

(1)测量上升延时:可以利用计算器(calculator)delay函数来计算信号c与信号b间的上升延时和下降延时如图所示。

《集成电路应用》课程实验实验一 4053门电路综合实验学院:物理与信息工程学院专业: 电子信息工程年级: 2015级姓名:张桢学号:指导老师:许志猛实验一4053门电路综合实验一、实验目的:1.掌握当前广泛使用的74/HC/HCT系列CMOS集成电路、包括门电路、反相器、施密特触发器与非门等电路在振荡、整形、逻辑等方向的应用。

2.掌握4053的逻辑功能,并学会如何用4053设计门电路。

3.掌握多谐振荡器的设计原理,设计和实现一个多谐振荡器,学会选取和计算元件参数。

二、元件和仪器:1.CD4053三2通道数字控制模拟开关2.万用表3.示波器4.电阻、电容三、实验原理:1.CD4053三2通道数字控制模拟开关CD4053是三2通道数字控制模拟开关,有三个独立的数字控制输入端A、B、C和INH输入,具有低导通阻抗和低的截止漏电流。

幅值为4.5~20V的数字信号可控制峰-峰值至20V的数字信号。

CD4053的管脚图和功能表如下所示4053引脚图CD4053真值表根据CD4053的逻辑功能,可以由CD4053由4053电路构成如下图所示8种逻辑门(反相器与非门或非门、反相器、三态门、RS 触发器、——RS 触发器、异或门等)。

输入状态 接通通道])2)(()(ln[T DD T DD T DD T V V V V V V V RC T -+--=2.多谐振荡器的设计非门作为一个开关倒相器件,可用以构成各种脉冲波形的产生电路。

电路的基本工作原理是利用电容器的充放电,当输入电压达到与非门的阈值电压VT 时,门的输出状态即发生变化。

因此,电路输出的脉冲波形参数直接取决于电路中阻容元件的数值。

可以利用反相器设计出如下图所示的多谐振荡器这样的多谐振荡器输出的信号周期计算公式为:当R S ≈2R 时,若:VT=0.5VDD ,对于HC 和HCU 型器件,有T ≈2.2RC对于HCT 型器件,有T ≈2.4RC 四、实验内容:1. 验证CD4053的逻辑功能,用4053设计门电路,并验证其逻辑功能:(1)根据实验原理设计如下的反相器电路图:(2)在面包板上连接电路。

集成电路分析与设计实验报告班号:_________学号:_____姓名:___成绩:___________________完成日期:年月目录实验2:Linux环境下基本操作 (1)实验3:RTLCompiler对数字低通滤波器电路的综合 (3)实验4: NC对数字低通滤波器电路的仿 (6)实验2:Linux环境下基本操作集成电路设计发展过程中,EDA工具对设计效率的提高起到了巨大推动作用,继而成为现代集成电路设计中不可或缺的一环。

用于集成电路设计的EDA工具多数基于UNIX、Solaris、linux平台。

为了帮助同学学习和使用基于此类平台的集成电路EDA 工具,本实验介绍了linux下的基本操作、命令等。

本实验是实验3和实验4的必要组成部分。

实验中主要对命令行模式下的linux基本操作作了介绍。

命令行模式简单易行,是理解基于脚本的高效率使用EDA工具的方法的基础。

一、目的:1. 熟悉linux文件、目录管理命令;2. 熟悉linux文件链接命令;3. 熟悉linux下文件编辑命令。

二、实验设备与软件集成电路设计终端Linux RedHat 9三、实验内容和步骤1. 系统登陆启动计算机,选择启动linux输入用户名:cdsuser,输入密码:cdsuser至此,完成系统启动,并作为用户cdsuser登录一下简述各种操作。

2. 创建终端和工作文件夹在桌面区域单击右键,选择New Terminal,至此进入命令行模式(可根据需要打开多个)键入察看当前目录命令:pwd ↙说明:此时出现的是当前用户的根文件夹路径。

路径指的是一个文件夹或文件在系统中的位置。

Linux根路径为“/”;当前路径为“./”; 当前路径的上一级路径为“../”。

使用从根路径开始的路径名称成为绝对路径,如“/home/holygun/”。

利用“../”,“./”等方式定义的路径名称成为相对路径,如“../holygun/”。

键入察看当前目录文件命令:ls↙说明:此时列出的是当前目录下的文件和子文件夹列表键入创建文件夹命令:mkdir [学号]↙说明:以你的学号为名建立工作文件夹,所有实验工作应在此文件夹中完成。

《现代集成电路及应用》实验报告学院:班级:学号:姓名:专业:指导教师:实验日期:2012/6/12二○一四年六月十二日实验一Multisim 基本操作1.1放置基本元件(1)放置500欧姆、10K 、1M 电阻 (2)放置20pF 、0.1uF 、10uF 电容 (3)放置二极管(4)放置一个直流5V 电源和地 (5)放置一个5V ,1kHz 的信号源C120pF C2100nFC310uFR11MΩR210kΩR3500ΩDIODE_VIRTUALV15 VV25 Vrms 1kHz0°图一放置基本元器件2.2使用基本测试设备函数发生器和示波器将信号发生器和示波器连接在一起。

a.调节信号发生器的信号频率为1kHz。

b. 调节信号发生器的信号分别为正弦波、三角波,方波。

观察波形c. 调节示波器的时间轴,清楚显示一个周期完整波形。

2.3万用表按照下图连接,分析万用表显示结果是否正确。

万用表使用(1). 二极管仿真电路实验目的:1. 掌握multisim元件的查找,放置,参数调整。

2. 掌握信号源和示波器的设置,连接与结果显示。

(2). 稳压管仿真电路稳压二极管测试电路(3). RC 高通电路XBP1使用波特图仪观察幅频特性(5).共射放大电路实验一Multisim基本操作实验二集成运放的线性应用2.1 在图2.1反相比例运算电路中,R1=10KΩ RF=500KΩ,问R2的阻值应为多大。

若输入信号为10mV,用示波器测出输出信号的大小。

图2.1这是个标准的反相比例运算放大器Rif=R1//Rf Avf=-Rf/R1 平衡电阻为R22.2在Multisim仿真平台上设计一个同相比例运算电路,若输入信号为10mV,放大倍数为100倍,用示波器观察输入、输出信号波形的相位,并测出输出电压。

2.3已知ui1=1V,ui2=2V,ui3=3V,ui4=4V,R1= R2=2 KΩ,R3= R4=RF=1 KΩ,试测出uo。

实验二使用S-Edit设计简单逻辑电路一、实验目的1.进一步熟悉Tanner Pro 软件中S-Edit 软件的使用;2.了解和掌握用S-Edit 设计简单逻辑电路的流程和方法,并能自行设计简单逻辑电路;3.充分理解电路设计模式(Schematic Mode)和符号模式(Symbol Mode)。

二、实验仪器计算机一台三、实验原理本实验使用S-Edit设计简单逻辑电路,因此要求学生在上节课学习S-Edit 软件使用的基础上,还要熟悉简单逻辑电路CMOS反相器、与非门以及或非门等。

四、实验内容1.使用S-Edit编辑CMOS反相器电路图及符号图;2.使用S-Edit编辑CMOS与非门电路图及符号图;3.使用S-Edit编辑CMOS或非门电路图及符号图。

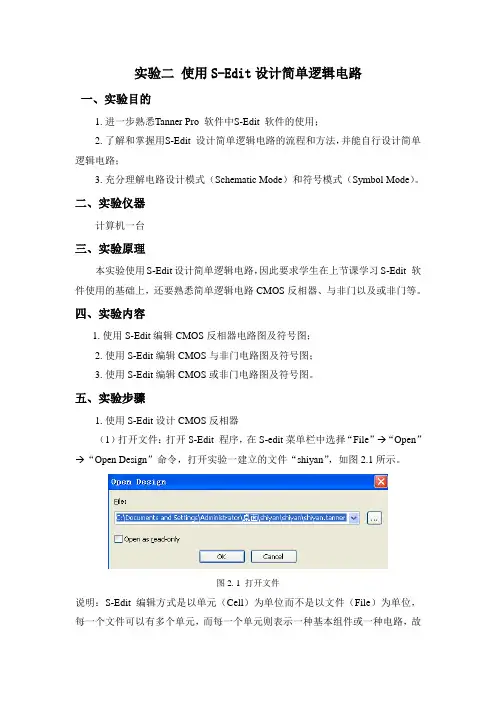

五、实验步骤1.使用S-Edit设计CMOS反相器(1)打开文件:打开S-Edit 程序,在S-edit菜单栏中选择“File”→“Open”→“Open Design”命令,打开实验一建立的文件“shiyan”,如图2.1所示。

图2. 1 打开文件说明:S-Edit 编辑方式是以单元(Cell)为单位而不是以文件(File)为单位,每一个文件可以有多个单元,而每一个单元则表示一种基本组件或一种电路,故一个文件内可能包含多种组件或多个电路。

(2)新建单元:选择“Cell”→“New view”命令,建立新的单元,命名为“INV”,并将View type选择为Schematic,如图2. 2所示。

图2. 2 新建电路设计单元说明:S-Edit 编辑方式是以单元(Cell)为单位而不是以文件(File)为单位,每一个文件可以有多个单元,而每一个单元则表示一种基本组件或一种电路,故一个文件内可能包含多种组件或多个电路。

因此本实验建立的电路单元与实验一的组件单元在同一个文件下。

(3)增加必要元件库:S-Edit本身附有多个元件库,分别是Devices、LogicGates、Misc、SPICE_Commands、SPICE_Elements和IO_Pads等。

最新模电实验二实验报告实验目的:1. 理解并掌握模拟电子技术中的基本概念和原理。

2. 学习使用常见的模拟电子实验仪器和设备。

3. 通过实验验证基本的模拟电路设计和分析方法。

4. 培养学生的动手能力和解决实际问题的能力。

实验内容:1. 设计并搭建基本的放大电路,包括共射放大器、共集放大器和共基放大器。

2. 测量并记录不同配置下放大器的输入阻抗、输出阻抗、增益和频率响应。

3. 实验中使用示波器观察放大器对不同输入信号的响应特性。

4. 搭建滤波电路,包括低通、高通、带通和带阻滤波器,并测量其频率特性。

5. 分析实验数据,与理论值进行比较,探讨误差来源。

实验设备和材料:1. 模拟电子技术实验箱。

2. 示波器。

3. 万用表。

4. 信号发生器。

5. 电阻、电容、二极管、晶体管等基本电子元件。

实验步骤:1. 根据实验指导书的要求,正确连接电路元件,搭建放大电路。

2. 调整信号发生器,产生所需频率和幅度的输入信号。

3. 使用示波器观察并记录放大器的输出波形,调整电路直至达到预期效果。

4. 改变电路配置,重复步骤2和3,测量不同放大器类型的特性。

5. 搭建滤波电路,并使用示波器和信号发生器测试其性能。

6. 使用万用表测量电路的输入阻抗、输出阻抗和增益。

7. 记录所有实验数据,并进行整理分析。

实验结果与分析:1. 列出实验中测量到的输入阻抗、输出阻抗、增益等参数,并与理论值进行对比。

2. 分析滤波电路的频率响应特性,验证其设计的有效性。

3. 讨论实验中遇到的问题及其解决方案,分析可能的误差来源。

4. 根据实验结果,提出改进电路设计的建议。

结论:通过本次实验,我们成功地搭建并测试了不同类型的放大器和滤波电路。

实验结果与理论预测相符,验证了模拟电路设计的基本原理。

同时,实验过程中遇到的问题和挑战也加深了我们对模拟电子技术的理解。

通过动手实践,我们的实验技能和问题解决能力得到了提升。

最新数字电路实验二实验报告实验目的:1. 理解并掌握数字电路的基本组成原理和工作原理。

2. 学习使用数字逻辑分析仪进行电路测试和故障诊断。

3. 通过实验加深对组合逻辑和时序逻辑电路设计的理解。

实验内容:1. 设计并搭建一个4位二进制加法器电路。

2. 实现一个简单的数字时钟电路,能够显示时、分、秒。

3. 使用数字逻辑分析仪检测电路的功能和时序。

实验设备:1. 数字逻辑分析仪2. 示波器3. 集成电路芯片(如74LS系列)4. 面包板5. 跳线实验步骤:1. 根据实验指导书,选择合适的逻辑门芯片,设计4位二进制加法器电路。

2. 在面包板上搭建电路,并使用跳线连接逻辑门。

3. 利用数字逻辑分析仪检查电路的输入输出情况,确保电路正确实现二进制加法功能。

4. 设计数字时钟电路,包括计数器、分频器和显示模块。

5. 同样在面包板上搭建数字时钟电路,并进行测试,调整电路以确保时间显示准确无误。

6. 再次使用数字逻辑分析仪,观察时钟电路的时序关系和稳定性。

实验结果:1. 成功搭建了4位二进制加法器电路,并通过测试,验证了其加法功能。

2. 数字时钟电路运行正常,能够准确显示时间,并通过逻辑分析仪确认了其稳定的时序关系。

实验分析:1. 在实验过程中,发现加法器电路在处理进位时存在延迟,通过优化电路布局和选择合适的逻辑门芯片,成功解决了问题。

2. 数字时钟电路的分频部分需要精确的电阻和电容值,实验中通过调整这些元件的参数,确保了时钟的准确性。

实验结论:通过本次实验,加深了对数字电路设计和测试的理解,特别是在组合逻辑和时序逻辑方面的应用。

同时,也提高了使用数字逻辑分析仪进行电路分析和问题诊断的能力。

一、实训背景与目的随着信息技术的飞速发展,集成电路(IC)已经成为现代电子设备的核心部件。

为了提高学生对集成电路技术的理解和应用能力,我们于2023年秋季学期开展了为期两周的集成电路技术应用实训。

本次实训旨在通过理论与实践相结合的方式,让学生深入了解集成电路的基本原理、设计方法、制造工艺以及在实际应用中的挑战和解决方案。

二、实训内容与安排本次实训共分为两个阶段:线上理论学习和线下实操训练。

线上理论学习阶段1. 集成电路基础知识:介绍了集成电路的发展历程、分类、基本结构以及工作原理。

2. 数字电路设计:学习了数字逻辑门、组合逻辑电路、时序逻辑电路等基本概念和设计方法。

3. 模拟电路设计:介绍了模拟电路的基本元件、放大器、滤波器等设计原理。

4. 集成电路制造工艺:了解了集成电路制造的基本流程,包括硅片制备、光刻、蚀刻、离子注入、扩散等。

线下实操训练阶段1. 集成电路设计与仿真:使用Multisim软件进行数字电路和模拟电路的设计与仿真。

2. 集成电路版图设计:使用Cadence软件进行集成电路版图设计,包括布局、布线、DRC等。

3. 集成电路封装与测试:学习集成电路封装的基本原理和测试方法。

4. 集成电路应用案例分析:分析实际应用中的集成电路设计案例,了解集成电路在不同领域的应用。

三、实训过程与成果1. 线上理论学习阶段在理论学习阶段,我们通过在线视频课程、教材阅读和小组讨论等方式,深入学习了集成电路的相关知识。

学生们对集成电路的基本原理和应用有了更深刻的理解,为后续的实操训练打下了坚实的基础。

2. 线下实操训练阶段在实操训练阶段,学生们分组进行集成电路设计与仿真、版图设计、封装与测试等实践项目。

以下是部分实训成果:- 数字电路设计与仿真:学生们成功设计并仿真了一个简单的数字逻辑电路,实现了基本的逻辑功能。

- 模拟电路设计与仿真:学生们设计并仿真了一个低通滤波器,验证了电路的滤波性能。

- 集成电路版图设计:学生们完成了集成电路版图设计,并进行了DRC检查,确保版图设计的正确性。

实验 3 使用T-Spice 进行单元电路的瞬时分析3.1 实验目的及要求1.进一步熟悉Tanner Pro 软件中T-Spice 软件的使用;2.掌握使用T-Spice 分析简单电路的方法与操作流程,从而学会分析较为复杂的逻辑电路。

3.2 实验内容3.2.1 反相器瞬时分析(1)打开S-Edit,由于本实例中所使用的电路需要在反相器电路的基础上进行适当修改,为不影响后面的版图设计,同学们可以建立新文件EX3,将EX2 中反相器模块复制到EX3 文件中,再打开加入电源进行适当修改即可。

反相器电路设计较为简单,在此只是教大家掌握复制模块的方法,希望大家掌握。

(2)复制inv 模块方法如下:先打开实验 2 中设计的“EX2.sdb”。

进行复制前必须回到EX3 文件环境,方法为选择Module->Open 命令,打开Open Module 对话框,在Files下拉列表中选择EX3,单击OK 回到EX3 环境,才能进行复制模块操作。

选择Module->Copy命令,打开Copy Module 对话框,在下拉列表中选择EX2 选项,在Select Module To Copy列表中选择inv 选项,单击OK 按钮即可。

(3)加入工作电源:inv 模块在电路设计模式下,选择Moudle->Symbol Browser 命令,在Library 列表框中选择spice 组件库,其中有很多电压源符号,选取直流电压源Source_v_dc 作为此电路的工作电压源。

直流电压源Source_v_dc 符号有正(+)端与负(-)端。

在inv 模块编辑窗口中直流电压源有两种接法可以直接连线接到原电路图的Vdd 与Gnd,也可另外复制两个Vdd 与Gnd(Ctrl+C 复制Ctrl+V 粘贴)接到电压源正负极,虽然两个全域符号Vdd 与Gnd 符号分开放置,但两个分离的Vdd 符号实际上是接到同一个节点,而两个Gnd 符号也是共同接地的。

集成电路原理及应用班级:组员名单:学号:实验报告实验一芯片基本结构测试实验目的:1、了解芯片的基本结构2、掌握微分析设备显微镜的使用3、掌握集成电路反向设计中的图片提取实验内容:观察芯片的表面结构。

实验要求:(1)装好的芯片,并用在显微镜下观察记录芯片形貌。

(2)拼合拍摄下来的芯片表面图,还原原始芯片整体图。

实验原理:参照显微镜结构,利用CCD数字图像系统显示微观图形。

实验仪器:VM3000显微镜、IBM服务器计算机、晶圆样品、镊子等常用工具实验步骤:(1)连接好显微镜系统。

(2)打开电源启动计算机、显示仪和显微仪。

(3)放置好晶圆样品。

(4)显微镜粗调焦距。

(5)显微镜细调焦距。

(6)控制显微镜载物台,进行扫描观察芯片表面结构,并用计算机保存各块图像(7)打印所有图片并拼合。

实验报告:( 1 )实验目的;(2)实验内容;(3)所用仪器设备;(4)实验步骤;(5)图片拼合总体图;(6)小结。

(每个小组交一份报告)实验二 CMOS电路版图设计实验目的:1、学习CMOS电路的版图设计方法和设计流程。

2、学习版图设计软件L-edit使用。

3、理解CMOS电路中MOS器件的纵向结构和工艺流程。

4、掌握P阱CMOS工艺下的设计规则。

5、设计CMOS电路中异或门的逻辑结构和版图。

实验内容:1、设计CMOS电路中异或门的电路能够实现同或逻辑功能,2、设计的版图满足P阱CMOS电路的λ版图设计规则。

实验原理:1、异或门逻辑功能:Y=A⊕B2、P阱CMOS工艺下CMOS电路版图结构(反相器为例)3、P阱CMOS工艺的λ设计规则实验仪器与器件:微型计算机版图设计软件L-edit。

实验步骤:1、学习P阱CMOS工艺的λ设计规则2、在L-edit环境下设置图层结构、栅格尺寸和设计规则。

3、设计异或门逻辑结构和版图草图;4、设计编辑出异或门的版图文件。

思考题:(1)CMOS电路结构有何特点;(2)MOS管级联在版图中如何实现。

《集成电路应用》课程设计基于锁相环CD4046的数字频率合成器学院:物理与信息工程学院专业: 电子信息工程年级: 2015级某某:X 桢学号:指导教师:许志猛基于锁相环CD4046的数字频率合成器一、内容摘要:随着通讯,宇航和遥控遥测技术的不断开展,对信号频率的调控,稳定度和准确度的要求不断提高。

频率合成器就是以一个或少量的高准确度和高稳定度的标准频率作为参考频率,导出多个或大量的输出频率,这些输出频率的准确度和稳定度与参考频率是一致的。

本设计是基于锁相环CD4046制作的是频率合成器,锁相环是一种很有效的信号处理技术,它能严格跟踪想干信号频率。

利用锁相环构成的频率合成器电路结构简单,输出频率成分频谱纯度高,是一个较好的频率转换系统。

锁相频率合成器是一个闭环系统,结构简单,本钱低,有较高的频率准确度。

二、设计目的:1. 掌握锁相环的根本工作原理,锁相环外部元件的选择方法。

2. 掌握频率合成器的设计思路。

3. 结合所学的内容和知识,学会设计一个完整的电路。

三、设计步骤:1. 设计方案,确定电路形式,画出电路图。

2. 选取各局部电路所需元件并计算出元件参数。

3. 绘制PCB 电路图。

4. 转印并腐蚀电路板,进展焊接和组装电路。

5. 调试并测量电路性能。

四、主要技术指标:1. 频率合成X 围:KHz 100~KHz 102. 步进频率:KHz 13. 频率稳定度:%5≤∆ff4. 振荡器局部指定采用4053芯片5. 时钟源分频 > 2五、总体方案确实定:总体方案的设计原理框图如图1所示,锁相环路对稳定度的参考振动器锁定,环内串接可编程的分频器,通过改变分频器的分配比N ,从而就得到N 倍参考频率的稳定输出。

振荡源输出的信号频率f1,经固定分频后〔M 分频〕得到基准频率f2,输入锁相环的相位比拟器〔PC 〕。

锁相环的VCO 输出信号经可编程分频器〔N 分频〕后输入到PC 的另一端,这两个信号进展相位比拟,当锁相环路锁定后得到: f1/M=f2=f3/N=f4 故 f3=Nf2 (f2为基准频率) 当N 变化时,或者N/M 变化时,就可以得到一系列的输出频率f3。

实验名称:(请在此处填写实验名称)实验日期:(请在此处填写实验日期)实验地点:(请在此处填写实验地点)实验者:(请在此处填写实验者姓名)指导教师:(请在此处填写指导教师姓名)一、实验目的(简要描述本次实验的目的,例如:验证某种理论、探究某种现象、测试某种设备等)(此处应填写具体实验目的)二、实验原理(简要介绍实验所依据的原理,包括相关公式、定律等)(此处应填写具体实验原理)三、实验仪器与材料1. 仪器:(列举实验中所使用的仪器及其型号或规格)- 仪器1:……(型号/规格)- 仪器2:……(型号/规格)- 仪器3:……(型号/规格)2. 材料:(列举实验中所使用的材料及其来源)- 材料1:……(来源)- 材料2:……(来源)- 材料3:……(来源)四、实验步骤1. 步骤一:(描述实验的第一步操作及注意事项)- 操作:……- 注意事项:……2. 步骤二:(描述实验的第二步操作及注意事项)- 操作:……- 注意事项:……3. 步骤三:(描述实验的第三步操作及注意事项)- 操作:……- 注意事项:……(依此类推,详细描述所有实验步骤)五、实验数据记录与分析1. 数据记录:(根据实验内容,记录实验过程中所观察到的数据或现象) - 数据1:……- 数据2:……- 数据3:……2. 数据分析:(对实验数据进行整理、计算、比较等分析,得出结论)- 分析1:……- 分析2:……- 分析3:……(依此类推,详细分析实验数据)六、实验结果与讨论1. 实验结果:(总结实验过程中得到的主要结果,与预期目标进行对比)- 结果1:……- 结果2:……- 结果3:……2. 讨论:(对实验结果进行深入讨论,分析实验过程中可能存在的问题,提出改进建议) - 讨论点1:……- 讨论点2:……- 讨论点3:……(依此类推,详细讨论实验结果)七、实验结论(总结实验目的、实验结果、实验结论等,给出本次实验的总体评价)(此处应填写具体实验结论)八、参考文献(列出实验过程中参考的文献资料)1. [文献1]2. [文献2]3. [文献3]九、附录(如有需要,可在此处添加实验过程中的照片、图表、计算过程等补充材料)(此处可添加实验相关补充材料)注意:1. 本报告纸仅供参考,请根据实际实验内容进行修改和完善。

《集成电路应用》课程实验实验二锁相环综合实验

学院:物理与信息工程学院

专业: 电子信息工程

年级: 2015级

姓名:张桢

学号:

指导老师:许志猛

实验二锁相环综合实验

一、实验目的:

1.掌握锁相环的基本原理。

2.掌握锁相环外部元件的选择方法。

3.应用CD4046锁相环进行基本应用设计。

二、元件和仪器:

1.CD4046

2.函数信号发生器

3.示波器

4.电阻、电容若干

5.面包板

三、实验原理:

1.锁相环的基本原理。

锁相环最基本的结构如图所示。

它由三个基本的部件组成:鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)。

锁相环工作原理图

鉴相器是个相位比较装置。

它把输入信号Si(t)和压控振荡器的输出信号So(t)的相位进行比较,产生对应于两个信号相位差的误差电压Se(t)。

环路滤波器的作用是滤除误差电压Se(t)中的高频成分和噪声,以保证环路所要求的性能,增加系统的稳定性。

压控振荡器受控制电压Sd(t)的控制,使压控振荡器的频率向输入信号的频率靠拢,直至消除频差而锁定。

锁相环是个相位误差控制系统。

它比较输入信号和压控振荡器输出信号之间的相位差,从而产生误差控制电压来调整压控振荡器的频率,以达到与输入信号同频。

在环路开始工作时,如果输入信号频率与压控振荡器频率不同,则由于两信号之间存在固有的频率差,它们之间的相位差势必一直在变化,结果鉴相器输出的误差电压就在一定范围内变化。

在这种误差电压的控制下,压控振荡器的频率也在变化。

若压控振荡器的频率能够变化到与输入信号频率相等,在满足稳定性条件下就在这个频率上稳定下来。

达到稳定后,输入信号和压控振荡器输出信号之间的频差为零,相差不再随时间变化,误差电压为一固定值,这时环路就进入“锁定”状态。

这就是锁相环工作的大致过程。

2.CD4046芯片的工作原理。

CD4046是通用的CMOS锁相环集成电路,其特点是电源电压范围宽(为3V -18V),输入阻抗高(约100MΩ),动态功耗小,在中心频率f0为10kHz下功耗仅为600μW,属微功耗器件。

CD4046锁相的意义是相位同步的自动控制,功能是完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

锁相环主要由相位比较器(PC)、压控振荡器(VCO)、低通滤波器三部分组成,如下所示。

4046组成框图

CD4046内部电原理框图如下图所示:

CD4046工作原理:输入信号Ui从14脚输入后,经放大器A1进行放大、整形后加到相位比较器Ⅰ、Ⅱ的输入端,图3开关K拨至2脚,则比较器Ⅰ将从3脚输入的比较信号Uo与输入信号Ui作相位比较,从相位比较器输出的误差电压UΨ则反映出两者的相位差。

UΨ经R3、R4及C2滤波后得到一控制电压Ud加至压控振荡器VCO的输入端9脚,调整VCO的振荡频率f2,使f2迅速逼近信号频率f1。

VCO的输出又经除法器再进入相位比较器Ⅰ,继续与Ui进行相位比较,最后使得f2=f1,两者的相位差为一定值,实现了相位锁定。

若开关K拨至13 脚,则相位比较器Ⅱ工作,过程与上述相同,不再赘述。

右图是CD4046的引脚排列:

CD4046采用16脚双列直插式,各管脚功能:

1脚相位输出端,环路人锁时为高电平,

环路失锁时为低电平。

2脚相位比较器Ⅰ的输出端。

3脚比较信号输入端。

4脚压控振荡器输出端。

5脚禁止端,高电平时禁止,低电平时

允许压控振荡器工作。

6、7脚外接振荡电容。

8、16脚电源的负端和正端。

9脚压控振荡器的控制端。

10脚解调输出端,用于FM解调。

11、12脚外接振荡电阻。

13脚相位比较器Ⅱ的输出端。

14脚信号输入端。

15脚内部独立的齐纳稳压管负极。

四、实验内容:

1.掌握CD4046锁相环的工作原理,选取合适的参数设计一个锁相环(1)根据实验原理和设计要求,设计如下的电路图:

设计要求:(1)输入信号:F=10KHz (2)V CC=10V(3)中心频率:10KHz (4)锁定范围:1KHz

(2)在面包板上连接电路。

(3)用示波器观察锁相环输出的信号。

调整输入信号的频率,观察CD4046芯片上1脚的电平变化:当1脚电平指示为“1”电平时,标志着进入锁定范围。

反之为失锁。

(4)记录锁定范围(带宽)。

(5)讨论锁定范围和中心频率与设定值的误差

五、实验总结:

通过本次实验,我进一步学习和掌握CMOS集成芯片的特点。

了解了锁相环的原理,能够使用CD4046锁相环进行基本应用设计。

通过实验,我学会如何选取锁相环的元件和元件参数的计算方法。

---精心整理,希望对您有所帮助。