第3章习题答案 计算机组成原理课后答案(清华大学出版社 袁春风主编)

- 格式:pdf

- 大小:432.46 KB

- 文档页数:9

![计算机组成原理 [袁春风]chap3_1](https://uimg.taocdn.com/6a0eacceaa00b52acfc7cacf.webp)

第三章(P101)1.(1)M 4832*220= 字节 (2)片84*28*51232*1024==K K(3)1位地址作芯片选择2. (1)个内存条4264*264*222426==(2)328*264*22242=每个内存条内共有32个DRAM 芯片 (3)4*32 = 128个主存共需要128个DRAM 芯片,CPU 通过由高位地址选择各内存条。

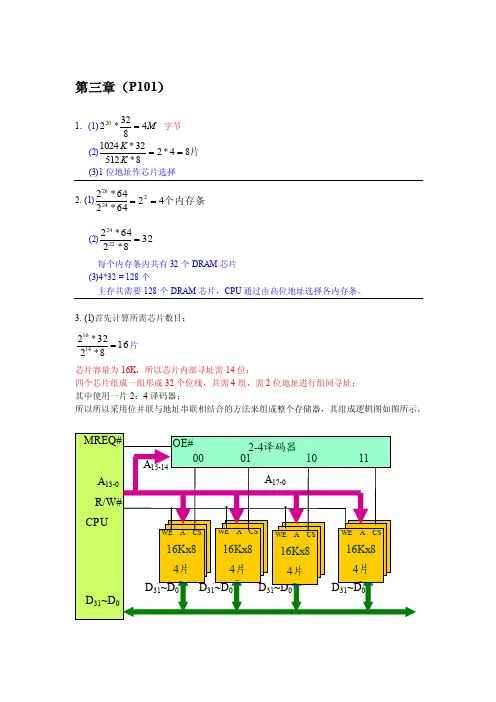

3. (1)首先计算所需芯片数目:168*232*21416=片 芯片容量为16K ,所以芯片内部寻址需14位;四个芯片组成一组形成32个位线,共需4组,需2位地址进行组间寻址; 其中使用一片2:4译码器;所以所以采用位并联与地址串联相结合的方法来组成整个存储器,其组成逻辑图如图所示,(2)根据已知条件,CPU 在1us 内至少访存一次,而整个存储器的平均读/写周期为0.5us ,如果采用集中刷新,有64us 的死时间,肯定不行 如果采用分散刷新,则每1us 只能访存一次,也不行 所以采用异步式刷新方式。

假定16K*8位的DRAM 芯片用128*128矩阵存储元构成,刷新时只对128行进行异步方式刷新,则刷新间隔为2ms/128 = 15.5us ,可取刷新信号周期15us 。

刷新一遍所用时间=15us ×128=1.92ms4. (1)片328*12832*1024 K K ,共分8组,每组4片;地址线共20位,其中组间寻址需3位,组内17位; (2)(3)如果选择一个行地址进行刷新,刷新地址为A 0-A 8,因此这一行上的2048个存储元同时进行刷新,即在8ms 内进行512个周期(即512行)。

采用异步刷新方式,刷新信号周期为:8ms/512 = 15.5us 。

注:存储器由128K*8位的芯片构成,分8组,每组4片,组内芯片并行工作,需17条地址线进行寻址,其中X 行线为9根,Y 位线为8根,29=512行。

5. 用256K*16位的SRAM 芯片设计1024K*32的存储器,需进行字位同时扩展方式继续拧设计,所需芯片数目:片816*25632*1024 K K ,设计的存储器容量为1M ,字长为32,故需20位地址(A0~A19);所用芯片存储容量为256K ,字长为16位,故片内寻址需18位(A0~A17)。

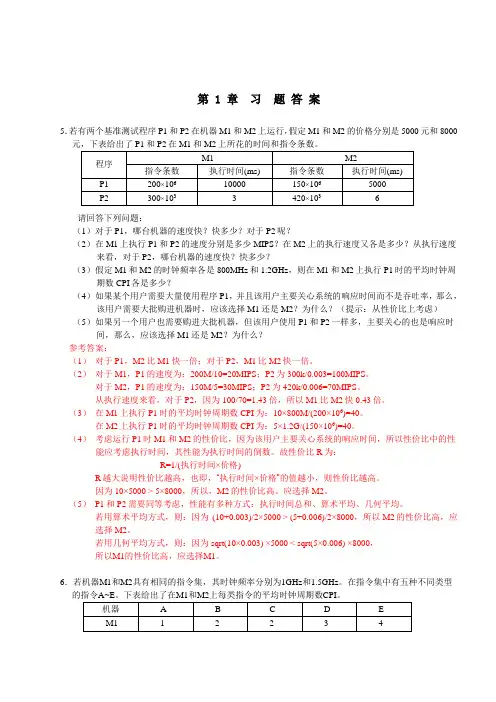

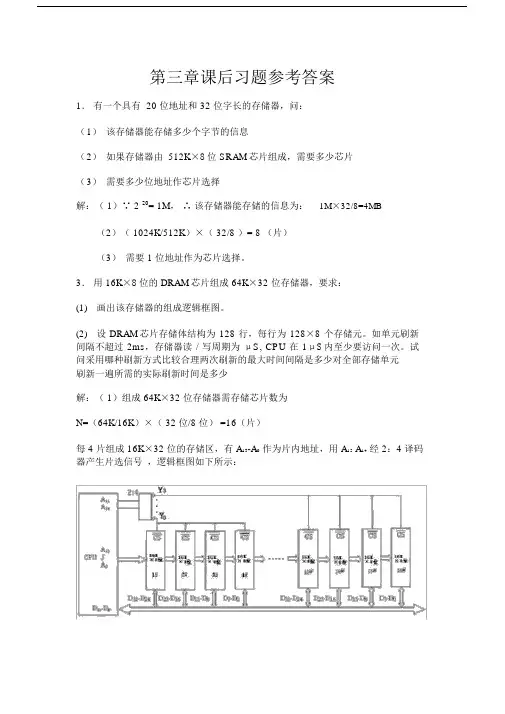

第 1 章习题答案5.若有两个基准测试程序P1和P2在机器M1和M2上运行,假定M1和M2的价格分别是5000元和8000请回答下列问题:(1)对于P1,哪台机器的速度快?快多少?对于P2呢?(2)在M1上执行P1和P2的速度分别是多少MIPS?在M2上的执行速度又各是多少?从执行速度来看,对于P2,哪台机器的速度快?快多少?(3)假定M1和M2的时钟频率各是800MHz和1.2GHz,则在M1和M2上执行P1时的平均时钟周期数CPI各是多少?(4)如果某个用户需要大量使用程序P1,并且该用户主要关心系统的响应时间而不是吞吐率,那么,该用户需要大批购进机器时,应该选择M1还是M2?为什么?(提示:从性价比上考虑)(5)如果另一个用户也需要购进大批机器,但该用户使用P1和P2一样多,主要关心的也是响应时间,那么,应该选择M1还是M2?为什么?参考答案:(1)对于P1,M2比M1快一倍;对于P2,M1比M2快一倍。

(2)对于M1,P1的速度为:200M/10=20MIPS;P2为300k/0.003=100MIPS。

对于M2,P1的速度为:150M/5=30MIPS;P2为420k/0.006=70MIPS。

从执行速度来看,对于P2,因为100/70=1.43倍,所以M1比M2快0.43倍。

(3)在M1上执行P1时的平均时钟周期数CPI为:10×800M/(200×106)=40。

在M2上执行P1时的平均时钟周期数CPI为:5×1.2G/(150×106)=40。

(4)考虑运行P1时M1和M2的性价比,因为该用户主要关心系统的响应时间,所以性价比中的性能应考虑执行时间,其性能为执行时间的倒数。

故性价比R为:R=1/(执行时间×价格)R越大说明性价比越高,也即,“执行时间×价格”的值越小,则性价比越高。

因为10×5000 > 5×8000,所以,M2的性价比高。

第 1 章习题答案5.若有两个基准测试程序P1和P2在机器M1和M2上运行,假定M1和M2的价格分别是5000元和8000元,下表给出了P1和P2在M1和M2上所花的时间和指令条数。

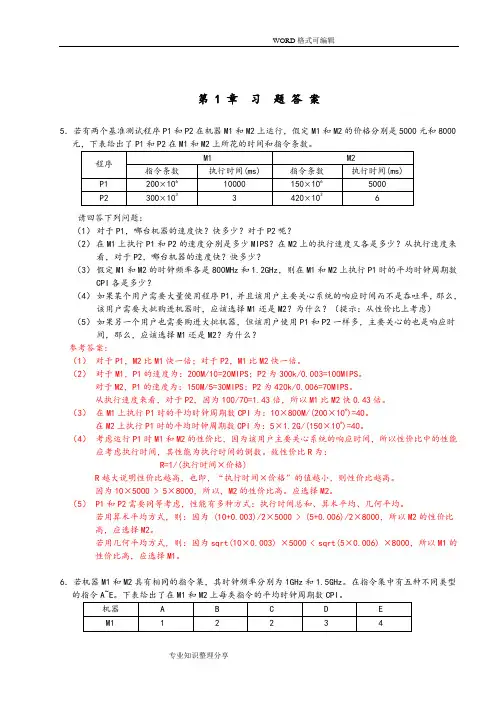

请回答下列问题:(1)对于P1,哪台机器的速度快?快多少?对于P2呢?(2)在M1上执行P1和P2的速度分别是多少MIPS?在M2上的执行速度又各是多少?从执行速度来看,对于P2,哪台机器的速度快?快多少?(3)假定M1和M2的时钟频率各是800MHz和1.2GHz,则在M1和M2上执行P1时的平均时钟周期数CPI各是多少?(4)如果某个用户需要大量使用程序P1,并且该用户主要关心系统的响应时间而不是吞吐率,那么,该用户需要大批购进机器时,应该选择M1还是M2?为什么?(提示:从性价比上考虑)(5)如果另一个用户也需要购进大批机器,但该用户使用P1和P2一样多,主要关心的也是响应时间,那么,应该选择M1还是M2?为什么?参考答案:(1)对于P1,M2比M1快一倍;对于P2,M1比M2快一倍。

(2)对于M1,P1的速度为:200M/10=20MIPS;P2为300k/0.003=100MIPS。

对于M2,P1的速度为:150M/5=30MIPS;P2为420k/0.006=70MIPS。

从执行速度来看,对于P2,因为100/70=1.43倍,所以M1比M2快0.43倍。

(3)在M1上执行P1时的平均时钟周期数CPI为:10×800M/(200×106)=40。

在M2上执行P1时的平均时钟周期数CPI为:5×1.2G/(150×106)=40。

(4)考虑运行P1时M1和M2的性价比,因为该用户主要关心系统的响应时间,所以性价比中的性能应考虑执行时间,其性能为执行时间的倒数。

故性价比R为:R=1/(执行时间×价格)R越大说明性价比越高,也即,“执行时间×价格”的值越小,则性价比越高。

第 1 章习题答案5.若有两个基准测试程序P1和P2在机器M1和M2上运行,假定M1和M2的价格分别是5000元和8000元,下表给出了P1和P2在M1和M2上所花的时间和指令条数。

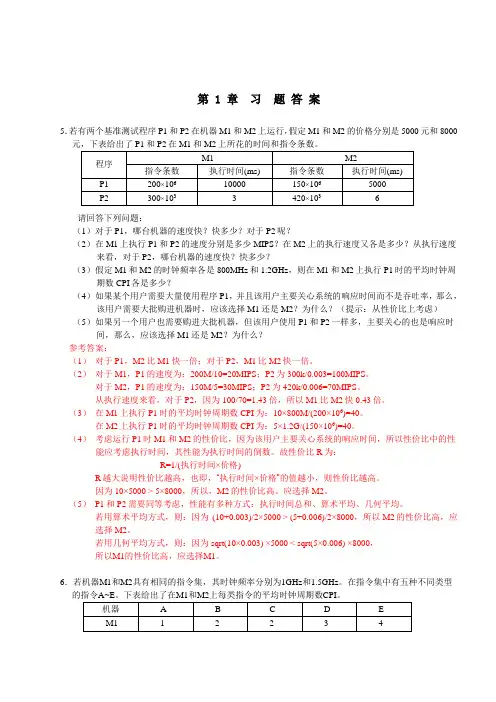

请回答下列问题:(1)对于P1,哪台机器的速度快?快多少?对于P2呢?(2)在M1上执行P1和P2的速度分别是多少MIPS?在M2上的执行速度又各是多少?从执行速度来看,对于P2,哪台机器的速度快?快多少?(3)假定M1和M2的时钟频率各是800MHz和1.2GHz,则在M1和M2上执行P1时的平均时钟周期数CPI各是多少?(4)如果某个用户需要大量使用程序P1,并且该用户主要关心系统的响应时间而不是吞吐率,那么,该用户需要大批购进机器时,应该选择M1还是M2?为什么?(提示:从性价比上考虑)(5)如果另一个用户也需要购进大批机器,但该用户使用P1和P2一样多,主要关心的也是响应时间,那么,应该选择M1还是M2?为什么?参考答案:(1)对于P1,M2比M1快一倍;对于P2,M1比M2快一倍。

(2)对于M1,P1的速度为:200M/10=20MIPS;P2为300k/0.003=100MIPS。

对于M2,P1的速度为:150M/5=30MIPS;P2为420k/0.006=70MIPS。

从执行速度来看,对于P2,因为100/70=1.43倍,所以M1比M2快0.43倍。

(3)在M1上执行P1时的平均时钟周期数CPI为:10×800M/(200×106)=40。

在M2上执行P1时的平均时钟周期数CPI为:5×1.2G/(150×106)=40。

(4)考虑运行P1时M1和M2的性价比,因为该用户主要关心系统的响应时间,所以性价比中的性能应考虑执行时间,其性能为执行时间的倒数。

故性价比R为:R=1/(执行时间×价格)R越大说明性价比越高,也即,“执行时间×价格”的值越小,则性价比越高。

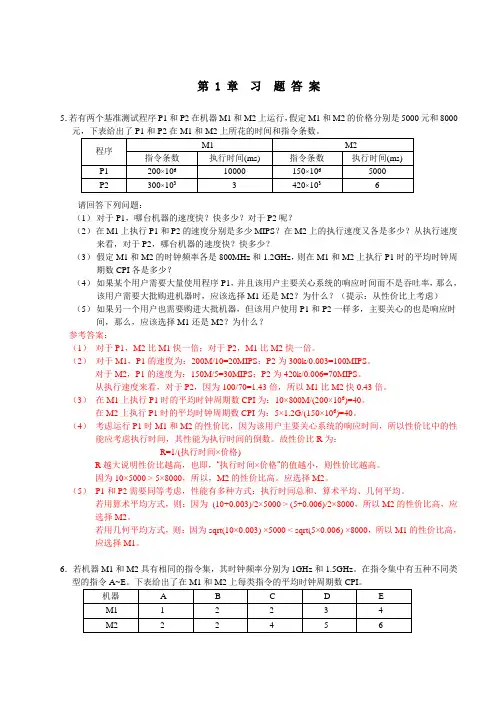

第三章课后习题参考答案1.有一个具有 20 位地址和 32 位字长的存储器,问:(1)该存储器能存储多少个字节的信息(2)如果存储器由 512K×8位 SRAM芯片组成,需要多少芯片(3)需要多少位地址作芯片选择解:( 1)∵ 2 20= 1M,∴该存储器能存储的信息为:1M×32/8=4MB (2)( 1024K/512K)×( 32/8 )= 8 (片)(3)需要 1 位地址作为芯片选择。

3.用 16K×8位的 DRAM芯片组成 64K×32 位存储器,要求:(1)画出该存储器的组成逻辑框图。

(2)设 DRAM芯片存储体结构为 128 行,每行为 128×8 个存储元。

如单元刷新间隔不超过 2ms,存储器读 / 写周期为μS, CPU 在 1μS内至少要访问一次。

试问采用哪种刷新方式比较合理两次刷新的最大时间间隔是多少对全部存储单元刷新一遍所需的实际刷新时间是多少解:( 1)组成 64K×32 位存储器需存储芯片数为N=(64K/16K)×( 32 位/8 位) =16(片)每 4 片组成 16K×32 位的存储区,有 A13-A0作为片内地址,用 A15 A14经 2:4 译码器产生片选信号,逻辑框图如下所示:( 2)根据已知条件, CPU 在期为,如果采用集中刷新,有1us 内至少访存一次,而整个存储器的平均读64us 的死时间,肯定不行;/ 写周所以采用分散式刷新方式:设 16K×8位存储芯片的阵列结构为 128 行× 128 列,按行刷新,刷新周期T=2ms,则分散式刷新的间隔时间为:t=2ms/128=(?s) 取存储周期的整数倍 ?s 的整数倍 )则两次刷新的最大时间间隔发生的示意图如下可见,两次刷新的最大时间间隔为 t MAXt MAX=× 2-= ( μ S)对全部存储单元刷新一遍所需时间为t Rt R=× 128=64 ( μS)4.有一个 1024K× 32 位的存储器,由128K× 8 位 DRAM芯片构成。

计算机组成与系统结构课后答案免费版全(清华大学出版社_袁春风主编)第 1 章习题答案5.若有两个基准测试程序P1和P2在机器M1和M2上运行,假定M1和M2的价格分别是5000元和8000请回答下列问题:(1)对于P1,哪台机器的速度快?快多少?对于P2呢?(2)在M1上执行P1和P2的速度分别是多少MIPS?在M2上的执行速度又各是多少?从执行速度来看,对于P2,哪台机器的速度快?快多少?(3)假定M1和M2的时钟频率各是800MHz和1.2GHz,则在M1和M2上执行P1时的平均时钟周期数CPI各是多少?(4)如果某个用户需要大量使用程序P1,并且该用户主要关心系统的响应时间而不是吞吐率,那么,该用户需要大批购进机器时,应该选择M1还是M2?为什么?(提示:从性价比上考虑)(5)如果另一个用户也需要购进大批机器,但该用户使用P1和P2一样多,主要关心的也是响应时间,那么,应该选择M1还是M2?为什么?参考答案:(1)对于P1,M2比M1快一倍;对于P2,M1比M2快一倍。

(2)对于M1,P1的速度为:200M/10=20MIPS;P2为300k/0.003=100MIPS。

对于M2,P1的速度为:150M/5=30MIPS;P2为420k/0.006=70MIPS。

从执行速度来看,对于P2,因为100/70=1.43倍,所以M1比M2快0.43倍。

(3)在M1上执行P1时的平均时钟周期数CPI为:10×800M/(200×106)=40。

在M2上执行P1时的平均时钟周期数CPI为:5×1.2G/(150×106)=40。

(4)考虑运行P1时M1和M2的性价比,因为该用户主要关心系统的响应时间,所以性价比中的性能应考虑执行时间,其性能为执行时间的倒数。

故性价比R为:R=1/(执行时间×价格)R越大说明性价比越高,也即,“执行时间×价格”的值越小,则性价比越高。

第三章课后习题参考答案1.有一个具有20位地址和32位字长的存储器,问:(1)该存储器能存储多少个字节的信息?(2)如果存储器由512K×8位SRAM芯片组成,需要多少芯片?(3)需要多少位地址作芯片选择?解:(1)∵ 220= 1M,∴该存储器能存储的信息为:1M×32/8=4MB (2)(1024K/512K)×(32/8)= 8(片)(3)需要1位地址作为芯片选择。

3.用16K×8位的DRAM芯片组成64K×32位存储器,要求:(1) 画出该存储器的组成逻辑框图。

(2) 设DRAM芯片存储体结构为128行,每行为128×8个存储元。

如单元刷新间隔不超过2ms,存储器读/写周期为0.5μS, CPU在1μS内至少要访问一次。

试问采用哪种刷新方式比较合理?两次刷新的最大时间间隔是多少?对全部存储单元刷新一遍所需的实际刷新时间是多少?解:(1)组成64K×32位存储器需存储芯片数为N=(64K/16K)×(32位/8位)=16(片)每4片组成16K×32位的存储区,有A13-A0作为片内地址,用A15 A14经2:4译码器产生片选信号,逻辑框图如下所示:(2)根据已知条件,CPU在1us内至少访存一次,而整个存储器的平均读/写周期为0.5us,如果采用集中刷新,有64us的死时间,肯定不行;所以采用分散式刷新方式:设16K×8位存储芯片的阵列结构为128行×128列,按行刷新,刷新周期T=2ms,则分散式刷新的间隔时间为:t=2ms/128=15.6(s) 取存储周期的整数倍15.5s(0.5的整数倍)则两次刷新的最大时间间隔发生的示意图如下可见,两次刷新的最大时间间隔为tMAXt MAX=15.5×2-0.5=30.5 (μS)对全部存储单元刷新一遍所需时间为tRt R=0.5×128=64 (μS)4.有一个1024K×32位的存储器,由128K×8位DRAM芯片构成。

第 1 章习题答案5.若有两个基准测试程序P1和P2在机器M1和M2上运行,假定M1和M2的价格分别是5000元和8000元,下表给出了P1和P2在M1和M2上所花的时间和指令条数。

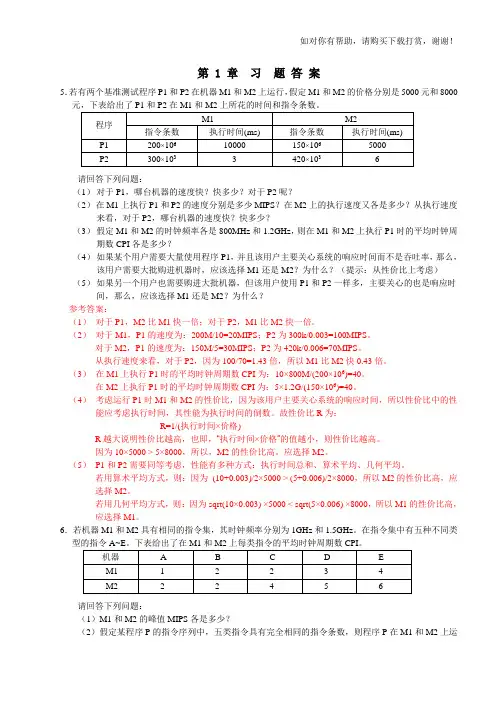

请回答下列问题:(1)对于P1,哪台机器的速度快?快多少?对于P2呢?(2)在M1上执行P1和P2的速度分别是多少MIPS?在M2上的执行速度又各是多少?从执行速度来看,对于P2,哪台机器的速度快?快多少?(3)假定M1和M2的时钟频率各是800MHz和1.2GHz,则在M1和M2上执行P1时的平均时钟周期数CPI各是多少?(4)如果某个用户需要大量使用程序P1,并且该用户主要关心系统的响应时间而不是吞吐率,那么,该用户需要大批购进机器时,应该选择M1还是M2?为什么?(提示:从性价比上考虑)(5)如果另一个用户也需要购进大批机器,但该用户使用P1和P2一样多,主要关心的也是响应时间,那么,应该选择M1还是M2?为什么?参考答案:(1)对于P1,M2比M1快一倍;对于P2,M1比M2快一倍。

(2)对于M1,P1的速度为:200M/10=20MIPS;P2为300k/0.003=100MIPS。

对于M2,P1的速度为:150M/5=30MIPS;P2为420k/0.006=70MIPS。

从执行速度来看,对于P2,因为100/70=1.43倍,所以M1比M2快0.43倍。

(3)在M1上执行P1时的平均时钟周期数CPI为:10×800M/(200×106)=40。

在M2上执行P1时的平均时钟周期数CPI为:5×1.2G/(150×106)=40。

(4)考虑运行P1时M1和M2的性价比,因为该用户主要关心系统的响应时间,所以性价比中的性能应考虑执行时间,其性能为执行时间的倒数。

故性价比R为:R=1/(执行时间×价格)R越大说明性价比越高,也即,“执行时间×价格”的值越小,则性价比越高。

第1章3.解:(1) (25.8125)10 = (1 1001.1101)2= (31.64)8= (19.D)16(2)(101101.011)2 = (45.375)10 = (55.3)8= (2D.6)16= (0100 0101.0011 0111 0101)8421(3)(0101 1001 0110.0011)8421 = (596.3)10≈ (1001010100.010011)2=(254.4C)16(4)(4E.C)16 = (78.75)10=(100 1110.11)24.假定机器数为8位(1位符号,7位数值),写出下列各二进制数的原码和补码表示。

5.假定机器数为8位(1位符号,7位数值),写出下列各二进制数的补码和移码(偏置常数为128)。

6.已知补码求真值。

7.(R1)=0000108BH,(R2)=8080108BH(1)解:执行无符号整数加法指令时,两数均为无符号数,故:[R1]真值=108BH,[R2]真值=8080108BH(2)解:执行带符号整数乘法指令时,两数为带符号数,此值为补码,即:[R1]补=0000108BH,[R2]补=8080108BH=1000_0000_1000_0000_0001_0000_1000_1011B根据补码与真值的转换规则,可以求出真值:[R1]真值=+108BH,[R2]真值=-111_1111_0111_1111_1110_1111_0111_0101B=-7F7FEF75H(3)解:执行单精度浮点数减法指令时,两数为32位IEEE754格式的浮点数(书P19),按下述过程求真值:(a)将机器数展开成二进制形式(R1)=0000108BH=0000_0000_0000_0000_0001_0000_1000_1011B(R2)=8080108BH=1000_0000_1000_0000_0001_0000_1000_1011B(b)按32位IEEE754标准规定,写出符号位s,阶码e和尾数f的值对于R1:s=0,e=00000000,f=000_0000_0001_0000_1000_1011对于R2:s=1,e=00000001,f=000_0000_0001_0000_1000_1011(c)按32位IEEE754标准规定,真值的计算公式是:(−1)s⨯1.f⨯2e−127,据此可以求出真值:对于R1,由于s=0,阶码e=00000000,依据书P19-表1.2的解释,[R1]真值=0.f⨯2−126=−(0.000_0000_0001_0000_1000_1011)2⨯2−126对于R2,[R2]真值=(−1)s⨯1.f⨯2e−127=−(1.000_0000_0001_0000_1000_1011)2⨯2−1268.解:9.解:13.以IEEE754单精度浮点数格式表示下列十进制数。

第1 章习题答案5.若有两个基准测试法度P1和P2在机器M1和M2上运行,假定M1和M2的价格辨别是5000元和8000元,下表给出了P1和P2在M1和M2上所花的时间和指令条数。

请回答下列问题:(1)对P1,哪台机器的速度快?快几多?对P2呢?(2)在M1上执行P1和P2的速度辨别是几多MIPS?在M2上的执行速度又各是几多?从执行速度来看,对P2,哪台机器的速度快?快几多?(3)假定M1和M2的时钟频率各是800MHz和1.2GHz,则在M1和M2上执行P1时的平均时钟周期数CPI各是几多?(4)如果某个用户需要年夜量使用法度P1,并且该用户主要关心系统的响应时间而不是吞吐率,那么,该用户需要年夜批购进机器时,应该选择M1还是M2?为什么?(提示:从性价比上考虑)(5)如果另一个用户也需要购进年夜批机器,但该用户使用P1和P2一样多,主要关心的也是响应时间,那么,应该选择M1还是M2?为什么?参考谜底:(1)对P1,M2比M1快一倍;对P2,M1比M2快一倍。

(2)对M1,P1的速度为:200M/10=20MIPS;P2为300k/0.003=100MIPS。

对M2,P1的速度为:150M/5=30MIPS;P2为420k/0.006=70MIPS。

从执行速度来看,对P2,因为100/70=1.43倍,所以M1比M2快0.43倍。

(3)在M1上执行P1时的平均时钟周期数CPI为:10×800M/(200×106)=40。

在M2上执行P1时的平均时钟周期数CPI为:5×1.2G/(150×106)=40。

(4)考虑运行P1时M1和M2的性价比,因为该用户主要关心系统的响应时间,所以性价比中的性能应考虑执行时间,其性能为执行时间的倒数。

故性价比R为:R=1/(执行时间×价格)R越年夜说明性价比越高,也即,“执行时间×价格”的值越小,则性价比越高。