模拟锁相环测试实验

- 格式:ppt

- 大小:101.00 KB

- 文档页数:15

锁相调频电路实验实验六锁相调频电路实验一、实验目的1、进一步了解锁相环路的工作原理及性能特点。

2、初步熟悉锁相环路及其基本组成的部件性能指示的测试方法。

二、实验原理1、我们知道锁相环路由鉴相器(Phase Detector)环路滤波器(Loop Fifter)和压控振荡器(voltage control oscillator)三个基本部分组成。

锁相环路实际上是一个相位自动调节系统(ω≠ωR)进入锁定状态ωV=ωR的捕捉过程,与环路保持锁定状态的同步和跟踪过程。

锁相环锁定和失锁的基本标志是:锁定时ω=ωV,△ω=0鉴相器输出一直流电压Vd可以用直流电压表测出,也可以用示波器观察。

失锁时,ω≠ωV鉴相器输出一个交变的交流电压,用直流电压表测量时,其Vd为零,用示波器观察则Vd为交变的交流信号电压,鉴相器的鉴相灵敏度,VCO的控制特性,环路滤波器的滤波性能等参数都对锁相环的性能有很大的影响。

同步过程:起始条件是环路已处于动态平衡中由于不稳定因素的影响,使ωV 产生缓慢漂移时,环路内所发生的使ωV继续锁定在ωR 上的过程,同步过程的进行受一定的限制当起始频差δωV达到一定值时,环路是不能再锁定而失锁,这一边界ΔωH成为同步带。

捕捉过程:起始条件是环路失锁既ωR≠ωV的情况下,环路由失锁进入锁定时环路内所发生的运动过程。

捕捉过程分为快捕和慢捕,通常所指为快捕过程。

捕捉带,它是指环路失锁已既进入锁定的两个边界频率之差的1/2。

2、实验电路介绍实验电路如图6—1所示:限幅器:对输入的方波信号进行整形,消除毛刺、寄生调幅。

用7LS00与非门来完成。

鉴相器:比较两个信号的相位产生与相位差成下比例的电压、它也利用与非门来完成。

(74LS00)74LS00是二输入端四与非门。

图6—1 锁相环路实验电路方框图滤波器:选出反映相位差的直流分量去控制VCO,本滤波器为比例滤波器。

放大器:由LM741组成的基极定时多谢振荡器,它的振荡频率相位受到控制得以调整输出反馈到鉴相器。

模拟锁相环模块信息工程学院08级电子班安艳芳0839107一、实验目的1、熟悉模拟锁相环的基本工作原理2、掌握模拟字锁相环的基本参数及设计二、实验仪器JH5001通信原理综合实验系统(一台)、20MHz双踪示波器(一台)、函数信号发生器(一台)三、实验原理和电路说明锁相的重要性:在电信网中,同步是一个十分重要的概念。

其最终目的使本地终端时钟源锁定在另一个参考时钟源上。

同步的技术基础是锁相,因而锁相技术是通信中最重要的技术之一在系统工作中模拟锁相环将接收端的256KHz时钟锁在发端的256KHz的时钟上,来获得系统的同步时钟,如HDB3接收的同步时钟及后续电路同步时钟。

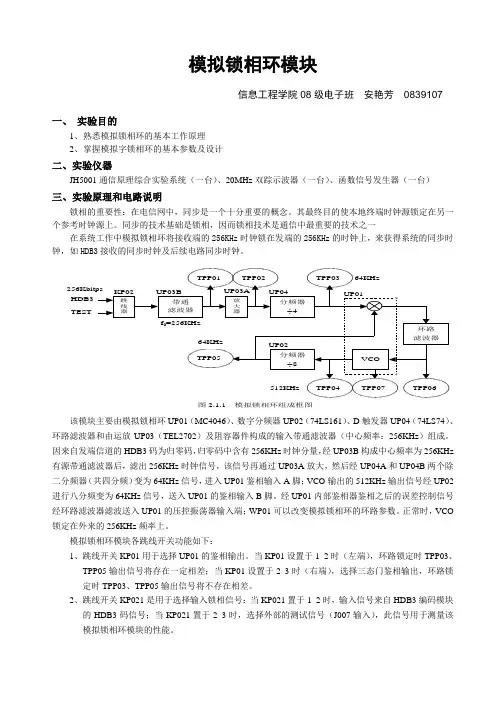

该模块主要由模拟锁相环UP01(MC4046)、数字分频器UP02(74LS161)、D触发器UP04(74LS74)、环路滤波器和由运放UP03(TEL2702)及阻容器件构成的输入带通滤波器(中心频率:256KHz)组成。

因来自发端信道的HDB3码为归零码,归零码中含有256KHz时钟分量,经UP03B构成中心频率为256KHz 有源带通滤波器后,滤出256KHz时钟信号,该信号再通过UP03A放大,然后经UP04A和UP04B两个除二分频器(共四分频)变为64KHz信号,进入UP01鉴相输入A脚;VCO输出的512KHz输出信号经UP02进行八分频变为64KHz信号,送入UP01的鉴相输入B脚。

经UP01内部鉴相器鉴相之后的误差控制信号经环路滤波器滤波送入UP01的压控振荡器输入端;WP01可以改变模拟锁相环的环路参数。

正常时,VCO 锁定在外来的256KHz频率上。

模拟锁相环模块各跳线开关功能如下:1、跳线开关KP01用于选择UP01的鉴相输出。

当KP01设置于1_2时(左端),环路锁定时TPP03、TPP05输出信号将存在一定相差;当KP01设置于2_3时(右端),选择三态门鉴相输出,环路锁定时TPP03、TPP05输出信号将不存在相差。

模拟锁相环实验报告锁相环(PLL)是一种常见的控制系统,它可以将输入信号的频率和相位与参考信号匹配,从而实现精确的信号同步和频率锁定。

本次实验旨在通过模拟锁相环的实验,了解PLL的基本原理和实现方式,并探究其在频率合成和时钟恢复等应用中的优势和局限性。

一、实验原理1.1 PLL的基本原理PLL由相频比较器、环形控制器、振荡器和分频器等组成。

其基本原理如下:(1)将参考信号和输出信号输入相频比较器,得到误差信号;(2)将误差信号输入环形控制器,控制其输出的控制电压;(3)将控制电压输入振荡器,控制其输出的频率和相位;(4)将振荡器的输出信号通过分频器分频后反馈给相频比较器,形成闭环控制。

通过不断比较和修正,PLL可以使输出信号的频率和相位与参考信号匹配,从而实现锁定。

1.2 实验器材本次实验采用的器材如下:信号发生器、示波器、多路开关、振荡器、计数器等。

1.3 实验步骤(1)将信号发生器产生的正弦波信号作为参考信号,通过示波器观测其频率和相位;(2)将信号发生器产生的方波信号作为输入信号,通过多路开关控制输入信号的频率和幅值;(3)将输入信号和参考信号输入相频比较器,得到误差信号;(4)将误差信号输入环形控制器,控制其输出的控制电压;(5)将控制电压输入振荡器,控制其输出的频率和相位;(6)将振荡器的输出信号通过分频器分频后反馈给相频比较器,形成闭环控制;(7)通过计数器观测输出信号的频率和相位,调整环形控制器的参数,使输出信号与参考信号匹配。

二、实验结果在实验过程中,我们先设置参考信号的频率为1KHz,通过示波器观测其频率和相位,然后将信号发生器产生的方波信号作为输入信号,进行频率和幅值的调节,使其与参考信号匹配。

在调节的过程中,我们观测到输出信号的频率和相位逐渐趋近于参考信号的频率和相位,最终实现了同步锁定。

然后,我们进一步测试了PLL在频率合成和时钟恢复等应用中的性能。

我们将输入信号的频率和幅值进行变化,观测输出信号的变化情况。

实验八模拟锁相环应用实验一、实验目的1、掌握模拟锁相环的组成及工作原理。

2、学习用集成锁相环构成锁相解调电路。

3、学习用集成锁相环构成锁相倍频电路。

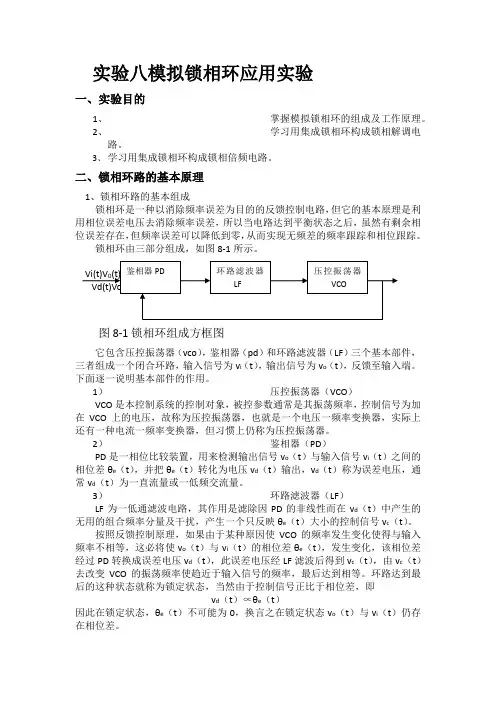

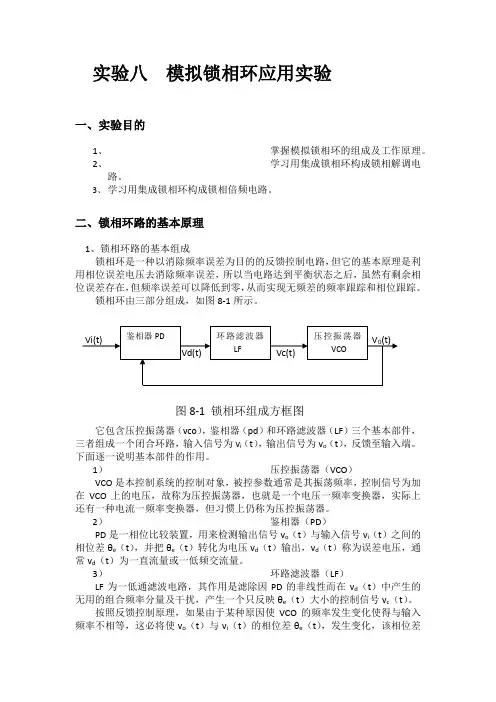

二、锁相环路的基本原理1、锁相环路的基本组成锁相环是一种以消除频率误差为目的的反馈控制电路,但它的基本原理是利用相位误差电压去消除频率误差,所以当电路达到平衡状态之后,虽然有剩余相位误差存在,但频率误差可以降低到零,从而实现无频差的频率跟踪和相位跟踪。

锁相环由三部分组成,如图8-1所示。

图8-1锁相环组成方框图它包含压控振荡器(vco),鉴相器(pd)和环路滤波器(LF)三个基本部件,三者组成一个闭合环路,输入信号为v i(t),输出信号为v o(t),反馈至输入端。

下面逐一说明基本部件的作用。

1)压控振荡器(VCO)VCO是本控制系统的控制对象,被控参数通常是其振荡频率,控制信号为加在VCO上的电压,故称为压控振荡器,也就是一个电压一频率变换器,实际上还有一种电流一频率变换器,但习惯上仍称为压控振荡器。

2)鉴相器(PD)PD是一相位比较装置,用来检测输出信号v o(t)与输入信号v i(t)之间的相位差θe(t),并把θe(t)转化为电压v d(t)输出,v d(t)称为误差电压,通常v d(t)为一直流量或一低频交流量。

3)环路滤波器(LF)LF为一低通滤波电路,其作用是滤除因PD的非线性而在v d(t)中产生的无用的组合频率分量及干扰,产生一个只反映θe(t)大小的控制信号v c(t)。

按照反馈控制原理,如果由于某种原因使VCO的频率发生变化使得与输入频率不相等,这必将使v o(t)与v i(t)的相位差θe(t),发生变化,该相位差经过PD转换成误差电压v d(t),此误差电压经LF滤波后得到v c(t),由v c(t)去改变VCO的振荡频率使趋近于输入信号的频率,最后达到相等。

环路达到最后的这种状态就称为锁定状态,当然由于控制信号正比于相位差,即v d(t)∝θe(t)因此在锁定状态,θe(t)不可能为0,换言之在锁定状态v o(t)与v i(t)仍存在相位差。

模拟锁相环实验报告实验一模拟锁相环模块一、实验原理和电路说明模拟锁相环模块在通信原理综合实验系统中可作为一个独立的模块进行测试。

在系统工作中模拟锁相环将接收端的256KHz 时钟锁在发端的256KHz 的时钟上,来获得系统的同步时钟,如HDB3接收的同步时钟及后续电路同步时钟。

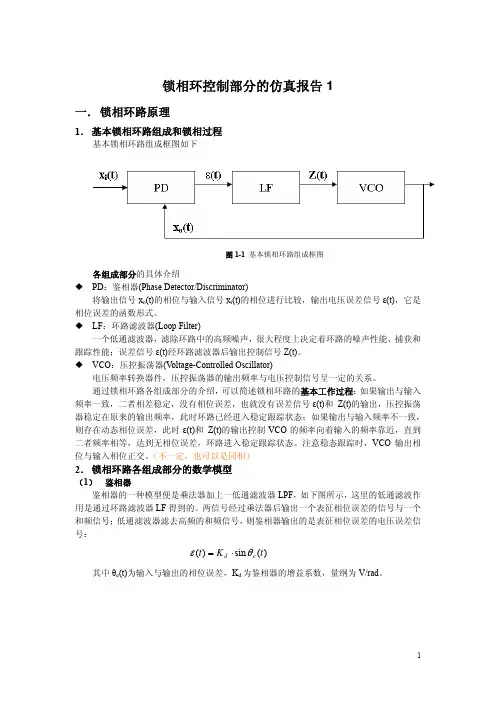

f 0=256K H z 64K H z U P 04U P 03B U P 02U P 01512K H z 分频器÷4分频器÷8H D B 3环路滤波器放大器图 2.1.1 模拟锁相环组成框图T P P 02T E S T 跳线器K P 02V C O T P P 03T P P 06T P P 04T P P 05256K b itp sT P P 07带通滤波器T P P 01U P 03A 64K H z 该模块主要由模拟锁相环UP01(MC4046)、数字分频器UP02(74LS161)、D 触发器UP04(74LS74)、环路滤波器和由运放UP03(TEL2702)及阻容器件构成的输入带通滤波器(中心频率:256KHz )组成。

在UP01内部有一个振荡器与一个高速鉴相器组成。

该模拟锁相环模块的框图见图2.1.1。

因来自发端信道的HDB3码为归零码,归零码中含有256KHz 时钟分量,经UP03B 构成中心频率为256KHz 有源带通滤波器后,滤出256KHz 时钟信号,该信号再通过UP03A 放大,然后经UP04A 和UP04B 两个除二分频器(共四分频)变为64KHz 信号,进入UP01鉴相输入A 脚;VCO 输出的512KHz 输出信号经UP02进行八分频变为64KHz 信号,送入UP01的鉴相输入B 脚。

经UP01内部鉴相器鉴相之后的误差控制信号经环路滤波器滤波送入UP01的压控振荡器输入端;WP01可以改变模拟锁相环的环路参数。

正常时,VCO 锁定在外来的256KHz 频率上。

模拟锁相环模块各跳线开关功能如下:1、跳线开关KP01用于选择UP01的鉴相输出。

:锁相环测试及应用实验试验目的:1.了解锁相环的组成、基本原理及性能特点。

2.掌握集成锁相环4046芯片的使用方法。

3.掌握锁相环路及各部件性能(鉴相特性、压控特性、同步带和捕捉带)的测试方法。

4.掌握锁相调频、锁相鉴频电路的构成、基本原理及参数测试测试方法。

5.掌握简单锁相频率合成器的基本原理及性能指标的测试方法实验设备:1.调幅与调频发射模块。

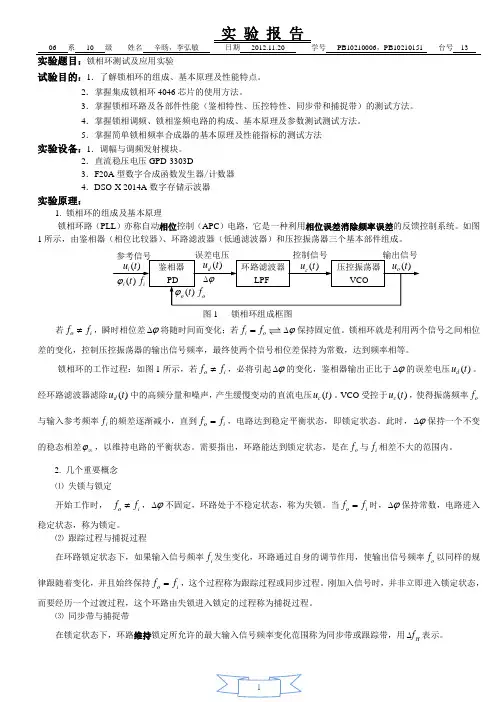

2.直流稳压电压GPD-3303D3.F20A 型数字合成函数发生器/计数器 4.DSO-X 2014A 数字存储示波器实验原理:1. 锁相环的组成及基本原理锁相环路(PLL )亦称自动相位控制(APC )电路,它是一种利用相位误差消除频率误差的反馈控制系统。

如图1所示,由鉴相器(相位比较器)、环路滤波器(低通滤波器)和压控振荡器三个基本部件组成。

若o i f f ≠,瞬时相位差ϕ∆将随时间而变化;若i of f ϕ∆=保持固定值。

锁相环就是利用两个信号之间相位差的变化,控制压控振荡器的输出信号频率,最终使两个信号相位差保持为常数,达到频率相等。

锁相环的工作过程:如图1所示,若o i f f ≠,必将引起ϕ∆的变化,鉴相器输出正比于ϕ∆的误差电压()d u t 。

经环路滤波器滤除()d u t 中的高频分量和噪声,产生缓慢变动的直流电压()c u t 。

VCO 受控于()c u t ,使得振荡频率o f 与输入参考频率i f 的频差逐渐减小,直到o i f f =,电路达到稳定平衡状态,即锁定状态。

此时,ϕ∆保持一个不变的稳态相差ϕ∞,以维持电路的平衡状态。

需要指出,环路能达到锁定状态,是在o f 与i f 相差不大的范围内。

2. 几个重要概念 ⑴ 失锁与锁定开始工作时, o i f f ≠,ϕ∆不固定,环路处于不稳定状态,称为失锁。

当o i f f =时,ϕ∆保持常数,电路进入稳定状态,称为锁定。

⑵ 跟踪过程与捕捉过程在环路锁定状态下,如果输入信号频率i f 发生变化,环路通过自身的调节作用,使输出信号频率o f 以同样的规律跟随着变化,并且始终保持o i f f =,这个过程称为跟踪过程或同步过程。

锁相实验心得(通用5篇)锁相实验心得篇1锁相实验是一种用于研究信号处理和系统同步的重要实验方法。

在本次实验中,我们主要探讨了锁相环路的原理、设计及其在控制系统中的应用。

通过本次实验,我对锁相环路的原理和设计有了更深入的理解,并在实践中提高了自己的技能。

在实验中,我们首先介绍了锁相环路的背景和意义。

作为一种常见的信号处理方法,锁相环路在许多领域中都有着广泛的应用,如通信、控制和测量等。

通过对其工作原理和特性的学习,我对锁相环路的应用有了更清晰的认识。

接着,我们详细讲解了锁相环路的原理和设计。

通过模拟仿真和实际电路搭建,我对锁相环路的性能和参数调整有了更深入的了解。

我学会了如何根据具体应用场景选择合适的环路带宽、相位裕度等参数,以实现系统同步和稳定。

在实验过程中,我遇到了一些问题,如电路调试不成功、参数调整不当等。

通过查阅资料和与同学讨论,我找到了问题的原因并加以解决。

这些问题让我更加深入地理解了锁相环路的原理和设计,提高了我的实践技能。

通过本次实验,我收获颇丰。

我深刻理解了锁相环路的原理和设计,掌握了其应用技巧。

同时,我也发现了自己在实验中的不足之处,如对电路理论知识的欠缺、实验技能的提升等。

在未来的学习和工作中,我将继续努力,提高自己的理论水平和实践能力,以更好地应对各种挑战。

总之,本次实验让我对锁相环路的原理和设计有了更深入的理解,提高了我的实践技能。

我将继续深入学习相关理论,并将其应用于实践中,为未来的研究和工作打下坚实的基础。

锁相实验心得篇2在进行锁相实验的过程中,我不仅加深了对相关理论知识的理解,还提高了自己的实验技能。

这次经历使我对信号处理和自动控制有了更深入的认识。

在实验中,我首先根据实验要求,搭建了锁相实验的电路。

我仔细检查了电路连接,确保无误。

然后,我输入待测信号,并观察了实验结果。

通过对比实验结果和预期结果,我发现自己的实验技能有了显著提高。

在实验过程中,我遇到了一些问题。

例如,在调整电路参数时,我无法使输入信号与反馈信号保持相位同步。

本科生毕业设计(申请学士学位)论文题目基于Matlab的数字锁相环的仿真设计作者专业名称电子信息工程指导教师2014年5月学生:(签字)学号:答辩日期:2014 年 5 月24 日指导教师:(签字)目录摘要 (1)Abstract (1)1 绪论 (2)1.1 本文研究背景 (2)1.2 本文研究意义 (2)1.3 锁相环和仿真方式 (2)1.3.1 锁相环 (2) (2)3 2 模拟锁相环Matlab仿真 (3)2.1 模拟锁相环方案 (3)2.1.1 模拟鉴相器 (3)2.1.2 模拟低通滤波器 (6)2.1.3 模拟压控振荡器 (7)2.2 模拟锁相环仿真 (8)2.3 本章小结 (9)3 数字锁相环Matlab仿真 (10)3.1 数字锁相环方案 (10)3.1.1 数字鉴相器 (10)3.1.2 数字滤波器 (12)3.1.3 数字压控振荡器 (13)3.2 数字锁相环仿真 (14)3.3 本章小结 (15)4 总结与展望 (15)参考文献 (16)致 (18)基于Matlab的数字锁相环的仿真设计摘要:锁相环是一种能够自动跟踪信号相位并达到锁频目的的闭环负反馈系统。

数字锁相环在无线电领域得到较广泛的应用和发展。

而且已经成为雷达、通信、导航等各类电子信号产品不可替代的元器件之一。

锁相环的窄带跟踪性能使其得到较广泛应用。

因为锁相技术在实际应用中较为复杂,所以锁相环的设计通常采用仿真设计这种方式。

本次设计采用Matlab这一软件进行辅助仿真设计,完全能达到设计预期的目标。

Matlab中的Simulink仿真软件,具有很强的灵活性和直观性。

本次设计所采用的方法是在simulink中搭建模拟锁相的模型,并对模拟锁相环的组成、结构、设计进行不断的分析和改进。

然后根据模拟锁相环的原理进行改进,并搭建数字锁相环。

关键词:锁相环;自动跟踪;matlab;simulinkSimulative design of digital phase-locked loop based onMatlabAbstract:PLL is the automatic tracking system of close loop atracking signal phase. It is widely used in various fields of radio. It has become an irreplaceable part of radar, communication, navigation and all kinds of electronicsignal device. PLL is able to be widely used. Because, it has unique narrow-band tracking performance. However, because of the complexity of phase lock technique, for the design of PLL have brought great difficulty. This design uses Matlab, the simulative software for design assistance, can completely meet the design expectations. Simulink simulative software on Matlab, has strong flexibility and intuitive. Methods used by this project is to build the analog phase locked in the Simulink model, and the composition, structure, design of analog phase-locked loop of continuous improvement and analysis. It improved according to the principle of analog PLL, build digital phase-locked loop in Simulink, and then reach the simulation design of digitalphase-locked loop based on Matlab the design objective .Key words: PLL, Automatic tracking, Matlab, simulink1 绪论1.1 本文研究背景19世纪30年代法国H.de Bellescize首次提出同步检波这一概念,并且设计出锁相环电路这一划时代的研究成果[1]。

实验八模拟锁相环应用实验一、实验目的1、掌握模拟锁相环的组成及工作原理。

2、学习用集成锁相环构成锁相解调电路。

3、学习用集成锁相环构成锁相倍频电路。

二、锁相环路的基本原理1、锁相环路的基本组成锁相环是一种以消除频率误差为目的的反馈控制电路,但它的基本原理是利用相位误差电压去消除频率误差,所以当电路达到平衡状态之后,虽然有剩余相位误差存在,但频率误差可以降低到零,从而实现无频差的频率跟踪和相位跟踪。

锁相环由三部分组成,如图8-1所示。

图8-1 锁相环组成方框图它包含压控振荡器(vco),鉴相器(pd)和环路滤波器(LF)三个基本部件,三者组成一个闭合环路,输入信号为v i(t),输出信号为v o(t),反馈至输入端。

下面逐一说明基本部件的作用。

1)压控振荡器(VCO)VCO是本控制系统的控制对象,被控参数通常是其振荡频率,控制信号为加在VCO上的电压,故称为压控振荡器,也就是一个电压一频率变换器,实际上还有一种电流一频率变换器,但习惯上仍称为压控振荡器。

2)鉴相器(PD)PD是一相位比较装置,用来检测输出信号v o(t)与输入信号v i(t)之间的相位差θe(t),并把θe(t)转化为电压v d(t)输出,v d(t)称为误差电压,通常v d(t)为一直流量或一低频交流量。

3)环路滤波器(LF)LF为一低通滤波电路,其作用是滤除因PD的非线性而在v d(t)中产生的无用的组合频率分量及干扰,产生一个只反映θe(t)大小的控制信号v c(t)。

按照反馈控制原理,如果由于某种原因使VCO的频率发生变化使得与输入频率不相等,这必将使v o(t)与v i(t)的相位差θe(t),发生变化,该相位差经过PD转换成误差电压v d(t),此误差电压经LF滤波后得到v c(t),由v c(t)去改变VCO的振荡频率使趋近于输入信号的频率,最后达到相等。

环路达到最后的这种状态就称为锁定状态,当然由于控制信号正比于相位差,即v d(t)∝θe(t)因此在锁定状态,θe(t)不可能为0,换言之在锁定状态v o(t)与v i(t)仍存在相位差。

实验五 锁相环路的实验研究一、实验目的1.通过实验深入了解锁相环的工作原理和特点。

2.初步掌握锁相环主要参数的测试方法。

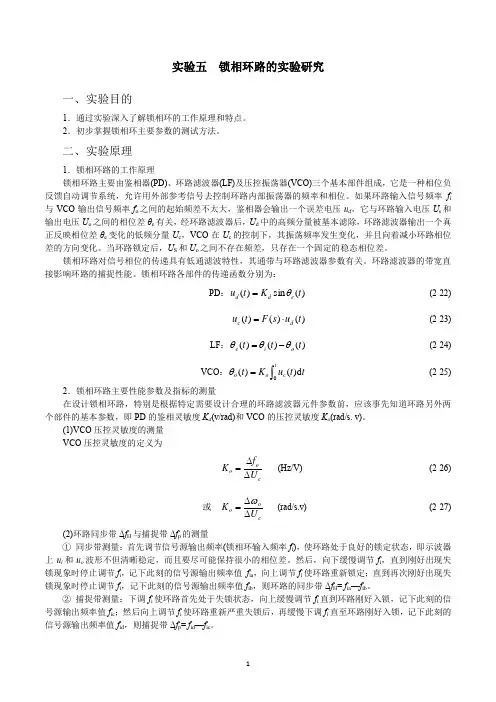

二、实验原理1.锁相环路的工作原理锁相环路主要由鉴相器(PD)、环路滤波器(LF)及压控振荡器(VCO)三个基本部件组成,它是一种相位负反馈自动调节系统,允许用外部参考信号去控制环路内部振荡器的频率和相位。

如果环路输入信号频率f i 与VCO 输出信号频率f o 之间的起始频差不太大,鉴相器会输出一个误差电压u d ,它与环路输入电压U s 和输出电压U o 之间的相位差θe 有关,经环路滤波器后,U d 中的高频分量被基本滤除,环路滤波器输出一个真正反映相位差θe 变化的低频分量U c ,VCO 在U c 的控制下,其振荡频率发生变化,并且向着减小环路相位差的方向变化。

当环路锁定后,U S 和U o 之间不存在频差,只存在一个固定的稳态相位差。

锁相环路对信号相位的传递具有低通滤波特性,其通带与环路滤波器参数有关。

环路滤波器的带宽直接影响环路的捕捉性能。

锁相环路各部件的传递函数分别为:PD :)(sin )(t K t u e d d θ= (2-22))()()(t u s F t u d c ⋅= (2-23)LF :)()()(t t t o i e θθθ-= (2-24)VCO :0()()d to o c t K u t t θ=⎰ (2-25) 2.锁相环路主要性能参数及指标的测量在设计锁相环路,特别是根据特定需要设计合理的环路滤波器元件参数前,应该事先知道环路另外两个部件的基本参数,即PD 的鉴相灵敏度K d (v/rad)和VCO 的压控灵敏度K o (rad/s. v)。

(1)VCO 压控灵敏度的测量VCO 压控灵敏度的定义为o o cf K U ∆=∆ (Hz/V) (2-26) 或 c o o U K ∆∆=ω (rad/s.v) (2-27) (2)环路同步带Δf H 与捕捉带Δf p 的测量① 同步带测量:首先调节信号源输出频率(锁相环输入频率f i ),使环路处于良好的锁定状态,即示波器上u i 和u o 波形不但清晰稳定,而且要尽可能保持很小的相位差。

实验三模拟锁相环与载波同步实验一、实验目的1. 掌握模拟锁相环的工作原理,以及环路的锁定状态、失锁状态、同步带、捕捉带等基本概念2. 掌握用平方环法从2DPSK信号中提取相干载波的原理及模拟锁相环的设计方法3. 了解相干载波相位模糊现象产生的原因二、实验内容1. 观察模拟锁相环的锁定状态、失锁状态及捕捉过程2. 观察环路的捕捉带和同步带3. 用平方环法从2DPSK信号中提取载波同步信号,观察相位模糊现象三、基本原理常用平方环或同相正交环(科斯塔斯环)从2DPSK信号中提取相干载波。

本实验用平方环,其原理方框图及电路原理图如图3-1、图3-2所示。

图3-1 载波同步方框图载波同步模块上有以下测试点及输入输出点:2DPSK-IN 2DPSK信号输入点MU 平方器输出测试点,VP-P>1V COMP 锁相环输入信号测试点Ud 锁相环压控电压测试点VCO 锁相环输出信号测试点,VP-P>0.2VCAR-OUT 相干载波信号输出点/测试点图3-1中各单元与图3-2中的主要元器件的对应关系如下:平方器 U2:模拟乘法器MC1496 鉴相器 U4: 锁相环HC4046环路滤波器 U4: 锁相环HC4046压控振荡器 U4: 锁相环HC4046÷2 U6:D触发器74HC74移相器 U8:单稳态触发器74LS123滤波器电感L1;电容C43压控振荡器 U5: 锁相环CD4046锁相环由鉴相器(PD)、环路滤波器(LF)及压控振荡器(VCO)组成,如图3-3所示。

图3-3 锁相环方框图模拟锁相环中,PD是一个模拟乘法器,LF是一个有源或无源低通滤波器。

锁相环路是一个相位负反馈系统,PD检测ui(t)与uo(t)之间的相位误差并进行运算形成误差电压ud(t),LF用来滤除乘法器输出的高频分量(包括和频及其他的高频噪声)形成控制电压uc(t),在uc(t)的作用下、uo(t)的相位向ui(t)的相位靠近。

设ui(t)=Uisin[ωit+θi(t)],uo(t)=Uocos[ωit+θo(t)],则ud(t)=Udsinθe(t),θe(t)=θi(t)-θo(t),故模拟锁相环的PD是一个正弦PD。

实验报告数值大小不同,环路的工作情况也不同。

若1w ∆较小,处于环路滤波器的通频带内,则差拍误差电压()e u t 能顺利通过环路滤波器加到VCO 上,控制VCO 的振荡频率,使其随差拍电压的变化而变化,所以VCO 输出是一个调频波,即()y w t 将在yo w 上下摆动。

由于1w ∆较小,所以()y w t 很容易摆动到i w ,环路进入锁定状态,鉴相器将输出一个与稳态相位差对应的直流电压,维持环路动态平衡。

若瞬时角频差1w ∆数值较大,则差拍电压()e u t 的频率较高,它的幅度在经过环路滤波器时可能受到一些衰减,这样VCO 的输出振荡角频率()y w t 上下摆动的范围也将减小一些,故需要多次摆动才能靠近输入角频率()i w t ,即捕捉过程需要许多个差拍周期才能完成,因此捕捉时间较长,若1w ∆太大,将无法捕捉到,环路一直处于失锁状态。

能够由失锁进入锁定所允许的最大固有角频差1m w ∆的两倍称为环路的捕捉带。

3、集成锁相环NE564介绍及应用(1)在本实验中,所使用的锁相环为NE564(国产型号为L564)是一种工作频率可高达50MHz 的超高频集成锁相环。

'其内部框图和脚管定义如图8-2。

其内部电路原理图如图8-3。

a、在图8-2(a )中,A1(LIMITER )为限幅放大器,它主要由原理图中的Q1~Q5及Q8,Q7组成。

Q1~Q5组成PNP ,NPN 互补的共集—共射组合差分放大器,由于Q2,Q3负载并联有肖特基二极管D1,D2,故其双端输出电压被限幅在20.3~0.4D V v =左右。

因此可有效消除FM 信号输入时,干扰所产生的寄生调幅。

Q7,Q8为射极输出差放,以作缓冲,其输出信号送鉴相器。

(a)NE564内部框图(b)NE564管脚分布图图8-2 锁相环内部框图和引脚图b、鉴相PD (PHASE COMPARATOR )采用普通双差分模拟相乘器,由压控振荡器反馈过来的信号从外部由③端输入。

simulink仿真锁相环工作原理

Simulink仿真锁相环的工作原理如下:

1. 锁相环由相位比较器、低通滤波器、电压控制振荡器(VCO)以及除频

器组成。

2. 相位比较器接收输入信号和反馈信号,并输出相位误差,表示输入信号和反馈信号之间的相位差。

3. 低通滤波器对相位误差进行滤波处理,产生直流偏置电压,控制VCO的频率调节。

4. 电压控制振荡器根据LF输出的直流偏置电压调整自身的振荡频率,将VCO的输出信号作为反馈信号输入到PD中。

5. 除频器根据设定的除数将VCO输出的频率进行分频,输出给相位比较器,以提供稳定的参考信号。

以上是锁相环的工作原理,如需了解更多信息,建议查阅相关书籍或咨询专业人士。

实验十 锁相环电路测试一、实验目的1. 加深对锁相环基本工作原理的理解。

2. 掌握锁相环同步带、捕捉带的测试方法,增加对锁相环捕捉、跟踪和锁定等概念的理解。

3. 掌握集成锁相环CD4046的使用方法。

二、实验仪器1.锁相环调频与测试电路实验板2.高频信号源、低频信号源、100MHz 双踪示波器、万用表。

三、锁相环与CD4046集成锁相环锁相环由相位比较器(PC)、低通滤波器( LP)、压控振荡器( VCO)三个基本部件组成。

锁相环路是一个相位误差控制系统,它将参考信号与输出信号之间的相位进行比较,产生相位误差电压来调整输出信号的相位,以达到与参考信号同频的目的。

锁相环路由于具有良好的跟踪特性、窄带滤波特性和良好的门限特性等一些特殊的性能,而广泛应用于电子技术的各个领域。

图10-1是锁相环的构成框图。

图10-1锁相环的构成框图相位比较器用来比较输入信号)(t u i 与压控振荡器输出信号)(t u o 的相位,输出电压对应于这两个信号相位差的函数,称为误差电压)(t u d 。

低通滤波器是滤除)(t u d 高频分量及噪声,输出低频分量。

压控振荡器受环路滤波器输出低频电压)(t u C 的控制,使振荡频率向输入信号的频率靠拢,最后如果压控振输出信号的频率和输入信号的频率保持一致,两者的相位差保持某一恒定值,则相位比较器的输出将是一个恒定直流电压,低通滤波器的输出就是一个直流电压,这时,环路处于“锁定状态”。

与锁相环有关的几个基本概念:环路锁定: 如果环路有一个输入信号)(t u i ,开始时输入频率i ω不等于VCO 的振荡频率o ω,即o i ωω≠。

如果i ω 与o ω 相差不大,在适当的范围内,相位比较器输出一误差电压)(t u d ,经低通滤波器后输出)(t u C ,控制VCO 的频率,使其输出频率变化接近到i ω,趋向o i ωω=,而且两信号的相位差为常数,这种状态称为环路锁定。