ARINC429总线接口电路设计及仿真

- 格式:doc

- 大小:26.50 KB

- 文档页数:7

第Z 8卷!第Z 期Z O O 5年6月电!子!器!件C h i n e s e J o u r n a l o f e l e c t r o nd e v i c e sV o l .Z 8!No .Z J u n .Z O O 5D e s i g n a n d I m pl e m e n t a t i o n o f aU S B -B a s e dA R I N C 429I n t e r f a c e Z h O Ud e -s i n 9F a n Z h i -$o n g(A e r o n a u t i c a \e c h a n i c a 8A u i o n i c s e n g i n e e r i n g C o e g e 9C A U C 9T i a n ji n 3O O 3O O 9C h i n a )A b s t r a c t :W i t hm o d u l a rm e t h o d 9t h i s d e s i g n i n t e g r a t e s t h e t r a n s m i t a n d r e c e i v e f u n c t i o n o f A R I N C 4Z 9s i g-n a l a n dt h ec o n t r o l l o g i ct o U S B b u si no n eF P G A c h i p 9W h i c ha c t u a l i z e st h es i g n a lc o n v e r s i o no f A R I N C 4Z 9t oU S Ba n d i m p r o v e s t h e r e l i a b i l i t y a n d f l e x i b i l i t yi n d a t a t r a n s f e r .K e y w o r d s :A R I N C 4Z 99U S B 9F P G A 9b u s i n t e r f a c e E E A C C :1265B基于U S B 的A R I N C 429总线接口设计与实现周德新!樊智勇(中国民用航空学院机电工程学院9天津3O O 3O O)收稿日期!Z O O 4-11-1Z摘!要!A R I N C 4Z 9总线是美国航空无线电公司(A R I N C)制定的民用航空数字总线传输标准9广泛应用于航空电子系统的数据传输D 本设计采用模块化的设计方法9将A R I N C 4Z 9信号的接收与发送功能以及对U S B 总线的控制逻辑集成于一块F P G A 中9实现了A R I N C 4Z 9信号与U S B 信号的转换9提高了数据传输的可靠性和灵活性D 关键词!A R I N C 4Z 99U S B 9F P G A 9总线接口中图分类号!T E 832.2"T P 331.1!!文献标识码!A !!文章编号!1005-9490#2005$02-0432-03!!在实际的航空电子设备的测试过程中9首先要解决的就是测试系统(计算机)和A R I N C 4Z 9总线间的接口问题D 目前9U S B (U n i v e r s a l S e r i a lB u s 9通用串行总线)已成为P C 机上的标准接口9具有即插即用~热插拔~接口体积小巧~节省系统资源~传输可靠~提供电源和低成本等优点D 本设计主要作为A 3Z 1飞机音频系统综合校验测试仪的信号转换部分而开发的D 采用F P G A 实现A R I N C 4Z 9总线与U S B 总线间的接口电路9有效地缩小了系统的体积9增加了系统配置的灵活度的提高了4Z 9总线设备的检测效率D1!AR I N C 429总线简介A R I N C 4Z 9总线是一种单向广播式数据总线9数据采用双极性归零码开环传输9调制信号由 高 ~零 和 低 三种状态组成D 传输的标准速率为:高速传输位速率1O O k b /s 9低速传输位速率1Z .5k b /s D 通信设备间双向传输时9需要在两个方向上各用一根独立的传输总线 1I DA R I N C 4Z 9数据字由3Zb i t 组成9每个数据字分为5组:1。

信Q与电1BChina Computer&Communication网絡与通信孜术2021年第5期基于HI-3593的ARINC429总线接口设计张杰侯大勇刘光明(苏州长风航空电子有限公司,江苏苏州215151)摘要:ARINC429总线具有结构简单、性能稳定、传输可靠、抗干扰能力强等特征.在需要高可靠性、高集成度设计的应用领域,可以采用SPI接口的ARINC429协议芯片HI-3593实现数据协议处理,与ARM处理器完成ARINC429总线数据收发功能.基于此,笔者围绕该系统架构分析了各部分的功能,并对硬件接口进行了详细设计.关键词:ARINC429协议芯片;ARM处理器;SPI接口中图分类号:V243文献标识码:A文章编号:1003-9767(2021)05-216-03Design of ARINC429Bus Interface Based on HI-3593ZHANG Jie,HOU Dayong,LIU Guangming(Suzhou Changfeng Avionics Co.,Ltd.,Suzhou Jiangsu215151,China)Abstract:The ARINC429bus has the characteristics of simple structure,stable performance,reliable transmission,and strong anti-interference ability.In application areas that require high reliability and high integration design,the ARINC429protocol chip HI-3593with SPI interface can be used to realize data protocol processing,and the ARINC429bus data transceiver function can be completed with the ARM processor.Based on this,the author analyzes the functions of each part around the system architecture,and designs the hardware interface in detail.Keywords:ARINC429protocol chip;ARM processor;SPI interface0引言ARINC429总线在当代的战斗机、运输机和民航客机中有着广泛的应用。

ARINC429总线接口电路设计及仿真作者:申广兵来源:《科技视界》2013年第13期【摘要】本文简要地介绍了ARINC429总线传输规范及数据特性,并对某型发射装置外场测试设备中的ARINC429总线接口的结构和功能进行了分析,然后利用VHDL语言对其逻辑功能进行了描述,最后借助于XILINX Spantan-3 FPGA进行了逻辑功能仿真验证。

【关键词】ARINC429;FPGA;VHDL0 引言ARINC429总线是目前在航空电子领域内广泛应用的一种数字信息传输标准,随着数字化传输技术的不断发展,其应用范围愈加广泛。

同样ARINC429总线在导弹发射装置及其测试设备中也得到了广泛地应用,本文研究一种利用FPGA并借助于VHDL语言来实现某外场测试设备中 ARINC429总线接口数字部分的设计方案,它克服了传统的ARINC429接口芯片固有的缺点,使系统的综合性能得到了明显的改善和提高。

1 ARINC 429总线简介[1]ARINC429总线是一种数字信息传输标准,它采用双极性归零码进行数据调制,并通过一对双绞屏蔽线进行反相传输,因此具有很强的抗干扰能力。

一个ARINC429数字信息字由32个码位组成,共分为五段,其字格式如表1所示。

表1 ARINC429数字字格式ARINC429的32位数据字采用双极性归零方式进行调制,然后以脉冲形式进行发。

发送的脉冲电平有三种:高电平(+10V)、0电平(0V)以及低电平(-10V),分别对应于逻辑1、发送时钟脉冲和逻辑0,并且高低电平只在每一个发送时钟周期的前一半有效,在后一半周期,电位回到0电平,以保持发送信息与时钟的同步。

ARINC429总线以单向串行方式传输数字信息,其传输速率分为100kbps(高速)和12.5kbps(低速)两种,可以通过相应的控制位来实现高低传输速率的选择,但两者不得在同一总线中混用。

2 基于FPGA的实现方案基于FPGA的ARINC429总线接口设计采用了数字系统设计中广泛应用的“自顶向下”的设计方法,首先从总体上对系统进行功能、层次的分解,然后对各子系统和模块进行基于VHDL 语言的详细设计,最后在进行逻辑功能仿真和综合时序仿真的基础上进行了系统集成。

工业技术科技创新导报 Science and Technology Innovation Herald67A R I N C 429总线广泛应用于航空机载设备,对429总线的测试需求导致了各种测试系统的出现[1-3]。

在某型飞机的液压能源和起落架系统总装调试过程中,由于航电机组成员告警系统和中央维护系统安装调试未完成,系统的单独调试缺乏对总线信号的模拟和测试而困难重重,当航电系统存在错误时,单是依靠机组告警显示页就很难定位故障,因为有时故障是显示页面本身。

通用的A R I N C 429总线测试设备只显示32比特数据,不能直观的反应系统的状态和参数的变化,工程人员需要根据接口控制文件挨个查阅并换算总线的二进制数为系统参数,增加了系统调试的时间。

在外场排故过程中,时间更为宝贵,需要快速定位并排除故障。

综合上述的应用场合,测试系统不仅需要读取并解析总线数据,确保发送给系统或者系统发出的数据正常;还需要仿真总线数据,用于模拟系统状态或故障信息;对数据的显示需要直观,能一目了然发现状态异常的信号;此外还对设备的便携性有一定要求。

1 ARINC429总线A R I N C 429总线协议是美国航空电子工程委员会(Ai rli n es E n g i n e e r i n g C o m m it t e e)提出的航空数字总线传输标准,协议标准规定了航空电子设备及有关统间的数字信息传输规范。

A R I N C 429协议以单向方式传输数字数据信息,传输速率分高低两档,高速状态的位速率为100 K b/s,低速状态的位速率12.5 Kb/s。

A R I N C 429总线数据每个字由32位组成,见图1。

其中,第32位为奇偶校验位(Parity bit),它用于检查发送的数据在传输过程中是否有丢失或破坏。

29位或30位到31位为符号状态矩阵位(Sig n /St at u s M a t r i x ,S S M ),它指出数据的特性。

基于USB的ARINC429总线接口模块设计引言ARINC429总线由美国航天无线电设备公司所资助,是广泛应用于当前航空电子设备中的一种数据总线传输标准。

与传统的航空电子设备间的模拟传输相比,ARINC429总线具有抗干扰能力强、传输精度高、传输线路少以及成本低等优点。

ARINC数据总线协议规定一个数据由32位组成,采用双极性归零码,以12.5Kb/s或100Kb/s码速率传输。

本设计利用USB即插即用、FPGA可灵活配置等特点,设计了基于USB总线的ARINC429总线接口模块。

接口模块总体设计结构接口模块总体设计包括硬件设计和软件设计两部分。

硬件设计由USB接口芯片,FPGA和调制/解调电路三部分组成。

硬件设计整体框软件设计主要包括USB-ARINC仪器驱动程序,USB设备驱动程序以及底层USB固件程序的设计。

软件设计整体框接口模块硬件设计接口模块硬件部分由USB接口芯片,FPGA和调制/解调电路三部分组成。

下面以一路429设备为例来介绍接口模块的发送和接收部分的硬件设计。

发送部分硬件设计发送部分硬件设计框USB接口芯片CY68013负责接收PC机传来的32 位429数据字,并传输给PC机所指定的429总线设备。

由于要传输给多路429总线设备,所以PC机还必须给每一个429数据字加上一个设备通道号。

由于在测试ARINC429电子设备中,时常要求多路ARINC429总线同时传输数据。

为了实现接口模块多路ARINC429总线同时工作,本设计采用了一个全局start/stop信号。

当PC机传下start信号后,FPGA中各路的发送控制模块开始将RAM中数据取出并传输给移位寄存器。

移位寄存器再将并行输入的32位。

ARINC-429总线信号源电路设计与开发作者:李国星白仲斐支高飞来源:《硅谷》2011年第10期摘要:以单片机和可编程逻辑芯片为核心,结合ARINC-429总线控制、驱动芯片,设计出ARINC-429总线数据的收发电路,配合上位机软件,实现对机载ARINC-429信号的仿真,从而便于对该型总线的工程排故。

关键词:单片机;可编程逻辑芯片;航空总线;ARINC-429总线中图分类号:TP334.7 文献标识码:A 文章编号:1671-7597(2011)0520055-010 引言ARINC-429总线是美国航空无线电公司(ARINC)制定的一种航空串行数据总线标准,在当代运输机和民航客机(如A310、A300、B757、B767等)以及军用飞机中得到了广泛的应用[1]。

随着国内航空业的发展,ARINC-429总线已大量使用在机载设备当中[2]。

因此,实现对机载ARINC-429总线的仿真,对排除ARINC-429总线故障,具有重要的意义。

基于单片机和可编程逻辑芯片CPLD,运用ARINC-429总线控制和驱动芯片,本文设计出了ARINC-429总线信号源电路,从而实现了该类型总线数据的收发功能。

1 ARINC-429信号特性[3][4]ARINC-429总线协议规定数字信息采用一对单向、差分耦合、双绞屏蔽线传输,采用双极性归零制的三态调制方式BNR码,即“高”、“零”和“低”状态组成的三电平调制状态。

双绞线中的差分电压在+7.25~+11V,逻辑状态为“高”;差分电压在-0.5~+0.5V时,逻辑状态为“零”;差分电压在-11~-7.25V时,逻辑状态为“低”。

因此,ARINC-429总线具有很强的抗干扰能力。

2 方案设计与实现2.1 方案设计ARINC429总线信号源由计算机软件和信号处理电路构成,如图1所示。

计算机软件实现对ARINC429总线数据的设置。

信号处理电路由单片机、逻辑控制芯片CPLD和ARINC-429控制、驱动芯片电路构成,主要实现对ARINC429总线数据的收、发功能。

ARINC429总线信号仿真和测试方案

或信息的终端。

11~28 或29 位是数据位(Data Field),是所确定的用于传输

的信息。

29 到30 或31 位为符号状态矩阵位(SSM),表示数据的特性或字类型,

也可表示发送设备的状态信息。

32 位为奇偶校验位(P),实现简单的数据校验

功能。

图2 429 信号32 位字格式

基本设计思想

设计航空429 总线信号的仿真和检测采用了虚拟仪器的设计思路。

简单

的说,虚拟仪器就是通用计算机加上软件和硬件。

硬件用来解决信号的输入输出问题,软件用来实现对信号的处理、显示等功能。

它利用计算机的强大支持,使用户可以很方便地对其维护、扩展和升级。

与传统仪器相比,虚拟仪器具有很高的灵活性,可以通过编制软件来定义功能。

目前在这一领域内,使用较为广泛的软件包括NI 公司的LabVIEW 和LabWindows/CVI,HP 公司的VEE 等。

设计中,硬件方面使用基于PCI 插槽的429 信号收发板卡,将其插入通

用电脑PCI 插槽达到了测试的硬件要求,实现429 信号的发送和接收;软件方面

使用NI 公司的LabWindows/CVI 作为开发平台,主要用来完成发送前的数据

准备、对接收数据的处理和显示等工作。

设计实现方法

硬件介绍

选用西安方元明公司代理的EXC_M4K429RTx 模块板卡。

该板卡的基本。

ARINC429总线接口电路设计及仿真

【摘要】本文简要地介绍了arinc429总线传输规范及数据特性,并对某型发射装置外场测试设备中的arinc429总线接口的结构和功能进行了分析,然后利用vhdl语言对其逻辑功能进行了描述,最后借助于xilinx spantan-3 fpga进行了逻辑功能仿真验证。

【关键词】arinc429;fpga;vhdl

0 引言

arinc429总线是目前在航空电子领域内广泛应用的一种数字信

息传输标准,随着数字化传输技术的不断发展,其应用范围愈加广泛。

同样arinc429总线在导弹发射装置及其测试设备中也得到了广泛地应用,本文研究一种利用fpga并借助于vhdl语言来实现某外场测试设备中 arinc429总线接口数字部分的设计方案,它克服了传统的arinc429接口芯片固有的缺点,使系统的综合性能得到了明显的改善和提高。

1 arinc 429总线简介[1]

arinc429总线是一种数字信息传输标准,它采用双极性归零码进行数据调制,并通过一对双绞屏蔽线进行反相传输,因此具有很强的抗干扰能力。

一个arinc429数字信息字由32个码位组成,共分为五段,其字格式如表1所示。

表1 arinc429数字字格式

arinc429的32位数据字采用双极性归零方式进行调制,然后以

脉冲形式进行发。

发送的脉冲电平有三种:高电平(+10v)、0电平(0v)以及低电平(-10v),分别对应于逻辑1、发送时钟脉冲和逻辑0,并且高低电平只在每一个发送时钟周期的前一半有效,在后一半周期,电位回到0电平,以保持发送信息与时钟的同步。

arinc429总线以单向串行方式传输数字信息,其传输速率分为

100kbps(高速)和12.5kbps(低速)两种,可以通过相应的控制位来实现高低传输速率的选择,但两者不得在同一总线中混用。

2 基于fpga的实现方案

基于fpga的arinc429总线接口设计采用了数字系统设计中广泛应用的“自顶向下”的设计方法,首先从总体上对系统进行功能、层次的分解,然后对各子系统和模块进行基于vhdl语言的详细设计,最后在进行逻辑功能仿真和综合时序仿真的基础上进行了系统集成。

2.1 逻辑功能分析及结构设计

429总线接口电路的主要功能是在429信号及相关外设之间起到桥梁作用,它既能接收双极归零制的429信号并将其转换为数字信号送入计算机或其它设备,又可将计算机或其它设备发出的数字信号转换为429信号输出。

由于各设备之间在处理速度、信号类型等方面存在差异,为了确保总线数据信息传输的正确性,arinc429总线接口电路应具备以下功能[2]:

1)电平转换。

arinc429两路双极性归零码的差分电压为±10v,与ttl电平(ttl‘0’和ttl‘1’)不匹配,因此需要借助于接口

电路来实现两者之间的相互转换;

2)数据缓冲及暂存。

为了保证在处理速度上存在差异的设备之间数据传输的完整性,需要对接收和发送的数据进行缓冲和暂存;3)数据格式转化。

arinc429数据与cpu处理的数据之间需进行必要的格式转换;

4)自检测及校验。

主要指发送数据的自检测、数据的奇偶检验和源/目的地识别码校验;

5)生成信息传输同步时钟信号,并可以进行信息传输速率的选择。

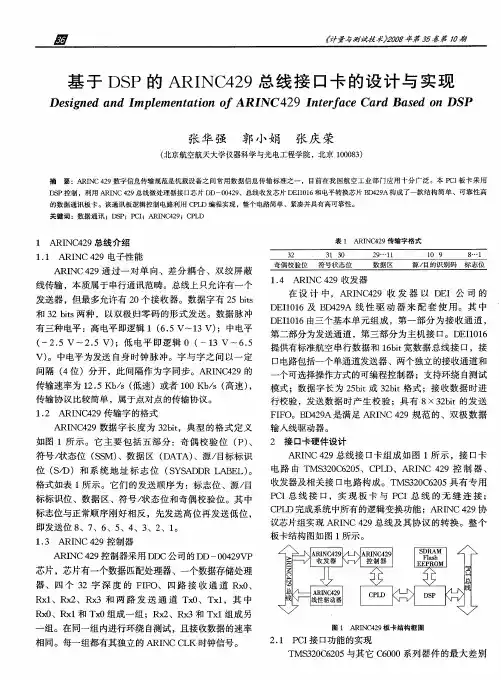

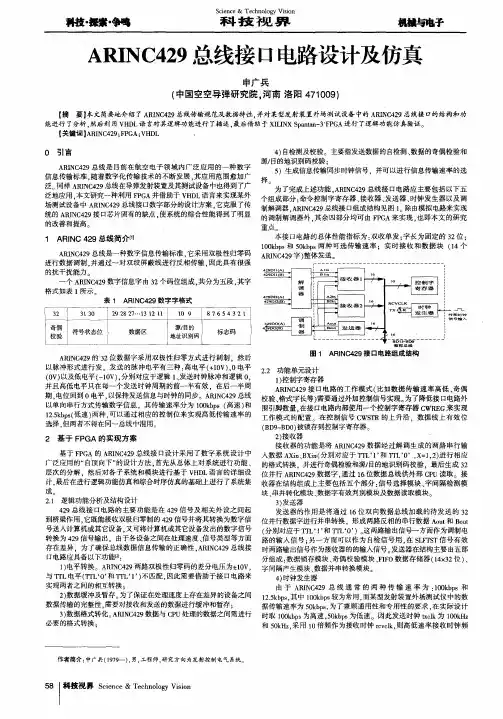

为了完成上述功能,arinc429总线接口电路应主要包括以下五个组成部分:命令控制字寄存器、接收器、发送器、时钟发生器以及调制解调器,arinc429总线接口组成结构见图1。

除由模拟电路来实现的调制解调器外,其余四部分均可由fpga来实现,也即本文的研究重点。

本接口电路的总体性能指标为:双收单发;字长为固定的32位;100kbps和50kbps两种可选传输速率;实时接收和数据块(14个arinc429字)整体发送。

图1 arinc429接口电路组成结构

2.2 功能单元设计

1)控制字寄存器

arinc429接口电路的工作模式(比如数据传输速率高低、奇偶校验、格式字长等)需要通过外加控制信号实现。

为了降低接口电路

外围引脚数量,在接口电路内部使用一个控制字寄存器cwreg来实现工作模式的配置。

在控制信号cwstr的上升沿,数据线上有效位(bd9-bd0)被锁存到控制字寄存器。

2)接收器

接收器的功能是将arinc429数据经过解调生成的两路串行输入数据axin、bxin(分别对应于ttl’1’和ttl’0’,x=1,2)进行相应的格式转换,并进行奇偶检验和源/目的地识别码校验,最后生成32位并行arinc429数据字,通过16位数据总线供外部cpu 读取。

接收器在结构组成上主要包括五个部分:信号选择模块、字间隔检测模块、串并转化模块、数据字有效判别模块及数据读取模块。

3)发送器

发送器的作用是将通过16位双向数据总线加载的待发送的32位并行数据字进行并串转换,形成两路反相的串行数据aout和bout (分别对应于ttl‘1’和ttl‘0’)。

这两路输出信号一方面作为调制电路的输入信号;另一方面可以作为自检信号用,在slftst 信号有效时两路输出信号作为接收器的的输入信号。

发送器在结构主要由五部分组成:数据锁存模块、奇偶校验模块、fifo数据存储器(14×32位)、字间隔产生模块、数据并串转换模块。

4)时钟发生器

由于arinc429总线通常的两种传输速率为:100kbps和

12.5kbps,其中100kbps较为常用,而某型发射装置外场测试仪中

的数据传输速率为50kbps,为了兼顾通用性和专用性的要求,在实际设计时取100kbps为高速,50kbps为低速。

因此发送时钟txclk 为100khz和50khz,采用10倍频作为接收时钟rcvclk,则高低速率接收时钟频率分别为1mhz和500khz。

这里取外部时钟clk为

8mhz,通过对clk进行8分频即可得到高速率时的接收时钟rcvclk,再对rcvclk进行10分频即可得到高速率时的发送时钟txclk。

低速时也可按此办法计算分频比例,从而得到发送时钟和接收时钟。

高低速率的选择通过cwreg中txsel和rcvsel来选择。

5)调制解调电路

解调电路由电压比较器来实现,它通过将arinc429两路反相信号(429a和429b)与基准电压比较,实现429电平到ttl电平的转换。

调制电路由差动运放器来实现,发送器的输出数据aout和bout通过差动运放转换成arinc429数据格式。

3 功能仿真

该arinc429接口电路采用xilinx spantan-3系列芯片xc3s400来实现数据的接收和发送功能,该芯片集成了400k个门电路,存储器单元为344k(其中分散的存储器位为56k,块存储器位为288k),用户可支配的i/o数高达264个[3]。

利用xilinx公司提供的fpga集成开发环境ise对设计进行了逻辑设计和功能仿真。

由于是进行逻辑功能仿真,主要目的是验证逻辑设计的正确性,因此在仿真时将数据字长度降低为8位,同时双向数据线相应地降为4位,字间隔为2位数据位。

接收器仿真结果

见图2,发送器仿真结果见图3。

图2 接收器工作时序

从接收器工作时序(图2)可以看出:该电路正确接收了符合校验条件的第一个字,而没有接收不满足预设偶校验条件的第二个数据;接收器仿真结果表明接收器工作正常。

图3 发送器工作时序

从发送器工作时序(图3)可以看出:在加载控制信号pl1和pl2的控制下四个8位数据(01100011,00110010,00010010,00110001)经过奇偶校验位重置后被加载载到fifo中,在发送使能entx为‘1’时,四个8位数据字在发送时钟txclk的控制下实现并串转换,并逐位输出,当fifo存储器中的四个字被依次发送完成后,发送完成标志txr被置‘1’,发送器仿真结果表明发送器工作时序正常。

4 结论

综上所述,fpga具有编程灵活、配置方便、可靠性高等优点,随着其综合性能的不断提升,fpga在现代数字电路系统设计中将扮演越来越重要的角色,而vhdl作为一种标准的与器件无关的硬件电路描述语言,可以很方便地实现设计的共享和移植。

本文研究的用vhdl语言描述并借助于fpga硬件来实现的arinc429接口电路,不仅可以很好地满足某型外场测试设备的相关要求,而且有利于提升整个系统设计的灵活性、可扩展性和可靠性。

【参考文献】

[1]arinc specification 429-12 mark33 digital information

transfer syestem[s]. the airline electronic enginerring committee,1990.

[2]hs-3282 cmos arinc bus interface reference

an400[z].1997,3.

[3]spartan-3 fpga family complete data sheet

ds009[z].2005,8.。