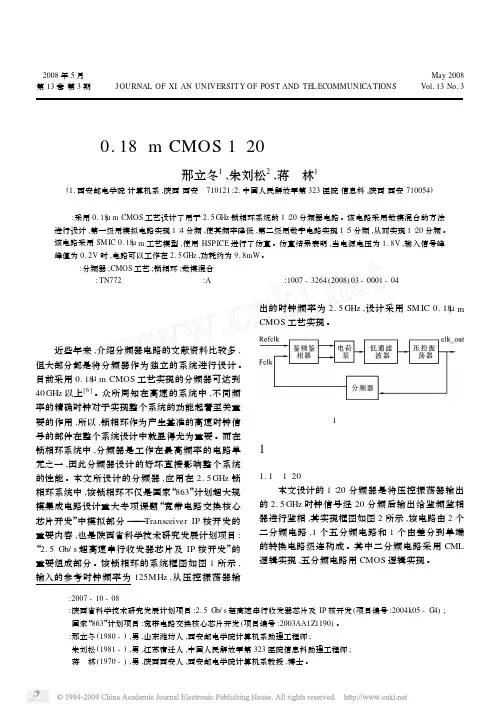

CMOS1:4分接器的设计

- 格式:pdf

- 大小:3.09 MB

- 文档页数:82

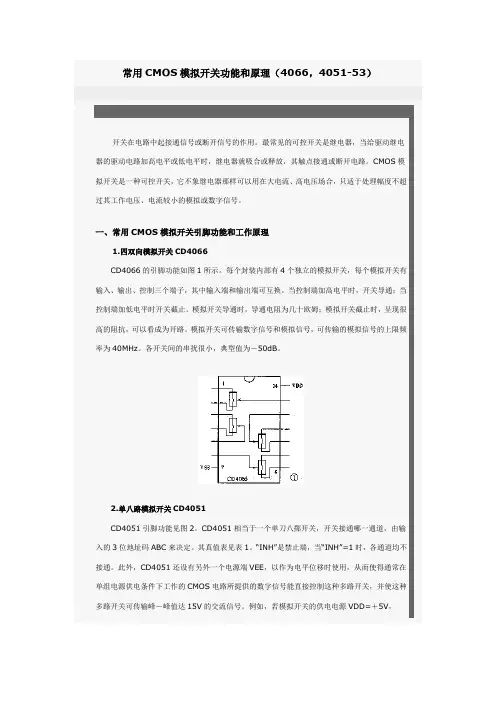

用固态继电器更加的不行!4051之类的模拟开关过模拟量不太精确,可考虑使用固态继电器发帖者IP:211.91.211.35发表时间:2003年4月7日13:21:47常用CMOS模拟开关功能和原理(4066,4051-53)二二、典型应用举例1.单按钮音量控制器单按钮音量控制器电路见图6。

VMOS管VT1作为一个可变电阻并接在音响装置的音量电位器输出端与地之间。

VT1的D极和S极之间的电阻随VGS成反比变化,因此控制模拟开关介绍与应用模拟开关是一种三稳态电路,它可以根据选通端的电平,决定输人端与输出端的状态。

当选通端处在选通状态时,输出端的状态取决于输人端的状态;当选通端处于截止状态时,则不管输人端电平如何,输出端都呈高阻状态。

模拟开关在电子设备中主要起接通信号或断开信号的作用。

由于模拟开关具有功耗低、速度快、无机械触点、体积小和使用寿命长等特点,因而,在自动控制系统和计算机中得到了广泛应用。

一、模拟开关的电路组成及工作原理模拟开关电路由两个或非门、两个场效应管及一个非门组成,如图一所示。

模拟开关的真值表见表一。

表一模拟开关的工作原理如下:当选通端E和输人端A同为1时,则S2端为0,S1端为1,这时VT1导通,VT2截止,输出端B输出为1,A=B,相当于输入端和输出端接通。

当选通E为0时,而输人端A为0时,则S2端为1,S1端为0,这时VT1截止,VT2导通,输出端B为0,A=B,也相当于输人端和输出端接通。

当选通端E为0时,这时VT1和VT2均为截止状态,电路输出呈高阻状态。

从上面的分析可以看出,只有当选通端E为高电平时,模拟开关才会被接通,此时可从A向B传送信息;当输人端A为低电平时,模拟开关关闭,停止传送信息。

二、常用的CMOS模拟开关集成电路根据电路的特性和集成度的不同,MOS模拟开关集成电路可分为很多种类。

现将常用的模拟开关集成电路的型号、名称及特性列入表二中。

表二常用的模拟开关三、CD4066模拟开关集成电路的应用举例CD4066是一种双向模拟开关,在集成电路内有4个独立的能控制数字及模拟信号传送的模拟开关。

CMOS(Complementary Metal Oxide Semiconductor)指互补金属氧化物(PMOS管和NMOS管)共同构成的互补型MOS集成电路制造工艺,它的特点是低功耗。

由于CMOS中一对MOS组成的门电路在瞬间看,要么PMOS导通,自1958年美国德克萨斯仪器公司(TI)发明集成电路(IC)后,随着硅平面技术的发展,二十世纪六十年代先后发明了双极型和MOS型两种重要的集成电路,它标志着由电子管和晶体管制造电子整机的时代发生了量和质的飞跃。

MOS是:金属-氧化物-半导体(Metal-Oxide-Semiconductor)结构的晶体管简称MOS晶体管,有P 型MOS管和N型MOS管之分。

由MOS管构成的集成电路称为MOS集成电路,而由PMOS管和NMOS管共同构成的互补型MOS集成电路即为CMOS-IC( Complementary MOS Integrated Circuit)。

目前数字集成电路按导电类型可分为双极型集成电路(主要为TTL)和单极型集成电路(CMOS、NMOS、PMOS等)。

CMOS电路的单门静态功耗在毫微瓦(nw)数量级。

CMOS发展比TTL晚,但是以其较高的优越性在很多场合逐渐取代了TTL。

以下比较两者性能,大家就知道其原因了。

1.CMOS是场效应管构成,TTL为双极晶体管构成2.CMOS的逻辑电平范围比较大(5~15V),TTL只能在5V下工作3.CMOS的高低电平之间相差比较大、抗干扰性强,TTL则相差小,抗干扰能力差4.CMOS功耗很小,TTL功耗较大(1~5mA/门)5.CMOS的工作频率较TTL略低,但是高速CMOS速度与TTL差不多相当。

集成电路中详细信息:1,TTL电平:输出高电平>2.4V,输出低电平<0.4V。

在室温下,一般输出高电平是3.5V,输出低电平是0.2V。

最小输入高电平和低电平:输入高电平>=2.0V,输入低电平<=0.8V,噪声容限是0.4V。

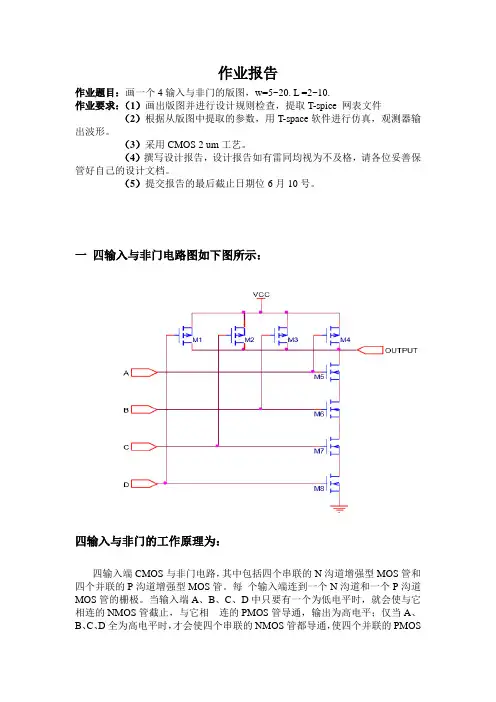

作业报告作业题目:画一个4输入与非门的版图,w=5~20. L =2~10.作业要求:(1)画出版图并进行设计规则检查,提取T-spice 网表文件(2)根据从版图中提取的参数,用T-space软件进行仿真,观测器输出波形。

(3)采用CMOS 2 um工艺。

(4)撰写设计报告,设计报告如有雷同均视为不及格,请各位妥善保管好自己的设计文档。

(5)提交报告的最后截止日期位6月10号。

一四输入与非门电路图如下图所示:四输入与非门的工作原理为:四输入端CMOS与非门电路,其中包括四个串联的N沟道增强型MOS管和四个并联的P沟道增强型MOS管。

每个输入端连到一个N沟道和一个P沟道MOS管的栅极。

当输入端A、B、C、D中只要有一个为低电平时,就会使与它相连的NMOS管截止,与它相连的PMOS管导通,输出为高电平;仅当A、B、C、D全为高电平时,才会使四个串联的NMOS管都导通,使四个并联的PMOS管都截止,输出为低电平。

真值表如下所示:二版图的绘制这次作业要求四输入与非门的宽和长的范围是w=5~20. L =2~10。

我绘制的版图选取W=16 um L=2um ,绘制的过程为:(1)绘制接合端口Abut(2)绘制电源Vdd和Gnd,以及相应端口(3)绘制Nwell层(4)绘制N阱节点(5)绘制衬底节点(6)绘制Nselect区和Pselect区(7)绘制NMOS有源区和PMOS有源区(8)绘制多晶硅层(9)绘制NAND 4 的输入口(10)绘制NAND 4 的输出口(11)绘制NMOS有源区和PMOS的源极三T-spice仿真在绘制完版图之后,经过设计规则检查无误后就可以提取网表进行仿真了。

(1)版图的网表提取结果为:* Circuit Extracted by Tanner Research's L-Edit Version 13.00 / Extract Version 13.00 ; * TDB File: D:\20113250\youwenhao-NAND4.tdb* Cell: Cell0 Version 1.03* Extract Definition File: D:\Tanner EDA\Tanner Tools v13.0\ExampleSetup\lights.ext* Extract Date and Time: 06/10/2014 - 01:20.include "C:\Users\Administrator\Desktop\ml5_20.md"V1 Vdd Gnd 5va A Gnd PULSE (0 2.5 100n 2.5n 2.5n 100n 200n)vb B Gnd PULSE (0 2.5 50n 2.5n 2.5n 50n 100n)vc C Gnd PULSE (0 2.5 25n 2.5n 2.5n 25n 50n)vd D Gnd PULSE (0 2.5 12.5n 2.5n 2.5n 12.5n 25n).tran 1n 400n.print tran v(A) v(B) v(C) v(D) v(Out)* Warning: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly1-Poly2 Capacitor ID>* NODE NAME ALIASES* 1 = GND (34.5 , -41.5)* 2 = vdd (32, 15)* 3 = OUT (47.5 , 9)* 4 = D (84 , -6)* 5 = C (70.5 , -5.5)* 6 = B (59.5 , -6)* 7 = A (38 , -5)V1 Vdd Gnd 5va A Gnd PULSE (0 12.5 500n 12.5n 12.5n 5100n 1000n)vb B Gnd PULSE (0 12.5 250n 12.5n 12.5n 250n 500n)vc C Gnd PULSE (0 12.5 125n 12.5n 12.5n 125n 250n)vd D Gnd PULSE (0 12.5 62.5n 12.5n 12.5n 62.5n 125n).tran 1n 1000n.print tran v(D) v(C) v(B) v(A) v(Out)M1 Vdd 4 Out Vdd PMOS L=2u W=16u AD=88p PD=47u AS=60p PS=23.5u $ (44 37 46 53)M2 Out 5 Vdd Vdd PMOS L=2u W=16u AD=60p PD=23.5u AS=56p PS=23u $ (34.5 37 36.5 53)M3 Vdd 6 Out Vdd PMOS L=2u W=16u AD=56p PD=23u AS=112p PS=30u $ (25.5 37 27.5 53)M4 Out 7 Vdd Vdd PMOS L=2u W=16u AD=112p PD=30u AS=88p PS=47u $ (9.5 37 11.5 53)M5 Out 4 Out Gnd NMOS L=2u W=16u AD=120p PD=47u AS=60p PS=23.5u $ (44 0 46 16)M6 Out 5 Out Gnd NMOS L=2u W=16u AD=60p PD=23.5u AS=56p PS=23u $ (34.5 0 36.5 16)M7 Out 6 Out Gnd NMOS L=2u W=16u AD=56p PD=23u AS=112p PS=30u $ (25.5 0 27.516)M8 Out 7 Gnd Gnd NMOS L=2u W=16u AD=112p PD=30u AS=92p PS=47u $ (9.5 0 11.5 16)* Pins of element D1 are shorted:* D1 vdd vdd D_lateral $ (88 18.5 91 26.5)* Pins of element D2 are shorted:* D2 vdd vdd D_lateral $ (36 18.5 39.5 26.5)* Total Nodes: 11* Total Elements: 10* Total Number of Shorted Elements not written to the SPICE file: 0* Output Generation Elapsed Time: 0.001 sec* Total Extract Elapsed Time: 0.746 sec.END(2)提取的网表经过T-spice运行后的文件为:T-Spice - Tanner SPICET-Spice - Tanner SPICEVersion 13.00Standalone hardware lockProduct Release ID: T-Spice Win32 13.00.20080321.01:01:33Copyright ?1993-2008 Tanner EDAOpening output file "C:\Users\Administrator\Desktop\游文浩20113250\youwenhao-NAND4.out"Parsing "C:\Users\Administrator\Desktop\游文浩20113250\youwenhao-NAND4.spc"Initializing parser from header file "C:\Users\Administrator\Desktop\游文浩20113250\header.sp"Including "C:\Users\Administrator\Desktop\ml5_20.md"Loaded MOSLevel2 model library, SPICE Level 2 MOSFET revision 1.0Warning : Pulse period is too small, reset to rt + ft + pw = 5.125e-006Accuracy and Convergence options:numndset|dchold = 100Timestep and Integration options:relq|relchgtol = 0.0005Model Evaluation options:dcap = 2 defnrb = 0 [sq] defnrd = 0 [sq]defnrs = 0 [sq] tnom = 25 [deg C]General options:search = C:\Users\Administrator\Desktop temp = 25 [deg C]threads = 4Output options:acout = 1 ingold = 0Device and node counts:MOSFETs - 8 MOSFET geometries - 8BJTs - 0 JFETs - 0MESFETs - 0 Diodes - 0Capacitors - 0 Resistors - 0Inductors - 0 Mutual inductors - 0Transmission lines - 0 Coupled transmission lines - 0V oltage sources - 5 Current sources - 0VCVS - 0 VCCS - 0CCVS - 0 CCCS - 0V-control switch - 0 I-control switch - 0Macro devices - 0 External C model instances - 0HDL devices - 0Subcircuits - 0 Subcircuit instances - 0Independent nodes - 5 Boundary nodes - 6Total nodes - 11*** 1 WARNING MESSAGE GENERATED DURING SETUPParsing 0.00 secondsSetup 0.01 secondsDC operating point 0.00 secondsTransient Analysis 0.11 secondsOverhead 1.50 seconds-----------------------------------------Total 1.62 secondsSimulation completed with 1 Warning(3)仿真结果为:四作业总结:完成这次作业之后,我对于集成电路版图的绘制有了一个全新的认识,初步掌握了Tunner软件的使用以及T-spice仿真软件的使用。

2021年浙江省一般高校招生选考科目模拟试题(二) 本试题卷分选择题和非选择题共4页,满分50分,考试时间45分钟。

其中加试题为15分,用【加试题】标出。

【XZB2022YLZJXUANTJ002】一、选择题(本大题共13小题,每小题2分,共26分。

每小题列出的四个备选项中只有一个是符合题目要求的,不选、多选、错选均不得分)1.如图所示是一种无线充电器,该设备将电能以无线传输方式传送到用电设备。

该技术设备具有隐形,设备磨损率低,无需导线等优点。

该充电设备型号必需和手机型号配对才能正常使用,并且能量损失大,很难实现大功率远距离传输等,以下说法不正确的是()A.无线充电器使手机无需连接数据线充电,可让用户在充电时不受限制地自由行动,体现出技术具有解放人的作用B.无线充电器型号和手机型号不配对就无法正常使用,体现出技术的两面性C.生产该设备需要考虑材料学、物理等学科,体现技术的综合性D.将原有的充电设备进行了革新,体现出技术的创新性B[本题考查了技术与人的关系以及技术的性质。

解放人一方面指的是技术能解放人类的体力、劳动力,原来由手工完成,现在由机器设备来完成,另一方面指的是技术能延长人类身体器官的功能,A选项正确;技术的两面性是指技术既可以给人们带来福音,也可能给人们带来危害,无线充电器型号和手机型号不配对就无法正常使用,不属于危害,B选项错误;技术的综合性是指从事一项技术活动,这个过程要综合运用多个学科、多方面的学问,C选项正确;技术的创新性包括技术创造和技术革新,D选项正确。

]2.如图所示是一款橡胶底的塑料盆。

水倒入后,橡胶部分向下延展,能有效防止水洒出;能很好地适应各种各样的环境,且制作成本不高,可以替代硬底盆。

关于该产品的设计,以下说法中不恰当的是()A.有效防止了水的洒出,体现了设计的有用原则B.橡胶软底设计,体现了设计的创新原则C.制作成本不高,体现了设计的经济原则D.可以替代硬底盆,体现了设计的可持续进展原则D[本题考查的是设计的一般原则。

1.N 阱 (um)N 阱最小阱宽D1=4N 阱最小间距不同电位(高压与低压)D2=14N 阱最小间距同电位D2=0N 阱内N 阱边界到P +和N +扩散的最小间距D3=4N 阱外N 阱边界到P +扩散的最小间距D4=8N 阱外N 阱边界到N +扩散的最小间距D5=132.有源区扩散的最小宽度(管子的最小宽度)(无孔时)D6=4同型扩散的最小间距D7=4N 阱内N +扩散到P +扩散的最小间距D8=3N 阱外N +扩散到P +扩散的最小间距D9=53.场区注入N 场区版由N 阱版每边扩5得到 D10=4P 场区版取N 场区版的反版4.多晶硅最小多晶硅的宽度D11=3在掺杂区上多晶最小间距D12=3多晶硅盖过场区 extend D13=3场区上的多晶硅到场区的最小间距D14=1栅到场区边缘的最小距离(无引线孔)D15=3D3D6D9P+有源区N 阱N场N+D5D4D7D8D1N+D2D3N 阱D10D15D115.N 管源漏N select overlap N 管源漏包N +扩散区D16=2N 管源漏最小宽度D17=5N 管源漏最小间距 space between n-select D18=2N 管源漏到P +扩散区的最小间距D19=1P 管源漏版由N 管源漏版的反版得到6.引线孔最小接触孔宽D20=3有源区孔到有源区的最小距离D21=2铝包孔D22=2孔间最小间距D23=3孔到多晶的最小间距D24=3多晶包孔D25=2多晶的孔到扩散区间距D26=27.金属最小宽度D27=3最小间距D28=38.钝化孔钝化孔尺寸D29=1002钝化空的间距D30=100金属包钝化孔D31=5n 管源漏n+n+D18D19多晶硅铝D28D27铝D22D21D24D25D26有源区。

一种高电源抑制比的CMOS带隙基准电压源设计【摘要】提出了一种用于温度传感器的高电源抑制比(PSRR)、低温度系数、低功耗的CMOS带隙基准电压源。

在传统CMOS带隙基准电压电路的基础上,增加了优化的电源抑制比增强电路,在带隙基准反馈环路中引入电源噪声,使上面电流镜的栅源电压保持恒定值,从而提高电源抑制比。

采用自偏置共源共栅电流镜,来实现匹配更好的与绝对温度成正比(PTAT)电流镜像。

采用华虹宏力0.13um FS13QPR CMOS工艺实现,使用HSPICE仿真。

仿真结果表明电路输出基准电压为1.2V,电源抑制比在1K Hz时达到90dB,在-40~100℃的温度范围内温度系数是10ppm/℃,在1.8~3.6V工作电压范围内的线调整率为0.5mV/V,工作电流43uA。

【关键词】带隙基准电压;电源抑制比;自偏置共源共栅电流镜;温度传感器引言带隙基准电压源(Bandgap V oltage Reference)具有与温度、电源电压和工艺变化几乎无关的突出优点,能够提供稳定的参考电压或参考电流,被广泛应用与集成温度传感器、比较器、A/D和D/A转换器、存储器以及其他模数混合系统集成芯片中,并且高性能基准电压源直接影响着电路的性能。

研究用CMOS 工艺实现的可集成于片上系统(SOC)的高精度带隙基准源显得尤为重要[1]。

对于高精度的温度传感器,从电源注入到带隙基准输出的噪声是各种噪声中最重要的噪声,会严重影响参考电压和温度传感器的与绝对温度成正比(PTAT)电压。

因此,设计高电源抑制比(PSRR)的带隙基准源满足其要求显得十分必要[2]。

本文先介绍了带隙基准源的基本原理,再基于等效小信号模型,对带隙基准源的电源抑制比做了详细的分析,进而提出了一个具有高电源抑制比、低温度系数、低功耗可用于温度传感器的带隙基准电压源。

1.带隙基准源电源抑制比分析利用与CMOS兼容工艺的纵向PNP晶体管和采用放大器负反馈实现的传统CMOS带隙基准电压如图1所示。

四输入或非门课程设计学生姓名:专业班级:指导教师:工作单位:题目: 四输入或非门的设计初始条件:计算机、ORCAD软件,L-EDIT软件要求完成的主要任务:(包括集成电路专项实践工作量及其技术要求,以及说明书撰写等具体要求)1、集成电路专项实践工作量:1周2、技术要求:(1)学习ORCAD软件,L-EDIT软件。

(2)设计一个四输入或非门电路。

(3)利用ORCAD软件,L-EDIT软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。

3、查阅至少5篇参考文献。

按《武汉理工大学课程设计工作规范》要求撰写设计报告书。

全文用A4纸打印,图纸应符合绘图规范。

时间安排:2015.6.19布置集成电路专项实践任务、选题;讲解集成电路专项实践具体实施计划与课程设计报告格式的要求;集成电路专项实践答疑事项。

2015.6.19-6.20学习ORCAD软件,L-EDIT软件,查阅相关资料,复习所设计内容的基本理论知识。

2015.6.21-6.25用ORCAD软件设计四输入或非门电路并进行仿真工作,再利用L-EDIT软件绘制其版图,完成集成电路专项实践报告的撰写。

2015.6.26 提交集成电路专项实践报告,进行答辩。

指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要 .............................................................................................................................................. Abstract . (I)1 绪论 02 四输入或非门 (1)2.1 四输入或非门的电路结构 (1)2.2 四输入或非门的电路设计与仿真 (2)2.2.1 ORCAD软件介绍 (2)2.2.2 绘制电路图 (2)2.2.3 电路仿真 (3)2.4 四输入或非门的版图绘制 (5)2.4.1 L-EDIT软件介绍 (5)2.4.2 版图绘制 (5)3 总结 (9)参考文献 (10)摘要性能优越的四输入或非门是数字电路中很常见的一种逻辑电路,可广泛应用于算术逻辑单元等电路中。

全国大学生电子设计大赛题目1. 《AVR高速嵌入式单片机原理与应用》2. 《数字电路元件》3. 《数字电子技术》电子教案4. 《通用集成电路速查手册》5. 51单片机+程序+书籍+教案+应用设计6. 400HZ中频电源7. 555集成电路应用800例8. 2003电子设计大赛智能车9. 2008年求是杯智能寻线小车10. AVR单片机+程序+书籍+教案+应用设计11. AVR可用程序12. cd4094串口扫描13. CMOS 4000系列60钟常用集成电路的应用14. CPLD15. danpianjichengxu16. DS18B20控制风扇转速17. ds1302时钟芯片应用万年历18. isd256019. L298N驱动步进电机资料20. nRF2401 无线传输模块21. pc智能家电控制盒22. PDF格式23. PLL电路的研究及在信号产生中的应用24. S52可用程序25. usb下载线制作26. 八位数字密码锁27. 比较全面的手机原理资料28. 毕业论文格式29. 便捷式单片机实验开发装置30. 变压器的智能绕线功能系统31. 步进电机32. 步进电机调试33. 步进电机控制调速器34. 蚕种催青自动化测控系统电脑终端35. 超级点阵,上位机发送任意汉字到单片机显示资料36. 超声波测距原理图37. 成品设计资料38. 出租车计价器39. 触模屏ocmj8x15b40. 串行通信41. 串行通信的电子密码锁42. 单工无线发射接收系统43. 单片机红外遥控系统设计44. 单片机软件45. 单片机实训46. 单片开关电源的设计与应用47. 导游助理机48. 倒车雷达49. 灯光控制集成电路与灯光控制器制作50. 第三届全国大学生“飞思卡尔”杯智能汽车51. 点阵52. 电子拔河53. 电子单片机教案54. 电子设计55. 电子万年历设计56. 电子万年历设计与制作57. 多功能电机控制器58. 风扇调速59. 高频电路实训装置60. 光纤通信复用技术的研究61. 合泰杯资料62. 红外遥控电路设计63. 华苑杯200864. 基于AT89S52单片机和DS1302的电子万年历设计65. 基于CPLD的三相多波形函数发生器66. 基于IGBT的变频电源设计67. 基于PLL信号发生器的设计68. 基于两个单片机串行通信的电子密码锁69. 交通灯控制系统70. 交通控制器设计71. 经典之经典单片机设计72. 开关电源73. 开关电源的设计与应用74. 开关稳压电源75. 开关稳压电源——原理、设计与实用电路76. 凌阳单片机资料77. 密码锁78. 频率和占空比同时可调电路79. 七悬迪厅灯80. 汽车尾灯控制电路设计81. 实用电子电路大全82. 实用家用电器功能扩展器制作83. 使用电子线路集84. 数控频率计85. 数控直流电流源86. 数字抢答器87. 数字示波器的制作88. 数字温度计89. 数字应用电路90. 通信电源新技术与新设备丛书通信用高频开关电源91. 图书馆资料92. 万年历93. 危险气体泄露报警器设计94. 微型打印机控制电路的设计95. 温度测量96. 温湿显示系统97. 无线电制作精汇98. 无线调频发射器的设计99. 无线视频监控系统设计100. 无线数据收发系统101. 无线遥控设计102. 下载线103. 项目-360度天线显示104. 项目-360度天线显示带36指示灯105. 芯片资料106. 新型电源107. 新型开关电源实用技术108. 新颖开关稳压电源109. 新颖实用电子设计与制作110. 寻线机器人系统设计实例111. 遥控系统的设计112. 液晶资料113. 智能风扇调速系统114. 智能家电控制盒115. 智能键盘无线遥控电路116. 智能温度报警系统117. 自动加料控制系统118. 《不怕掉电的超级万年历》源程序及文件资料119. 《高频电子线路》实验指导书120. 《汽车底盘电子技术》实验指导书121. 《数字电子技术》实验指导书122. 《无线电通信技术》期刊参考文献著录格式123. 1.5V调频无线话筒电路制作124. 1.8 GHz CMOS 有源负载低噪声放大器125. 1.8V 5.2 GHz 差分结构CMOS 低噪声放大器126. 2A、2MHz同步降压/升压型DC/DC转换器127. 6位数显频率计数器 .rtf128. 16×16点阵(滚动显示)资料129. 30kHz高频开关电源变压器的设计130. 40kHZ_超声波测距131. 44b0开发板原理图和PCB图132. 48V50A开关电源整流模块主电路设计133. 51单片机C语言编程实验134. 51控制硬盘135. 400HZ中频电源设计资料136. 430通用型变频器137. 3208LED点阵屏电子钟制作全资料资料138. 8051单片机自动控制交通灯及时间显示的方139. 12232液晶显示程序140. 12864-12 LCD模块与射频SoC nRF9E5的串行接口设计141. 145152频率合成器及其应用142. AD0809在数据采集中的应用143. AT89C51编程密码控制器144. AT89C51单片机温度控制系统145. AT89C51单片机在无线数据传输中的应用146. A题直流稳定电源147. c8051f020中文版148. C8051FXXX单片机FLASH程序的自动升级149. CDMA通信系统中的接入信道部分进行仿真与分析资料150. CMOS 混频器的设计技术151. CMOS 斩波稳定放大器的分析与研究152. DDS-PLL组合跳频频率合成器153. DDS波形合成技术中低通椭圆滤波器的设计154. DownPaper155. EDA技术及其应用156. EDA技术及其应用设计资料157. Flash单片机实验课件的制作158. FM调制器(三知杯)159. GPS高精度的时钟的设计和实现160. I2C总线数字式温湿度传感器SHT11及其在单片机系统的应用161. ISD2560芯片在汽车报站器的应用162. ISD2560语音芯片在排队机系统中的应用163. JDM PIC编程器的原理与制作164. KD-2000型LED智能显示系统165. Keil C51中文教程166. LC振荡器制作方案167. led大屏幕点阵资料168. LED显示屏动态显示和远程监控的实现资料169. MC1648两种改进型VCO的压控170. MC1648两种基本型VCO的压控特性171. MC34262系列PFC控制芯片的应用研究172. MC145151173. MC145163P型锁相频率合成器的原理与应用174. MCGS数据采集单片机数据传送175. MCGS数据采集单片机数据传送设计资料176. MCS51单片机应用系统设计177. MCS-51单片机温度控制系统178. MCS-51单片机温度控制系统的设计179. MSP430超声波测距180. MSP430和nRF905的无线数传系统设计181. nRF905的无线数据传输系统1182. nRF905的无线数据传输系统183. N阶多环反馈低通滤波器的系统设计184. PDP 中的模拟视频数字化电路设计185. pid调节规律和过程控制186. PLC控制电梯制作资料187. PWM开关调整器及其应用电路188. RCC电路间歇振荡的研究189. RCC电路间歇振荡现象的研究190. RCD箝位反激变换器的设计与实现191. RFID产品几个技术问题的说明192. RFID傻瓜书193. S51下载线的制作——单片机实用技术探讨194. SL-DIY02-3:单片机创新开发与机器人制作的核心控制板195. SPCE061A在电冰箱中应用196. SPI总线在51系列单片机系统中的实现197. TDA2822M198. TEA1504开关电源低功耗控制IC199. terex工程车1200. TL494脉宽调制控制电路201. TX-1B单片机实验板使用手册-good202. UC3842N组成的开关电源203. UC3842典型应用电路204. UC3842应用于电压反馈电路中的探讨205. UC3843 是高性能固定频率电流模式控制器专为离线和直流变换206. UC3843A的内部等效电路框图207. UC3843控制多路输出开关电源设计与实现208. UC3844组成的开关电源209. UCC3895全桥控制集成电路开关电源210. US_FL_IOM_001_0803211. USB接口设计212. U盘制作资料(原理图、文档、底层驱动源程序)213. VHDL基本语法单元214. XC6371系列直流变换电路215. 按照实验指导书的要求216. 八路红外遥控开关的设计资料217. 八路抢答器218. 半导体三极管测量设计219. 编码器与译码器.ppt220. 别墅区可视对讲系统221. 波形发生器(A题)222. 步进电机223. 步进电机的单片机控制224. 步行者机器人225. 采集与发射系统设计226. 采用CoolSET-ICE2B265的30瓦开关电源设计227. 采用MEC002A制作远程调频发射机228. 采用PROG-110制作的打铃器电路229. 餐厅无线呼叫系统设计230. 仓库温湿度的监测系统231. 测力传感器设计的应力集中原则232. 常导超导磁悬浮演示试验装置的控制233. 常见放大电路集锦234. 常见监控视频干扰分析235. 常见监控视频干扰分析236. 超级点阵,上位机发送任意汉字到单片机显示资料237. 超声波测距238. 超声波在超声波测距中的应用239. 出租车多功能计费器的设计240. 出租车计费器设计与实现241. 出租车计价器242. 出租车计价器243. 出租车计价器程序244. 出租车计价器论文245. 串行接口键盘控制器SK5278及其在单片机系统中的应用246. 大功率开关电源中功率MOSFET的驱动技术247. 单电源运放图解资料手册248. 单端反激开关电源变压器设计249. 单工无线发射接收系统设计资料250. 单工无线呼叫系统1251. 单工无线呼叫系统252. 单工无线呼叫系统-good253. 单片机C语言编程与实例254. 单片机超声波测距仪255. 单片机串行通信发射机256. 单片机大屏幕温湿度测控电路257. 单片机定时闹钟258. 单片机构成的精确测距系统259. 单片机和图形液晶显示器接口应用技术260. 单片机交通灯.txt261. 单片机课程设计__电子密码锁报告262. 单片机控制的吊扇多功能控制器263. 单片机控制固态继电器SSR的264. 单片机控制红外线防盗报警器265. 单片机控制机械手臂的设计与制作266. 单片机控制交通灯267. 单片机控制语音芯片的录放音系统的设计268. 单片机内存资源冲突的问题269. 单片机上网计时器270. 单片机实训271. 单片机实验板使用与C语言源程序272. 单片机实验指导书273. 单片机是怎样在液晶上显示字符的274. 单片机数字时钟275. 单片机数字时钟资料276. 单片机温度控制系统在电阻炉中的应用277. 单片机温度控制应用设计—温室电炉控制278. 单片机学习机及编程器的设计与制作279. 单片机应用技术选280. 单片机应用系统设计技术教学大纲281. 单片机应用中的几种软件抗干扰方1 282. 单片机应用中的几种软件抗干扰方法283. 单片机游戏设计284. 单片机与软盘驱动器的接口285. 单片机语言C51应用实战集锦286. 单片机原理与应用287. 单片机在超声波测距中的应用288. 单片机在家用电器中的应用289. 单片机在炉温控制中的应用290. 单片机制作的新型安全密码锁291. 单片机综合开关保护器292. 单片及的综合技术应用-good293. 单片开关电源的快速设计法294. 单片微机控制的全自动交流稳压电源295. 单相Boost功率因数校正电路优化及仿真296. 单相相位触发器TC782A的设计及应用297. 单向无线数据传输系统的设计298. 单周期控制BoostDC/DC变换器分析与设计299. 低成本DC-DC转换器34063的应用300. 低功耗10Gbs CMOS 1∶ 4 分接器301. 第八届“挑战杯”全部文件302. 点阵电子显示屏制作资料303. 点阵电子显示屏资料304. 电磁波实验指导书305. 电动智能小车资料306. 电力电子实验指导书2007307. 电容降压电源原理和计算公式308. 电容阵列开关时序优化在A D 转换器中的应用309. 电视监控及其发展310. 电视节目“多维组合”分类法及其编码设计311. 电视音乐的结构特殊性详细内容312. 电信运营商收入保障系统设计与实现资料313. 电压控制 LC 振荡器314. 电压控制 LC 振荡器(A 题)315. 电压控制振荡器(2004 年吉林省大学生电子设计竞赛) 316. 电源的分类及知识317. 电源技术与电子变压器318. 电源输入端口的电磁兼容设计319. 电子车速里程表的单片机实现方案320. 电子密码锁321. 电子闹钟322. 电子琴323. 电子设计大赛点阵电子显示屏资料324. 电子时钟资料325. 电子实验指导丛书326. 电子式多功能电能表的设计与实现327. 电子式里程表328. 电子万年历设计329. 电子万年历设计设计资料330. 电子万年历设计与制作设计资料331. 电子线路课程设计题332. 电子学习资料[适合初学者]333. 电子语音导游机334. 电阻电容在线测试及LCD显示335. 调幅发射机电路的设计336. 调频收音机设计337. 调频无线话筒接收机电路338. 对“C51语言应用编程的若干问题”339. 对电子设备防雷击有关问题的看法340. 多参数可调扩频信号源的设计341. 多功能数字时钟2004342. 多功能数字时钟2004资料343. 多功能数字时钟毕业设计344. 多功能数字时钟毕业设计资料345. 多功能数字钟设计346. 多功能数字钟设计.rtf347. 多路读写的SDRAM接口设计348. 多路无线呼叫数显系统349. 多媒体教室综合控制器350. 多相位低相位噪声5GHz 压控振荡器的设计351. 发射三极管352. 反激式DC—DC电源的集成化研究353. 反激式电源中电磁干扰及其抑制354. 房间电器综合控制系统设计资料355. 非对称纯后级功率放大器的电路设计356. 肺活量测量仪357. 改进的并行积分算法低通滤波器的FPGA设计358. 改善8051系统用电效率的微控制器359. 高保真音响设计制作360. 高精度正弦全自动激励信号源的设计与实现361. 高灵敏无线探听器电路362. 高频电路实训装置设计资料363. 高频电子线路实验364. 高频电子线路实验指导书(初稿)365. 高频电子线路实验指导书366. 高频高效DC-DC模块电源367. 高频开关电源368. 高频试验箱369. 高清电视音频解码的定点DS P 实现370. 高线性度上变频混频器设计371. 高压开关电源的应用电路设计372. 个人总结373. 个人总结的89s52单片机的c语言程序374. 给初学单片机的40个实验375. 关于单端反激变换器的变压器设计376. 光纤通信复用技术的研究设计资料377. 焊后热处理温控装置378. 红外电路379. 红外遥控电风扇控制系统设计380. 红外遥控电路设计设计资料381. 火灾自动报警系统的发展及案例382. 火灾自动报警系统设计383. 获奖作品FM调制器384. 基才酒店无线呼叫系统设计385. 基于16位单片机的语音电子门锁系统386. 基于51单片机的3线双向零等待IO通讯机制387. 基于51单片机的CRC16校验的程序388. 基于89C51的计算机可锁定加密键盘设计389. 基于8051单片机制作多光束激光围栏390. 基于8051的CF卡文件系统的实现391. 基于8051的KVM系统设计392. 基于145152-2芯片的频率合成器的设计393. 基于AT89C51SND1C单片机的MP3硬件播放器的实现394. 基于AT89C205 1和ISD2560的录放音系统设计395. 基于AT89S51的液位控制系统396. 基于AT89S52单片机和DS1302的电子万年历设计设计资料(低价...397. 基于AVR及无线收?⒛?榈穆霾嗖庀低成杓?398. 基于CPLD/FPGA的出租车计费399. 基于CPLD/FPGA的出租车计费器400. 基于CPLD的三相多波形函数发生器设计资料401. 基于CPLD和接触式图像传感器的图像采集系统402. 基于CPLD控制的DDS数字频率合成器设计403. 基于DDS的雷达中频信号源设计与实现404. 基于DDS的信号源405. 基于D类功放的宽范围可调开关电源的设计406. 基于FPGA的四阶IIR数字滤波器407. 基于FPGA的小功率立体声发射机的设计408. 基于FPGA多通道采样系统设计409. 基于FT245BM的简易USB接口开发410. 基于GPS的高精度无误差倒计时牌的设计411. 基于GSM短信模块的家庭防盗报警系统412. 基于GSM模块的车载防盗系统设计资料413. 基于IGBT的变频电源设计设计资料414. 基于MSP430和nRF905的多点无线通讯模块415. 基于nRF9E5的无线光标控制系统416. 基于nRF905的无线数据多点跳传通信系统417. 基于nRF905射频收发模块的设计418. 基于nRF905芯片的无线传输设计与实现419. 基于nRF905芯片的无线呼号系统设计与实现1 420. 基于nRF905芯片的无线呼号系统设计与实现421. 基于nRF2401的无线数据传输系统422. 基于PLC的锅炉内胆水温控制系统设计423. 基于PLL信号发生器的设计424. 基于PLL信号发生器的设计制作资料425. 基于PSTN的家用电器远程控制系统426. 基于UC3843的反激式开关电源反馈电路的设计427. 基于USB的经络信号的检测系统与设计428. 基于USB接口的温度控制器429. 基于VHDL语言的出租车计费系统设计430. 基于μPD78F0034单片机的出租车计费器的设计与实现431. 基于大容量IC卡AT45D041的出租车数据采集系统432. 基于单片机AT89C51的节拍器的设计与制作433. 基于单片机的超声波测距系统434. 基于单片机的电集中抄表435. 基于单片机的红外通讯设计436. 基于单片机的迷你型软磁盘读写装置设437. 基于单片机的喷墨打印机控制技术438. 基于单片机的频率计设计439. 基于单片机的数字电子钟的设计与制作440. 基于单片机的数字频率计设计与制作441. 基于单片机的数字式电子钟的设计与制作442. 基于单片机的数字钟设计443. 基于单片机的水温控制系统资料444. 基于单片机控制的开关电源445. 基于电流控制传送器的电可调梯形滤波器446. 基于电位计实现自行车机器人的拟人智能控制447. 基于汇编语言的数字时钟448. 基于阶梯阻抗发夹谐振器的小型低通滤波器449. 基于两个单片机串行通信的电子密码锁制作资料450. 基于软件无线电的多制式信号发生器的设计与实现451. 基于射频收发芯片nRF903的无线数传模块设计452. 基于锁相频率合成器的电压控制LC振荡器453. 基于网络的虚拟仪器测试系统a) 基于无线传输技术的多路温度数据采集系统设计b) 基于小波变换的谐波检测法454. 基于准浮栅技术的超低压运放及滤波器设计455. 集群通信技术在GPS车辆监控系统中的应用456. 计算机控制灯阵列457. 计算机组装与维护.ppt458. 家用音响设计、制作459. 简单实用的通用单片机控制板460. 简易数字电压表的设计.rtf461. 降压/升压DC—DC转换器四开关控制方法462. 交通灯系统设计463. 交通控制器设计制作资料464. 揭开电视图像的“神话”面纱-图像意义生成过程演示465. 解析几种有效的开关电源电磁干扰的抑制措施466. 开关电源(SMPS)的发展趋势467. 开关电源EMC设计468. 开关电源保护电路的研究469. 开关电源测试参考470. 开关电源冲击电流控制471. 开关电源的干扰及其抑制472. 开关电源的设计与应用473. 开关电源的制作及学习474. 开关电源电感器的选用475. 开关电源高频变压器设计——正激式476. 开关电源论文477. 开关电源论文最终478. 开关电源原理及各功能电路详解479. 开关电源原理及其应用480. 开关电源原理与维修481. 开关式稳压电源的工作原理482. 开关稳压电源的设计483. 抗干扰能力强的反射式传感器484. 可提高Buck型DC/DC转换器带载能力的斜坡补偿设计485. 课程设数字?氡淼纳杓?486. 空调室温控制的质量与节能487. 宽频带数控频率合成器488. 宽频鱼雷自导目标回波模拟仿真489. 款基于单片机技术的电子抢答器490. 扩频通信491. 来水厂全自动恒压供水监控系统492. 利用AT89C2051单片机与DS18B20和两个数码管显示温度493. 利用MC145152-2设计吞脉冲锁相频率合成器494. 利用TL431作大功率可调稳压电源495. 利用计算机设计单片开关电源讲座(1)496. 利用计算机设计单片开关电源讲座(2)497. 利用计算机设计单片开关电源讲座(3)498. 利用计算机设计单片开关电源讲座(4) 499. 利用计算机设计单片开关电源讲座(5) 500. 利用计算机设计单片开关电源讲座(6) 501. 利用计算机设计单片开关电源讲座(7) 502. 利用计算机设计单片开关电源讲座(7) 503. 利用计算机设计单片开关电源讲座(8) 504. 利用位置式PID控制算法实现对恒温箱的控制505. 两种调制506. 楼宇智能化系统的过程控制507. 论文—多点无线数据传输系统508. 论文—多点无线数据传输系统资料509. 论文-功率放大器510. 脉冲无线电技术511. 密码小键盘512. 模糊免疫PID在主汽温控制系统中的应用513. 牧场智能挤奶与综合信息管理系统514. 频率计0-100.txt515. 频率计516. 频率计.txt517. 频率记518. 汽车尾灯设计519. 汽车ESP用传感器及其接口技术520. 汽车尾灯控制电路设计设计资料521. 汽车智能MP3无线发射器的设计522. 浅谈开关电源的过流保护电路523. 浅谈智能大厦保安监控系统524. 嵌入式POL DC/DC转换器设计525. 全遥控数字音量控制的D 类功率放大器526. 如何使用4N27光耦合器来设计开关调整器527. 设计论文全部资料528. 射频SoC nRF9E5及无线数据传输系统的实现529. 射频模块nRF9E5在污水数据监测系统中的应用530. 深井泵自动控制器531. 实验指导书532. 实用电子技术系列讲座第三讲功率放大电路的设计与制作533. 实用电子技术系列讲座——第七讲数字电子技术基础知识534. 使用315MHz收发模块制作的遥控插座535. 使用PWM得到精密的输出电压536. 使用315MHz收发模块制作的遥控插座537. 使用PWM得到精密的输出电压538. 使用SN8P1702A的低成本上下限通用数字表头539. 使用单片机制作的毫欧表540. 手把手教你学单片机的C语言程序设计(十六)541. 手把手教你学单片机的C语言程序设计(十七)542. 鼠标:罗技V450激光无线鼠标543. 数控直流电流源资料544. 数控直流电源545. 数控直流稳压电源完整论文资料546. 数码管动态扫描示例程序.txt547. 数显实验电源的制作548. 数字电视技术549. 数字电子技术基础实验指导书550. 数字电子实验指导书551. 数字化会议系统的分析与设计552. 数字化舞台布光灯具控制器的设计553. 数字滤波器参数的设计554. 数字密码锁设计资料555. 数字抢答器(数字电路)资料556. 数字示波器的制作557. 数字式秒表文档资料558. 数字锁相环的设计559. 数字温度计论文560. 数字温度计论文资料561. 数字显示“L、C”表的制作电路562. 数字钟课程设计报告资料563. 水库564. 水箱单片机控制系统资料565. 四通道温度-脉宽转换器MAX6691566. 谈开关电源的指标及检测567. 通恒电子-开关电源的电路设计568. 通信电源现状分析569. 通信原理实验指导书570. 同步电机模型的MATLAB仿真资料571. 同步整流DC/DC升压芯片中驱动电路的设计572. 椭圆滤波器边带优化设计方法研究573. 危险气体泄露报警器设计资料574. 微机接口技术实验指导书575. 微机原理及应用实验指导书576. 微型打印机控制电路的设计资料577. 未来电视台摄录设备分析578. 温度579. 温度监控系统的设计资料580. 温度控制系统资料581. 温度控制虚拟对象的设计及其组态王控制582. ?业穆畚纳杓频缱用苈胨?583. 无线调频发射器的设计资料584. 无线呼叫器585. 无线呼叫系统的设计586. 无线你我他——认识红外线接口587. 无线射频识别系统无线射频识别系统588. 无线识别装置589. 无线视频监控系统设计资料590. 无线收发芯片nRF905的原理及其在单片机系统中的应用591. 无线数传模块及其应用592. 无线数据传输系统的设计与实现593. 无线数据收发系统资料594. 无线遥控设计595. 无线遥控设计设计资料596. 无线语音遥控智能车597. 无线语音遥控智能车资料598. 无线智能报警器的设计599. 五种PWM反馈控制模式研究600. 吸尘器设计资料601. 下载电缆串行编程 AT89S5X ISP602. 下载线+接口电路——制作实用的单片机编程器603. 显示测试系统数字I O 口控制的设计与实现604. 小崔风火轮简易版,开源全部资料!605. 小型机载计算机电源的设计与研究606. 小型机载计算机电源的设计与研究607. 小型机载计算机电源的设计与研究资料608. 新潮电风扇专用集成电路应用大观_609. 新建 Microsoft Word 文档610. 新建文本文档.txt611. 新型彩色LCOS 头盔微显示器光学系统612. 新型单片机开关电源的设计与应用613. 新型单片开关电源的设计614. 新型集成电路简化嵌入式POL DC/DC转换器设计615. 新型开放式液滴驱动芯片616. 新型开关芯片TOP224P在开关电源中的应用617. 新型温控仪的研制618. 新一代单片PFC+PWM控制器619. 信号与系统实验系统620. 悬挂运动控制系统资料621. 遥控系统的设计资料622. 也谈单片机掉电数据623. 也谈用单片机控制624. 液体点滴速度监控装置625. 液体点滴速度监控装置资料626. 一款新颖的插座式自动温控器627. 一些经典的滤波电路.ppt628. 一种低功耗的锂离子电池保护电路的设计629. 一种点对多点无线数据传输系统的设计630. 一种电池供电的单片机电源电路631. 一种基于AT89C51的433MHz无线呼叫系统的设计632. 一种基于nRF9E5的无线监测局域网系统的设计633. 一种简单有效的限流保护电路634. 一种精准的升压型DC—DC转换器自调节斜坡补偿电路635. 一种输出电压4~16V开关稳压电源的设计636. 一种无线多点远程监控系统的设计与实现637. 一种无线数据传输方案及实现638. 一种小型化高压小功率电源639. 一种新的适于集成的模拟温度补偿晶体振荡器的设计640. 一种新颖的消除DC-DC中斜坡补偿影响的电路结构641. 一种用单片机制作的高频正弦波逆变器642. 一种用方波驱动鼠标光标移动的鼠标电路的设计643. 一种用于单片机的红外串行通信接口644. 一种直接采用计算机串行口控制步进电机的新方法645. 音乐播放器。

模拟CMOS集成电路设计课程设计报告--------二级运算放大器的设计信息科学技术学院电子与科学技术系一、概述:运算放大器是一个能将两个输入电压之差放大并输出的集成电路。

运算放大器是模拟电子技术中最常见的电路,在某种程度上,可以把它看成一个类似于BJT 或FET 的电子器件。

它是许多模拟系统和混合信号系统中的重要组成部分。

它的主要参数包括:开环增益、单位增益带宽、相位阈度、输入阻抗、输入偏流、失调电压、漂移、噪声、输入共模与差模范围、输出驱动能力、建立时间与压摆率、CMRR、PSRR以及功耗等。

二、设计任务:设计一个二级运算放大器,使其满足下列设计指标:工艺Smic40nm电源电压 1.1v负载100fF电容增益20dB 至少40dB3dB带宽20MHz输入小信号幅度5uV 共模电平自己选取输出共模电平自己选取电路结构两级放大器相位裕度60~70度功耗无要求三、电路分析:1.电路结构:最基本的二级运算放大器如下图所示,主要包括四部分:第一级放大电路、第二级放大电路、偏置电路和相位补偿电路。

2.电路描述:输入级放大电路由PM2、PM0、PM1和NM0、NM1组成。

PM0和PM1构成差分输入对,使用差分对可以有效地抑制共模信号干扰;NM0和NM1构成电流镜作为有源负载;PM2作为恒流源为放大器第一级提供恒定的偏置电流。

第二级放大电路由NM2和PM3构成。

NM2为共源放大器;PM3为恒流源作负载。

相位补偿电路由电阻R0和电容C0构成,跨接在第二级输入输出之间,构成RC米勒补偿。

此外从电流电压转换角度来看,PM0和PM1为第一级差分跨导级,将差分输入电压转换为差分电流。

NM0和NM1为第一级负载,将差模电流恢复为差模电压。

NM2为第二级跨导级,将差分电压信号转换为电流,而PM3再次将电流信号转换成电压信号输出。

偏置电压由V0和V2给出。

3.静态特性对第一级放大电路:构成差分对的PM0和PM1完全对称,故有G m1=g mp0=g mp1 (1)第一级输出电阻R out1=r op1||r on1 (2)则第一级电压增益A1=G m1Rout1=g mp0,1(r op1||r on1) (3) 对第二级放大电路:电压增益A2=G m2R out2= -g mn2(r on2||r op3) (4) 故总的直流开环电压增益A0=A1A2= -g mp0,1g mn2(r op1||r on1)(r on2||r op3) (5)由于所有的管子都工作在饱和区,所以对于gm 我们可以用公式 g m =D I L W )/(Cox 2μ (6) 进行计算;而电阻r o 可由下式计算 r o =DI 1λ (7)其中λ为沟道长度调制系数且λ∝1/L 。

vf D Gnd PULSE (0 5 15n 2n 2n 25n 50n).tran 1n 400n.print tran v(ctrl1) v(ctrl2) v(A) v(B) v(C) v(D) v(F)* Main circuit: Module0M1 C N1 N5 Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM2 N1 ctrl1 Gnd Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u M3 N18 ctrl2 Gnd Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u M4 A ctrl1 N5 Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM5 B ctrl1 N2 Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM6 D N1 N2 Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM7 N5 ctrl2 F Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM8 N2 N18 F Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM9 C ctrl1 N5 Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM10 A N1 N5 Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM11 N1 ctrl1 Vdd Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u M12 N18 ctrl2 Vdd Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u M13 B N1 N2 Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM14 D ctrl1 N2 Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM15 N5 N18 F Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM16 N2 ctrl2 F Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u* End of main circuit: Module0电路图瞬时分析波形图:版图设计:内容(方法、步骤、要求或考核标准及所需工具、设备等)一、实训设备与工具1.PVI计算机一台;2.Tanner Pro集成电路设计软件二、项目总体要求采用全CMOS线路结构,实现如下电路功能:对应选择信号的四种组合,将输入数据信号一一传送到输出端。