一种宽带复接器的设计与实现.

- 格式:docx

- 大小:11.62 KB

- 文档页数:3

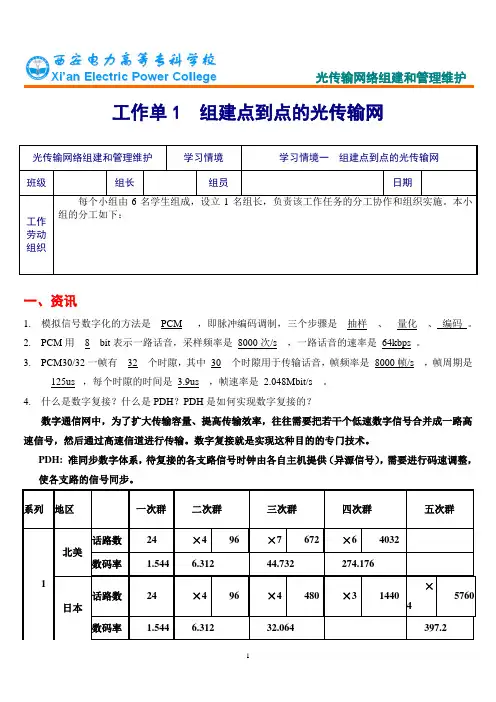

工作单1 组建点到点的光传输网一、资讯1. 模拟信号数字化的方法是__PCM___,即脉冲编码调制,三个步骤是__抽样__、__量化__、_编码 。

2. PCM 用__8__bit 表示一路话音,采样频率是_8000次/s__,一路话音的速率是_64kbps_。

3. PCM30/32一帧有__32__个时隙,其中_30__个时隙用于传输话音,帧频率是_8000帧/s__,帧周期是__125us _,每个时隙的时间是_3.9us__,帧速率是_2.048Mbit/s__。

4. 什么是数字复接?什么是PDH ?PDH 是如何实现数字复接的?数字通信网中,为了扩大传输容量、提高传输效率,往往需要把若干个低速数字信号合并成一路高速信号,然后通过高速信道进行传输。

数字复接就是实现这种目的的专门技术。

PDH: 准同步数字体系,待复接的各支路信号时钟由各自主机提供(异源信号),需要进行码速调整,使各支路的信号同步。

光传输网络组建和管理维护5.PDH有何缺点?(1)接口方面----与设备互联有关电接口方面:PDH具有多种电接口规范,有欧洲系列、北美系列和日本系列标准,我国采用的是欧洲系列标准。

由于不存在世界性标准,因此无法实现多厂家互连互通。

光接口方面:和电接口一样,PDH在光接口方面也没有世界性标准的光接口规范。

各厂家在进行线路编码时,为完成不同的线路监控功能,在信息码后加上不同的冗余码,导致不同厂家同一速率等级的光接口码型和速率也不一样,无法实现多厂家互连互通。

这样在同一传输路线两端必须采用同一厂家的设备,给组网、管理及网络互联带来困难。

(2)复用方式PDH采用异步复用方式通过码速调整(塞入bit)匹配和容纳信号时钟的偏差低速信号在高速信号中的位置无规律性从高速信号插/分低速信号要一级一级进行复用/解复用增加了信号的损伤,不利于大容量传输(3)运行维护方面(OAM)——决定设备维护成本PDH信号的帧结构中用于运行维护工作OAM的开销字节不多,要通过增加冗余码来完成线路性能监控功能。

第一章习题一、填空题。

1、模拟信号在幅度上是随时间连续的的。

2、数字信号在时间上是离散的,在幅度上是离散的。

3、信号是信息的物理载体。

4、世界电信日是每年的 5月17。

5、产生信息的人或机器叫信源。

6、接收信息的人或机器叫信宿。

7、三网融合包括计算机网、电信网和有线电视网。

8、通信按收信者是否运动分为移动通信和固定通信。

9、通信按传输媒质分为有线通信和无线通信。

10、电信业务分为基础电信业务和增值电信业务。

二、选择题1.世界电信日是每年的(C )A、5月20日B、5月30日C、5月17日D、6月17日2.电话通信技术是在哪一年产生的(C)A、1906B、1896C、1876D、18373.ITU的中文含义是(B)A、国际电报联盟B、国际电信联盟C、国际数据联盟D、国际电话联盟4.发明电话的人是(A )A、贝尔B、莫尔斯C、奈奎斯特D、高锟5.莫尔斯电报是在哪一年产生的(D)A、1906B、1896C、1876D、18376.IP电话属于(A )A、第一类基础电信业务B、第二类基础电信业务C、第一类增值电信业务D、第二类增值电信业务7.8比特可表示的信息数为(D)A、8B、32C、64D、2568.在电话网中传输的话音信号的频率范围是(C)A、100~3400HzB、100~4000HzC、300~3400HzD、300~4000Hz9.时间上离散的,幅值上连续的信号是(B)A、数字信号B、模拟信号C、数据信号D、声音信号10.一路模拟电话占用的带宽是(D )A、0.3kHzB、3.1kHzC、3.4kHzD、4kHz三、多项选择题1.模拟通信系统的特点(ABDE)A、存在噪声积累B、近距离传输C、对信号加密,安全性强D、抗干扰能力弱E、占用带宽少2.按照功能划分,通信网可以分为(ABCD )A、业务网B、信令网C、管理网D、同步网E、电话网3.简单的通信系统组成包括(ABCDE )A、信源B、接收设备C、发送设备D、信宿E、信道4.电信支撑网包括(BCD )A、业务网B、信令网C、管理网D、同步网E、电话网5.数字通信系统的特点(BCDE )A、存在噪声积累B、远距离传输C、对信号加密,安全性强D、统一编码E、低成本,集成化6.按照业务划分,通信网可以分为(ACE )A、广播电视网B、信令网C、数据通信网D、同步网E、电话网7.三网融合包括(ABC )A、电信网B、有线电视网C、计算机网D、数据网E、电话网8.信息的表现形式有(ABCE )A、数据B、文本C、图像D、数字E、声音四、判断题。

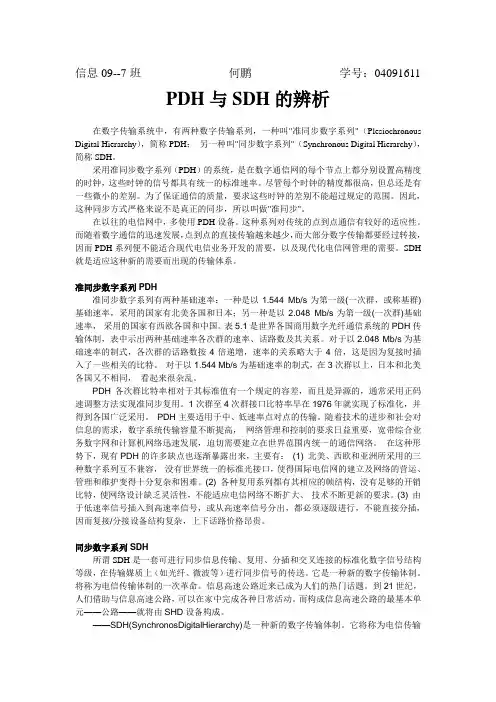

信息09--7班何鹏学号:04091611PDH与SDH的辨析在数字传输系统中,有两种数字传输系列,一种叫"准同步数字系列"(Plesiochronous Digital Hierarchy),简称PDH;另一种叫"同步数字系列"(Synchronous Digital Hierarchy),简称SDH。

采用准同步数字系列(PDH)的系统,是在数字通信网的每个节点上都分别设置高精度的时钟,这些时钟的信号都具有统一的标准速率。

尽管每个时钟的精度都很高,但总还是有一些微小的差别。

为了保证通信的质量,要求这些时钟的差别不能超过规定的范围。

因此,这种同步方式严格来说不是真正的同步,所以叫做"准同步"。

在以往的电信网中,多使用PDH设备。

这种系列对传统的点到点通信有较好的适应性。

而随着数字通信的迅速发展,点到点的直接传输越来越少,而大部分数字传输都要经过转接,因而PDH系列便不能适合现代电信业务开发的需要,以及现代化电信网管理的需要。

SDH 就是适应这种新的需要而出现的传输体系。

准同步数字系列PDH准同步数字系列有两种基础速率:一种是以1.544 Mb/s为第一级(一次群,或称基群)基础速率,采用的国家有北美各国和日本;另一种是以2.048 Mb/s为第一级(一次群)基础速率,采用的国家有西欧各国和中国。

表5.1是世界各国商用数字光纤通信系统的PDH传输体制,表中示出两种基础速率各次群的速率、话路数及其关系。

对于以2.048 Mb/s为基础速率的制式,各次群的话路数按4倍递增,速率的关系略大于4倍,这是因为复接时插入了一些相关的比特。

对于以1.544 Mb/s为基础速率的制式,在3次群以上,日本和北美各国又不相同,看起来很杂乱。

PDH各次群比特率相对于其标准值有一个规定的容差,而且是异源的,通常采用正码速调整方法实现准同步复用。

1次群至4次群接口比特率早在1976年就实现了标准化,并得到各国广泛采用。

在数字通信网中,为了提高传输效率,常常需要将若干路低速数字信号合并成一路高速数字信号,以便通过高速信道进行传输.实现此功能的设备称为数字复接系统.数字复接系统包括发送端和接收端两部分,通常称为复接器和分接器.为了使分接器的帧状态相对于复接器的帧状态获得并保持相位关系,以便正确地实施分接,数字复接系统在发送端把低速数字信号合并为高速信号的同时,往往还要插入用于同步的帧同步码;而在接收端,分接器要把发送端数字信号中的帧同步码检测出来并去除,然后才能分解为原来的支路数字信号,其中完成帧同步码检出这一功能的单元称为数字复接系统的帧同步器.在合路数字信号中,帧同步码能否被准确识别直接决定了能否正确的分接出各个支路信号.目前,FPGA已在通信领域得到了广泛应用,这也为数字复接技术提供了灵活且可移植的设计方法.本文将介绍数字复接系统中帧同步器的工作原理和FPGA的设计流程,同时将给出具体实现方法以及设计中需要注意的问题.1 帧同步器原理图1是笔者设计的一种数字复接系统接收端的原理框图.其中,定时发生器为帧同步系统提供帧定位标志信号;帧同步系统用来检测所传输数据码流中的帧同步码;比特分接电路用于把串行数据转换成并行数据;告警优先电路用来指示当前系统处于同步状态还是失步状态.在复接系统的发送端,可以将帧同步码集中插在每帧的开头位置;也可以将其分散插在各个支路的前面.前者称为帧同步码集中插入法,后者称为分散插入法.图2所示是使用集中插入法时,接收端帧同步器的原理框图.通常帧同步电路有两种状态,同步未建立时系统处于搜捕态,建立后则处于保持态;保持态下的同步保护措施称为前方保护,搜捕态下的同步保护措施称为后方保护.帧同步系统电路设计的原则是:同步建立时,假同步概率要小;同步建立后,漏同步概率要小.图2中的帧同步器前端是由8位移位寄存器组成的帧同步码检测电路,当输入码流中无同步码组时,检测电路输出始终为1,这时定时发生器关闭,比较/计数电路(由a、b、c、d四个D触发器组成)不工作,系统处于搜捕态;一旦在输入码流中检测到同步码组,检测电路输出就为0,定时发生器开始产生比较/计数电路的计数时钟,计数器开始后方保护计数;如果随后在规定时刻上又连续α-1次(图中α=3)检测到帧同步码组,则系统同步,帧同步器进入保持态.在同步保持状态下,一旦帧同步码检测电路在规定时刻有一次未发现帧同步码,步码检测电路将继续搜捕,直至检测到真正的帧同步码为止.2.4 比较/计数电路计数电路用于完成搜捕态与保持态下的计数.搜捕态下,当帧同步码检测电路连续3α=3 次捕获到同相位的正确帧同步码时,帧同步器将进入保持态;而在保持态下,如果帧同步码检测电路连续4(β=4)次未检测到帧同步码,帧同步器将进入搜捕态.程序如下(其中,比较/计数电路计数时钟clk_yf5由帧定位标志信号f8和时钟clk产生,yf2为输出保持结果,yf3为输出搜捕结果):3 设计中需要注意的问题设计中要严格控制定时发生器产生时钟clk_yf5的宽度,以避免出现不定状态.如果帧定位标志信号f8与帧同步检出电路都是由时钟clk的上升沿或下降沿产生的,那么clk_yf5脉冲中就会出现一小段不定状态,而在这段时间里帧同步系统是不能正常工作的.所以,帧定位标志信号f8由时钟clk的下降沿触发产生,帧同步检出电路则由时钟clk的上升沿触发,这样便可以得到一半码元宽度的时钟clk_yf5脉冲,且脉冲中不存在不定状态.设计中应多采用同步时序电路来实现各个进程模块的功能,以免电路中产生毛刺.。

A TM技术在SDH上实现宽带传输邓银波3(重庆邮电学院教务处,重庆400065)摘 要 论述A TM技术在SDH上实现宽带传输,讨论了A TM技术和SDH技术的优点,以及A TM SDH技术建立宽带信息网的方案及其优势。

关键词 A TM;SDH;宽带信息网中图法分类号 TN915.2The Techn ique of AT M Rea l izesW ideband Tran s m ission i n S D HD eng Y inbo(T each ing A f f a irs D iv ision,Chong qing U n iversity of P osts and T eleco mm un ica tions,Chong qing400065) Abstract T h is paper in troduces superi o rity of A TM and SDH w ideband tran s m issi on sys2 tem.It discu sses advan tage of A TM and SDH,and A TM SDH w ideband info rm ati on net2 w o rk.Key words A TM;SDH;w ideband info rm ati on netw o rk0 引 言随着通信领域一些新的信息业务的开发,如数据通信业务、图象、话音、多媒体等迅速增加,在信息网络上需要处理的各种宽带信息业务越来越多,特别是采用了能提供宽带业务的光纤技术能支持具有同步时分交换、高速大容量等特点的同步数字系列(SDH)网络。

因而SDH技术是建立信息网络理想的技术基础,同时面对繁杂的多种业务、不断变化的技术标准和管理法规会给信息网络建设带来巨大压力,不过最近出现用于在电信网络上传输业务量的新类型——异步传递模式(A TM)。

A TM可提供灵活的多业务广域平台,能支持VBR(可变比特率)和任意速率(如非2M b it s的整数倍),可能保证每个用户流所需的传输质量。

1、什么是通信网?人们常说的“三网”指的是什么?是由一定数量的节点(包括终端设备和交换设备)和连接节点的传输链路相互有机地组合在一起,以实现两个或多个规定点间信息传输的通信体系。

电信网,广播电视网,宽带网2、通信网在硬件设备的构成要素是什么?硬件包括终端设备、传输链路及交换设备3通信网的基本结构有哪些?网形网星形网复合形网总线形网环形网树形网(前三种应用最多)4 存储-转发交换最基本的思想是什么?分组交换5 什么是固定通信网的等级结构?等级结构的固定电话网中通常采用什么拓扑结构?等级结构就是将全网的交换局划分为若干个等级。

低等级的交换局与管辖它的交换局相连、形成多级汇接辐射网即星形网的拓扑结构;而最高等级的交换局则直接相连,形成网形网的拓扑结构。

从整体来看,整个电话网呈现复合形网的拓扑结构。

7 、国内长途电话网分为两极,DC1 和DC2 分别指什么?功能是什么?省级交换中心(DC1):汇接全省(含终端)长途来话、去话话务本地网交换中心(DC2):职能是汇接本地网长途终端话务。

8 、本地网的概念是什么?扩大本地网的特点和主要类型有哪些?概念:本地电话网简称本地网,是指在同一个长途编号区范围内,由若干个端局、汇接局、局间中继线、长市中继线,以及用户线、电话机组成的电话网。

用来疏通接续本长途编号区范围内任何两个用户间的电话呼叫和长途发话、来话业务。

特点:分区汇接①分区单汇接②分区双汇接全覆盖汇接类型:(1)特大和大城市本地网:用于直辖市、省会或经济发达人口众多的省级城市的组网。

(2)中等城市本地网:用于地级市城市组网。

9 、试画出本地网四种汇接方式的示意图。

集中汇接来话汇接去话汇接来去话汇接10 、简述长途网的路由选择规则。

1、网中任一长途交换中心呼叫另一长途交换中心的所选路邮局最多为3个;2、同一汇接区内的话务应在该汇接区内疏通;3、发话区的路由选择方向为自下而上,受话区的路由选择方向为自上而下;4、按照“自远而近”的原则设置选路顺序,即首选直达路由,次选迂回路由,最后选最终路由。

WSS10+ 5.8G宽带IP微波接入设备用户手册北京天合立方科技发展有限责任公司缩略语表目录1 概述 (5)1.1产品简介 (5)1.2产品的技术特点 (5)1.3功能简介 (6)1.4设备的典型应用 (6)2 设备概述 (7)2.1设备的组成 (7)2.2设备的接口 (8)2.2.1一体机的接口说明 (8)2.2.2 分体机的接口说明 (9)2.3设备的工作原理 (12)2.3.1中频单元(IDU)系统原理方框图 (12)2.3.2射频单元(ODU)系统方框图 (14)3 设备技术指标 (15)3.1分体机技术指标 (15)3.1.1中频单元(IDU)技术指标 (15)3.1.2 射频单元(ODU)技术指标 (17)3.2室外一体机技术指标 (18)4 系统传输容量 (18)5 设备的网络管理说明 (19)5.1设备状态菜单 (20)5.1.1设备参数设置 (21)5.2系统配置菜单 (24)5.3网络配置界面 (25)5.4密码配置界面 (25)6设备的安装 (26)6.1安装前的准备 (26)6.1.1 施工技术资料 (26)6.1.2 施工使用的工具仪表 (26)6.1.3 安装位置的确定与抱杆的安装 (26)6.1.4 开箱检查 (26)6.2系统的安装 (27)6.2.1 分体机的安装 (27)6.2.2一体机的安装 (28)6.3天线的调整 (28)6.3.1 通电 (29)6.3.2 天线的校对 (29)6.4系统开通测试 (29)7设备维护及故障处理 (30)7.1日常维护 (30)7.2故障分析处理 (30)7.3维修注意事项 (30)8 包装、储存及运输 (30)感谢您使用WSS10+5.8G宽带IP微波接入设备,本手册主要介绍此设备的系统性能及工作参数指标。

随着设备的不断改进,软件的不断升级,本手册中的参数、规格、尺寸及其他如有变更,我公司不另行通知。

相关参数可于本公司网站下载或与公司的相关人员沟通得到。

1.1.2 DMT调制ADSL的调制方法,可以分为:CAP、DMT两种,而DMT方式又分为频分复用方式(FDM)和回声抵消方式(EC)。

其中DMT技术相比CAP技术具有线路适应性强的优势,被确立为ITU-T的建议,表1-1为CAP和DMT两种调制方式的比较。

下主要说明DMT调制技术以及DMT上下行频率使用的两种方式:FDM方式、EC方式。

1. DMT调制DMT(Discrete MultiTone)离散多频调制技术,以4.3125kHz频宽为基本单位,把1MHz的频带分为256个子信道,而原本普通的POTS业务在电话线上占用的频带大致为300Hz-4kHz,再加上隔离效果等因素,在DMT 技术中把0-25kHz的频带都留给话音业务使用,也就是前面的6个子信道,实际用来作为数字业务传输的子信道为250个。

DMT技术中的每个信道都采用QAM技术(除去前面用于话音业务的子信道),然后把每个子信道的输出波形再叠加(因为每个子信道的频率不一样)后输入到线路上;对端接收端再根据频率先分解成各子信道的输入波形,各子信道再采用QAM解调过程解出传送的比特数据。

250个子信道用于传送ADSL数据业务,其中0-31(前面6个不可用)是分给上行(用户端到局端),下行(局端到用户端)有两种分配方案。

一种是分配全部的0-255子信道,重叠使用上行业务占用的子信道,但前提必须采用回波抵消技术;另一种就是分配32-255子信道,这时上下行频带没有重叠,所以无需回波抵消技术。

2. DMT上下行频率使用方式(1) 频分复用方式(FDM):上行导频点在69kHz(子带#16)下行导频点在276kHz(子带#64)上行数据传输子带从#7到#31 (除去#16)下行数据传输子带从#3 (2) 回波抵消方式(EC)上行导频点在69kHz(子带#16)下行导频点在276kHz(子带#64)上行数据传输频段从#7到#31 (除去#16)下行数据传输频段从#7到 1.1.3 常用概念1. ADSL帧发送接收流程(以DMT调制为例):[帧]——〉CRC——〉加扰——〉FEC编码——〉(交织)——〉DMT调制——〉整波及D/A——〉 ------------------------------------通道--------------------------------------——〉整波及D/A——〉DMT——〉(解交织)——〉FEC解码——〉解扰——〉CRC——〉[帧]其中:交织与解交织只有在交织方式下才有效。

一种宽带复接器的设计与实现

摘要:DVB-C数据广播系统的基本结构,详细分析了 TS复接器在整个 系

统中的重要性与功能,提出一种 DSP与FPGA相结合的实现方案,及其设计方 法和系

统结构。

信息时代的到来使人们需要共享越来越多的信息。随着信息及其需求的爆 炸性

增长,信息的选择及传输速率成为一个重要问题。有线电视网络有其固有 的高带宽

特性,适合大容量的数据传输和实时性要求,使宽带数字接入成为可 能。在我国由

于有线电视网是一个已经存在的接入网络,成本低、可维护性 强、频率资源丰富、

覆盖面广、用户量大,因而通过有线电视网进行数据广播 是目前国内应用领域的一

大热点。 DVB-C是 ETSI (European Telecommunications Standards Institute )提

供的基于 Cable 上数据广播的 一整套标准[1,2,3],本文首先介绍DVB-C数据广播

系统的基本结构,接着详细 分析TS复接器在整个系统中的重要性与功能,然后详细

说明利用 DSP(数字信

号处理器)与FPGA(现场可编程门阵列)相结合的一个实现方案,阐明了其中 的设

计方法和系统结构。

1 DVB-C

数字广播系统简介

一个实用的DVB-C广播系统的结构如图1所示[3-6],整个系统可以大致分为三 个

部分:( 1)信息前端,包括视频服务器、播控服务器、通信控制服务器、用

户

>'http://lu nwen .freekaoya n.com/gua nlilu nwen/' target='_bla nk'

class='infotextkey'>

管理工作站、节目采集工作站、节目 编排工作站等;

(2)传输网络,利用现有的HFC网络巨大的频带资源实现数据传输;(3)用 户终

端,用户利用机顶盒或者Cable-Modem接收和浏览信息。

从图1可以看到,在DVB-C数字广播系统中,一个通道上传输的数据可能包含 多路

节目或来自多个节目源,因此需要对多路多节目 TS流(MPTS进行复合转

接,生成一个符合DVB-C标准的MPTS再经调制后在一个通道上传输。由

TS

复接器来完成这个功能。TS复接器在前端系统中相当于一个交换机,它负责对 多个

MPTS4行转换和复合,生成一个 MPTS

在复合过程中,要完成服务信息

(PSI/SI )、多路MPTS勺交织等工作[4,5]。从中可以看出复接器在整个系统

中的重要性,TS复接器工作是否稳定可靠,直接影响整个系统的正常运作。

2 TS

复接器勺设计方法

在该系统中需要对6路数字卫星电视节目进行复接。各路有效速率为 0〜

15Mbps的异步串行接口( ASI)输入,6路总速率不超过36Mbps

输出为恒定 速率

38.1Mbps的ASI输出,输出的MPTS为符合DVB-C标准的传送流;复接器 度同PID

,

包括将输入MPT卿的PSI/SI等不需要的信息过滤掉以及对有效 TS 包重新分配PID。

新的PSI/SI信息作为复接器的输入按一定速率插入到 MPIS 中,插入的PSI/SI信息

包括节目关联表(PAT、节目映射表(PMT、网络信 息表(NIT)、服务描述表(

SDT

等[4,5],复接器还能接受来自播控系统的数 据信息,作为复接器输出流的一部

分。系统的功能模块结构如图 2 所示。

由图 2 可以看到,由于需要处理的数据速率快、数据量大、要求实时性,一般 的处

理芯片无法完成。为了达到上述目的,采用高速 DSP和FPGA一起来完成。

整个系统基于DSP和FPGA配以CPLD高速SRAM异步FIFO等。DSP具有运 算速度快、

计算能力哟、可用资源比较丰富的特点,尤其适合于实现各种数字 信号的处理功

能,在各种领域具有广泛的应用。但由于所要处理的数量太大, 仅靠DSP片内

RAM

是远远不够的,所以还必须要有大容量、访问速度快的缓冲 区对接收到的数据进行

缓冲,以便于 DSP进行处理。基本思想是FPGA完成TS 包过滤和PID置换、

PSI/SI

提取等工作,系统的控制工作、TS包交织算法则由 DSP完成,整个控制逻辑则由

CPLD

完成。

3 TS

复接器的一种实现方案

针对上述分析,采用DSP与 FPGA相结合的方法成功实现了 TS复接器,该实现 方案

如图3所示。图3中的DSP采用TI公司的TMS320VC5410-100它具有 100MIPS的快速

处理能力,以及片内64K的RAM和多个串口等资源,其片外寻 址空间可以多达

8M

Word FPGA则采用了 Xilinx 公司的XCV300

笔者为DSP扩展了 2M Word的高速SRAM作缓冲,分为两个1M Word的双缓冲, 处理

时以帧为单位,DSP和FPGAR能访问其中一个1M Word的SRAM 一般情况 下,FPGA从

输入接口把一帧数据存入其中一个缓冲区, DSP对另外一个缓冲区

进行操作,根据交织表把数据送到 FIFO,再输出到输出接口,两者的总线切换 由

FPGA

负责完成。

图 3 可以分为以下几个模块:

a. 输入模块:使用ASI接口将270M串行编码数据转换成27M

并行数据,并提供 接收

时钟、数据有效等控制信号。

b. FPGA模块:接收ASI接口输出的并行数据,实现同步、PID置换、PSI/SI

提 取

等,并将数据写入SRAM中,跟踪记录每路的TS包数;产生帧切换脉冲,控 制双缓

冲区的切换。

c. DSP主控模块:DSP

完成整个系统的控制功能,计算交织表,负责与播控系统 的通

信等。

d. CPLD模块:根据DSP

提供的 地址和数据进行译码,对总线上 的各设备进行互斥

片选;产生中 断申请信号;对发送FIFO的全 空信号进行采样,控制从发送

FIF 0

读数据并将数据送给输出

ASI

接口。

e. 输出模块:由CPLD提供控制 信号,将数据从发送FIFO

读出 来,同时写入发送

ASI

接口。

f.

命令通信接口:复接器通过串 口与播控服务器通信,从服务器 接收系统复位、

状态查询、PID 置换、PSI/SI插入和提取等命 令,并向服务器反馈必要的信 息。

为保证数据信号接收端解码器能 正确解码,缓冲区不会上溢或下 溢,解码输出信号

平稳,要求复 接器输入的各路TS包均匀分布在输出数据流中,所以必须在发送之前

对输入的 各路TS包做交织。采用实时交织的方法,FPGA能够在每次帧切换的时候记

录 各路TS包的数据目,然后计算交织表。交织表依照如下方式计算: 设数据流共

有K路MPTS流,数据流的一个数据帧有 M个TS包,每路

MPTSt m(i)(i=0,1,...k-1)

个TS包,假设各路TS包由大到小排序,m(0)最大,否则 首先排序。根据M K、

m(i)

对输入的TS流进行交织,对第i路有:用p(i,n) 指示第i路是否将一个TS包输出

到MPTS^的第n个TS包,q(i)表示第i路中 已输出到MPTS^的TS包数,初值为0;

i=0,n=0; while( n

if (P(i, n)-q(i)>=1)

{ 将第i路的第q(i)个TS包输出到MPTS^的第n个TS包; q(i)++;

n++; }

i++;

if(i=K) i=0;

}

最后在 Xilinx 的 Xilinx Foundation Series 先对所设计的逻辑进行仿真,利 用

DSP的simulation

进行程序的仿真,仿真结束后在单板上进行调试。由于选 用的

FPGA的容量限制,门数有限,能够进行 PID

置换的个数受到限制,但是可 以根据估

算出的各种TS包数对每一路能够置换的PID数目进行动态调整;由于 采用了交织算

法,能够对突发数据进行很好的平滑作用,利用后级进行处理。 把复接器接到图

1

所示的系统中去,通过复接器处理的节目流在 STB(机顶

盒)上能够接收到稳定清晰的节目,并且系统稳定工作,说明本文所设计的复 接器达

到了预期目的。

本文详细分析了 DVB-C数据广播系统中的关键部件--复接器的一种实现方法, 该方

法基于DSP+FPG的结构,便于以后的升级与扩展。同时,所设计的复接器 除了应用

在DVB-C数据广播系统外,凡是输入符合 DVB-C的TS流标准均可以使 用。