组成原理实验课件--运算器

- 格式:ppt

- 大小:4.47 MB

- 文档页数:48

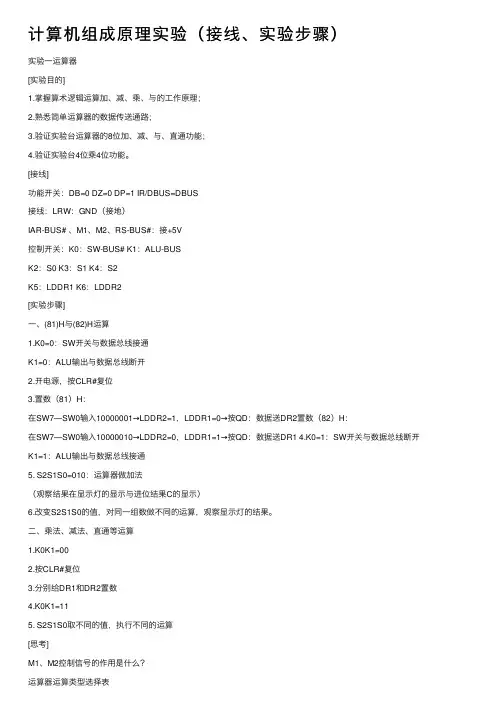

计算机组成原理实验(接线、实验步骤)实验⼀运算器[实验⽬的]1.掌握算术逻辑运算加、减、乘、与的⼯作原理;2.熟悉简单运算器的数据传送通路;3.验证实验台运算器的8位加、减、与、直通功能;4.验证实验台4位乘4位功能。

[接线]功能开关:DB=0 DZ=0 DP=1 IR/DBUS=DBUS接线:LRW:GND(接地)IAR-BUS# 、M1、M2、RS-BUS#:接+5V控制开关:K0:SW-BUS# K1:ALU-BUSK2:S0 K3:S1 K4:S2K5:LDDR1 K6:LDDR2[实验步骤]⼀、(81)H与(82)H运算1.K0=0:SW开关与数据总线接通K1=0:ALU输出与数据总线断开2.开电源,按CLR#复位3.置数(81)H:在SW7—SW0输⼊10000001→LDDR2=1,LDDR1=0→按QD:数据送DR2置数(82)H:在SW7—SW0输⼊10000010→LDDR2=0,LDDR1=1→按QD:数据送DR1 4.K0=1:SW开关与数据总线断开K1=1:ALU输出与数据总线接通5. S2S1S0=010:运算器做加法(观察结果在显⽰灯的显⽰与进位结果C的显⽰)6.改变S2S1S0的值,对同⼀组数做不同的运算,观察显⽰灯的结果。

⼆、乘法、减法、直通等运算1.K0K1=002.按CLR#复位3.分别给DR1和DR2置数4.K0K1=115. S2S1S0取不同的值,执⾏不同的运算[思考]M1、M2控制信号的作⽤是什么?运算器运算类型选择表选择操作S2 S1 S00 0 0 A&B0 0 1 A&A(直通)0 1 0 A+B0 1 1 A-B1 0 0 A(低位)ΧB(低位)完成以下表格ALU-BUS SW-BUS# 存储器内容S2S1S0 DBUS C输⼊时:计算时:DR1:01100011DR2:10110100(与)DR1:10110100DR2:01100011(直通)DR1:01100011DR2:01100011(加)DR1:01001100DR2:10110011(减)DR1:11111111DR2:11111111(乘)实验⼆双端⼝存储器[实验⽬的]1.了解双端⼝存储器的读写;2.了解双端⼝存储器的读写并⾏读写及产⽣冲突的情况。

运算器组成实验原理

运算器是计算机的关键部件之一,它负责执行各种数学和逻辑运算。

一个基本的运算器通常由算术逻辑单元(ALU)、控

制器和寄存器组成。

算术逻辑单元(ALU)是运算器的核心部件,它负责执行各

种算术和逻辑运算,如加法、减法、与、或等。

ALU通常由

一组逻辑门、加法器和寄存器组成。

逻辑门用于执行逻辑运算,如与门和或门可以实现与和或运算。

加法器用于执行加法运算,可以将两个二进制数相加并得到结果。

寄存器用于存储运算的中间结果或最终结果。

控制器是运算器的另一个重要组成部分,它负责调度和控制ALU的操作。

控制器根据指令和输入信号来确定ALU要执行

的操作,并将结果存储到相应的寄存器中。

控制器通常由逻辑电路和状态机组成,它可以根据不同的输入信号和状态来产生相应的控制信号。

寄存器是运算器中的存储设备,用于存储数据和中间结果。

寄存器可以存储一个或多个位的数据,并且可以通过地址进行读写操作。

在运算器中,寄存器主要用于存储操作数和结果。

运算器通常具有多个寄存器,以便同时执行多个运算。

总的来说,运算器的组成实验原理主要是基于逻辑门、加法器、寄存器和控制器的组合和控制。

通过合理的设计和控制,可以实现各种数学和逻辑运算,从而完成计算机的核心功能。

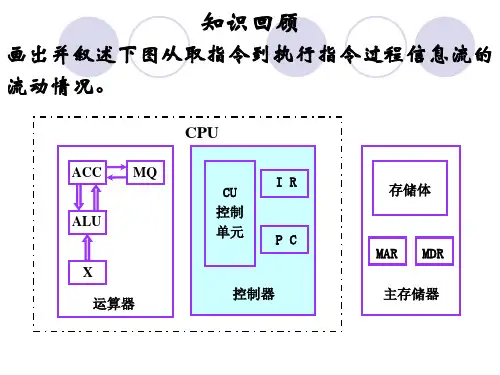

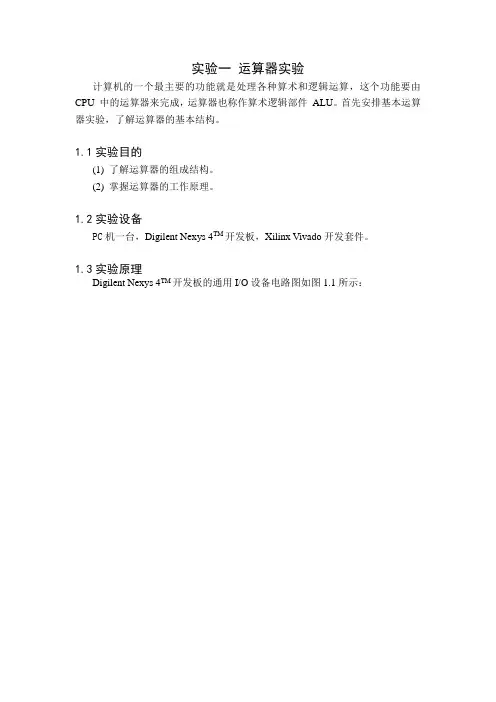

实验一运算器实验计算机的一个最主要的功能就是处理各种算术和逻辑运算,这个功能要由CPU 中的运算器来完成,运算器也称作算术逻辑部件ALU。

首先安排基本运算器实验,了解运算器的基本结构。

1.1实验目的(1) 了解运算器的组成结构。

(2) 掌握运算器的工作原理。

1.2实验设备PC机一台,Digilent Nexys 4TM开发板,Xilinx Vivado开发套件。

1.3实验原理Digilent Nexys 4TM开发板的通用I/O设备电路图如图1.1所示:图1.1Digilent Nexys 4TM开发板的通用I/O设备电路图如上所示,Nexys4 DDR板包括2个三色LED,16个滑动开关,6个按钮开关,16个单体LED和1个数字-8的七段显示器。

为了防止粗心大意的短路(假如一个FPGA针脚分派到一个按钮开关或者滑动开关被粗心大意的定为输出时将发生短路)损害,按钮开关和滑动开关通过串联电阻连接到FPGA。

5个按钮开关分派到1个“+”信号的配置是瞬时开关,在正常情况下,这些瞬时开关不用时产生低信号输出,被压时产生高信号输出。

另一方面,“CPU RESET”红色按钮不用时产生高信号输出,被压时产生低信号输出。

“CPU RESET”按钮常常在EDK(嵌入式开发套件)设计中用于重置进程,但你也可以把它当为常用按钮开关使用。

滑动开关根据他们的位置产生固定的高或低信号输入。

16个单体高效LED通过330欧姆的电阻阳极连接到FPGA,所以当其各自I/O 针脚应用到逻辑高电压时他们应该是打开的。

不被用户访问的额外LED表示电源,FPGA编程状态和USB和以太网端口状态。

控制显示模块的七段显示器的原理图如图1.2所示:图1.2七段显示器原理图Nexys4 DDR板包含2个4位同阳极7段LED显示器,配置表现得像1个8位数字显示。

8位数字的每一个由分派在一个“数字8”图案中的7段组成,每段嵌入1个LED。

如图17所示,每段LED是单独发光,所以128种模式的任何一个可以通过使某些LED段发光和另外的不发光显示在一个数字上。