典型处理器及体系结构

- 格式:pptx

- 大小:432.54 KB

- 文档页数:55

电脑的大脑CPU(中央处理器)CPU是中央处理单元(Central Processing Unit)的缩写,它可以被简称做微处理器(Microprocessor),不过经常被人们直接称为处理器(processor)。

不要因为这些简称而忽视它的作用,CPU是计算机的核心,其重要性好比大脑对于人一样,因为它负责处理、运算计算机内部的所有数据,而主板芯片组则更像是心脏,它控制着数据的交换。

CPU的种类决定了你使用的操作系统和相应的软件。

CPU主要由运算器、控制器、寄存器组和内部总线等构成,是电脑的核心,再配上储存器、输入/输出接口和系统总线组成为完整的电脑。

CPU的基本结构、功能及参数CPU主要由运算器、控制器、寄存器组和内部总线等构成。

寄存器组用于在指令执行过后存放操作数和中间数据,由运算器完成指令所规定的运算及操作。

CPU主要的性能指标有:1.主频主频也叫时钟频率,单位是MHz(或GHz),用来表示CPU的运算、处理数据的速度。

CPU的主频=外频×倍频系数。

很多人认为主频就决定着CPU的运行速度,这不仅是个片面的,而且对于服务器来讲,这个认识也出现了偏差。

至今,没有一条确定的公式能够实现主频和实际的运算速度两者之间的数值关系,即使是两大处理器厂家Intel和AMD,在这点上也存在着很大的争议,我们从Intel的产品的发展趋势,可以看出Intel很注重加强自身主频的发展。

像其他的处理器厂家,有人曾经拿过一块1G的全美达处理器来做比较,它的运行效率相当于2 G的Intel处理器。

所以,CPU的主频与CPU实际的运算能力是没有直接关系的,主频表示在CPU内数字脉冲信号震荡的速度。

在Intel的处理器产品中,我们也可以看到这样的例子:1 GHz Itanium芯片能够表现得差不多跟2.66 GHz Xeon/Opteron一样快,或是1.5 GHz Itanium 2大约跟4 GHz Xeon/Opteron一样快。

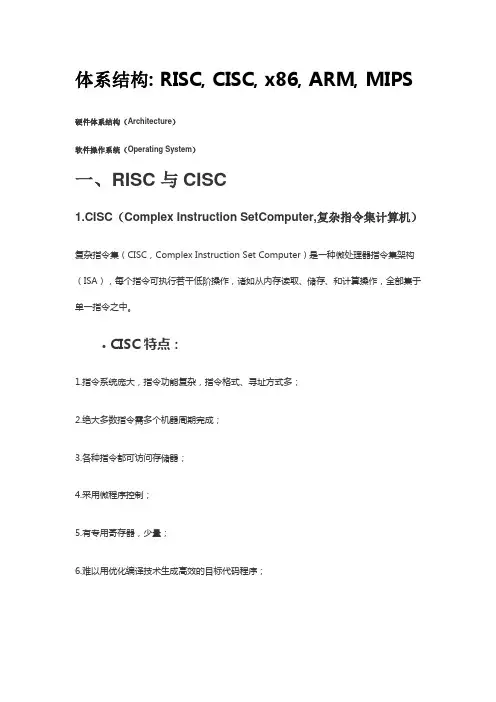

体系结构: RISC, CISC, x86, ARM, MIPS硬件体系结构(Architecture)软件操作系统(Operating System)一、RISC与CISC1.CISC(Complex Instruction SetComputer,复杂指令集计算机)复杂指令集(CISC,Complex Instruction Set Computer)是一种微处理器指令集架构(ISA),每个指令可执行若干低阶操作,诸如从内存读取、储存、和计算操作,全部集于单一指令之中。

CISC特点:1.指令系统庞大,指令功能复杂,指令格式、寻址方式多;2.绝大多数指令需多个机器周期完成;3.各种指令都可访问存储器;4.采用微程序控制;5.有专用寄存器,少量;6.难以用优化编译技术生成高效的目标代码程序;在CISC指令集的各种指令中,大约有20%的指令会被反复使用,占整个程序代码的80%。

而余下的80%的指令却不经常使用,在程序设计中只占20%。

2.RISC(reduced instruction setcomputer,精简指令集计算机)精简指令集这种设计思路对指令数目和寻址方式都做了精简,使其实现更容易,指令并行执行程度更好,编译器的效率更高。

它能够以更快的速度执行操作。

这种设计思路最早的产生缘自于有人发现,尽管传统处理器设计了许多特性让代码编写更加便捷,但这些复杂特性需要几个指令周期才能实现,并且常常不被运行程序所采用。

此外,处理器和主内存之间运行速度的差别也变得越来越大。

在这些因素促使下,出现了一系列新技术,使处理器的指令得以流水执行,同时降低处理器访问内存的次数。

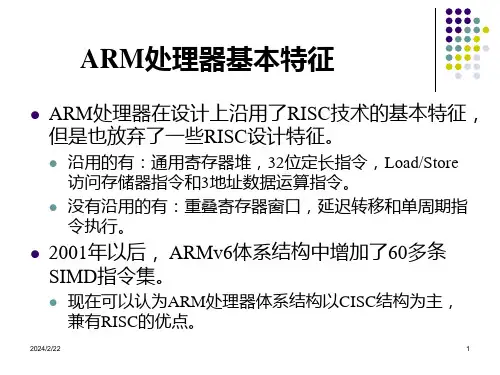

实际上在后来的发展中,RISC与CISC在竞争的过程中相互学习,现在的RISC指令集也达到数百条,运行周期也不再固定。

虽然如此,RISC设计的根本原则——针对流水线化的处理器优化—0—没有改变,而且还在遵循这种原则的基础上发展出RISC的一个并行化变种VLIW(包括Intel EPIC),就是将简短而长度统一的精简指令组合出超长指令,每次执行一条超长指令,等于并行执行多条短指令。

Cortex-M3体系结构学习笔记-寄存器知识要想了解Cortex-M3体系结构的知识,必须学习一下几个部分:CM3微处理器内核结构,处理器的工作模式及状态,寄存器,总线结构,存储器的组织与映射,指令集,流水线,异常和中断,存储器保护单元MPU。

这篇文章主要是我学习CM3机构寄存器的知识笔记。

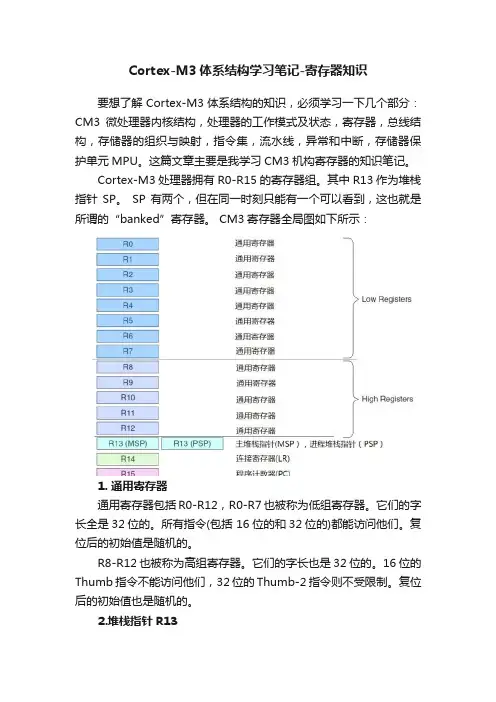

Cortex‐M3 处理器拥有R0‐R15 的寄存器组。

其中 R13 作为堆栈指针SP。

SP 有两个,但在同一时刻只能有一个可以看到,这也就是所谓的“banked”寄存器。

CM3寄存器全局图如下所示:1. 通用寄存器通用寄存器包括R0-R12,R0-R7也被称为低组寄存器。

它们的字长全是32位的。

所有指令(包括 16位的和32位的)都能访问他们。

复位后的初始值是随机的。

R8-R12也被称为高组寄存器。

它们的字长也是32位的。

16位的Thumb指令不能访问他们,32位的Thumb-2指令则不受限制。

复位后的初始值也是随机的。

2.堆栈指针R13Cortex‐M3 拥有两个堆栈指针,然而它们是banked,因此任一时刻只能使用其中的一个。

•主堆栈指针(MSP):复位后缺省使用的堆栈指针,用于操作系统内核以及异常处理例程(包括中断服务例程)•进程堆栈指针(PSP):由用户的应用程序代码使用。

堆栈指针的最低两位永远是0,这意味着堆栈总是4 字节对齐的。

(在ARM 编程领域中,凡是打断程序顺序执行的事件,都被称为异常(exception)。

除了外部中断外,当有指令执行了“非法操作”,或者访问被禁的内存区间,因各种错误产生的fault,以及不可屏蔽中断发生时,都会打断程序的执行,这些情况统称为异常。

在不严格的上下文中,异常与中断也可以混用。

另外,程序代码也可以主动请求进入异常状态的(常用于系统调用).)在处理模式和线程模式下,都可以使用MSP,但只能在线程模式下使用PSP。

堆栈与微处理器模式的对应关系如下图所示。

使用两个堆栈的目的是为了防止用户堆栈的溢出影响系统核心代码(如操作系统内核)的运行。

CPU的功能和组成提交新文章CPU组成计算机的工作过程就是计算机执行程序的过程。

程序是一个指令序列,这个序列明确告诉计算机应该执行什么操作,在什么地方能够找到用来操作的数据。

一旦把程序装入主存储器,计算机就可以自动执行取出指令和执行指令的任务。

专门用来完成此项工作的计算机部件称为中央处理器(Central Processing Unit,CPU),做成单片集成电路的CPU通常又称为微处理器(Microprocessor)。

图3-1为陶瓷PGA封装的Intel 80486 DX2 CPU。

(a) 顶视图(b) 底视图图3-1 陶瓷PGA封装的Intel 80486 DX2 CPU计算机工业从1960年代早期开始使用CPU这个术语。

迄今为止,CPU从形态、设计到实现都已发生了巨大的变化,但是其基本工作原理却一直没有大的变化。

早期的CPU通常是为大型、特定的应用而定制的。

目前,这种为特定应用而设计定制CPU的昂贵方法,在很大程度上已经让位于开发可大规模生产的通用处理器。

这种标准化趋势,大致始于分立晶体管大型计算机(Mainframe)和小型计算机(Minicomputer)年代,并且随着集成电路(IC)的普及而大大加速。

集成电路可以把日益复杂的CPU设计制造在很小的空间里。

CPU的小型化和标准化,大大增加了这些数字器件在现代生活中的应用范围,远远超出了专用运算机器这一有限的应用。

现代微处理器已经随处可见,从汽车到手机,甚至儿童玩具。

3.1 CPU的功能和组成3.1.1 指令系统的发展指令是计算机硬件能够识别并直接执行操作的命令,一台计算机中所有指令的集合构成了该计算机的指令系统。

指令系统是表征一台计算机性能的重要因素,其格式与功能不仅直接影响到机器的硬件结构,也直接影响到系统软件,影响到机器的适用范围。

因此,设计一个合理有效、功能齐全、通用性强并且丰富的指令系统是至关重要的。

从计算机组成的层次结构来说,计算机的指令分为微指令、机器指令和宏指令三类。

计算机体系结构基础计算机体系结构是计算机科学中的一个重要概念,它定义了计算机硬件和软件之间的交互方式以及如何组织和设计计算机系统的结构。

本文将探讨计算机体系结构的基础知识,包括指令集体系结构、处理器架构和存储器层次结构。

一、指令集体系结构指令集体系结构(Instruction Set Architecture),简称ISA,是计算机体系结构的基础。

它定义了一组与硬件交互的指令集合,并规定了指令的格式、操作码和寻址方式等。

常见的指令集体系结构包括CISC (复杂指令集计算机)和RISC(精简指令集计算机)。

CISC架构的特点是指令集复杂,提供了丰富的指令集合和多种寻址方式,使得每条指令可以执行多个操作。

而RISC架构则强调指令集的精简性和规范性,将更多的工作转移到编译器层面。

两者的选择取决于需求和设计目标,如应用场景的复杂度和对计算速度和资源利用效率的要求。

二、处理器架构处理器架构(Processor Architecture)决定了计算机的运算能力和效率。

处理器是计算机体系结构的核心部件,其结构和设计方式关系到计算机性能的提升和效能的增加。

传统的处理器架构采用单指令流单数据流(SISD)方式,即每次只能执行一条操作指令和一条数据流,效率有限。

而后来出现的多指令流多数据流(MIMD)方式,则能够同时处理多条指令和数据流,提高了计算能力和效率。

此外,处理器架构还包括流水线结构和超标量结构等。

流水线结构将一条指令的执行过程划分为多个阶段,使得各个阶段可以并行进行,从而提高整体执行效率。

超标量结构则允许多条指令并行执行,更进一步提高了计算速度。

三、存储器层次结构存储器层次结构(Memory Hierarchy)是计算机体系结构中的重要组成部分,用于解决计算机存储器访问速度和容量之间的矛盾。

它按照存取速度和容量的大小将存储器划分为多个层次。

存储器层次结构的基本原理是利用不同层次存储介质的速度和容量差异来平衡。