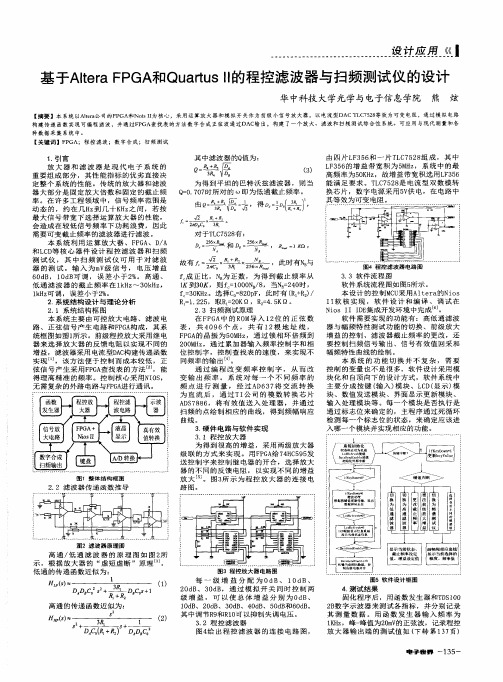

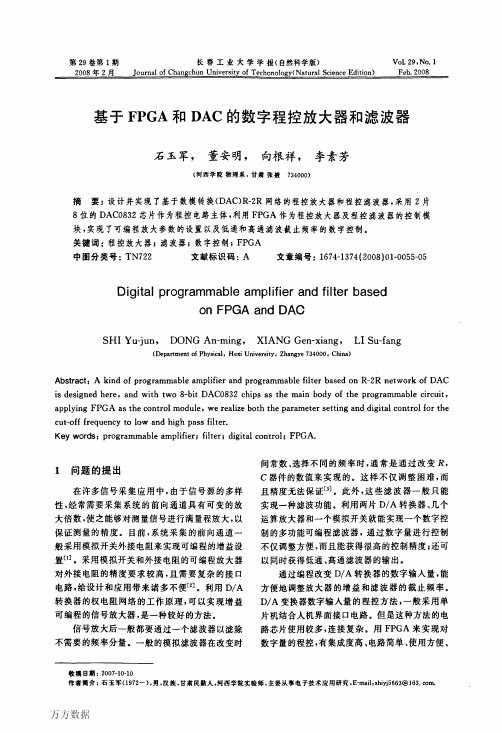

基于FPGA和DAC的数字程控放大器和滤波器

- 格式:pdf

- 大小:689.32 KB

- 文档页数:5

dac程控电压可调电路的工作原理-回复DAC(Digital-to-Analog Converter)程控电压可调电路是一种用于将数字信号转换为模拟电压信号的电路。

在很多应用中,我们需要将数字信号转换为模拟电压信号,以实现各种功能,比如音频处理、信号调制、控制系统等。

DAC电路的工作原理可以分为以下几个步骤:1. 数字信号输入:DAC电路通常通过数字输入端口接收来自数字信号源(比如微控制器、FPGA等)的数字信号。

这些数字信号可以是二进制表示的,也可以是其他自定义的编码方式。

2. 数字信号解码:接收到数字信号后,DAC电路会将其解码为相应的模拟电压值。

这个解码过程一般是通过查表的方式实现的,即根据输入的数字信号值,在一个预先定义好的查找表中找到对应的模拟电压值。

3. 数字信号转换:解码完成后,DAC电路将解码得到的模拟电压值转换为对应的模拟电压信号。

这个转换过程一般是通过电压控制电流源实现的。

例如,通过调节电流源产生的电流大小,可以实现对模拟电压信号的调整。

4. 输出电压滤波:为了保证输出的模拟电压信号质量,需要对其进行一定程度的滤波处理。

这个滤波过程一般是通过低通滤波器实现的,可以削弱或抑制高频成分,从而得到更为平滑的输出模拟电压信号。

通过以上几个步骤,DAC程控电压可调电路可以将输入的数字信号转换为与其数值对应的模拟电压信号。

这种转换可以实现信号的精确控制和调整,从而满足不同应用场景的需求。

在实际应用中,DAC电路的设计需要考虑一些重要的参数和特性。

其中包括分辨率、采样速率、电压范围、线性度、功耗等。

分辨率是指DAC能够提供的不同电压级别的数量,通常用位数表示,例如一个12位DAC可以提供4096个不同的电压级别;采样速率是指DAC每秒可以进行的数字信号采样次数,一般用Hz表示;电压范围是指DAC可以输出的模拟电压信号的范围,一般以伏特为单位;线性度是指DAC电路输出的模拟电压信号与输入的数字信号之间的线性关系程度;功耗是指DAC电路在工作过程中消耗的能量。

基于FPGA的多通道语音信号处理系统实现随着科技的不断发展,人们的生活也得到了极大的变化。

现在的人们更加注重高品质的音乐,同时也对语音信号处理有了更高的要求。

为了满足人们的需求,科学家们发明了一种基于FPGA的多通道语音信号处理系统,能够实现高效率的信号处理。

FPGA是什么?FPGA是Field Programmable Gate Array的缩写,中文名称为现场可编程门阵列。

FPGA可以根据用户的要求进行编程,从而实现特定的功能。

FPGA多通道语音信号处理系统的组成FPGA多通道语音信号处理系统由FPGA芯片、多路ADC、FPGA板、多路DAC等组成。

多路ADC是模数转换器(Analog-to-Digital Converter)的缩写,是一种将模拟信号转换为数字信号的装置。

多路ADC能够同时处理多个通道的模拟信号,将其转换为数字信号,为后续的数字信号处理提供了实时数据支持。

多路DAC是数字模拟转换器(Digital-to-Analog Converter)的缩写,是将数字信号转换为模拟信号的装置。

FPGA芯片是整个系统的核心,它的作用是根据用户要求进行编程,从而实现数字信号的处理和控制。

FPGA板是一个板子,上面集成了FPGA芯片、多路ADC和多路DAC,为整个系统提供了一起工作的基础。

多通道语音信号处理系统的功能FPGA多通道语音信号处理系统能够实现多种处理功能,例如滤波、降噪、分频、等化器等。

滤波滤波处理是将数字信号经过一系列滤波器,滤除干扰和杂音,使得数字信号更加纯净。

FPGA多通道语音信号处理系统可以通过滤波器对语音信号进行处理,使其更加清晰。

降噪降噪处理是去除语音信号中的背景噪音,例如环境噪音、电源噪音等。

FPGA多通道语音信号处理系统通过数字信号处理技术,对语音信号进行去噪,使其更加清晰。

分频分频处理是将语音信号分成不同频段进行处理。

FPGA多通道语音信号处理系统可以通过数字信号处理技术,将语音信号分成不同的频段,为后续处理提供便利。

基于FPGA的音频信号处理研究一、引言随着科学技术的不断发展,电子技术在各个领域中发挥着重要的作用,音频处理技术研究便是其中之一。

基于FPGA的音频信号处理极大地提高了音频信号处理的效率和精度。

二、基于FPGA的音频信号处理概述FPGA(现场可编程门阵列)是一种可编程数字嵌入式IC芯片,它可以采取不同的处理算法来执行各种任务。

而音频信号处理技术则是指对音频信号进行数字处理的过程,将信号处理为需要的形式。

在音频信号处理中,FPGA可以起到并行处理和高速计算的作用。

传统的数字信号处理器(DSP)对于音频信号处理能力较弱,而FPGA则可以通过自适应滤波器、FFT(快速傅里叶变换)、DWT(离散小波变换)等算法,以及直接的数字幅频滤波和数字滤波,对音频信号进行快速且精确的处理。

三、基于FPGA的音频信号处理算法1.自适应滤波器自适应滤波器是利用最小均方误差(LMS)算法的一种数字信号处理技术,它可以使得滤波器的系数根据收到的输入信号自动调整,使其输出信号与所需信号之间的误差最小。

自适应滤波器在音频降噪、语音增强等方面有着广泛的应用。

2.FFTFFT在音频信号处理中有着非常广泛的应用,如音频数据的频率分析、滤波和信号识别等。

FFT通过将时间域信号转换为频域信号,使得计算时间和内存要求大大降低。

3.DWTDWT是一种数字信号处理技术,可以将任意长度的信号转换为一组不同分辨率的信号,从高到低按照频率排列。

DWT在音频压缩、信号分析、音频滤波和语音增强等方面有着广泛的应用。

四、基于FPGA的音频信号处理应用1.音频降噪利用自适应滤波器对音频信号进行处理,可以达到良好的音频降噪效果。

2.音频识别FFT算法可以分析音频数据的频率特征,从而实现语音识别。

3.音频增强利用DWT算法可以将音频信号转换为不同分辨率的信号,并对信号进行分析和滤波,使得音频增强效果更加显著。

五、基于FPGA的音频信号处理发展趋势FPGA在音频信号处理中有着广泛的应用,同时随着FPGA硬件技术的快速发展,其计算能力和存储容量也日益增加。

基于 FPGA 的数字滤波器设计与实现引言:数字滤波器是现代信号处理的重要组成部分。

在实际应用中,为了满足不同信号处理的需求,数字滤波器的设计与实现显得尤为重要。

本文将围绕基于 FPGA的数字滤波器的设计与实现展开讨论,介绍其工作原理、设计方法以及优势。

同时,还将介绍一些实际应用场景和案例,以展示基于 FPGA 的数字滤波器在实际应用中的性能和效果。

一、数字滤波器的基本原理数字滤波器是一种将输入信号进行滤波处理,改变其频谱特性的系统。

可以对频率、幅度和相位进行处理,实现信号的滤波、去噪、增强等功能。

数字滤波器可以分为无限脉冲响应滤波器(IIR)和有限脉冲响应滤波器(FIR)两种类型。

IIR滤波器是通过递归方式实现的滤波器,其输出信号与过去的输入信号和输出信号相关。

FIR滤波器则是通过纯前馈结构实现的,其输出信号仅与过去的输入信号相关。

两种类型的滤波器在性能、复杂度和实现方式上存在一定差异,根据具体的应用需求选择适合的滤波器类型。

二、基于 FPGA 的数字滤波器的设计与实现FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,通过可编程逻辑单元(PLU)、可编程连线(Interconnect)和可编程I/O(Input/Output)实现。

其可编程性使得 FPGA 成为数字滤波器设计与实现的理想平台。

1. FPGA的优势FPGA具有以下几个优势,使得其成为数字滤波器设计与实现的首选平台:灵活性:FPGA可以根据设计需求进行自定义配置,可以通过修改硬件逻辑来满足不同应用场景的需求。

可重构性:FPGA可以重复使用,方便进行修改和优化,减少芯片设计过程中的成本和风险。

高性能:FPGA具有并行处理的能力,可以实现多通道、高速率的实时数据处理,满足对于实时性要求较高的应用场景。

低功耗:FPGA可以进行功耗优化,通过减少冗余逻辑和智能布局布线来降低功耗。

2. 数字滤波器的实现方法基于 FPGA 的数字滤波器的实现方法主要有两种:直接法和间接法。

基于FPGA的FIR数字滤波器设计摘要:文章介绍了CSD编码和流水线技术,将它们运用到VHDL语言编程中,设计了一个16阶8位输入17位输出的线性相位结构FIR数字滤波器,仿真结果符合要求。

最后比较了两种方法的使用在硬件资源和系统处理速度上的优缺点。

有限冲激响应(FIR数字滤波器和无限冲激响应(IIR数字滤波器广泛应用于数字信号处理系统中。

IIR数字滤波器方便简单,但它相位的非线性,要求采用全通网络进行相位校正,且稳定性难以保障。

FIR滤波器具有很好的线性相位特性,使得它越来越受到广泛的重视。

This article introduces CSD coding and production line technique, will they use to VHDL language programming, design of a 16th order 8-bit input 17 output of linear phase FIR digital filters, structural simulation results accord with the requirement. Last two methods were compared, the use of the system hardware resources and processing speed on the advantages and disadvantages. Finite impulse response (FIR digital filters and infinite impulse response (IIR digital filters widely used in digital signal processing system. IIR digital filter convenience simple, but it phase of the nonlinear requirements adopts full ventilation network phase calibration, and stability difficulty safeguards. FIR filters have very good linear phase characteristic, making it more and more extensive attention.关键词:FIR数字滤波器;线性相位;CSD编码;流水线技术1.引言数字滤波在图像处理、语音识别和模式识别等数字信号处理中占有重要地位。

332023年4月上 第07期 总第403期信息技术与应用China Science & Technology Overview进行相乘后,再积分运算,去除时间无关的干扰信号,获I/O 资源,含一个LTC 1407A 模数转换器和一个收稿日期:2022-10-10作者简介:周钧(1987—),男,壮族,广西南宁人,硕士研究生,工程师、硬件设计师,研究方向:FPGA、网络通信。

基于FPGA 的数字滤波器设计周 钧 樊 闯(中车大连电力牵引研发中心有限公司,辽宁大连 116000)摘 要:本文主要对一种基于FPGA 技术的数字锁相滤波器的设计。

结合Xilinx 开发平台,根据噪声信号非时间相干特性进行数字滤波器设计,在SPARTAN-3E 硬件板上完成了硬件协同仿真测试,同时给出测试结果。

测试结果表明,该数滤波器的消除噪声满足技术要求。

关键词:FPGA ;非时间相干特性;数字滤波图1 数字滤波设计原理342023年4月上 第07期 总第403期信息技术与应用China Science & Technology Overview示器。

示波器Tektronix TPS 2024:带宽为200MHz,最高取样速率:2.0GS/s,具有4个通道。

信号发生器HM-8030:频率50MHz 至10MHz,具备高纯度和幅度稳定性。

3.基于FPGA 的数字滤波器设计3.1 设计框架FPGA 设计框架如图2所示。

块,滤波模块和LCD 显示模块这些二级模块组成;(5)各二级模块根据功能划分,将各自功能用VHDL 进行编码设计。

二级模块经过仿真实现,在顶层模块进行结合,实现一整套系统功能。

3.3.1 模数转换设计ADC 芯片将采集的模拟信号离散化为单个离散采样值。

再将采样值转为数字值,根据板卡搭载的ADC 芯片[4]simulation 仿真产生的模拟信号可以非常接近,但是始图3 测试验证(a)测试1(b)测试2China Science & Technology Overview信息技术与应用0,4 V(max 0,223 V)(max 0,239 V)(max 0,233 V)(max 0,214 V)(max 0,234 V)352023年4月上 第07期 总第403期。

基于FPGA的数字滤波器设计与实现数字滤波器是信号处理中常用的工具,可以通过滤除不需要的频率成分或者增强需要的频率成分对信号进行处理。

在数字信号处理领域,基于FPGA的数字滤波器设计与实现是一项重要的研究课题。

本文将介绍FPGA数字滤波器的设计原理、实现方法和应用领域。

首先,我们来了解一下FPGA(可编程逻辑门阵列)是什么。

FPGA是一种可重构的硬件平台,它由大量的可编程逻辑门电路构成。

相比于传统的ASIC(专用集成电路)设计,FPGA具有更高的灵活性和可重构性,可以实现多种不同的电路功能。

在数字滤波器设计中,FPGA可以用来实现各种类型的滤波器,如低通滤波器、高通滤波器、带通滤波器和带阻滤波器等。

FPGA数字滤波器的设计通常包括以下几个步骤:1. 规格定义:确定滤波器的工作频率范围、滤波器类型(如FIR滤波器或IIR滤波器)、滤波器阶数和滤波器的性能指标等。

2. 滤波器设计:根据规格定义,选择适合的滤波器结构和滤波器系数设计方法,如窗函数法、频率采样法或者最小二乘法等。

设计好的滤波器可以通过MATLAB等工具进行模拟验证。

3. 滤波器实现:将滤波器设计转化为可在FPGA上实现的硬件描述语言(如VHDL或Verilog)。

在这个步骤中,需要将滤波器结构转化为逻辑电路,并根据具体的FPGA平台选择适合的资源分配和布局策略。

4. 仿真验证:使用EDA(电子设计自动化)工具对滤波器进行仿真验证,确保其在FPGA上的功能和性能与设计规格一致。

5. 实际实现:将经过仿真验证的滤波器设计烧录到FPGA 芯片中,并进行实际的性能测试。

测试结果可以与仿真结果进行比较,来评估滤波器的实现质量。

FPGA数字滤波器的设计和实现具有以下几个优势:1. 高性能:FPGA提供了大量的逻辑资源和高速IO接口,可以实现复杂的滤波器结构和算法,并能够处理高速数据流。

2. 低功耗:相比于通用处理器,FPGA的功耗较低,可以在不牺牲性能的情况下降低系统的功耗。

基于fpga的滤波器设计与实现基于FPGA的滤波器设计与实现一、引言滤波器是信号处理中常用的一种工具,它可以通过剔除或增强信号中的特定频率分量来改变信号的特性。

而基于FPGA的滤波器是一种利用可编程逻辑器件FPGA来实现滤波功能的方法。

本文将介绍基于FPGA的滤波器的设计与实现过程。

二、滤波器的基本原理滤波器主要通过改变信号的频谱特征来实现滤波效果。

它可以分为两类:低通滤波器和高通滤波器。

低通滤波器通过剔除高频分量,保留低频分量;高通滤波器则相反,剔除低频分量,保留高频分量。

滤波器的设计需要根据具体的需求选择合适的滤波器类型和参数。

三、基于FPGA的滤波器设计与实现基于FPGA的滤波器设计与实现可以分为以下几个步骤:1. 确定滤波器类型和参数:根据实际需求,选择合适的滤波器类型和参数。

例如,如果需要设计一个低通滤波器,需要确定截止频率和滤波器阶数等参数。

2. 数字滤波器设计:将滤波器的模拟设计转化为数字滤波器的设计。

常见的数字滤波器设计方法有FIR滤波器设计和IIR滤波器设计。

FIR滤波器是一种无反馈的滤波器,具有线性相位特性;IIR滤波器则具有反馈结构,可以实现更高阶的滤波器。

3. 将数字滤波器转化为FPGA可实现的结构:将数字滤波器转化为FPGA可实现的结构,可以采用直接形式实现、级联形式实现或者管线化实现等方法。

其中,直接形式实现是最简单直观的方法,但其硬件资源占用较多;级联形式实现可以减少硬件资源的占用,但增加了延迟;管线化实现则可以兼顾硬件资源和延迟。

4. 使用HDL语言进行FPGA设计:使用HDL语言,如VHDL或Verilog,进行FPGA设计。

根据设计的结构和功能,编写相应的HDL代码。

在编写代码时,需要注意代码的可重用性和可维护性,以便后续的设计和调试。

5. 硬件验证和性能优化:完成HDL代码后,进行FPGA的硬件验证和性能优化。

通过仿真和验证,确保设计的正确性和稳定性。

同时,可以根据实际需求对硬件进行优化,如减小资源占用、降低功耗等。