基于FPGA的滤波器的设计

- 格式:doc

- 大小:406.00 KB

- 文档页数:30

基于FPGA的sinc3结构的数字抽取滤波器基于FPGA的sinc3结构的数字抽取滤波器,今年电子设计大赛D题必用的模块,实测效果非常好,做西格玛-德尔塔ADC必用的滤波器module sinc3(mdata1, mclk1, reset, DATA ,word_clk,mode);input mclk1; /*滤波器工作时钟*/input reset; /*滤波器复位*/input mdata1; /*接收到的待滤波的数据*/input [1:0]mode;output [15:0] DATA; /*滤波完成的数据*/output word_clk;integer location;integer info_file;reg [35:0] ip_data1;reg [35:0] acc1;reg [35:0] acc2;reg [35:0] acc3;reg [35:0] acc3_d1;reg [35:0] acc3_d2;reg [35:0] diff1;reg [35:0] diff2;reg [35:0] diff3;reg [35:0] diff1_d;reg [35:0] diff2_d;reg [15:0] DATA;reg [11:0] word_count;reg word_clk;reg init;/*Perform the Sinc ACTION*/always @ (mdata1)if(mdata1==0)ip_data1 <= 0; /* change from a 0 to a -1 for 2's comp */elseip_data1 <= 1;/*ACCUMULATOR (INTEGRATOR) Perform the accumulation (IIR) at thespeed of the modulator.Z = one sample delayMCLKOUT = modulators conversion bit rate*/always @ (posedge mclk1 or posedge reset)if (reset)begin/*initialize acc registers on reset*/acc1 <= 0;acc2 <= 0;acc3 <= 0;endelsebegin/*perform accumulation process*/acc1 <= acc1 + ip_data1;acc2 <= acc2 + acc1;acc3 <= acc3 + acc2;end/*DECIMATION STAGE (MCLKOUT/ WORD_CLK)*/ always @ (negedge mclk1 or posedge reset)if (reset)。

编号:__________基于FPGA实现FIR数字滤波电路的设计及应用(最新版)编制人:__________________审核人:__________________审批人:__________________编制单位:__________________编制时间:____年____月____日车辆在动态称重时,作用在平台上的力除真实轴重外,还有许多因素产生的干扰力,如:车速、车辆自身谐振、路面激励、轮胎驱动力等,给动态称重实现高测量造成很大困难。

若在消除干扰的过程中采用模拟方法滤波,参数则不能过大,否则将产生过大的延迟导致不能实现实时处理,从而造成滤波后的信号仍然含有相当一部分的噪声。

所以必须采用数字滤波消除干扰。

FIR滤波的原理及实现本文采用FIR数字滤波,其原理如公式1所示。

Y(n)=(1)其中h(k)为系统滤波参数,x(n)为采集的信号,Y (n)为滤波后的输出信号。

FIR滤波器的h(n)0≤n≤N-1H(z)=(2)在本文中N=17。

由于h(n)具有对称性质,即:h(n)=h(N-1-n)(n=0,1,。

..,(N-1)/2)(3)这样就可以把FIR滤波器设计成具有线性相位。

利用这一情况,可以得到的乘法结构,需要(N+1)/2次乘法,仅是级联或并联结构所需次数的一半,因此,实际应用中多采用此方法。

我们选用17点的FIR滤波算法,这样实现 FIR卷积运算需要执行9次乘法和16次加法。

为了实现数据的实时处理,需要在20ms内完成这个卷积运算,如果选用单片机89C51(12M晶振)则无法实现。

所以我们选用了Altera公司的FLEX10K20。

FLEX10K系列是工业界个嵌入式的PLD,采用重复可构造的CMOSSRAM工艺,把连续的快速通道互连与独特的嵌入式阵列结构相结合,同时也结合了众多可编程器件的优点来完成普通门阵列的宏功能。

具有高密度、低成本、低功率等特点。

图1硬件结构框图硬件设计由于我们选用的AD1674芯片转换时间为10ms,而所设计的电路每隔20ms启动转换,所以有足够的时间完成模数转换。

基于FPGA的数字滤波器设计院系:信息科学与工程学院专业班:通信工程1102班姓名:李羚学号:20111181082指导教师:周忠强王军舰2015年5月基于FPGA的FIR数字滤波器设计摘要随着公元的第二十一个世纪的到来,今天我们进入了一个科技日新月异的时代。

在现代电子数字系统中,滤波器都以一个不可缺少的身份出现。

其中,FIR数字滤波器又以其良好的线性特性被广泛和有针对性的大量使用。

众所周知,灵活性和实时性是工程实践中对数字信号处理的基本要求。

在以往使用的各种滤波器技术中,不难发现有许许多多的问题。

但是,随着现代计算机技术在滤波问题上的飞跃,派生出一个全新的分支——数字滤波器。

利用可编程逻辑器件和EDA技术,使用FPGA来实现FIR 滤波器,可以同时兼顾实时性和灵活性。

基于FPGA的FIR数字滤波器的研究势在必行。

本论文讨论基于FPGA的FIR数字滤波器设计,针对该毕业设计要做的基本工作有如下几点:(一)掌握有限冲击响应FIR(Finite Impulse Response,FIR)的基本结构,研究现有的实现方法。

对各种方案和步骤进行比较和论证分析,然后针对目前FIR数字滤波器需要的特点,速度快和硬件规模小,作为指导思想进行设计计算。

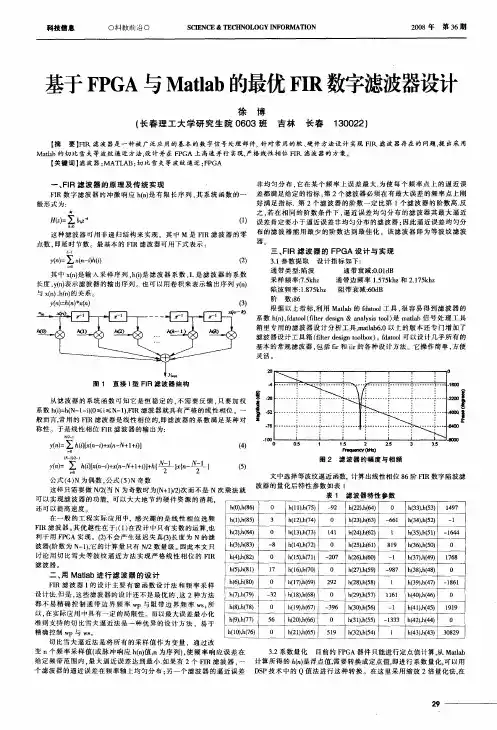

(二)基于硬件FPGA的特点,利用Matlab软件以及窗函数法设计滤波器。

对整个FPGA 元件,计划采用模块化、层次化设计思想,从而对各个部分功能进行更为详细的理解和分工设计。

最终FIR数字滤波器的设计语言选择VHDL硬件编程语言。

(三)设计中的软件仿真使用Altera公司的综合性PLD开发软件Quartus II,并且利用Matlab工具进行对比仿真,在仿真的过程中,对比证明,本论文设计的滤波器的技术指标已经全部达标。

关键词:数字滤波器Matlab 可编程逻辑元件模块化算法Based On FPGA Design Of FIR Digital FiltersMajor:Electronic And Information Engineering Department(Information Engineering)Student: YangChengjie Supervisor:FengLiuAbstractAs we have entered the twenty first century,our technology is changing continuously with the times. In the modern electronic digital systems,filters are indispensable. Among them,the FIR digital filters are widely used with the excellent linear characteristic. As is well-known to us all,flexibility and real-time quality are the basic requirements in digital signal processing of engineering practice. Since we have used a variety of filter technology in the past,it is not difficult for us to find many problems in it. Moreover,with the development of modern computer technology in filter,a new branch - digital filter has derived. We make use of the programmable logic devices and EDA technology,together with the FPGA to design the FIR filter,which is real-time and flexible. In a nutshell,it is imperative to do the research in the FIR digital filters based on the technology of FPGA. This thesis is focused on the design of the FIR digital filters based on the technology of FPGA. Several points are worth mentioning here:(1)To understand and master the basic structure of the limited shock Response FIR (Finite Impulse Response,FIR),research existing realization method,to use various solutions to compare and analyze the steps and demonstrations; then,to do the self design and correction concerning the characteristics of the present FIR digital filters,that is,fast in speed and small scale in hardware.(2) To design FIR filter based on the characteristics of FPGA hardware. In the design process,ready to use of Matlab software and window function method design filter. As far as the whole FPGA components are concerned,we plan to carry on the modularized and hierarchic design,in order to have a more detailed understanding of the function of eachpart and make a division of design. Eventually,FIR digital filters will adopt the VHDL hardware programming language.(3) To adopt the comprehensive PLD development software Quartus II of the Altera company in the design of the software simulation. And we will use of the Matlab tools for the simulation 。

xxx大学本科毕业设计·论文 I 摘 要 自适应滤波器是统计信号处理的一个重要组成部分。在现代滤波处理技术中,自适应滤波器的处理效果尤为突出。在众多滤波器中,特别是在一些对信号处理的实时性要求比较高,体积功耗有严格限制的场合,使用FPGA硬件实现的数字滤波器更为广泛。 本论文从自适应滤波器研究的重要意义入手,介绍了线性自适应滤波器的算法,对几种基于最小均方误差准则或最小平方误差准则的自适应滤波器算法进行研究,就滤波器的基本原理及设计方法做了简单的介绍,最终设计基于FPGA的LMS算法设计复数自适应滤波器,对设计方法进行叙述,并以VHDL语言编写程序进行仿真测试。

关键词:自适应滤波器;FPGA;自适应算法LMS;有限冲激响应滤波器

xxx大学本科毕业设计·论文

II FPGA-based design of adaptive filter Student:TAN xx Teacher:CHEN xx

Abstract:Adaptive filter is a statistical signal processing as an important component.

Processing technology in the modern filter, the adaptive filter, particularly in the treatment effect. Among the filters, especially in some of the real-time signal processing requirements of higher power, there are strict restrictions on the size of the occasion, the use of FPGA hardware to achieve a wider range of digital filters. In this paper, adaptive filter from the importance of research to start to introduce the linear adaptive filter algorithm, based on several criteria MMSE or least square error criteria for the study of adaptive filter algorithm, it filters The basic principle and design method of a brief introduction, the final design of FPGA-based design of complex LMS adaptive filter algorithm, the design methods described, and VHDL languages in maxplus simulation test platform.

Keywords: adaptive filter;FPGA;LMS adaptive algorithm;finite impulse response filter xxx大学本科毕业设计·论文

III 目 录 摘 要 ................................................................................................................................... I 1 绪论 .................................................................................................................................. 1 1.1 引 言 ....................................................................................................................... 1 2 自适应算法研究及分析 ................................................................................................... 1 2.1 自适应滤波基本概念 ............................................................................................. 1 2.2 变步长自适应滤波算法 ......................................................................................... 2 2.3 仿射投影算法 ......................................................................................................... 3 2.4 RLS自适应滤波算法 .............................................................................................. 3 2.5 LMS算法及其推广 ................................................................................................. 3 2.6小结.......................................................................................................................... 6 3 滤波器原理介绍............................................................................................................... 7 3.1 自适应滤波器原理 ................................................................................................. 7 3.2 本文滤波器的工作原理 ......................................................................................... 8 4 基于FPGA的自适应滤波器的设计 ............................................................................ 11 4.1 基本设计方法 ....................................................................................................... 11 4.2 设计流程 ............................................................................................................... 12 4.2.1 设计准备 ....................................................................................................................... 13 4.2.2 设计输入 ....................................................................................................................... 13 4.2.3 功能仿真 ....................................................................................................................... 14 4.2.4 设计处理 ....................................................................................................................... 14 4.2.5 时序仿真 ....................................................................................................................... 14 4.2.6 器件编程测试 ............................................................................................................... 14 4.3 自适应滤波器设计 ............................................................................................... 15 4.3.1 自适应滤波器结构 ....................................................................................................... 16 4.3.2 复数滤波器设计与实现 ............................................................................................... 18 4.3.3 基本设计准备 ............................................................................................................... 19 4.3.4 复数自适应滤波器设计防真 ....................................................................................... 22 4.4小结........................................................................................................................ 24 5 结论 ................................................................................................................................ 25 致 谢 .............................................................................................................................. 26 参考文献 ............................................................................................................................ 27