十进制计数器设计

- 格式:doc

- 大小:644.00 KB

- 文档页数:12

同步和异步十进制加法计数器的设计全文共四篇示例,供读者参考第一篇示例:同步和异步是计算机系统中常用的两种通信机制,它们在十进制加法计数器设计中起到了至关重要的作用。

在这篇文章中,我们将深入探讨同步和异步十进制加法计数器的设计原理及应用。

让我们来了解一下十进制加法计数器的基本概念。

十进制加法计数器是一种用于执行十进制数字相加的数字电路。

它通常包含多个十进制加法器单元,每个单元用于对应一个十进制数位的运算。

在进行加法操作时,每个数位上的数字相加后,可能会产生进位,这就需要进位传递的机制来满足计数器的正确操作。

在同步十进制加法计数器中,每个十进制加法器单元都与一个时钟信号同步,所有的操作都按照时钟信号的节拍来进行。

具体来说,当一个数位的加法计算完成后,会将结果通过进位端口传递给下一个数位的加法器单元,这样就能确保每个数位的计算都是按照特定的顺序来进行的。

同步十进制加法计数器的设计较为简单,在时序控制方面有很好的可控性,但由于需要受限于时钟信号的频率,其速度受到了一定的限制。

在实际应用中,根据不同的需求可以选择同步或异步十进制加法计数器。

如果对计数器的速度要求较高,并且能够承受一定的设计复杂度,那么可以选择异步设计。

如果对计数器的稳定性和可控性要求较高,而速度不是首要考虑因素,那么同步设计可能更为适合。

无论是同步还是异步,十进制加法计数器的设计都需要考虑诸多因素,如延迟、数据传输、进位控制等。

通过合理的设计和优化,可以实现一个高性能和稳定的十进制加法计数器,在数字电路、计算机硬件等领域中有着广泛的应用。

同步和异步十进制加法计数器的设计都有其各自的优势和劣势,需要根据具体的需求来选择合适的设计方案。

通过不断的研究和实践,我们可以进一步完善十进制加法计数器的设计,为计算机系统的性能提升和应用拓展做出贡献。

希望这篇文章能够为大家提供一些启发和帮助,让我们共同探索数字电路设计的奥秘,开拓计算机科学的新境界。

第二篇示例:同步和异步计数器都是数字电路中常见的设计,用于实现特定的计数功能。

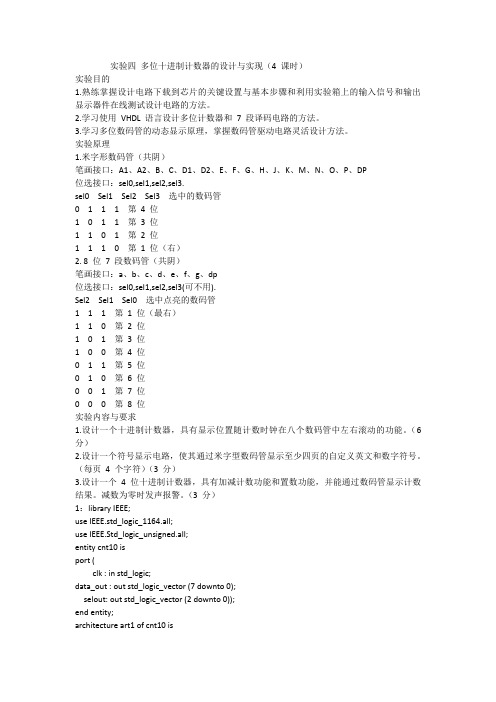

实验四多位十进制计数器的设计与实现(4 课时)实验目的1.熟练掌握设计电路下载到芯片的关键设置与基本步骤和利用实验箱上的输入信号和输出显示器件在线测试设计电路的方法。

2.学习使用VHDL 语言设计多位计数器和7 段译码电路的方法。

3.学习多位数码管的动态显示原理,掌握数码管驱动电路灵活设计方法。

实验原理1.米字形数码管(共阴)笔画接口:A1、A2、B、C、D1、D2、E、F、G、H、J、K、M、N、O、P、DP位选接口:sel0,sel1,sel2,sel3.sel0 Sel1 Sel2 Sel3 选中的数码管0 1 1 1 第4 位1 0 1 1 第3 位1 1 0 1 第2 位1 1 1 0 第1 位(右)2. 8 位7 段数码管(共阴)笔画接口:a、b、c、d、e、f、g、dp位选接口:sel0,sel1,sel2,sel3(可不用).Sel2 Sel1 Sel0 选中点亮的数码管1 1 1 第1 位(最右)1 1 0 第2 位1 0 1 第3 位1 0 0 第4 位0 1 1 第5 位0 1 0 第6 位0 0 1 第7 位0 0 0 第8 位实验内容与要求1.设计一个十进制计数器,具有显示位置随计数时钟在八个数码管中左右滚动的功能。

(6 分)2.设计一个符号显示电路,使其通过米字型数码管显示至少四页的自定义英文和数字符号。

(每页4 个字符)(3 分)3.设计一个4 位十进制计数器,具有加减计数功能和置数功能,并能通过数码管显示计数结果。

减数为零时发声报警。

(3 分)1:library IEEE;use IEEE.std_logic_1164.all;use IEEE.Std_logic_unsigned.all;entity cnt10 isport (clk : in std_logic;data_out : out std_logic_vector (7 downto 0);selout: out std_logic_vector (2 downto 0));end entity;architecture art1 of cnt10 isbeginprocess(clk)variable cnt1:integer range 0 to 9; beginif clk'event and clk='1' thencnt1:=cnt1+1;if cnt1>9 thencnt1:=0;end if;end if;case cnt1 iswhen 0 => data_out <= "11111100"; -- 0 when 1 => data_out <= "01100000"; -- 1 when 2 => data_out <= "11011010"; -- 2 when 3 => data_out <= "11110010"; -- 3 when 4 => data_out <= "01100110"; -- 4 when 5 => data_out <= "10110110"; -- 5 when 6 => data_out <= "10111110"; -- 6 when 7 => data_out <= "11100000"; -- 7 when 8 => data_out <= "11111100"; -- 8 when 9 => data_out <= "11101110"; -- 9 when others => NULL;end case;end process;process(clk)variable cntsel:integer range 0 to 13; beginif clk'event and clk='1' then cntsel:=cntsel+1;if cntsel>13 thencntsel:=0;end if;end if;case cntsel iswhen 0 => selout <= "111";when 1 => selout <= "110";when 2 => selout <= "101";when 3 => selout <= "100";when 4 => selout <= "011";when 5 => selout <= "010";when 6 => selout <= "001";when 7 => selout <= "000";when 8 => selout <= "001";when 9 => selout <= "010";when others => NULL;end case;end process;end art1;2:Library IEEE;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Entity miguan isport( clk : in std_logic;WX : out std_logic_vector (3 downto 0);DX : out std_logic_vector (15 downto 0)); End entity miguan;Architecture bhv of miguan isType state is(st0,st1,st2,st3);Signal current_state:state :=st0;Signal next_state:state;Signal shu1 : integer range 0 to 3;Signal shu2 : std_logic_vector(13 downto 0); Signal A,B,C,D:std_logic_vector(15 DOWNTO 0); Beginprocess (clk) isBeginIf (clk'event and clk='1') thenshu2<=shu2+"00000000000001";If shu2="11111111111111"thencurrent_state<=NEXT_STATE;elsecurrent_state<=current_state;End if;End if;End process;Process (current_state)BeginCase current_state iswhenst0=>A<="0110101000000000";--xB<="0000000011110000";--lC<="1000010000011110";--dD<="0001000110111011";--sNEXT_STATE<=ST1;whenst1=>A<="0000000011111100";--UB<="1000010000000011";--TC<="0001000111110011";--ED<="0011000111000111";--RNEXT_STATE<=ST2;whenst2=>A<="0000000011111111";--0B<="0001000111111011";--6C<="0000000000001100";--1D<="0001000111111111";--8NEXT_STATE<=st3;whenst3=>A<="0001000111111011";--6B<="1001010110000000";--4C<="0001000110111011";--5D<="0000000000001100";--1NEXT_STATE<=ST0;End case;End process;Process (clk) isBeginif rising_edge(clk) thenif shu1>3 thenshu1<=0;elseshu1<=shu1+1;end if;case shu1 isWHEN 0 =>WX<="1110";DX<=A;WHEN 1 =>WX<="1101";DX<=B;WHEN 2 =>WX<="1011";DX<=C;WHEN 3 =>WX<="0111";DX<=D;End case;End if;End process;End architecture bhv;3:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity wybcount4 isport(count_clk,saopin_clk,en,load,reset,add_sub:in std_logic;data_in3:in std_logic_vector(3 downto 0);--Left1data_in2:in std_logic_vector(3 downto 0);data_in1:in std_logic_vector(3 downto 0);data_in0:in std_logic_vector(3 downto 0);--Right1duanxuan:out std_logic_vector(7 downto 0);--duan xuansel:out std_logic_vector(1 downto 0);--wei xuanbell:out std_logic);end entity wybcount4;architecture beh of wybcount4 isconstant num0:std_logic_vector:="01111110";constant num1:std_logic_vector:="00001100";constant num2:std_logic_vector:="10110110";constant num3:std_logic_vector:="10011110";constant num4:std_logic_vector:="11001100";constant num5:std_logic_vector:="11011010";constant num6:std_logic_vector:="11111010";constant num7:std_logic_vector:="00001110";constant num8:std_logic_vector:="11111110";constant num9:std_logic_vector:="11011110";function number(x:std_logic_vector) return std_logic_vector is begincase x iswhen "0000" => return num0;when "0001" => return num1;when "0010" => return num2;when "0011" => return num3;when "0100" => return num4;when "0101" => return num5;when "0110" => return num6;when "0111" => return num7;when "1000" => return num8;when "1001" => return num9;when others =>return "00000000";end case;end number;signal Q3:std_logic_vector(3 downto 0);--zhong jian zhisignal Q2:std_logic_vector(3 downto 0);signal Q1:std_logic_vector(3 downto 0);signal Q0:std_logic_vector(3 downto 0);beginprocess(count_clk,reset,en,load,add_sub) isbegin--counter10IF reset = '0' THENQ0<=(OTHERS => '0');Q1<=(OTHERS => '0');Q2<=(OTHERS => '0');Q3<=(OTHERS => '0');ELSIF rising_edge(count_clk) THENif en='0' thenif load='0' thenQ0<=data_in0;Q1<=data_in1;Q2<=data_in2;Q3<=data_in3;elsif add_sub='0' then--addQ0<=Q0+1;if Q0>=9 thenQ0<="0000";Q1<=Q1+1;if Q1>=9 thenQ1<="0000";Q2<=Q2+1;if Q2>=9 thenQ2<="0000";Q3<=Q3+1;if Q3>=9 thenQ3<="0000";end if;end if;end if;end if;else--subQ0<=Q0-1;if Q0<=0 thenQ0<="1001";Q1<=Q1-1;if Q1<=0 thenQ1<="1001";Q2<=Q2-1;if Q2<=0 thenQ2<="1001";Q3<=Q3-1;if Q3<=0 thenQ3<="1001";end if;end if;end if;end if;end if;end if;END IF;if (Q0="0000" and Q1="0000" and Q2="0000" and Q3="0000") then bell<='1';elsebell<='0';end if;end process;process(saopin_clk) is--sao pin xian shivariable qq:std_logic_vector(0 to 1);beginif (saopin_clk'event and saopin_clk='1') thenif qq<=3 then qq:=qq+1;else qq:="00";end if;end if;case qq iswhen "00" => sel<="00";duanxuan<=number(Q0);when "01" => sel<="01";duanxuan<=number(Q1);when "10" => sel<="10";duanxuan<=number(Q2);when "11" => sel<="11";duanxuan<=number(Q3);end case;end process;end architecture beh;。

十进制计数器概述十进制计数器是一种可用于计数或记录十进制数字的设备或电路。

它通常由多个计数单元组成,每个计数单元可以表示一个十进制数位。

在计算机科学和电子工程中,计数器是一种基础的组件,用于各种应用,包括计时、频率分频和数据传输等。

在本文中,我们将介绍十进制计数器的基本工作原理、常见的实现方法以及应用场景。

工作原理十进制计数器是基于二进制计数器的改进版本。

二进制计数器由多个触发器组成,每个触发器可以对应一个二进制位,依次表示2的幂次方(从右向左)。

十进制计数器引入了各位进位的概念,允许在每个计数单位溢出之后将进位传递到下一个单位。

这样,每个计数单位表示0-9之间的数字,当计数溢出到9时,进位将传递到下一个单位,当前单位将重置为0。

实现方法二进制计数器的十进制转换一个简单的方法是将二进制计数器的输出转换为十进制。

例如,对于4位二进制计数器,输出为4个二进制位,可以将这4个二进制位转换为0-9之间的十进制数字。

这种方法的主要缺点是需要进行二进制到十进制的转换,速度较慢,并且实现复杂。

BCD(Binary-Coded Decimal)计数器BCD计数器是一种专门为实现十进制计数而设计的计数器。

BCD计数器使用BCD码来表示十进制数字。

BCD码是一种二进制表示方法,将每个十进制数字分别表示为四个二进制位组成的码。

BCD计数器通过改变BCD码来表示不同的十进制数字。

当计数溢出时,BCD计数器将相应的BCD码重置为0,并将进位传递到下一个计数单位。

预设十进制计数器预设十进制计数器是将计数器的初始值预设为一个特定的十进制数字。

该计数器每次计数时按照预设值进行递增或递减。

当计数溢出或下溢时,预设十进制计数器将相应的数值重置为预设值。

预设十进制计数器可以通过硬件设置或者通过编程来实现。

它具有灵活性和可编程性,可以根据需要设置任意的初始值和增量。

应用场景十进制计数器广泛应用于各种计数和记录场景,包括:•时钟和计时器:十进制计数器可以实现时钟和计时器功能,例如用于显示时间、计算时间间隔等。

未知驱动探索,专注成就专业

十进制计数器

十进制计数器是一种用于记录和显示十进制数值的计数器。

它通常由数个数字显示模块组成,每个数字显示模块都可

以显示0到9的数字。

当计数器接收到一个触发信号时,它会将记录的数字加1。

当数字达到9时,它会自动进位,并将下一个数字加1。

例如,当计数器记录的数字为999时,接收到触发信号后,

会将数字变为1000。

十进制计数器广泛应用于各种计数场景,如电子表计、计

时器等。

它可以方便地记录和显示人类习惯使用的十进制

数值,使得计数操作更加直观和易于理解。

1。

十进制计数法教案设计一、教学目标1.让学生理解十进制计数法的概念及特点。

2.培养学生运用十进制计数法进行数数和计算的能力。

3.培养学生合作交流、自主探究的学习习惯。

二、教学重难点重点:理解十进制计数法的概念及特点。

难点:运用十进制计数法进行数数和计算。

三、教学准备1.教具:计数棒、计数器、PPT等。

2.学具:计数棒、计数器、练习本等。

四、教学过程(一)导入1.利用图片或故事引入,让学生对十进制计数法产生兴趣。

2.引导学生思考:我们平时是怎样计数的?为什么这样计数?(二)新课讲解1.讲解十进制计数法的概念及特点。

a.十进制计数法的定义:逢十进一。

b.十进制计数法的表示方法:数字0-9组成,每一位的权值是10的幂次。

c.十进制计数法的优越性:便于计算和表示。

2.讲解十进制计数法的运算规则。

a.加法:逢十进一,退位减十。

b.减法:退位减十,借位加十。

c.乘法:逢十进一,乘积的位值变化。

d.除法:商的位值变化,余数小于除数。

3.结合教具演示,让学生直观地理解十进制计数法的运算过程。

(三)课堂练习1.让学生用计数棒或计数器进行数数练习,巩固十进制计数法的概念。

2.出具一些简单的加减乘除题目,让学生运用十进制计数法进行计算。

(四)拓展延伸1.引导学生思考:除了十进制计数法,还有哪些计数法?它们之间有什么区别和联系?2.介绍其他计数法,如二进制、八进制、十六进制等,让学生了解不同计数法之间的转换。

(五)课堂小结2.强调十进制计数法在实际生活中的应用。

(六)课后作业1.复习十进制计数法的概念、特点及运算规则。

2.完成一些相关的练习题目,巩固所学知识。

五、教学反思本节课通过讲解、演示、练习等多种教学手段,让学生对十进制计数法有了深入的了解。

在教学过程中,要注意关注学生的反应,及时调整教学节奏,确保每位学生都能跟上教学进度。

同时,注重培养学生的合作交流和自主探究能力,提高学生的学习兴趣和积极性。

课后要关注学生的作业完成情况,及时给予反馈,巩固所学知识。

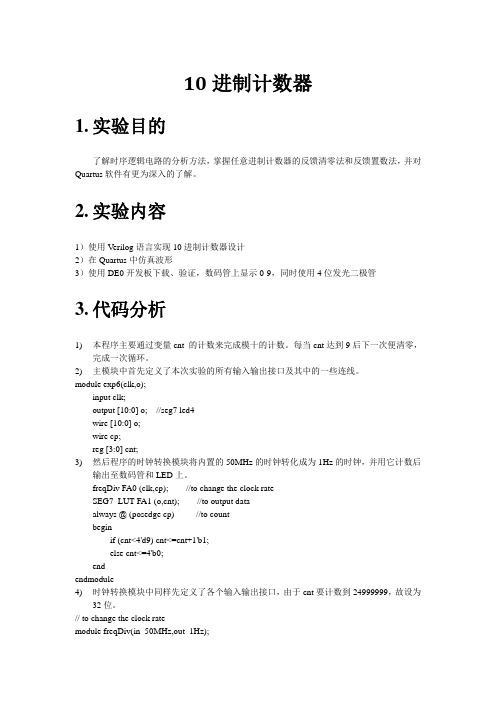

10进制计数器1.实验目的了解时序逻辑电路的分析方法,掌握任意进制计数器的反馈清零法和反馈置数法,并对Quartus软件有更为深入的了解。

2.实验内容1)使用Verilog语言实现10进制计数器设计2)在Quartus中仿真波形3)使用DE0开发板下载、验证,数码管上显示0-9,同时使用4位发光二极管3.代码分析1)本程序主要通过变量cnt 的计数来完成模十的计数。

每当cnt达到9后下一次便清零,完成一次循环。

2)主模块中首先定义了本次实验的所有输入输出接口及其中的一些连线。

module exp6(clk,o);input clk;output [10:0] o; //seg7 led4wire [10:0] o;wire cp;reg [3:0] cnt;3)然后程序的时钟转换模块将内置的50MHz的时钟转化成为1Hz的时钟,并用它计数后输出至数码管和LED上。

freqDiv FA0 (clk,cp); //to change the clock rateSEG7_LUT FA1 (o,cnt); //to output dataalways @ (posedge cp) //to countbeginif (cnt<4'd9) cnt<=cnt+1'b1;else cnt<=4'b0;endendmodule4)时钟转换模块中同样先定义了各个输入输出接口,由于cnt要计数到24999999,故设为32位。

// to change the clock ratemodule freqDiv(in_50MHz,out_1Hz);input in_50MHz;output out_1Hz;reg out_1Hz;reg [31:0]cnt;5)然后通过cnt的计数来转换时钟频率:always@(posedge in_50MHz)beginif(cnt < 32'd2*******)begincnt <= cnt + 1'B1;endelsebegincnt <= 32'b0;out_1Hz <= ~out_1Hz;endendendmodule6)在输出模块中,先定义了4位的数据输入和7位的数码管输出和4位LED灯输出,并将输出设为寄存器变量。

数电时序电路设计报告(一)实验题目:JK触发器附加必要的门电路设计8421BCD码的十进制计数器。

(二)实验要求:(1)设计要求:用一个译码驱动器74LS48驱动1个LED七段显示器;轮流显示1位十进制数;(2)仿真测试电路的输出(用发光二极管指示)。

(三)实验思路:8421BCD码是四位编码方式,而一个JK触发器只能储存一位二进制代码,所以要用四个JK触发器才能构成一个十进制计数器,再在四个输出端接一个74LS48译码器,就能满足题目的要求。

(四)设计步骤(1)由设计要求画出真值表Q3n Q2n Q1n Q0n Q3n+1 Q2n+1 Q1n+1 Q0n+10 0 0 00 0 0 10 0 0 10 0 1 00 0 1 00 0 1 10 0 1 10 1 0 00 1 0 00 1 0 00 1 0 10 1 0 10 1 1 00 1 1 00 1 1 10 1 1 11 0 0 0 1 0 0 01 0 0 10 0 0 0(2)由真值表画出卡诺图,并化简卡诺图Q3n+1 00X100X001X X00X XQ2n+101X001X010X X01X XQ1n+100X011X000X X11X XQ0n+111X100X000X X11X X与触发器的特征方程进行对比得,J0=K0=1;J1= Q0n·Q3n’(即Q3n非), K1=Q0n;J2=K2=Q1n·Q0n; J3= Q2n·Q1n·Q0n, K3=Q0n.(3)采用Quartus II 7.2软件画出设计电路图(4)对设计电路图进行仿真测试(5)参照型号EP2C5T144C8可编程芯片的实验板情况下,给设计好的原理图配置芯片引脚,并重新输出电路图。

则此时该实验电路设计已完成,连接实验板,下载设计好的文件,则可进行测试。

(四)设计电路图初始原理图仿真结果图配置好芯片引脚后的实验原理电路图:(一)心得体会1、在用Quartus II 7.2软件设计电路图时,会发现器件在纸上画的电路图略有不同,因此需要把他们进行一一对应。

十进制计数教案6篇十进制计数教案篇1教学目标1.使学生知道数的产生.2.认识亿级的数,掌握计数单位亿、十亿、百亿、千亿及千亿内的数位顺序表和,会根据数级正确地读千亿以内的数.教学重点掌握数位顺序表及多位数的读法和应用.教学难点读法应用及数中零的读法.教学步骤一、铺垫孕伏.谈话导入:同学们,我们已经学习了三年多数学,每天都要和数打交道,那么你们知道数是怎样产生的吗?b、十亿、百亿、千亿也叫计数单位.我们共学了哪些计数单位?c、从刚才一边拨珠,一边数数的过程中,谁发现了每相邻两个计数单位之间有什么关系?教师明确:a、比千亿大的计数单位,因不常用,暂时不学,所以在千亿的左面用表示(板书:)b、每相邻的两个计数单位之间的进率都是十的计数方法,叫做.(三)认识数位和数位顺序表.1.我们知道了什么叫,要把一个数写出来,就要用到数字,教师提问:我们学过哪些数字?(1、2.3、4、5、6、7、8、9.0)教师说明:这些数字叫阿拉伯数字.教师强调:写数的时候,把计数单位按一定的顺序排列起来,它们所占的位置叫做数位.一个数字所在的数位不同,表示的大小也不同.2.观察数位顺序表.教师提问:亿以内的数位顺序是怎样的?(强化右起第五位是万位,第九位是亿位.)千万位百万位十万位万位千位百位十位个位3.数位分级(学生自学)自学题目:从右边起几个数位为一级,各是什么数级?个级、万级、亿级有什么异同点?(四)教学亿级的读法.1.下面的数该怎样读呢?(回忆读亿以内数的方法.)教师板书:50000 106000 400305002.在上面三个数后各加4个0,变成例1.(1)学生试读、互相读、小组讨论读.(2)引导学生总结多位数的读法法则.学生讨论:含有亿级、万级和个级的数,按什么顺序来读?怎样读亿级、万级的数?什么位置的0不读?什么位置的读,读几个?学生总结法则:(1)从高位起,一级一级地往下读;(2)读亿级或万级的数时,要按照个级的数的读法来读,再在后面加上亿字或万字;(3)每级末尾的0都不读,其他数位有一个0或连续有几个0都只读一个零.三、巩固练习.1.填空.(1)从右起第9位是位.(2)十个一亿是亿.(3)10个一百亿是亿.(4)、、、是亿级,万级有、、、.2.判断.(1)两个计数单位间的进率是10.(2)308040000000读作三千八十亿四千万.3.读出下面每组数.(1)65 650000 65 0000 0000(2)4070 4070 0000 4070 0000 0000四、课堂小结.引导学生总结,正确读多位数的法则.五、布置作业.读出下面横线上的数.1.到20__年第五次全国人口普查为止,我国总人口达到1295330000人2.1999年全国有小学生135479600人3.地球和太阳的平均距离是149500000千米六、板书设计.1、数的产生2、相邻两个计数单位间的进率都是10.十进制计数教案篇2教学内容:课本16---18页的内容教学目标1、了解数的产生,理解自然数的概念和特点。

实验一十进制计数器的设计一、实验目的:通过设计实现四种频率可选的十进制计数器,实现输出顺序为:0,2,5,6,1,9,4,8,7,3,0(并可预置,可使能,带有七段译码显示),以熟悉VHDL语言编程。

二、实验原理与设计思路:系统整体由分频器、多路选择器、计数器和共阴极七段LED数码管译码器四个原件组成。

输入信号有个,分别为复位信号rst(高有效)、时钟clk(提供整个系统的时钟信号)、选择器输入Sel(选择不同的频率输入)、置位信号load(高有效)和置位输入信号state(3 downto 0)。

输出引脚有8根,分别为现态state_1(3 downto 0)和次态state_2(3 downto 0)的计数。

(注意:仿真结果使用16进制显示该两个输出信号的值)。

分频器模块设计:可选用计数器模块实现,如下所示:if (rst='1')thencount<="0000";elsif(clk'event and clk='1')thencount<=count+1;end if;clk1<=count(0);clk2<=count(1);clk4<=count(2);clk8<=count(3);多路选择器模块设计:可以考虑使用选择语句来实现:case sel iswhen "00"=>clock<=clk1;when "01"=>clock<=clk2;when "10"=>clock<=clk4;when "11"=>clock<=clk8;when others =>null;end case;计数器模块的实现:在本设计中总共要设计两个计数器分别用于实现现态state_1(3 downto 0)和次态state_2(3 downto 0)的计数再考虑复位置位信号,可用以下语句实现:if(rst='1')thenstate_1<="0000";elsif(load='1')thenstate_1<=state;elsif(clock'event and clock='1')thenstate_1 <= state_2;end if;case state_1 iswhen"0000"=>state_2<="0010";when "0010"=>state_2<="0101";when "0101"=>state_2<="0110";when "0110"=>state_2<="0001";when "0001"=>state_2<="1001";when "1001"=>state_2<="0100";when"0100"=>state_2<="1000";when"1000"=>state_2<="0111";when"0111"=>state_2<="0011";when"0011"=>state_2<="0000";when others =>null;end case;共阴极七段LED数码管译码器case state_1 iswhen "0000"=>segs<="1111110";when "0001"=>segs<="0110000";when "0010"=>segs<="1101101";when "0011"=>segs<="1111001";when "0100"=>segs<="0110011";when "0101"=>segs<="1011011";when "0110"=>segs<="1011111";when "0111"=>segs<="1110000";when "1000"=>segs<="1111111";when "1001"=>segs<="1111011";when others=>segs<="0000000";end case;三、实验代码综上,可得实验完整代码如下:LIBRARY ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;useieee.std_logic_unsigned.all;ENTITY ddd ISP ORT(clk,rst : IN STD_LOGIC;sel : IN STD_LOGIC_VECTOR(1 DOWNTO 0);state : in std_logic_vector(3 downto 0);load : in std_logic;segs : OUT STD_LOGIC_vector(6 downto 0));END ddd;ARCHITECTURE behav OF ddd ISS IGNAL count : STD_LOGIC_vector(3 downto 0);s ignal clk1: std_logic;s ignal clk2: std_logic;s ignal clk4: std_logic;s ignal clk8: std_logic;s ignal clock: std_logic;s ignal state_1 : std_logic_vector(3 downto 0);s ignal state_2 : std_logic_vector(3 downto 0);BEGINp rocess(rst,clk,clk1,clk2,clk 4,clk8)b eginif (rst='1')thencount<="0000";elsif(clk'event and clk='1')thencount<=count+1;end if;clk1<=count(0);clk2<=count(1);clk4<=count(2);clk8<=count(3);e nd process;p rocess(sel,clk1,clk2,clk4,cl k8)b egincase sel iswhen"00"=>clock<=clk1;when"01"=>clock<=clk2;when"10"=>clock<=clk4;when"11"=>clock<=clk8;when others =>null;end case;e nd process;p rocess(clock,rst,load)b eginif(rst='1')thenstate_1<="0000";elsif(load='1')thenstate_1<=state;elsif(clock'event and clock='1')thenstate_1 <= state_2;end if;e nd process;p rocess(state_1)b egincase state_1 iswhen"0000"=>state_2<="0010";when"0010"=>state_2<="0101";when"0101"=>state_2<="0110";when"0110"=>state_2<="0001";when"0001"=>state_2<="1001";when"1001"=>state_2<="0100";when"0100"=>state_2<="1000";when"1000"=>state_2<="0111";when"0111"=>state_2<="0011";when"0011"=>state_2<="0000";when others =>null;end case;e nd process;p rocess(state_1)b egincase state_1 iswhen"0000"=>segs<="1111110";when"0001"=>segs<="0110000";when"0010"=>segs<="1101101";when"0011"=>segs<="1111001";when"0100"=>segs<="0110011";when"0101"=>segs<="1011011";when"0110"=>segs<="1011111";when "0111"=>segs<="1110000";when "1000"=>segs<="1111111";when "1001"=>segs<="1111011";whenothers=>segs<="0000000";end case;e nd process;END behav;四、实验结果与分析编译结束后得编译报告如下:由编译报告得,实验硬件耗用23/5980(<1%),占用管脚16/185(9%),逻辑设计较好,布线合理。

十进制计数器设计-CAL-FENGHAI-(2020YEAR-YICAI)_JINGBIAN

十进制计数器设计

一、实验目的:熟悉Quartus II的Verilog文本设计流程全过程,学习十进制计数器的设计、仿真,掌握计数器的工作原理。

二、实验原理:计数器属于时序电路的范畴,其应用十分普遍。

该程序设计是要实现带有异步复位、同步计数使能和可预置型的十进制计数器。

该计数器具有5个输入端口(CLK、RST、EN、LOAD、DATA)。

CLK输入时钟信号;RST起异步复位作用,RST=0,复位;EN是时钟使能,EN=1,允许加载或计数;LOAD 是数据加载控制,LOAD=0,向内部寄存器加载数据;DATA是4位并行加载的数据。

有两个输出端口(DOUT和COUT)。

DOUT的位宽为4,输出计数值,从0到9;COUT是输出进位标志,位宽为1,每当DOUT为9时输出一个高电平脉冲。

RST在任意时刻有效时,如CLK非上升沿时,计数也能即刻清0;当EN=1,且在时钟CLK的上升沿时刻LOAD=0,4位输入数据DATA被加载,但如果此时时钟没有上升沿,尽管出现了加载信号LOAD=0,依然未出现加载情况;当EN=1,RST=1,LOAD=1时,计数正常进行,在计数数据等于9时进行输出高电平。

三、实验任务:在Quartus II上将设计好的程序进行编辑、编译、综合、适配、仿真,从时序仿真图中学习计数器工作原理,了解计数器的运行情况及时钟输入至计数器数据输出的延时情况。

四、实验步骤:

(一)、建立工作库文件和编辑设计文件

任何一项设计都是一项Project(工程),而把一个工程下的所有文件放在一个文件夹内是一个非常好的习惯,以便于我们整理,利用和提取不同工程下的文件,而此文件夹将被EDA软件默认为Work Library(工作库),所以第一步先根据自己的习惯,建立个新的文件夹。

(1)新建文件夹:在盘建立并保存工程,将文件夹取名Jishuqi。

(2)输入源程序:打开Quartus II,选择菜单File New Design

Files VerilogHDL File OK(如图1所示)。

图1

在空白处工作框处输入任务要求中的代码,代码如下:

module CNT10 (CLK,RST,EN,LOAD,COUT,DOUT,DATA);

input CLK, EN, RST,LOAD;

input [3:0] DATA;

output [3:0] DOUT;

output COUT;

reg [3:0] Q1;

reg COUT;

assign DOUT = Q1;

always @ (posedge CLK or negedge RST)begin

if(!RST) Q1 <= 0;

else if(EN)begin

if(!LOAD) Q1 <= DATA;

else if(Q1<9) Q1 <= Q1+1;

else Q1 <= 4'b0000;end

end

always @ (Q1)

if(Q1==4'h9) COUT = 1'b1;

else COUT = 1'b0;

endmodule

(3)保存文件:选择File Save as,选择保存路径,即刚才新建文件夹Jishuqi,文件名应与实体名保持一致,即CNT10,点击保存后会跳出“Do you want to create a new project with this file”选择“是”,则进入如下界面,如图2所示。

图2

点击Next,进入“工程设置”对话框,第一行表示工程所在的文件夹,第二行为工程名,可以与顶层文件的实体名保持一致,也可以另取别的名字,第三行为当前工程顶层文件的实体名,如图3所示。

图3

点击Next,进入ADD FILE对话框,单击Add All 按钮,将工程相关的所有Verilog文件加进工程,也可以单击“Add...”选择性加入,从工程目录中选出相关的Verilog文件,然后点击Next,当先直接建立工程时,需要自己添加,如图4所示。

图4

(4)选择目标芯片:我们选用的是CycloneIII系列的EP3C55F484C8,在Family 栏选择芯片系列——CycloneIII,在窗口右边的三个下拉列表框选择过滤条件,分别选择Package为FBGA、Pin count为484和Speed grade为8,点击Next,如图5所示。

图5

(5)工具设置:进入EDA工具设置窗口,有三个选项,分别是选择输入的HDL 类型和综合工具、选择仿真工具、选择时序分析工具,这是除Quartus II自含的所有设计工具以外的外加的工具,如果不作选择的,表示仅选择Quartus II自含的所有设计工具,本次不需要其他的设计工具,可以直接点击Next,如图6所示。

图6

(6)结束设置:进入“工程设置统计”窗口,列出了与此工程相关的设置情况,设置完成,点击Finish,如图7所示。

图7

(二)、编译

配置好后就可以进行编译了,点击Processing Start Compilation命令,启动全程编译

编译成功后的界面如图8所示。

图8

(三)、时序仿真

(1)打开波形编辑器:File New Verification/Debugging Files Vector Waveform OK,即出现空白的波形编辑器,如图9所示。

图9

(2)设置仿真时间区域:Edit-->End Time在Time栏中输入50,单位选择“us”,点击确定并保存波形文件,如图10所示。

图10

(3)点击Edit Insert Insert Node or Bus Node Finder List >>OK,如图11所示。

图11

(4)编辑输入波形:

首先进行时钟窗口设置:点击左边的输入CLK的周期为,50%的占空比,如图12所示,设置EN、RST与LOAD,将它们设置为高电平。

图12

接着进行总线数据格式设置和参数设置:点击输入数据信号DATA的左边的+号,能展开此总线中的所有信号;如果双击此+号左边的信号标记,将弹出对该信号数据格式设置的Node Properties对话框,在该对话框的Radix下拉列表中有四种选择,这里选择十进制表达方式。

其次输入波形数据:由于DATA是4位待加载的输入数据,需要设置输入数据。

用鼠标在所示信号名DATA的某一数据区拖拉出来一块蓝色区域,然后单

击左侧工具栏的按钮,在弹出窗口输入数据如1,继而在不同区域设置不同数据。

这里为方便观察,输入的数据依次是1,5,7,9,4,如图13所示。

图13

(5)仿真

仿真器参数仿真:选择Assignment Settings命令,在Settings窗口下选择Category Simulator Settings。

在右侧的Simulation mode下拉列表中选择Timing,即选择时序仿真,并选择仿真激励文件名。

选择Simulation Period栏,确认选中了“Run simulation until all vector stimuli are used”,如图14所示。

图14

启动仿真器:Processing Start Simulation,直至出现Simulation was successful,仿真结束,然后会自动弹出“Simulation Report”,点击输出信号“DOUT”旁边的“+”,展开总线中的所有信号,可以便于我们观察和分析波形,如图15所示。

图15

(四)应用RTL电路图观察器

Tools Netlist Viewers RTL Viewer,结果如图16所示。

图16

五、实验心得

通过几周的学习,我了解了FPGA编程语言的使用方法,通过设计实验项目,我掌握了Quartus II软件的用法以及十进制计数器的工作原理。

在这个过程中,让我明白了动手能力的重要性,同时也使我认识到自己所学的知识还很欠缺,要加强这方面的学习。