电子技术基础 数字部分 第六版 康华光第 章逻辑门电路共 节

- 格式:ppt

- 大小:2.97 MB

- 文档页数:96

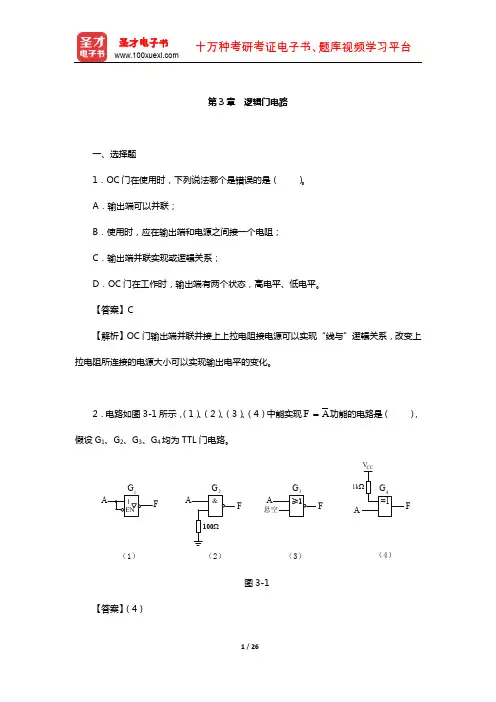

第3章 逻辑门电路一、选择题1.OC 门在使用时,下列说法哪个是错误的是( )。

A .输出端可以并联;B .使用时,应在输出端和电源之间接一个电阻;C .输出端并联实现或逻辑关系;D .OC 门在工作时,输出端有两个状态,高电平、低电平。

【答案】C【解析】OC 门输出端并联并接上上拉电阻接电源可以实现“线与”逻辑关系,改变上拉电阻所连接的电源大小可以实现输出电平的变化。

2.电路如图3-1所示,(1)、(2)、(3)、(4)中能实现A F =功能的电路是( ),假设G 1、G 2、G 3、G 4均为TTL 门电路。

1kG FG FFA(1)(2)(3)(4)图3-1【答案】(4)【解析】(1)中具有使能端,当A =0时,该门电路不工作,没有输出;(2)中的门电路由于是与非门,其中的一个输入端连低电阻再连地是低电平输入,F 总是输出高电平;(3)TTL 门电路悬空的时候表示高电平,或非门始终输出0;(4)中门电路表示异或,其中一个接电阻连高电平,逻辑不发生变化还是逻辑1,。

3.已知74系列TTL 集成电路的静态参数如下:I IH =20μA,I IL =-1.0mA ,I OH =-0.4mA ,I OL =16mA 下列说法正确的是( )A .高电平扇出系数:20B .低电平扇出系数:16C .扇出系数:16D .扇出系数:20 【答案】ABC【解析】高电平扇出系数=20OH IHI I =;低电平扇出系数=16OL IL II =;扇出系数为两者中的小值。

4.可以将输出端直接并联实现“线与”逻辑的门电路是( )。

A .三态输出的门电路; B .推拉式输出结构的TTL 门电路 C .集电极开路输出的TTL 门电路: D .互补输出结构的CMOS 门电路 【答案】A【解析】BC 两项,一般TTL 门输出端并不能直接并联使用,否则这些门的输出管之间由于低阻抗形成很大的短路电流(灌电流),而烧坏器件。

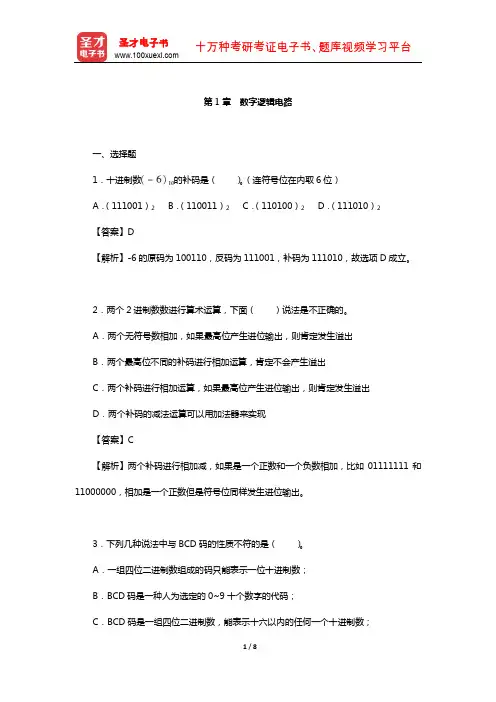

第1章数字逻辑电路一、选择题1.十进制数的补码是()。

(连符号位在内取6位)A.(111001)2B.(110011)2C.(110100)2D.(111010)2【答案】D【解析】-6的原码为100110,反码为111001,补码为111010,故选项D成立。

2.两个2进制数数进行算术运算,下面()说法是不正确的。

A.两个无符号数相加,如果最高位产生进位输出,则肯定发生溢出B.两个最高位不同的补码进行相加运算,肯定不会产生溢出C.两个补码进行相加运算,如果最高位产生进位输出,则肯定发生溢出D.两个补码的减法运算可以用加法器来实现【答案】C【解析】两个补码进行相加减,如果是一个正数和一个负数相加,比如01111111和11000000,相加是一个正数但是符号位同样发生进位输出。

3.下列几种说法中与BCD码的性质不符的是()。

A.一组四位二进制数组成的码只能表示一位十进制数;B.BCD码是一种人为选定的0~9十个数字的代码;C.BCD码是一组四位二进制数,能表示十六以内的任何一个十进制数;D.BCD码有多种。

【答案】C【解析】BCD码只能表示一个十位数,其他数的组合表示的数实际上是无效的,10~16一定不可能被一个四位的BCD码表示出来。

4.以下代码中为无权码的为()。

A.8421BCD码B.5421BCD码C.余三码D.格雷码【答案】CD【解析】位权:在某一进位制的数中,每一位的大小都对应着该位上的数码乘上一个固定的数,这个固定的数就是这一位的权数,权数是一个幂。

明显AB每位上表示某一个数值,CD只是为了方便设定的编码。

二、填空题1.【答案】00010100【解析】2.已知8位二进制数码为10100101,则相应的格雷码为()。

【答案】11110111【解析】二进制转化为格雷码的规则:从最右边的位开始,每位与其左边相邻的位异或,所得结果作为该位的值,最左边位的值不变。

3.X对应的原码为111010,则2X对应的8位原码为(),X/2对应的8位补码形式为()。

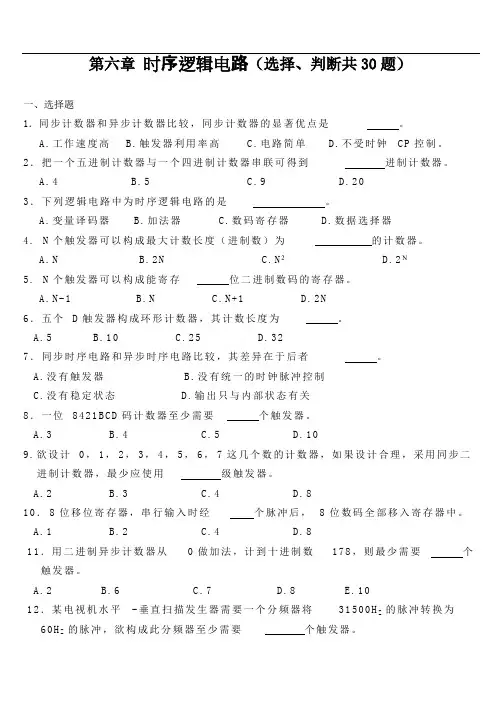

第六章时序逻辑电路(选择、判断共30题)一、选择题1.同步计数器和异步计数器比较,同步计数器的显著优点是。

A.工作速度高B.触发器利用率高C.电路简单D.不受时钟C P控制。

2.把一个五进制计数器与一个四进制计数器串联可得到进制计数器。

A.4B.5C.9D.203.下列逻辑电路中为时序逻辑电路的是。

A.变量译码器B.加法器C.数码寄存器D.数据选择器4.N个触发器可以构成最大计数长度(进制数)为的计数器。

A.NB.2NC.N2D.2N5.N个触发器可以构成能寄存位二进制数码的寄存器。

A.N-1B.NC.N+1D.2N6.五个D触发器构成环形计数器,其计数长度为。

A.5B.10C.25D.327.同步时序电路和异步时序电路比较,其差异在于后者。

A.没有触发器B.没有统一的时钟脉冲控制C.没有稳定状态D.输出只与内部状态有关8.一位8421B C D码计数器至少需要个触发器。

A.3B.4C.5D.109.欲设计0,1,2,3,4,5,6,7这几个数的计数器,如果设计合理,采用同步二进制计数器,最少应使用级触发器。

A.2B.3C.4D.810.8位移位寄存器,串行输入时经个脉冲后,8位数码全部移入寄存器中。

A.1B.2C.4D.811.用二进制异步计数器从0做加法,计到十进制数178,则最少需要个触发器。

A.2B.6C.7D.8E.1012.某电视机水平-垂直扫描发生器需要一个分频器将31500H Z的脉冲转换为60H Z的脉冲,欲构成此分频器至少需要个触发器。

A.10B.60C.525D.3150013.某移位寄存器的时钟脉冲频率为100K H Z ,欲将存放在该寄存器中的数左移8位,完成该操作需要时间。

A.10μSB.80μSC.100μSD.800m s 14.若用J K 触发器来实现特性方程为,则J K 端的方程为 。

AB Q A Q n 1n +=+A.J =A B ,K = B.J =A B ,K = C.J =,K =A B D.J =,K =A B B A +B A B A +B A 15.要产生10个顺序脉冲,若用四位双向移位寄存器CT74LS194来实现,需要 片。