MC9S12XS128指令集

- 格式:docx

- 大小:30.10 KB

- 文档页数:6

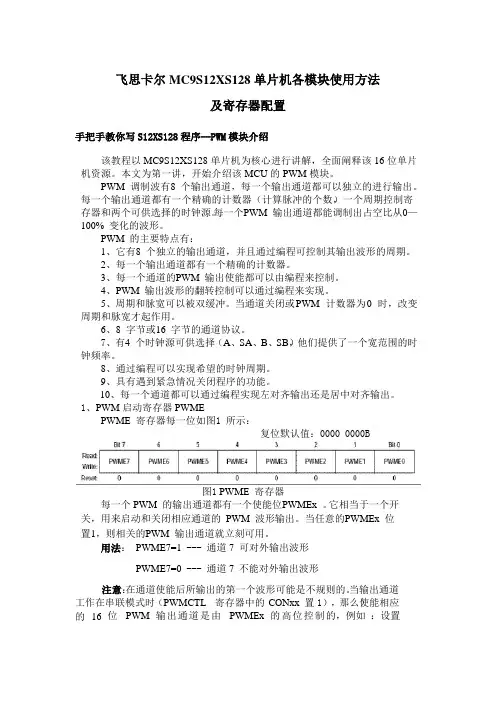

飞思卡尔MC9S12XS128单片机各模块使用方法及寄存器配置手把手教你写S12XS128程序--PWM模块介绍该教程以MC9S12XS128单片机为核心进行讲解,全面阐释该16位单片机资源。

本文为第一讲,开始介绍该MCU的PWM模块。

PWM 调制波有8个输出通道,每一个输出通道都可以独立的进行输出。

每一个输出通道都有一个精确的计数器(计算脉冲的个数),一个周期控制寄存器和两个可供选择的时钟源。

每一个P WM 输出通道都能调制出占空比从0—100% 变化的波形。

PWM 的主要特点有:1、它有8个独立的输出通道,并且通过编程可控制其输出波形的周期。

2、每一个输出通道都有一个精确的计数器。

3、每一个通道的P WM 输出使能都可以由编程来控制。

4、PWM 输出波形的翻转控制可以通过编程来实现。

5、周期和脉宽可以被双缓冲。

当通道关闭或PWM 计数器为0时,改变周期和脉宽才起作用。

6、8 字节或16 字节的通道协议。

7、有4个时钟源可供选择(A、SA、B、SB),他们提供了一个宽范围的时钟频率。

8、通过编程可以实现希望的时钟周期。

9、具有遇到紧急情况关闭程序的功能。

10、每一个通道都可以通过编程实现左对齐输出还是居中对齐输出。

1、PWM启动寄存器PWMEPWME 寄存器每一位如图1所示:复位默认值:0000 0000B图1 PWME 寄存器每一个PWM 的输出通道都有一个使能位P WMEx 。

它相当于一个开关,用来启动和关闭相应通道的PWM 波形输出。

当任意的P WMEx 位置1,则相关的P WM 输出通道就立刻可用。

用法:PWME7=1 --- 通道7 可对外输出波形PWME7=0 --- 通道7 不能对外输出波形注意:在通道使能后所输出的第一个波形可能是不规则的。

当输出通道工作在串联模式时(PWMCTL 寄存器中的CONxx置1),那么)使能相应的16位PWM 输出通道是由PWMEx 的高位控制的,例如:设置PWMCTL_CON01 = 1,通道0、1级联,形成一个16位PWM 通道,由通道 1 的使能位控制PWM 的输出。

飞思卡尔MC9S12XS128技术手册(AD转换部分)英文资料:飞思卡尔MC9S12XS256RMV1官方技术手册1.1 XS12系列单片机的特点XS12系列单片机特点如下:·16位S12CPU—向上支持S12模糊指令集并去除了其中的MEM, WAV, WAVR, REV, REVW 五条指令;—模块映射地址机制(MMC);—背景调试模块(BDM);·CRG时钟和复位发生器—COP看门狗;—实时中断;·标准定时器模块—8个16位输入捕捉或输出比较通道;;—16位计数器,8位精密与分频功能;—1个16位脉冲累加器;·周期中断定时器PIT—4具有独立溢出定时的定时器;—溢出定时可选范围在1到2^24总线时钟;—溢出中断和外部触发器;·多达8个的8位或4个16位PWM通道—每个通道的周期和占空比有程序决定;—输出方式可以选择左对齐或中心对其;—可编程时钟选择逻辑,且可选频率范围很宽;·SPI通信模块—可选择8位或16位数据宽度;—全双工或半双工通信方式;—收发双向缓冲;—主机或从机模式;—可选择最高有效为先输出或者最低有效位先输出;·两个SCI串行通信接口—全双工或半双工模式·输入输出端口—多达91个通用I/O引脚,根据封装方式,有些引脚未被引出;—两个单输入引脚;·封装形式—112引脚薄型四边引线扁平封装(LQFP);—80引脚扁平封装(QFP);—64引脚LQFP封装;·工作条件—全功率模式下单电源供电范围3.15V到5V;—CPU总线频率最大为40MHz—工作温度范围–40 C到125 C第十章模拟—数字转换10.1 介绍ADC12B16C是一个16通道,12位,复用方式输入逐次逼近模拟—数字转换器。

ATD的精度由电器规格决定。

10.1.1 特点·可设置8位、10位、12位精度·在停止模式下,ATD转换使用内部时钟·转换序列结束后自动进入低耗电模式·可编程采样时间·转化结果可选择左对齐或右对齐·外部触发控制·转换序列结束后产生中断·模拟输入的16个通道为复用方式·可以选择VRH、VRL、 (VRL+VRH)/2特殊转换方式·转换序列长度1到16·可选择连续转换方式·多通道扫描·任何AD通道均可配置外部触发功能,并且可选择4种额外的触发输入。

用了一年多飞思卡尔MC9S12XS128这款处理器,现在总结下各个功能模块的驱动.//锁相环时钟的初始化总线频率为40MHz(总线时钟为锁相环时钟的一半)//晶振为11.0592MHzvoid PLL_init(void) //PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1) { //锁相环时钟= 2*11.0592*(39+1)/(10+1)=80MHz 总线时钟为40MHzREFDV=0x0A;SYNR=0x67; //0110_0111 低6位的值为19,高两位的值为推荐值while(CRGFLG_LOCK != 1);CLKSEL_PLLSEL = 1; //选定锁相环时钟//FCLKDIV=0x0F; //Flash Clock Divide Factor 16M/16=1M}//周期中断定时器的初始化-// //周期中断通道1用于脉冲累加器的定时采样,定时周期为: 10ms= (199+1)*(1999+1)/(40M) (没有使用)//周期中断通道0用于控制激光管的轮流发射,定时周期为: 2000us= (399+1)*(199+1)/(40M)//2011/4/4 15:24 定时时间改为1msvoid PIT_init(void){PITCFLMT_PITE = 0; // 禁止使用PIT模块 PITCFLMT :PIT 控制强制加载微计数器寄存器。

PITCE_PCE0 = 1; // 使能定时器通道0//PITCE_PCE1 = 1; //使能定时器通道1PITMUX = 0; //通道0,和通道1均选择8位微计数器0//修改时间只需要改下面四行PITMTLD0 = 199; //向8位微计数器中加载的值PITLD0 = 199; //向16位计数器中加载的值//PITMTLD1 = 39; //向8位微计数器中加载的值 8位,最大值不要超过255//PITLD1 = 1999; //向16位计数器中加载的值PITINTE |= 0x01; //使能定时器通道0的中断PITCFLMT_PITE = 1;//使能PIT模块}//脉冲累加器的初始化, PT7口外接光电编码器//最新修改: 2011/3/25 16:53void PT7_PulAcc_Init(void){DDRT &= 0x77;//设置PT7,PT3口为输入(硬件上PT7,PT3通过跳线联到了一块)PERT |= 0x80; //使能通道7的上拉电阻PPST &= 0x7f; //电阻设为上拉电阻TCTL4 &= 0x3f; //禁止PT3的输入捕捉功能PACTL = 0x50; //启动脉冲累加计数器,上升沿触发,禁止触发中断和溢出中断,主定时器禁止}//通道1用于控制舵机1 PWM 高电平有效,//通道3用于控制电机1 PWM 低电平有效,这与前两代车高电平有效有区别!!!!!//通道7用于给上排激光管提供PWM信号 PWM高电平有效!!!!!//通道6用于给下排激光管提供PWM信号 PWM高电平有效!!!!!// 2011-03-17 7:56 增加了A端口的使用新增通道6//2011-6-9 23:03 //增加了通道4,5的联合使用,用于控制下排方向舵机 void PWM_init(void){PWME = 0x00;//PWM禁止PWMPRCLK = 0x03; // ClockA=40M/8=5M, Clock B = 40M/1=40M PWMSCLB = 10; // Clock SB= 40/2*10= 2MHz(供电机)PWMSCLA = 5; // SA = Clock A/2*5 = 5M/10 = 500K = SA 用于控制舵机PWMPOL = 0xe2; //1110_0010通道7,通道6与通道1、通道5先输出高电平然后输出低电平,POLx=1先输出高电平后输出低电平; PPOLx=0先输出低电平)PWMCAE = 0x00; // 左对齐输出(CAEx=0为左对齐,反之为中心对齐)//PWMCLK = 0010_1010 (0 1 4 5位控制SA_1;或A_0; 2 3 6 7位控制SB_1 或B_0)//为PWM通道1选择时钟 SA(500KHz),//为PWM通道5选择时钟 SA(500KHz),//为通道3选择时钟 SB(10MHz)//为通道7选择时钟B(40MHz)//为通道6选择时钟B(40MHz)PWMCLK = 0x2A; //0010_1010PWMCTL = 0x70; //0111_0000 CON45=1,把通道4,5联合使用。

/***************串口发送初始化****************//***************************************************/void uart_init(void){SCI0ACR1=0x00;SCI0CR2=0x0c; //允许发送SCI0BDH=0x00;SCI0BDL=64000000/(115200*16); //xxM}/*********************单个字符发送函数************************ 功能:发送一个字符输入参数:ch输出参数:无*************************************************************/void SCI_Putchar(char ch){while(!(SCI0SR1&0X80)); //检查发送寄存器空标志TDREwhile(!(SCI0SR1&0X40)); //检查发送完成标志TC//=0正在发送=1没有发送SCI0DRL=ch;}/*********************字符串发送函数************************ 功能:发送字符串输入参数:*str输出参数:无*************************************************************/void SCI_Putstr(char *str) //可直接发送中文,比如uart_putstr("个") {for(;*str!=0;str++){SCI_Putchar(*str);}}/*********************单个字符接收函数************************ 功能:接收一个字符输入参数:无输出参数:SCI0DRL寄存器中的字符*************************************************************/byte SCI_getchar(void){while(!SCI0SR1_RDRF); //RDRF 接收数据寄存器满标志//当接收移位寄存器中的数据发动到SCI数据寄存器中时,RDRF置位。

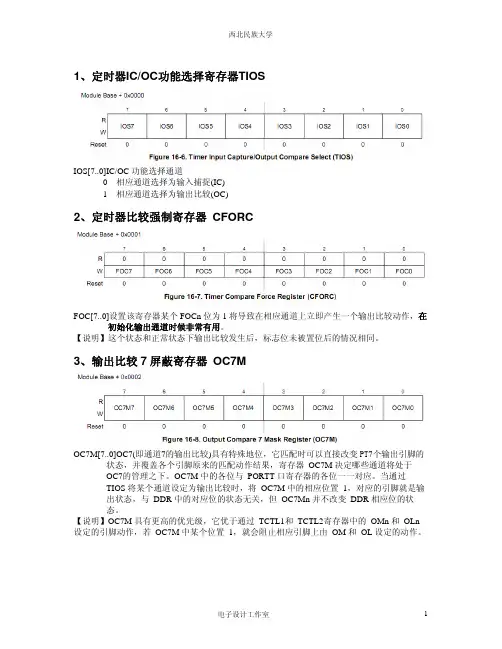

1、定时器IC/OC功能选择寄存器TIOSIOS[7..0]IC/OC功能选择通道0 相应通道选择为输入捕捉(IC)1 相应通道选择为输出比较(OC)2、定时器比较强制寄存器 CFORCFOC[7..0]设置该寄存器某个FOCn位为1将导致在相应通道上立即产生一个输出比较动作,在初始化输出通道时候非常有用。

【说明】这个状态和正常状态下输出比较发生后,标志位未被置位后的情况相同。

3、输出比较7屏蔽寄存器 OC7MOC7M[7..0]OC7(即通道7的输出比较)具有特殊地位,它匹配时可以直接改变PT7个输出引脚的状态,并覆盖各个引脚原来的匹配动作结果,寄存器OC7M决定哪些通道将处于OC7的管理之下。

OC7M中的各位与PORTT口寄存器的各位一一对应。

当通过TIOS将某个通道设定为输出比较时,将OC7M中的相应位置1,对应的引脚就是输出状态,与DDR中的对应位的状态无关,但OC7Mn并不改变DDR相应位的状态。

【说明】OC7M具有更高的优先级,它优于通过TCTL1和TCTL2寄存器中的OMn和OLn设定的引脚动作,若OC7M中某个位置1,就会阻止相应引脚上由OM和OL设定的动作。

4、输出比较7数据寄存器 OC7DOC7D[7..0]OC7M对于其他OC输出引脚的管理限于将某个二进制值送到对应引脚,这个值保存在寄存器OC7D中的对应位中。

当OC7匹配成功后,若某个OC7Mn=1,则内部逻辑将OC7Dn送到对应引脚。

OC7D中的各位与PORTT口寄存器的各位一一对应。

当通道7比较成功时,如果OC7M中的某个位为1,OC7D中的对应位将被输出到PORTT的对应引脚。

【总结】通道7的输出比较(OC7)具有特殊的位置,在OC7Mn和OC7Dn两个寄存器设置以后,OC7成功输出后将会引起一系列的动作。

比如:OC7M0=1,则通道0处在OC7的管理下,在OC7成功后,系统会将OC7D0的逻辑数据(仅限0或者1)反应在PT0端口上。

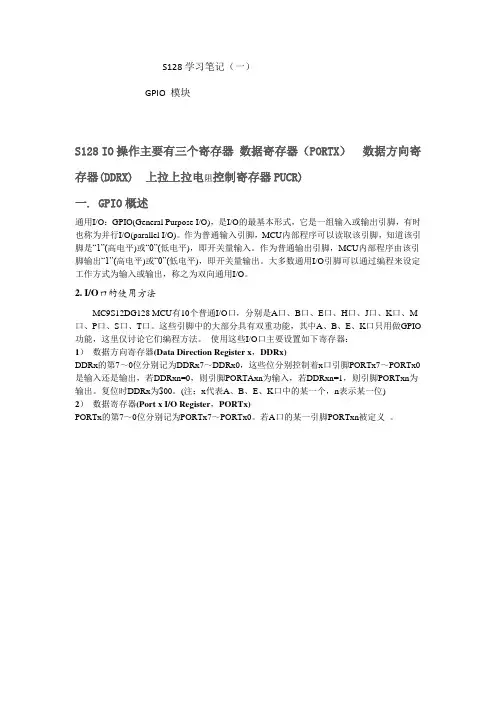

S128学习笔记(一)GPIO 模块S128 IO操作主要有三个寄存器数据寄存器(PORTX)数据方向寄存器(DDRX) 上拉上拉电阻控制寄存器PUCR)一. GPIO概述通用I/O:GPIO(General Purpose I/O),是I/O的最基本形式,它是一组输入或输出引脚,有时也称为并行I/O(parallel I/O)。

作为普通输入引脚,MCU内部程序可以读取该引脚,知道该引脚是“1”(高电平)或“0”(低电平),即开关量输入。

作为普通输出引脚,MCU内部程序由该引脚输出“1”(高电平)或“0”(低电平),即开关量输出。

大多数通用I/O引脚可以通过编程来设定工作方式为输入或输出,称之为双向通用I/O。

2. I/O口的使用方法MC9S12DG128 MCU有10个普通I/O口,分别是A口、B口、E口、H口、J口、K口、M 口、P口、S口、T口。

这些引脚中的大部分具有双重功能,其中A、B、E、K口只用做GPIO 功能,这里仅讨论它们编程方法。

使用这些I/O口主要设置如下寄存器:1)数据方向寄存器(Data Direction Register x,DDRx)DDRx的第7~0位分别记为DDRx7~DDRx0,这些位分别控制着x口引脚PORTx7~PORTx0是输入还是输出,若DDRxn=0,则引脚PORTAxn为输入,若DDRxn=1,则引脚PORTxn为输出。

复位时DDRx为$00。

(注:x代表A、B、E、K口中的某一个,n表示某一位)2)数据寄存器(Port x I/O Register,PORTx)PORTx的第7~0位分别记为PORTx7~PORTx0。

若A口的某一引脚PORTxn被定义。

成输出,程序使x口I/O寄存器PORTx的相应位PORTxn=0,则引脚PORTxn输出“低电平”;程序使PORTxn=1,则引脚PORTxn输出“高电平”。

若x口的某一引脚PORTxn被定义成输入,程序通过读取x口I/O寄存器PORTx,获得输入情况,0表示输入为“低电平”,1表示输入为“高电平”。

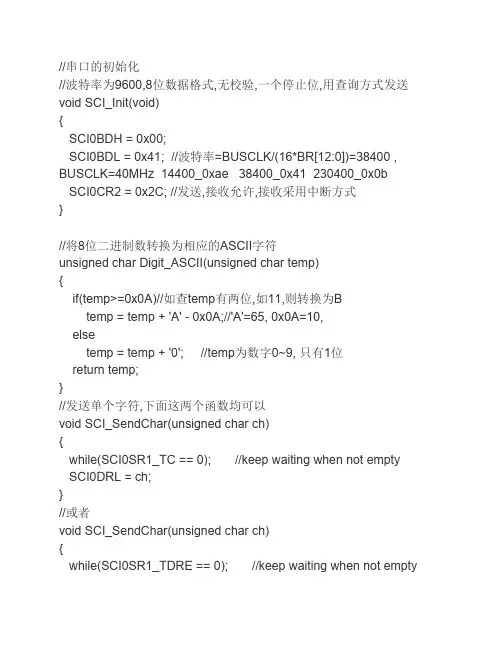

MC9S12XS128例程SCI程序串行通信时MCU与外部设备之间进行通信的一种简单而有效的硬件方法。

无论用查询方式还是中断方式进行串行通信编程,在程序初始化时均必须对SCI进行初始化。

初始化主要包括波特率设置、通信格式的设置、发送接收数据方式的设置等。

对SCI进行初始化,需要设置如下几部分:(1)定义波特率一般选内部总线时钟为串行通信的时钟源。

通过设置SCI波特率寄存器SCI0BD的波特率选择位SBR[12:0],来选择合适的分频系数。

(2)写控制字到SCI控制寄存器1(SCI0CR1)设置是否允许SCI、数据长度、输出格式、选择唤醒方法、是否校验等。

(3)写控制字到SCI控制寄存器2(SCI0CR2)设置是否允许发送与接收、是中断接收还是查询接收等。

串行通信程序如下:/** write in “Init.h” **/#include /* common defines and macros */#include "derivative.h" /* derivative-specific definitions */ //void InitBusClk(void); //可以不使用锁相环void InitSci(void);/** write in “Init.c” **///初始化程序#include "Init.h"/*//------------初始化Bus Clock------------//void InitBusClk(void) {DisableInterrupts;CLKSEL=0X00; //PLLSEL 1 : Bus Clock=PLLCLK/2// 0 : Bus Clock=OSCCLK/2PLLCTL_PLLON=1; //开启PLLSYNR=0; //OSCCLK=16MHzREFDV=0X0F;//PLLCLK=2*OSCCLK*[(1+SYNR)/(1+REFDV]=32/16=2MHz while(!(CRGFLG_LOCK==1)); //直到LOCK=1,when PLL is ready,退出循环CLKSEL_PLLSEL=1; //PLLSEL 1 : Bus Clock=PLLCLK/2=2MHz/2=1MHz// 0 : Bus Clock=OSCCLK/2=16M/2=8MHz}*///---------------初始化SCI---------------//void InitSci(void){SCI0BD=4545; //设波特率为110//SCI baud rate = SCI module clock/(16*SCIBD)=Bus Clock/(16*SCIBD)// = 8MHz/(16*4545)=500kHz/4545=110bps//SCIBD : SBR12-SBR0,Value from 1 to 8191SCI0CR1=0;SCI0CR2=0X2C; // 0010 1100 RIE=1,TE=1,RE=1// RIE=1 RDRF and OR interrupt requests enabled// TE=1 Transmitter enabled// RE=1 Receiver enabled}/** write in “SCI.h” **///函数声明unsigned char SciRead();void SciWrite(byte);/** write in “SCI.c” **///串行通信程序#include "Init.h"#include "SCI.h"//---------------读SCI数据---------------//unsigned char SciRead(){if(SCI0SR1_RDRF==1){//数据从移位寄存器传送到SCI数据寄存器SCIDRL//SCI0SR1_RDRF==1表明数据寄存器SCI0DRL为满,可以接收新的数据SCI0SR1_RDRF=1; //读取SCI数据寄存器会将RDRF清除,重新置位return SCI0DRL; //返回数据寄存器的数值}}//---------------写SCI数据---------------//void SciWrite(byte sci_value){while(!(SCI0SR1&0X80));//SCI0SR1_TDRE==1表明数据寄存器SCI0DRL为空,可以发送新的数据SCI0DRH=0;SCI0DRL=sci_value; //发送新的数据至数据寄存器SCI0DR}//---------------中断程序-----------------//#pragma CODE_SEG NON_BANKEDinterrupt 20 void Sci_Intrrupt(void){ //SCI的中断向量号为20 byte text;DisableInterrupts; //关中断text=SciRead(); //接收数据寄存器SCI0DRL中的数据asm nop;asm nop;SciWrite(text); //发送数据至数据寄存器SCI0DRLDDRA=0XFF; //设A口为输出,用来显示是否执行中断,可以不用PORTA_PA6=!PORTA_PA6;EnableInterrupts; //开中断}#pragma CODE_SEG DEFAULT/** write in “main.c”” **/#include "Init.h"#include "SCI.h"void main(void) {/* put your own code here */_DISABLE_COP(); //关看门狗DisableInterrupts; //关中断//InitBusClk();InitSci();EnableInterrupts; //开中断for(;;) {// _FEED_COP(); /* feeds the dog */} /* loop forever *//* please make sure that you never leave main */}A/D转换应用实例要让ATD 开始转换工作,必须经过以下三个步骤:1.将ADPU 置1,使ATD 启动;2.按照要求对转换位数、扫描方式、采样时间、时钟频率及标志检查等方式进行设置;3.发出启动命令;如果上电默认状态即能满足工作要求,那么只要将ADPU 置1,然后通过控制寄存器发出转换命令,即可实现转换。

飞思卡尔智能汽车竞赛XS128主要模块实验指导书第一章端口整合模块端口A,B和K为通用I/O接口端口E 整合了IRQ,XIRQ中断输入端口T 整合了1个定时模块端口S 整合了2个SCI模块和1个SPI模块端口M 整合了1个MSCAN端口P 整合了PWM 模块,同时可用作外部中断源输入端口H 和J 为通用I/O接口,同时可用作外部中断源输入端口AD 整合了1个16位通道ATD模块大部分I/O引脚可由相应的寄存器位来配置选择数据方向、驱动能力,使能上拉或下拉式装置。

当用作通用IO口时,所有的端口都有数据寄存器和数据方向寄存器。

对于端口T, S, M, P, H, 和J 有基于每个针脚的上拉和下拉控制寄存器。

对于端口AD 有基于每个针脚的上拉寄存器。

对于端口A、B、E 和K,有一个基于端口的上拉控制寄存器。

对于端口T, S, M, P, H, J, 和AD,有基于每个针脚的降额输出驱动控制寄存器。

对于端口A, B, E, 和K,有一个基于端口的降额输出驱动控制寄存器。

对于端口S、M,有漏极开路(线或)控制寄存器。

对于端口P、H 和J,有基于每个针脚的中断标志寄存器。

纯通用IO端口共计有41个,分别是:PA[7:0]PB[7:0]PE[6:5]PE[3:2]PK[7,5:0]PM[7:6]PH[7:0] (带中断输入)PJ[7:6] (带中断输入)PJ[1:0] (带中断输入)第二章脉冲宽度调制模块XS128具有8位8通道的PWM,相邻的两个通道可以级联组成16位的通道。

PWME:PWM通道使能寄存器。

PWMEx=1将立即使能该通道PWM波形输出。

若两个通道级联组成一个16位通道,则低位通道(通道数大的)的使能寄存器成为该级联通道的使能寄存器,高位通道(通道数小的)的使能寄存器和高位的波形输出是无效的。

PWMPOL:PWM极性寄存器。

PPOLx=1,则该通道的周期初始输出为高电平,达到占空比后变为低电平;相反,若PPOLx=0,则初始输出为低电平,达到占空比后变为高电平。

MC9S12XS128串口操作例程MC9S12XS128 串口操作例程Code Warrior 4.7Target : MC9S12XS128Crystal: 16.000Mhzbusclock: 8.000MHzpllclock:16.000MHz本程序主要包括以下功能:1.设置锁相环和总线频率;2.IO口使用;3.共四路ATD使用及显示方法。

LED计数,根据灯亮可以读取系统循环了多少次************************************************************** ***************************/#include /* common defines and macros */#include /* derivative information */#include#include#include#pragma LINK_INFO DERIVATIVE "mc9s12xs128"#pragma CODE_SEG DEFAULT#define CR_as_CRLF TRUE // if true , you can use "\n" to act as CR/LF,// if false, you have to use "\n\r",but can get a higher speed static int do_padding;static int left_flag;static int len;static int num1;static int num2;static char pad_character;unsigned char uart_getkey(void){while(!(SCI0SR1&0x80)) ; //keep waiting when not emptyreturn SCI0DRL;}/*void uart_init(void) {SCI0CR2=0x0c;SCI0BDH=0x00;//16MHz,19200bps,SCI0BDL=0x1aSCI0BDL=0x34;//16MHz,9600bps,SCI0BDL=0x34}*/void uart_putchar(unsigned char ch){if (ch == '\n'){while(!(SCI0SR1&0x80)) ;SCI0DRL= 0x0d; //output'CR'return;}while(!(SCI0SR1&0x80)) ; //keep waiting when not empty SCI0DRL=ch;}void putstr(char ch[]){unsigned char ptr=0;while(ch[ptr]){uart_putchar((unsigned char)ch[ptr++]);}}static void padding( const int l_flag){int i;if (do_padding && l_flag && (len < num1))for (i=len; i<="" p="">uart_putchar( pad_character);}static void outs( char* lp){/* pad on left if needed */len = strlen( lp);padding( !left_flag);/* Move string to the buffer */while (*lp && num2--) uart_putchar( *lp++);/* Pad on right if needed */len = strlen( lp);padding( left_flag);}static void reoutnum(unsigned long num, unsigned int negative, const long base ){char* cp;char outbuf[32];const char digits[] = "0123456789ABCDEF";/* Build number (backwards) in outbuf */cp = outbuf;do {*cp++ = digits[(int)(num % base)];} while ((num /= base) > 0);if (negative) *cp++ = '-';*cp-- = 0;/* Move the converted number to the buffer and *//* add in the padding where needed. */len = strlen(outbuf);padding( !left_flag);while (cp >= outbuf)uart_putchar( *cp--);padding( left_flag);}static void outnum(long num, const long base ,unsigned char sign)//1, signed 0 unsigned{unsigned int negative;if ( (num < 0L) && sign ){negative=1;num = -num;}else negative=0;reoutnum(num,negative,base);}static int getnum( char** linep){int n;char* cp;n = 0;cp = *linep;while (isdigit(*cp))n = n*10 + ((*cp++) - '0');*linep = cp;return(n);}void printp( char* ctrl, ...){int long_flag;int dot_flag;char ch;va_list argp;va_start( argp, ctrl);for ( ; *ctrl; ctrl++) {/* move format string chars to buffer until a format control is found. */ if (*ctrl != '%') {uart_putchar(*ctrl);#if CR_as_CRLF==TRUEif(*ctrl=='\n') uart_putchar('\r');#endifcontinue;}/* initialize all the flags for this format. */dot_flag = long_flag = left_flag = do_padding = 0;pad_character = ' ';num2=32767;try_next:ch = *(++ctrl);if (isdigit(ch)){if (dot_flag)num2 = getnum(&ctrl);else {if (ch == '0')pad_character = '0';num1 = getnum(&ctrl);do_padding = 1;}ctrl--;goto try_next;}switch (tolower(ch)) {case '%':uart_putchar( '%');continue;case '-':left_flag = 1;break;case '.':dot_flag = 1;break;case 'l':long_flag = 1;break;case 'd':if (long_flag ==1 ){if(ch == 'D') {outnum( va_arg(argp, unsigned long), 10L , 0);continue;}else /* ch == 'd' */ {outnum( va_arg(argp, long), 10L,1);continue;}}else{if(ch == 'D') {outnum( va_arg(argp, unsigned int),10L,0);continue;}else /* ch == 'd' */{outnum( va_arg(argp, int), 10L,1); continue;}}case 'x': // X 无符号,x 有符号if (long_flag ==1 ){if(ch == 'X'){outnum( va_arg(argp, unsigned long), 16L,0); continue;}else /* ch == 'x' */{outnum( va_arg(argp, long), 16L,1); continue;}}else{if(ch == 'X'){outnum( va_arg(argp, unsigned int), 16L,0); continue;}else /* ch == 'x' */{outnum( va_arg(argp, int), 16L,1);continue;}} //如果按照16进制打印,将全部按照无符号数进行continue;case 's':outs( va_arg( argp, char*));continue;case 'c':uart_putchar( va_arg( argp, int));continue;default:continue;}goto try_next;}va_end( argp);}#pragma CODE_SEG __NEAR_SEG NON_BANKED void interrupt 20 SCI0_ISR(void){SCI0CR2_RIE=0;//此处为串口中断需要处理的事情uart_putchar(uart_getkey());PORTA_PA0=~PORTA_PA0;SCI0CR2_RIE = 1;}#pragma CODE_SEG DEFAULT//-----------------------------------------------------void setbusclock(void){CLKSEL=0X00; //disengage PLL to systemPLLCTL_PLLON=1; //turn on PLLSYNR=1;REFDV=1; //pllclock=2*osc*(1+SYNR)/(1+REFDV)=32MHz;_asm(nop); //BUS CLOCK=16M_asm(nop);while(!(CRGFLG_LOCK==1)); //when pll is steady ,then use it;CLKSEL_PLLSEL =1; //engage PLL to system;}//-----------------------------------------------------static void SCI_Init(void){SCI0CR1 =0x00;SCI0CR2 =0x2c; //enable Receive Full Interrupt,RX enable,Tx enable SCI0BD =0x68; //SCI0BDL=busclk/(16*SCI0BDL) //busclk 8MHz, 9600bps,SCI0BD=0x34//busclk 16MHz, 9600bps,SCI0BD=0x68//busclk 24MHz, 9600bps,SCI0BD=0x9C} //busclk 32MHz, 9600bps,SCI0BD=0xD0//busclk 40MHz, 9600bps,SCI0BD=0x106//-----------------------------------------------------void Dly_ms(int ms){int ii,jj;if (ms<1) ms=1;for(ii=0;ii<ms;ii++)< p="">for(jj=0;jj<2670;jj++); //busclk:16MHz--1ms}void main(void){unsigned char LedCnt=0;setbusclock();SCI_Init();DDRA=0xFF;PUCR_PUPBE=1;EnableInterrupts;for(;;){LedCnt=(LedCnt>0XFE?0:++LedCnt);Dly_ms(1000); //修改延时以修改数据发送频率//低电平灯亮用这句,注释掉下面那句PORTA_PA0=~PORTA_PA0;//高电平灯亮用这句,注释掉上面那句//PORTB=LedCnt;putstr("\nhttp:%/%//doc/4115489903.html,");printp("\n Minute elapsed: %03ds",LedCnt); }}</ms;ii++)<>。

========================PS2.h=====================================#ifndef _PS2_H#define _PS2_H#define PS2_CLK PTJ_PTJ1#define PS2_RW PORTA_PA1typedef struct PS2_V alueType {char PS2_V alueData; /* 码表Num :77 /:E04A*:7C -:7B7: 6C 8:75 9:7D +:794: 6B 5:73 6:74 +:791: 69 2:72 3:7A Enter:E05A0: 70 .:71*//* 对应返回值Num :-5 /:-4 *:7C -:-27: 7 8:8 9:9 +:-14: 4 5:5 6:6 +:-11: 1 2:2 3:3 Enter:100: 0 .:-3 空格-6*/unsigned char PS2_V alueKind; //0 按下,1松手}PS2_V alueType;#endif _PS2_H======================================PS2.c============================ #include "PS2.h"#include "MC9S12XS128.h"//extern unsigned char PS2_Buffer[3];//extern unsigned char PS2_StopCodeFlag=0;//从PS/2中获取一个按键unsigned char PS2_GetData(void){unsigned char temp,i,res;for(i=0;i<11;i++) {while(PS2_CLK);if(i>0 && i<9) {res=res>>1;if(PS2_RW) {res=res|0x80;}}while (!PS2_CLK);}return res;}void Key_Interrupt(void) {//DDRJ=0X00;PIEJ_PIEJ1=1;PPSJ_PPSJ1=0;}void PS2_InsertBuffer(unsigned char *buffer,unsigned char bufferdata) {unsigned char *tempdata=buffer+1;(*buffer++)=(*tempdata++);(*buffer++)=(*buffer++);(*buffer)=bufferdata;}void PS2_GetChar(PS2_V alueType *PS2_V alue){unsigned char temp;temp=PS2_GetData();(*PS2_V alue).PS2_V alueKind=0;if(temp!=0xe0 && temp!=0xf0){switch (temp){/* 对应返回值Num :-6 /:-4 *:-5 -:-27: 7 8:8 9:9 +:-14: 4 5:5 6:6 +:-11: 1 2:2 3:3 Enter:100: 0 .:-3*/case 0x70 : (*PS2_V alue).PS2_V alueData=0; return;case 0x69 : (*PS2_V alue).PS2_V alueData=1; return;case 0x72 : (*PS2_V alue).PS2_V alueData=2; return;case 0x7A : (*PS2_V alue).PS2_V alueData=3; return;case 0x6B : (*PS2_V alue).PS2_V alueData=4; return;case 0x73 : (*PS2_V alue).PS2_V alueData=5; return;case 0x74 : (*PS2_V alue).PS2_V alueData=6; return;case 0x6C : (*PS2_V alue).PS2_V alueData=7; return;case 0x75 : (*PS2_V alue).PS2_V alueData=8; return;case 0x7D : (*PS2_V alue).PS2_V alueData=9; return;case 0x71 : (*PS2_V alue).PS2_V alueData=-3; return;case 0x79 : (*PS2_V alue).PS2_V alueData=-1; return;case 0x7B : (*PS2_V alue).PS2_V alueData=-2; return;case 0x7C : (*PS2_V alue).PS2_V alueData=-5; return;case 0x77 : (*PS2_V alue).PS2_V alueData=-6; return;case 0x66 : (*PS2_V alue).PS2_V alueData=-7; return;}}else if(temp==0xe0){temp=PS2_GetData();if(temp==0xf0){temp=PS2_GetData();(*PS2_V alue).PS2_V alueKind=1;if(temp==0x5A){(*PS2_V alue).PS2_V alueData=10; return;}else if(temp==0x4A){(*PS2_V alue).PS2_V alueData=-4; return;}}else{(*PS2_V alue).PS2_V alueKind=0;if(temp==0x5A){(*PS2_V alue).PS2_V alueData=10; return;}else if(temp==0x4A){(*PS2_V alue).PS2_V alueData=-4; return;}}}else if (temp==0xf0){(*PS2_V alue).PS2_V alueKind=1;temp=PS2_GetData();switch (temp){/* 对应返回值Num :-6 /:-4 *:-5 -:-27: 7 8:8 9:9 +:-14: 4 5:5 6:6 +:-11: 1 2:2 3:3 Enter:100: 0 .:-3 空格-7*/case 0x70 : (*PS2_V alue).PS2_V alueData=0; return;case 0x69 : (*PS2_V alue).PS2_V alueData=1; return;case 0x72 : (*PS2_V alue).PS2_V alueData=2; return;case 0x7A : (*PS2_V alue).PS2_V alueData=3; return;case 0x6B : (*PS2_V alue).PS2_V alueData=4; return;case 0x73 : (*PS2_V alue).PS2_V alueData=5; return;case 0x74 : (*PS2_V alue).PS2_V alueData=6; return;case 0x6C : (*PS2_V alue).PS2_V alueData=7; return;case 0x75 : (*PS2_V alue).PS2_V alueData=8; return;case 0x7D : (*PS2_V alue).PS2_V alueData=9; return;case 0x71 : (*PS2_V alue).PS2_V alueData=-3; return;case 0x79 : (*PS2_V alue).PS2_V alueData=-1; return;case 0x7B : (*PS2_V alue).PS2_V alueData=-2; return;case 0x7C : (*PS2_V alue).PS2_V alueData=-5; return;case 0x77 : (*PS2_V alue).PS2_V alueData=-6; return;case 0x66 : (*PS2_V alue).PS2_V alueData=-7; return;}}}。