MC9S12XS128中文资料

- 格式:doc

- 大小:490.00 KB

- 文档页数:38

1Chapter1 Device Overview MC9S12P-Family 1.1介绍The MC9S12P 系列单片机是经过优化后有着低成本、高性能、低引脚数的汽车专业级单片机产品,该产品倾向于弥补高端16位单片及产品如MC9S12XS和低端8位单片机产品之间的空缺。

MC9S12P 主要针对于要求使用CAN 或者LIN/J2602通讯接口的汽车应用产品,典型的应用案例包括车身控制器、乘坐人员检测、车门控制、座椅控制、遥控车门开关信号接收器、智能执行器、车灯模块、智能接线器。

The MC9S12P 系列单片机使用了很多MC9S12XS系列单片机相同的功能,包括片内闪存错误纠正代码(ECC)、一个专为数据诊断或者数据存储的单独的数据闪存模块、高速AD转换器和高频调制锁相环(IPLL)有效改善电磁兼容性能。

MC9S12P系列单片机提供的所有16为单片机优点和微处理器效率,同时保持飞思卡尔用户熟悉的8位及16位单片机,低成本,功耗,EMC和高效的代码80针QFP、64针LQFP、40针QFN封装产品,最大限度的与MC9S12尺寸的优点,如同MC9S12XS一样可以无需等待外围设备和内存的状态既可以运行16为带款的寻址,MC9S12P系列单片机主要有XS引脚兼容. I/O口在各种模式下都可以使用,同时具有中断功能的I/O口还可以在停止或等待模式下唤醒。

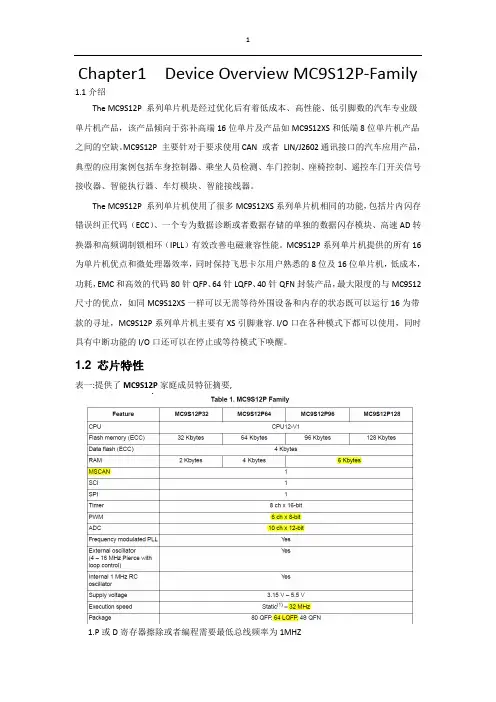

1.2 芯片特性表一:提供了MC9S12P家庭成员特征摘要,1.P或D寄存器擦除或者编程需要最低总线频率为1MHZ1.2.2 芯片功能• S12 CPU 内核• 高达128 KB具有ECC功能的片上闪存• 4 Kbyte带ECC功能的数据闪存• 高达6 Kb片上静态存储器(SRAM)• 具有内部滤波器的锁相环倍频器(IPLL)• 4–16 MHz 皮尔斯振荡器• 1 MHz内部RC振荡器• 定时器(TIM) 具有16位输入捕捉、输出比较、计数器脉冲累加器功能• 具有8位6通道的脉冲调制模块(PWM)• 10通道12位分辨率的逐次逼近AD转换器• 1个串行通信外部接口(SPI)• 1个支持局域网通讯串行通信(SCI) 模块•一个多可扩展控制器区域网络(MSCAN) 模块(支持CAN 协议2.0A/B)•片上电压调节器(VREG) 可对内部供电及内部电压整流• 自主周期中断(API)1.3 模块特征1.3.1 CPUS12 CPU 是一个高速的16位处理单元:•全16-bit数据通道提供有效的数学运算和高速的数学执行• 包含很多单字节指令,可以有效的利用ROM空间• 宽域变址寻址功能:—采用堆栈指针作为所有变址操作的变址寄存器—除了在自增或自减模式下都可以利用程序计数器作为变址寄存器—使用A\B\D累加器做累加器偏移—自动变址,前递增(++a)、前递减(--a)、后递减(a--)、后递增(a++)(by –8 to +8)1.3.2 带ECC功能的片内闪存• 高达128 Kb程序闪存空间— 32 位数据加7 位ECC (纠错码) 允许单字节纠错和双字节纠错— 512字节擦出扇区空间—自动编程和擦除算法—用户设置读写页面边界—具有可以防止偶然编程或者擦除的保护结构• 4 Kb 数据闪存空间— 16 位数据加6位纠错码允许单字节和双字节纠错功能— 256 字节的擦出扇区空间—自动编程和擦除算法—用户设置读写页面边界1.3.3 片内静态存储器3高达6kb通用RAM1.3.4 外部晶振(XOSC)• 闭环控制皮尔斯晶振频率为4MHZ---16MHZ—振幅增益控制输出电流—低谐波失真信号Signal with low harmonic distortion—低功耗—良好的噪声免疫—无需外部限流电阻—跨导尺寸优化提供良好的振荡器启动保证1.3.5 内部RC晶振(IRC)• 可调的内部参考时钟—频率: 1 MHz—在–40°C to +125°C环境温度范围内调节精度达: 1.5%1.3.6 内部锁相环倍频器(IPLL)—无需外部元件—参考分频器和倍频器提供大变化量的时钟频率—自动带宽控制低频率抖动操作—自动锁定频率—可配置的选项,扩频减少电磁干扰EMC (频率调制frequency modulation) —参考时钟源:–外部4–16 MHz 共振器/晶振(XOSC)–内部RC晶振1 MHz (IRC)1.3.7 系统支撑• 上电复位(POR)• 系统复位发生器• 非法寻址复位•低电压检测中断或复位• 实时中断(RTI)• 计算机正常工作复位(COP) 开门狗—可通过相应窗口设置COP用以采用错误侦测复位通过位操作对闪存进行初始化复位•时钟监控器监控晶振功能正常工作1.3.8 定时器(TIM)• 8通道16位定时器可进行输入捕捉和输出比较• 16-bit带有7位精度预分频器的自由运行计数器•一通道16-bit 脉冲累加器1.3.9 脉冲带宽调制器(PWM)• 6通道8位or 3 通道16-bit脉宽调制器—每个通道都可以对周期和占空比进行编程—中心对齐或者左对齐输出—宽频率范围内可编程逻辑时钟1.3.10 局域网控制器(MSCAN)•速率达1Mbit/s, 满足CAN 2.0 A, B 协议—标准和扩展数据帧— 0–8 字节长度—可编程比特率达1 Mbps•5个FIFO(先进先出)的接收缓冲器•三个内部优先发送缓冲器• 灵活的标识符可编程选通滤波器s:— 2 x 32-bit— 4 x 16-bit— 8 x 8-bit•集成了低通滤波器的唤醒操作• 闭环反馈自检测• CAN 总线监听•总线关闭可通过软件干预或者自动恢复• 16-bit 接收发送信息时钟戳1.3.11 串行通信接口(SCI)•可选择全双工或单工模式•标准的不归零格式•通过可编程脉宽调制选用IrDA 1.4 反转归零格式• 13位波特率可选•可编程字符长度•可编程改变其接收和发送极性for transmitter and receiver•边沿触发接收唤醒•支持LIN总线的间隔检测和传输冲突检测1.3.12 Serial Peripheral Interface Module (SPI) •可配置8- or 16-bit 数据大小•全双工或单线双向•全双工接收和发送• Master or slave 模式•最高位优先or 最低位优先可换• 并口时钟频率相位和极性选择1.3.13 AD转换(ATD)• 10通道12位AD转换器— 3微妙转换时间— 8-/10-/12-位解决方案5—数据结果左对齐或右对齐—停止模式下使用内部晶振作为转换器晶振—低功耗模式下模拟信号比较唤醒—连续转换模式e—多通道扫描•引脚可作为IO口1.3.14 片内电压调节器(VREG)•具有带隙标准的线性电压稳压器• 具有低电压中断功能的低压检测器•上电复位(POR) 电路•低电压复位功能(LVR)•高温传感器1.3.15 背景调试(BDM)• 非插入内存访问指令• 支持在线对片内非易始性存储单元编程1.3.16 调试器(DBG)•64个入口跟踪缓冲器• 三个比较器(A, B and C)—比较器A比较全16位地址总线额16位数据总线—精确寻址和寻址范围比较•两种匹配比较类型—标记位—程序强行置位该类型是在一数学公式出现后一个指令边界可用•四个跟踪模式•四个阶段状态序列发生器stage state sequencer1.4 内部结构框图71.5 引脚图1.6 存储器映像表Table 1-2. Device Register Memory Map注意在表1-2中保留的寄存器空间不分配给任何模块,该寄存器的保留空间是留给以后使用的,对这些保留空间写操作没有任何效果,读该空间返回值都为零。

M C9S12X S128之脉冲宽度调制P W M-CAL-FENGHAI-(2020YEAR-YICAI)_JINGBIAN半年前就开始写PWM的程序了,那时候只是用来控制电机和舵机。

最近在烦着摄像头的显示问题,再次探究PWM,看能不能找到出路。

我数了一下,整个PWM模块中,总共有37个寄存器。

不过把这些寄存器的功能都理了一下,发现:也不过这么一回事。

PWM就是脉冲宽度调制,是英文“Pulse Width Modulation”的缩写,是利用微处理器的数字输出来对模拟电路进行控制的一种非常有效的技术。

在XS128中,PWM主要就是通过设置相关的寄存器,让PWM0~PWM7引脚输出一定周期一定占空比的矩形波。

输出的矩形波的周期和占空比在输出的过程中,可以通过改变相关寄存器的值来改变的。

电机和舵机就这利用这点来控制期速度和转向的。

不过观察了一下,似乎在112引脚封装的芯片中才有PWM0到PWM7八个通道的引脚输出,而在80引脚封装的芯片中只有七个通道的引脚输出,没有PWM6的引脚输出。

接下来写一下各个寄存器的功能和设置方法:一、PWME:各通道使能寄存器明显,当某位置1时,相应通道的PWM就打开了。

置0时,就是禁止该通道的PWM。

二、PWMPOL:极性设置寄存器这个寄存器可以设置相应通道的PWM波在每个周期内是先出现高电平后低电平,或是先低电平后高电平。

PPOLn=1:n 通道对外输出波形先是高电平然后再变为低电平。

PPOLn=0:n通道对外输出波形先是低电平然后再变为高电平。

这个设置与占空比的计算有关。

三、PWMCLK:时钟选择寄存器PWM模块中共有四个时钟,分别为A、B、SA、SB。

对于第0、1、4、5通道,PCLKn=0时,则其通选择的是时钟A;当PCLKn=1时,其通道选择的是时钟SA。

对于2、3、6、7通道,PCLKn=0时,其通道选择的是时钟B,当PCLKn=1时,其通道选择的是时钟SB。

串行通信分为同步通信和异步通信。

串行通信接口都具有发送引脚TXD和接收引脚RXD,它们是TTL平电。

如果要利用这两个引脚与外界实行异步通信,必须将TTL电平转化为RS-232电平。

SCI是一种全双工异步串行通信接口,主要用于MCU与其他计算机或设备之间的通信,几个独立的MCU也能通过SCI实现串行通信,形成网络。

从编程角度看,先设定好波特率,通信格式,是否校验,是否允许中断等。

接着发送数据时,先检查相应的标志位是否允许发送数据,如果可以,则把数据放入SCI数据寄存器即可,剩下的工作芯片自动完成:将数据从SCI数据寄存器送到发送移位寄存器,硬件驱动将发送移位寄存器里的数据按规定发送到发送引脚TXD,供对方接收。

接收时,数据逐位从接收引脚RXD进入到接收移位寄存器,当收到一个完整字节时,芯片会自动将数据送到SCI数据寄存器,并置相应的标志位,我们就可以根据标志位的情况来读取数据了。

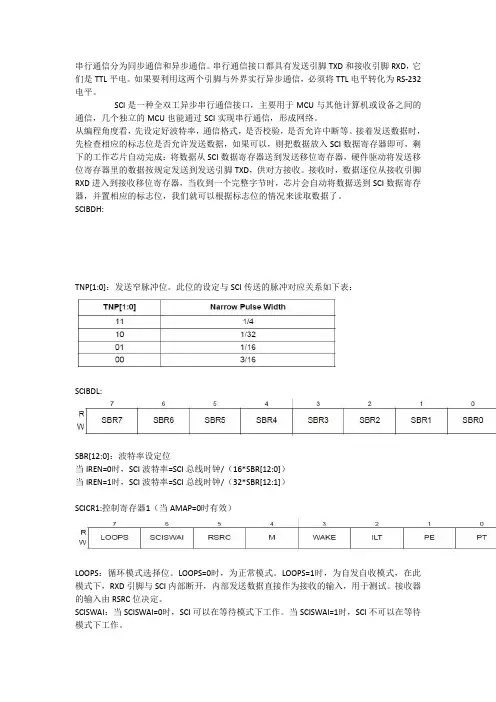

SCIBDH:TNP[1:0]:发送窄脉冲位。

此位的设定与SCI传送的脉冲对应关系如下表:SCIBDL:SBR[12:0]:波特率设定位当IREN=0时,SCI波特率=SCI总线时钟/(16*SBR[12:0])当IREN=1时,SCI波特率=SCI总线时钟/(32*SBR[12:1])SCICR1:控制寄存器1(当AMAP=0时有效)LOOPS:循环模式选择位。

LOOPS=0时,为正常模式。

LOOPS=1时,为自发自收模式,在此模式下,RXD引脚与SCI内部断开,内部发送数据直接作为接收的输入,用于测试。

接收器的输入由RSRC位决定。

SCISWAI:当SCISWAI=0时,SCI可以在等待模式下工作。

当SCISWAI=1时,SCI不可以在等待模式下工作。

RSRC:当LOOPS=1时,RSRC位决定接收移位寄存器接收数据的来源。

RSRC=1,RXD引脚与SCI模块断开,SCI用TXD引脚来发送及接收。

RSRC=0时,发送器的输出作为接收器的输入。

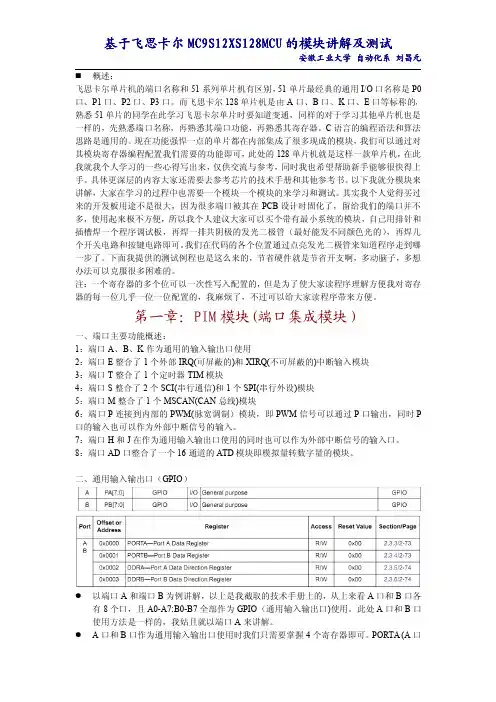

飞思卡尔MC9S12G系列详解

飞思卡尔MC9S12G系列详解

电子发烧友网:随着驾驶员对车内舒适度和便利性的要求在提高,汽车车身电子产品在保持具有竞争力价格的同时,还需要继续提供性能更高的半导体。

飞思卡尔半导体目前开始扩大现已普及的16位S12微控制器(MCU)系列,以优化大量对成本敏感的汽车车身电子应用。

先进的S12G 器件设计针对应用需求,提供灵活的内存、封装和成本选项。

MC9S12G系列是一个专注于低功耗、高性能、低引脚数量的高效汽车级16位微控制器产品。

这个系列是桥连8位高端微机和16位高性能微机,像MC9S12XS系列。

本文将详细介绍关于飞思卡尔MC9S12系列的芯片简介、MC9S12单片机最小系统硬件设计、典型程序应用、飞思卡尔XS128和G128两种单片机的主要区别等进行阐述。

飞思卡尔MC9S12G系列单片机中文简介

1.1介绍

MC9S12G系列是一个专注于低功耗、高性能、低引脚数量的高效汽车级16位微控制器产品。

这个系列是桥连8位高端微机和16位高性能微机,像MC9S12XS系列。

MC9S12G系列是为了满足通用汽车CAN或

LIN/J2602通信应用。

这些应用的典型例子包括body controllers,occupant。

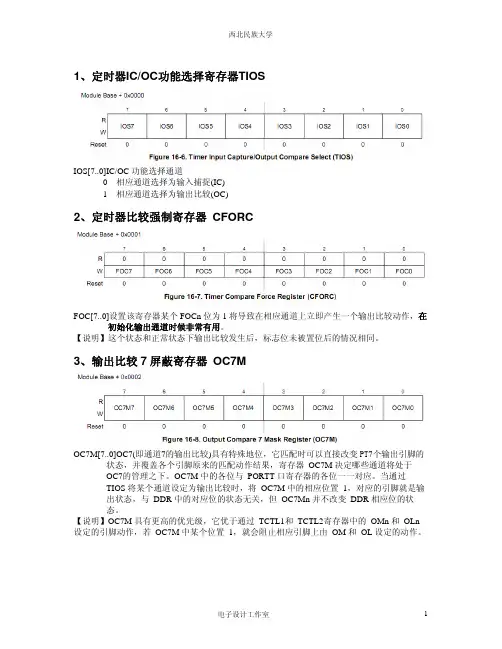

1、定时器IC/OC功能选择寄存器TIOSIOS[7..0]IC/OC功能选择通道0 相应通道选择为输入捕捉(IC)1 相应通道选择为输出比较(OC)2、定时器比较强制寄存器 CFORCFOC[7..0]设置该寄存器某个FOCn位为1将导致在相应通道上立即产生一个输出比较动作,在初始化输出通道时候非常有用。

【说明】这个状态和正常状态下输出比较发生后,标志位未被置位后的情况相同。

3、输出比较7屏蔽寄存器 OC7MOC7M[7..0]OC7(即通道7的输出比较)具有特殊地位,它匹配时可以直接改变PT7个输出引脚的状态,并覆盖各个引脚原来的匹配动作结果,寄存器OC7M决定哪些通道将处于OC7的管理之下。

OC7M中的各位与PORTT口寄存器的各位一一对应。

当通过TIOS将某个通道设定为输出比较时,将OC7M中的相应位置1,对应的引脚就是输出状态,与DDR中的对应位的状态无关,但OC7Mn并不改变DDR相应位的状态。

【说明】OC7M具有更高的优先级,它优于通过TCTL1和TCTL2寄存器中的OMn和OLn设定的引脚动作,若OC7M中某个位置1,就会阻止相应引脚上由OM和OL设定的动作。

4、输出比较7数据寄存器 OC7DOC7D[7..0]OC7M对于其他OC输出引脚的管理限于将某个二进制值送到对应引脚,这个值保存在寄存器OC7D中的对应位中。

当OC7匹配成功后,若某个OC7Mn=1,则内部逻辑将OC7Dn送到对应引脚。

OC7D中的各位与PORTT口寄存器的各位一一对应。

当通道7比较成功时,如果OC7M中的某个位为1,OC7D中的对应位将被输出到PORTT的对应引脚。

【总结】通道7的输出比较(OC7)具有特殊的位置,在OC7Mn和OC7Dn两个寄存器设置以后,OC7成功输出后将会引起一系列的动作。

比如:OC7M0=1,则通道0处在OC7的管理下,在OC7成功后,系统会将OC7D0的逻辑数据(仅限0或者1)反应在PT0端口上。

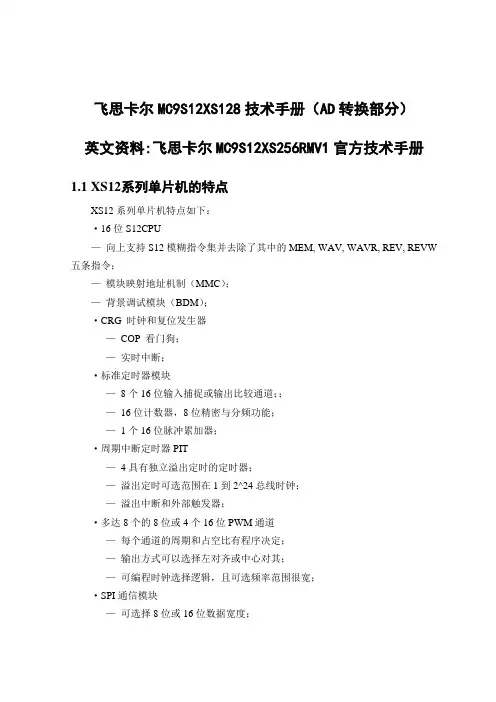

飞思卡尔MC9S12XS128技术手册(AD转换部分)英文资料:飞思卡尔MC9S12XS256RMV1官方技术手册1.1 XS12系列单片机的特点XS12系列单片机特点如下:·16位S12CPU—向上支持S12模糊指令集并去除了其中的MEM, WAV, WAVR, REV, REVW 五条指令;—模块映射地址机制(MMC);—背景调试模块(BDM);·CRG时钟和复位发生器—COP看门狗;—实时中断;·标准定时器模块—8个16位输入捕捉或输出比较通道;;—16位计数器,8位精密与分频功能;—1个16位脉冲累加器;·周期中断定时器PIT—4具有独立溢出定时的定时器;—溢出定时可选范围在1到2^24总线时钟;—溢出中断和外部触发器;·多达8个的8位或4个16位PWM通道—每个通道的周期和占空比有程序决定;—输出方式可以选择左对齐或中心对其;—可编程时钟选择逻辑,且可选频率范围很宽;·SPI通信模块—可选择8位或16位数据宽度;—全双工或半双工通信方式;—收发双向缓冲;—主机或从机模式;—可选择最高有效为先输出或者最低有效位先输出;·两个SCI串行通信接口—全双工或半双工模式·输入输出端口—多达91个通用I/O引脚,根据封装方式,有些引脚未被引出;—两个单输入引脚;·封装形式—112引脚薄型四边引线扁平封装(LQFP);—80引脚扁平封装(QFP);—64引脚LQFP封装;·工作条件—全功率模式下单电源供电范围3.15V到5V;—CPU总线频率最大为40MHz—工作温度范围–40 C到125 C第十章模拟—数字转换10.1 介绍ADC12B16C是一个16通道,12位,复用方式输入逐次逼近模拟—数字转换器。

ATD的精度由电器规格决定。

10.1.1 特点·可设置8位、10位、12位精度·在停止模式下,ATD转换使用内部时钟·转换序列结束后自动进入低耗电模式·可编程采样时间·转化结果可选择左对齐或右对齐·外部触发控制·转换序列结束后产生中断·模拟输入的16个通道为复用方式·可以选择VRH、VRL、 (VRL+VRH)/2特殊转换方式·转换序列长度1到16·可选择连续转换方式·多通道扫描·任何AD通道均可配置外部触发功能,并且可选择4种额外的触发输入。

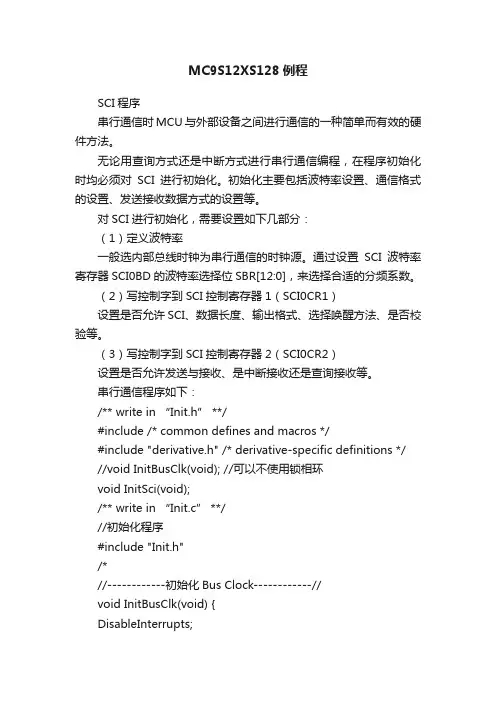

MC9S12XS128例程SCI程序串行通信时MCU与外部设备之间进行通信的一种简单而有效的硬件方法。

无论用查询方式还是中断方式进行串行通信编程,在程序初始化时均必须对SCI进行初始化。

初始化主要包括波特率设置、通信格式的设置、发送接收数据方式的设置等。

对SCI进行初始化,需要设置如下几部分:(1)定义波特率一般选内部总线时钟为串行通信的时钟源。

通过设置SCI波特率寄存器SCI0BD的波特率选择位SBR[12:0],来选择合适的分频系数。

(2)写控制字到SCI控制寄存器1(SCI0CR1)设置是否允许SCI、数据长度、输出格式、选择唤醒方法、是否校验等。

(3)写控制字到SCI控制寄存器2(SCI0CR2)设置是否允许发送与接收、是中断接收还是查询接收等。

串行通信程序如下:/** write in “Init.h” **/#include /* common defines and macros */#include "derivative.h" /* derivative-specific definitions */ //void InitBusClk(void); //可以不使用锁相环void InitSci(void);/** write in “Init.c” **///初始化程序#include "Init.h"/*//------------初始化Bus Clock------------//void InitBusClk(void) {DisableInterrupts;CLKSEL=0X00; //PLLSEL 1 : Bus Clock=PLLCLK/2// 0 : Bus Clock=OSCCLK/2PLLCTL_PLLON=1; //开启PLLSYNR=0; //OSCCLK=16MHzREFDV=0X0F;//PLLCLK=2*OSCCLK*[(1+SYNR)/(1+REFDV]=32/16=2MHz while(!(CRGFLG_LOCK==1)); //直到LOCK=1,when PLL is ready,退出循环CLKSEL_PLLSEL=1; //PLLSEL 1 : Bus Clock=PLLCLK/2=2MHz/2=1MHz// 0 : Bus Clock=OSCCLK/2=16M/2=8MHz}*///---------------初始化SCI---------------//void InitSci(void){SCI0BD=4545; //设波特率为110//SCI baud rate = SCI module clock/(16*SCIBD)=Bus Clock/(16*SCIBD)// = 8MHz/(16*4545)=500kHz/4545=110bps//SCIBD : SBR12-SBR0,Value from 1 to 8191SCI0CR1=0;SCI0CR2=0X2C; // 0010 1100 RIE=1,TE=1,RE=1// RIE=1 RDRF and OR interrupt requests enabled// TE=1 Transmitter enabled// RE=1 Receiver enabled}/** write in “SCI.h” **///函数声明unsigned char SciRead();void SciWrite(byte);/** write in “SCI.c” **///串行通信程序#include "Init.h"#include "SCI.h"//---------------读SCI数据---------------//unsigned char SciRead(){if(SCI0SR1_RDRF==1){//数据从移位寄存器传送到SCI数据寄存器SCIDRL//SCI0SR1_RDRF==1表明数据寄存器SCI0DRL为满,可以接收新的数据SCI0SR1_RDRF=1; //读取SCI数据寄存器会将RDRF清除,重新置位return SCI0DRL; //返回数据寄存器的数值}}//---------------写SCI数据---------------//void SciWrite(byte sci_value){while(!(SCI0SR1&0X80));//SCI0SR1_TDRE==1表明数据寄存器SCI0DRL为空,可以发送新的数据SCI0DRH=0;SCI0DRL=sci_value; //发送新的数据至数据寄存器SCI0DR}//---------------中断程序-----------------//#pragma CODE_SEG NON_BANKEDinterrupt 20 void Sci_Intrrupt(void){ //SCI的中断向量号为20 byte text;DisableInterrupts; //关中断text=SciRead(); //接收数据寄存器SCI0DRL中的数据asm nop;asm nop;SciWrite(text); //发送数据至数据寄存器SCI0DRLDDRA=0XFF; //设A口为输出,用来显示是否执行中断,可以不用PORTA_PA6=!PORTA_PA6;EnableInterrupts; //开中断}#pragma CODE_SEG DEFAULT/** write in “main.c”” **/#include "Init.h"#include "SCI.h"void main(void) {/* put your own code here */_DISABLE_COP(); //关看门狗DisableInterrupts; //关中断//InitBusClk();InitSci();EnableInterrupts; //开中断for(;;) {// _FEED_COP(); /* feeds the dog */} /* loop forever *//* please make sure that you never leave main */}A/D转换应用实例要让ATD 开始转换工作,必须经过以下三个步骤:1.将ADPU 置1,使ATD 启动;2.按照要求对转换位数、扫描方式、采样时间、时钟频率及标志检查等方式进行设置;3.发出启动命令;如果上电默认状态即能满足工作要求,那么只要将ADPU 置1,然后通过控制寄存器发出转换命令,即可实现转换。

PWM工作原理S12微控制器PWM模块是由独立运行的8位脉冲计数器PWMCNT和两个比较寄存器PWMPER和PWMDTY组成。

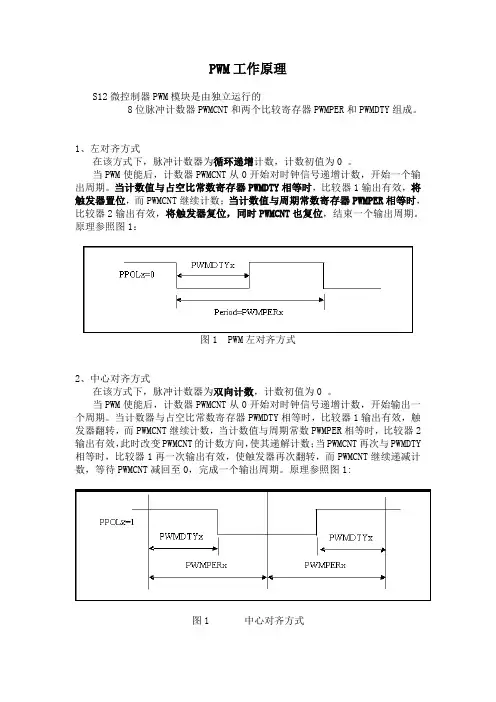

1、左对齐方式在该方式下,脉冲计数器为循环递增计数,计数初值为0 。

当PWM使能后,计数器PWMCNT从0开始对时钟信号递增计数,开始一个输出周期。

当计数值与占空比常数寄存器PWMDTY相等时,比较器1输出有效,将触发器置位,而PWMCNT继续计数;当计数值与周期常数寄存器PWMPER相等时,比较器2输出有效,将触发器复位,同时PWMCNT也复位,结束一个输出周期。

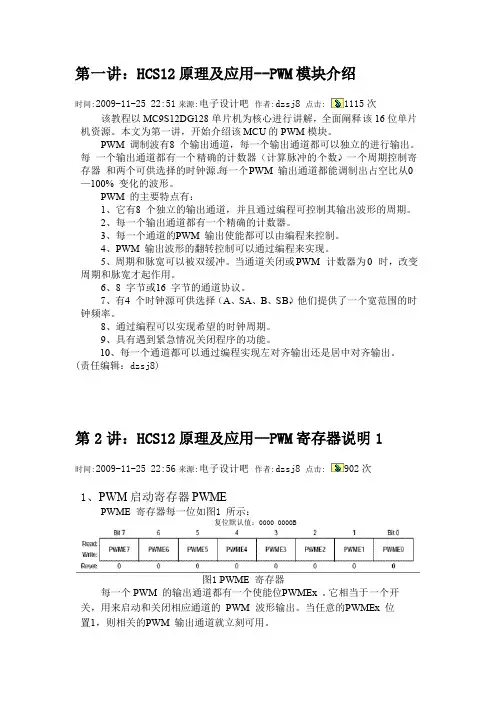

原理参照图1:图1 PWM左对齐方式2、中心对齐方式在该方式下,脉冲计数器为双向计数,计数初值为0 。

当PWM使能后,计数器PWMCNT从0开始对时钟信号递增计数,开始输出一个周期。

当计数器与占空比常数寄存器PWMDTY相等时,比较器1输出有效,触发器翻转,而PWMCNT继续计数,当计数值与周期常数PWMPER相等时,比较器2输出有效,此时改变PWMCNT的计数方向,使其递解计数;当PWMCNT再次与PWMDTY 相等时,比较器1再一次输出有效,使触发器再次翻转,而PWMCNT继续递减计数,等待PWMCNT减回至0,完成一个输出周期。

原理参照图1:图1 中心对齐方式3、周期计算方法左对齐方式:输出周期 = 通道周期× PWMPERx中心对齐方式:输出周期 = 通道周期× PWMPERx × 24、脉宽计算方法左对齐方式:占空比 = [ (PWMPERx - PWMDTYx) / PWMPERx ] × 100%中心对齐方式:占空比 = [ PWMDTYx / PWMPERx ] × 100%S12XS128 【例程】程序描述:由通道PTP3口输出频率为1K,占空比为50%的方波程序如下:#include <hidef.h> /* common defines and macros */#include <mc9s12dg128.h> /* derivative information */#pragma LINK_INFO DERIVATIVE "mc9s12dg128b"/***********初始化函数*************//*时钟初始化程序*/void PLL_Init(void) //PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1){ //锁相环时钟=2*16*(2+1)/(1+1)=48MHzREFDV=1; //总线时钟=48/2=24MHzSYNR=2;while(!(CRGFLG&0x08));CLKSEL=0x80; //选定锁相环时钟}/*PWM初始化程序*/void PWM_Init(void){PWME_PWME3=0x00; // Disable PWM 禁止PWMPRCLK=0x33; // 0011 0011 A=B=24M/8=3M 时钟预分频寄存器设置 PWMSCLA=150; // SA=A/2/150=10k 时钟设置PWMSCLB=15; // SB=B/2/15 =100k 时钟设置PWMCLK_PCLK3=1; // PWM3-----SB 时钟源的选择PWMPOL_PPOL3=1; // Duty=High Time 极性设置PWMCAE_CAE3=0; // Left-aligned 对齐方式设置PWMCTL=0x00; // no concatenation 控制寄存器设置PWMPER3=100; // Frequency=SB/100=1K 周期寄存器设置PWMDTY3=50; // Duty cycle = 50% 占空比寄存器设置PWME_PWME3=1; // Enable PWM 使能}/**********主函数**************/void main(void){PLL_Init();PWM_Init();/* put your own code here */EnableInterrupts;for(;;) {} /* wait forever *//* please make sure that you never leave this function */}增强型定时器模块(ECT)的结构框图如下,ECT功能相当于高速的I/O口,由一个4位预分频器、一个16位自由运行计数器,八个16位IC/OC通道,二个16位脉冲累加器以及一个16位模数递减计数器组成。

Freescale Semiconductor Application Note Document Number: AN3497Rev. 0, 07/2007 Contents1IntroductionThe S12XS family is a next generation, cost competitive MCU solution targeting existing S12 customers and emerging markets. The S12XS family features a power- and code-efficient 16-bit core, on-board data flash(D-flash), an on-board frequency-modulated PLL, and offers flexibility and compatibility with the fully featured S12XE family.Target applications include smart junction boxes, seat controllers, HV AC, low-end engine control, body ECU, RKE receiver, door modules, and steering modules. The S12XS is pin compatible and emulatable with the XE family. Key features of the XE-family that are not included on XS family are: XGATE coprocessor, memory protection unit, and advanced emulated EEPROM functionality. The S12XE and S12XS families give customers flexibility from 64K up to 1M flash and packages from 64LQFP to 208MapBGA.1Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 2Overview of S12XS Family . . . . . . . . . . . . . . . . . . . . . . . 2 3Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33.1P-Flash (Program Flash). . . . . . . . . . . . . . . . . . . . . 33.2D-Flash (Data Flash). . . . . . . . . . . . . . . . . . . . . . . . 43.3RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 4Peripherals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 5Port Integration Module (PIM). . . . . . . . . . . . . . . . . . . . . 6 6Part IDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 7Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7S12XS Family Compatibility Considerationsby:Lela GarofaloTSPGOverview of S12XS FamilyFor additional information on compatibility between S12XE and S12XS families, please refer to the Freescale application note, “Using the S12XE Family as a Development Platform for the S12XS Family,” (document AN3327).This document describes the differences and key similarities between the S12XS family members that must be considered when moving from a larger umbrella device with more memory and a larger package, to a smaller device with less memory and a smaller package.The topics discussed are:•Memory mapping and paging•Peripherals•Port integration module•Part IDs2Overview of S12XS FamilyThis document is meant to be used in conjunction with the S12XS family data sheet located at. Table1 gives an overview of the parts, available peripherals, and package options for each of the family members.Table1. Family FeaturesDevice Package XGATE CAN SPI SCI TIM PIT A/D PWM I/0S12XS256112 LQFPNotAvailable 1128ch4ch1/168ch9180 QFP1128ch4ch1/88ch59 64 LQFP1128ch4ch1/88ch44S12XS128112 LQFP1128ch4ch1/168ch91 80 QFP1128ch4ch1/88ch59 64 LQFP1128ch4ch1/88ch44S12XS64112 LQFP1128ch4ch1/168ch91 80 QFP1128ch4ch1/88ch59 64 LQFP1128ch4ch1/88ch44Memory3MemoryTable 2 gives an overview of the memory sizes available for the S12XS family. Local and global memory maps are compatible across the family. Out of reset, the family has equivalent maps and default values in the memory map control (MMC) registers. For devices with smaller amounts of memory, those areas unimplemented in the map will cause a reset if accessed.3.1P-Flash (Program Flash)The P-flash memory constitutes the main nonvolatile memory for applications. The P-Flash memory iscompatible for all flash devices in the S12XS family for all memory sizes in terms of functionality for program, erase, security, and protection setup. All family members have a single physical flash block that is equivalent to the defined flash size. Table 3 shows the physical flash block sizes in correlation to the global address.Table 2. Memory Sizes by DeviceDevice Flash R OM RAMData Flash9S12XS256256K — 12K 8K 9S12XS128128K — 8K 8K 9S12XS6464K —4K 4K 3S12XS256 —256K 12K — 3S12XS128—128K 8K — 3S12XS64—64K4K—Table 3. Physical P-Flash BlocksGlobal Address S12XS256S12XS128S12XS640x7C_0000256KB Flash BlockUnimplemented Unimplemented0x7D_FFFF 0x7E_0000128KB Flash BlockReserved0x7E_FFFF 0x7F_000064KB Flash Block 1The 9S12XS64 uses the 9S12XS128 die tested only for 9S12XS64 functionality. Accessing flash between address0x7E_0000 through 0x7E_FFFF does not cause an access error reset of device on a S12XS64 device with part ID $C1C0. The PartID register should be verified for the actual device.0x7F_FFFFMemoryFor all flash devices, programming and erase operations will be equivalent. Programming is done in phrases, or four word increments. Erase operations can be done in sectors or blocks. Simultaneous read while write and read while erase from P-flash is not available because there is only one physical block implemented on the 9S12XS family devices.Protection is compatible for all memory sizes of the S12XS family where implemented areas are equivalent.Security is equivalent for all S12XS family devices. The options/security byte is located at global address 0x7F_FF0F.PPAGEs for local memory maps are compatible across all family members where implemented areas are equivalent. Global memory map maps from higher order address down to a lower order address. Accessing unimplemented P-Flash space will cause an access error. An access error will cause the part to reset.3.2D-Flash (Data Flash)D-Flash will be compatible for all 9S12XS family flash devices where implemented areas are equivalent. 9S12XS256 and 9S12XS128 have an equivalent implemented amount of 8K. ROM devices do notimplement data flash. The global memory map maps from a lower order address to a higher order address.The D-flash can be accessed on the local memory map through the 1K DFLASH window through control of the EPAGE register. The EPAGE register has a default value of 0xFE out of reset. EPAGE 0xFE is unimplemented space on the S12XS family. Therefore, when accessing the D-Flash through the 1KD-Flash window, the EPAGE register must be written to with a valid EPAGE. Accessing unimplemented D-Flash space causes an access error. An access error causes the part to reset. Table 4 shows the valid EPAGEs and corresponding global addresses.Table 4. Data FlashEPAGE Global address 9S12XS2569S12X1289S12XS640x000x10_0000 8KB4KB0x10_3FFF 0x010x10_04000x10_7FF 0x020x10_08000x10_0BFF 0x030x10_0C000x10_0FFF 0x040x10_10000x10_13FF 0x050x10_14000x10_17FF 0x060x10_18000X10_1BFF 0x070x10_1C000x10_1FFFPeripherals3.3RAMRAM is compatible for all S12XS family devices where implemented areas are equivalent. Memory maps map from a higher-order address to lower-order address.The RPAGE register allows the user to page 4KB blocks into the RAM page window on the local memory map from address 0x1000 to 0x1FFF. The RPAGE default register value is 0xFD out of reset for all S12XS devices. Also, for all S12XS devices, addresses 0x2000 to 0x3FFF on the local memory map are fixed RAM pages for RPAGEs 0xFE and 0xFF. For the S12XS256, the default value of 0xFD allows for a linear address map to be accessible on the local map between addresses 0x1000 to 0x3FFF. For the S12XS128 and S12XS64 devices, RPAGE 0xFD is unimplemented space, and fixed page 0xFE (0x2000–3FFF) on the S12XS64 is unimplemented space. Accessing unimplemented space will cause an access error and the device to reset. For the S12XS128 and S12XS64, RPAGEs can be accessed through either the fixed RAM space or a valid RPAGE. Table 5 shows the location of RAM out of reset for the XS family.4PeripheralsAll peripherals are functionally compatible across the S12XS family. To maintain compatibility when developing on a larger memory and/or package option to move to a smaller device, pay careful attention to the pin-out and port routing options. A conclusive summary of the pin-outs for all three package options is available in the S12XS family can be found in the product preview, MC9S12XS256PB located at . Refer to table 6 for a complete summary of port routing options.The timer (TIM) module has eight channels available for all three package options. Channels IOC0, IOC1, and ICO2 have port-routing options (see Table 6). For the 80 QFP and 64 LQFP, if all eight PWM channels are used, then TIM channels IOC5 and IOC7 are not available simultaneously.The 112 LQFP has 16 ATD channels available, and all other package options have eight channels. To maintain compatibility when moving to smaller package options, use ATD channels 0–7 only.The pulse-width modulator (PWM) has eight channels available for all three package options. Channels PWM 4–7 have port routing options (see Table 6). PWM4 and PWM6 channels are available only on the 80 QFP and 64 LQFP if the port routing option is used to route to PT4 and PT6. Therefore, if all eight PWM channels are used, then TIM channels IOC5 and IOC7 are not available simultaneously for the 80 QFP and 64 LQFP.Table 5. RAM Global and Local AddressesGlobal Address Local Address RPAGE S12XS256S12XS128S12XS640x0F_D0000x10000xFD 12Kunimplementedunimplemented0x0F_DFFF 0x1FFF 0x0F_E0000x20000xFE 11Accessible through RP AGE window (0x1000 to 0x1FFF) by writing a valid RP AGE value to the RP AGE register.8K0x0F_EFFF 0x2FFF 0x0F_F0000x30000xFF14K0x0F_FFFF0x3FFFPort Integration Module (PIM)The S12XS family has two Serial Communication Interface (SCI) modules, SCI0 and SCI1 for all three package options. SCI1 has additional port routing options available. Refer to table 6 for port routing options.The Serial Peripheral Interface (SPI) has an additional port routing option (see Table 6).5Port Integration Module (PIM)The pin functions and priorities for all S12XS devices are the same after reset or a power-on reset (POR). Port routing options for PWM channels 4–7 and TIM channels 2–0 are controlled by the Port T Routing register (PTTRR). Likewise, port routing options for SCI1 and SPI0 are controlled by the Module Routingregister (MODRR). Table 6 shows the port routing options.6Part IDsFor the 9S12XS family, the part ID is located in two 8-bit registers: PARTIDH and PARTIDL (addresses 0x001A and 0x001B). The read-only value is a unique part ID for each device revision. Table 7 shows the assigned part ID number and mask-set number for each device.Table 6. Peripheral Port Routing Options 11x denotes reset condition, o denotespossible rerouting under software control.S C I 1S P I 0P W MT I M PM[1:0]o PM[5:2] o PP[2,0]o PP[2:0] o PP[7:4] x PS[3:2]x PS[7:4] x PT[2,0] x PT[7:4]oTable 7. Part IDsDevice Mask Set NumberPart ID MC9S12XS2560M05M $C0C0MC9S12XS1280M04M $C1C0MC9S12XS640M04M 1The 9S12XS64 uses the 9S12XS128 die tested for 9S12XS64 functionality only. An actual 9S12XS64 device may be done at a later time. A productchange notification will be posted in such an event. The PartlD register should be verified for actual device.$C1C0TBD$C2C0Summary 7SummaryThe key differences between the devices in the S12XS family are memory mapping. Although many of the peripherals are compatible, you should focus on the default pin/port-routing aspects of the specific peripherals to enable maximum scalability with anticipated future system needs. Part IDs are specific to each device. The S12XS64 device is a special case; any errata differences should be verified and associated to the corresponding part ID.This document is meant to be used with:•MC9S12XS Family Reference Manual•MC9S12XS Family Product Brief (document MC9S12XS256PB)•S12XCPUV2 Reference Manual (document S12XCPUV2)Document Number: AN3497Rev. 007/2007How to Reach Us:Home Page:Web Support:/support USA/Europe or Locations Not Listed:Freescale Semiconductor, Inc.Technical Information Center, EL5162100 East Elliot Road Tempe, Arizona 85284+1-800-521-6274 or +/supportEurope, Middle East, and Africa:Freescale Halbleiter Deutschland GmbH T echnical Information Center Schatzbogen 781829 Muenchen, Germany +44 1296 380 456 (English)+46 8 52200080 (English)+49 89 92103 559 (German)+33 1 69 35 48 48 (French)/supportJapan:Freescale Semiconductor Japan Ltd.Headquarters ARCO T ower 15F1-8-1, Shimo-Meguro, Meguro-ku,T okyo 153-0064Japan0120 191014 or +81 3 5437 9125support.japan@Asia/Pacific:Freescale Semiconductor Hong Kong Ltd.T echnical Information Center 2 Dai King StreetT ai Po Industrial Estate T ai Po, N.T., Hong Kong +800 2666 8080@For Literature Requests Only:Freescale Semiconductor Literature Distribution Center P .O. Box 5405Denver, Colorado 802171-800-441-2447 or 303-675-2140Fax: 303-675-2150LDCForFreescaleSemiconductor@Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. “Typical” parameters that may beprovided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals”, must be validated for each customer application by customer’s technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended orunauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that FreescaleSemiconductor was negligent regarding the design or manufacture of the part. RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-freecounterparts. For further information, see or contact your Freescale sales representative.For information on Freescale’s Environmental Products program, go to /epp .Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.© Freescale Semiconductor, Inc. 2007. All rights reserved.。

单片机课程设计报告题目:对可调光LED灯发光强度进行控制学院:机电工程学院班级:自09A-1姓名:学号:0910101011指导教师:一、设计任务:1、单片机可选用飞思卡尔型。

2、按键及显示方案可采用CH451芯片或其他方案。

3、设计并制作可调光LED灯,并对发光强度进行控制。

二、设计方案:硬件选择:飞思卡尔MC9S12S128系类单片机,驱动模块,LED 模块,CH4541模块;工作原理:通过调节PWM为1KHz至10KHz TTL方波,调节其占空比,从而调节电压,决定了发光强度。

MC9S12S128部分管脚图:MC9S12S128主要系统参数:S12X CPU,最高总线速度 40MHz64KB、128KB和256KB 闪存选项,均带有错误校正功能(ECC) 带有ECC的、4KB至8KB DataFlash,用于实现数据或程序存储配置8 、10或12位模数转换器(ADC),转换时间3μ s支持控制区域网(CAN)、本地互联网(LIN)和串行外设接口(SPI)协议模块带有16-位计数器的、8-通道定时器出色的EMC,及运行和停止省电模式1、由于MC9S12S128自带有AD以及PWM 功能,所以对软件的要求交简单。

2、键盘输入采用CH451整体模块3、通信端口为PA口,与中断端口三、硬件结构:CH451硬件电路结构驱动模块设计四、软件设计4.1 HCS12控制软件主要理论智能车开发环境采用了飞思卡尔HCS12系列单片机开发软件CodeWarrior。

该软件具有支持多种语言、开发环境界面统一、交叉平台开发以及支持插件工具等特点。

在CodeWarrior界面完成编译后,通过BDM FOR S12工具,在CodeWarrior环境下向MC9S12模块下载程序。

BDM FOR S12工具使用简单,十分方便。

在整个系统设计中,用到了4个单片机基本功能模块:时钟模块、PWM输出模块、AD转换模块、。

通过编写程序先对所用到的模块进行初始化,并通过对相应数据寄存器或状态寄存器的读写,实现期望的功能。

MC9S12XS128 单片机简介1、HCS12X 系列单片机简介Freescale 公司的16 位单片机主要分为HC12 、HCS12、HCS12X 三个系列。

HC12核心是16 位高速CPU12 核,总线速度8MHZ;HCS12 系列单片机以速度更快的CPU12 内核为核心,简称S12 系列,典型的S12 总线速度可以达到25MHZ。

HCS12X 系列单片机是Freescale 公司于2005 年推出的HCS12 系列增强型产品,基于S12 CPU 内核,可以达到25MHz 的HCS12 的2-5 倍性能。

总线频率最高可达40 MHz。

S12X 系列单片机目前又有几个子系列:MC9S12XA 系列、MC9S12XB 系列、MC9S12XD 系列、MC9S12XE 系列、MC9S12XF系列、MC9S12XH 系列和MC9S12XS 系列。

MC9S12XS128 就是S12X 系列中的一个成员。

2、MC9S12XS128 性能概述MC9S12XS128 是16 位单片机,由16 位中央处理单元(CPU12X)、128KB 程序Flash(P-lash)、8KB RAM、8KB 数据Flash(D-lash)组成片内存储器。

主要功能模块包括:内部存储器内部PLL 锁相环模块2 个异步串口通讯SCI1 个串行外设接口SPIMSCAN 模块1 个8 通道输入/输出比较定时器模块TIM周期中断定时器模块PIT16 通道A/D 转换模块ADC1 个8 通道脉冲宽度调制模块PWM输入/输出数字I/O 口3、输入/输出数字I/O 口MC9S12XS128 有3 种封装,分别为64 引脚、80 引脚、112 引脚封装。

其全名分别为MC9S12XS128MAE、MC9S12XS128MAA、MC9S12XS128MAL。

MC9S12XS 系列具有丰富的输入/输出端口资源,同时集成了多种功能模块,端口包括PORTA、PORTB、PORTE、PORTK、PORTT、PORTS、PORTM、PORTP、PORTH、PORTJ 和PORTAD 共11 个端口。

第一讲:HCS12原理及应用--PWM模块介绍时间:2009-11-25 22:51来源:电子设计吧作者:dzsj8 点击:996次该教程以MC9S12DG128单片机为核心进行讲解,全面阐释该16位单片机资源。

本文为第一讲,开始介绍该MCU的PWM模块。

PWM 调制波有8个输出通道,每一个输出通道都可以独立的进行输出。

每一个输出通道都有一个精确的计数器(计算脉冲的个数),一个周期控制寄存器和两个可供选择的时钟源。

每一个P WM 输出通道都能调制出占空比从0—100% 变化的波形。

PWM 的主要特点有:1、它有8个独立的输出通道,并且通过编程可控制其输出波形的周期。

2、每一个输出通道都有一个精确的计数器。

3、每一个通道的P WM 输出使能都可以由编程来控制。

4、PWM 输出波形的翻转控制可以通过编程来实现。

5、周期和脉宽可以被双缓冲。

当通道关闭或PWM 计数器为0时,改变周期和脉宽才起作用。

6、8 字节或16 字节的通道协议。

7、有4个时钟源可供选择(A、SA、B、SB),他们提供了一个宽范围的时钟频率。

8、通过编程可以实现希望的时钟周期。

9、具有遇到紧急情况关闭程序的功能。

10、每一个通道都可以通过编程实现左对齐输出还是居中对齐输出。

第2讲:HCS12原理及应用--PWM寄存器说明1时间:2009-11-25 22:56来源:电子设计吧作者:dzsj8 点击:794次1、PWM启动寄存器PWMEPWME 寄存器每一位如图1所示:复位默认值:0000 0000B图1 PWME 寄存器每一个PWM 的输出通道都有一个使能位P WMEx 。

它相当于一个开关,用来启动和关闭相应通道的PWM 波形输出。

当任意的P WMEx 位置1,则相关的P WM 输出通道就立刻可用。

用法:PWME7=1 --- 通道7 可对外输出波形PWME7=0 --- 通道7 不能对外输出波形注意:在通道使能后所输出的第一个波形可能是不规则的。

MC9S12XS简介1.1 S12XS介绍新16位微控制器S12XS的系列是一个兼容,减少版本的S12XE系列。

这个系列提供了一种简便的方法开发从低端到高端化应用程序的通用平台,减少硬件和软件的设计。

12XS系列提供32位的所有优势和效率性能的16位MCU,同时保持低成本,低功耗,EMC和代码大小目前享有的效率优势。

S12XS系列运行在等待状态的情况下为所有外围设备和存储器16位宽访问。

该S12XS系列有112引脚LQFP封装,80引脚QFP,64引脚LQFP封装选择,与S12XE系列高度兼容。

除了在每个模块提供I / O端口外,还有多达18个具有从停止或等待模式被唤醒的中断功能的I / O端口。

外围设备包括MSCAN,SPI,两个SCIs,一个8通道24位定时器周期中断,8 -通道16位定时器,8通道PWM,高达16 通道12位AD转换器。

1.1.1特性16位CPU12XS-向上兼容S12指令集,除了删除五个模糊指令(MEM,WAV ,WAVR,REV,REVW)-增强索引寻址-获取大量数据段独立PPAGEINT(中断模块)- 7个级别的嵌套中断-灵活的分配中断源到每个中断的层次。

-外部非屏蔽高优先级中断(XIRQ)-下面的输入可以作为唤醒中断- IRQ和非屏蔽XIRQ-CAN总线接收引脚-SCI接收引脚-根据不同的封装选择了20针在端口J,H和P的上升或下降沿敏感的配置MMC管理(模块映射控制)DBG(调试模块)-监测与标签的CPU总线型或力量型断点要求- 64 × 64位循环跟踪缓冲区的捕捉改变流或内存访问信息BDM(背景调试模式)OSC_LCP(振荡器)-低功率的闭环控制皮尔斯振荡器利用一个4MHz至16MHz石英晶体振荡器-良好的抗干扰-全摆幅皮尔斯选择利用一个2MHz至40MHz的晶振-根据跨导最佳启动的边缘典型晶体IPLL(内部过滤,调频锁相回路时钟发生器)-无需外部元件-可配置选项为减少传播EMC辐射(频率调制谱)CRG(时钟和复位产生)-看门狗-实时中断-时钟监视器-快速唤醒自我的停止时钟模式内存选项-64K,128K的和256K字节的闪存-闪存的基本特征- 64位数据加上8位并发ECC(纠错码),允许单个位失败校正和双故障检测-擦除扇区大小1024字节-自动编程和擦除算法-保护计划,以防止意外编程或擦除-安全选项,以防止未经授权的访问- 4K和8K字节数据闪存空间- 16位数据加上6位并发ECC(纠错码),允许单个位失败校正和双故障检测-擦除扇区大小256字节-自动编程和擦除算法- 4K,8K与第12K字节RAM16通道,12位模拟数字转换器- 8/10/12位分辨率- 3微秒,10位单次转换时间-左或右对齐结果数据-外部和内部转换触发功能-内部振荡器在停止模式转换-唤醒从模拟比较低功耗模式-连续转换模式- 16路模拟输入通道-多通道扫描-管脚也可以作为数字I / OMSCAN(1Mbit/s,CAN2.0的A,B软件兼容模块)- 1兆位每秒,CAN2.0的A,B软件兼容模块-标准和扩展数据帧- 0 - 8个字节数据的长度-可编程的比特率高达1 Mbps-五接收FIFO的存储方案缓冲区-三优先发送内部缓冲区-灵活的标识验收滤波器可编程为:- 2 x 32位- 4 x 16位- 8 × 8位-唤醒集成了低通滤波器的选择-环回自检-只能收听到CAN总线监控-16位发送/接收信息时间戳TIM(标准定时器模块)- 8 × 16的输入捕捉或输出比特的通道比较- 16位自由运行计数器的8位精度预分频器- 1个16位脉冲累加器PIT(周期性中断定时器)-多达4个独立的定时器超时周期-超时期限为1至224总线时钟周期选择-超时中断和周边触发器-定时器开始可以对齐高达8通道× 8位或4通道x 16位脉宽调制器-每通道占空比和周期都是可编程的-中心或左对齐输出-可编程时钟选择逻辑的和频率范围串行外设接口模块(SPI)-可设置为8位或16位数据的大小-全双工或单线双向-双缓冲的发送和接收-主或从模式-最高位先或LSB先移-串行时钟相位和极性选择两个串行通信接口(SCI)-全双工或单线运行-标准标记/空间不返回到归零(NRZ)格式-可选的IrDA 1.4返回到零反转(RZI)可编程脉冲宽度格式- 13位波特率选择-可编程的字符长度-可编程极性的发射机和接收机-接收唤醒的积极边缘-间隔检测和传输冲突检测支持片上电压调节器-两个平行的,与带隙基准的线性稳压器-低电压检测(LVD)认证的低电压中断(LVI)号-上电复位(POR)电路-低电压复位(LVR)的低功耗唤醒定时器(API)的-内部振荡器驾驶递减计数器-微调到+ / -10%的准确度-超时时间为0.2ms的范围内,从同一个0.2ms〜13秒的决议输入/输出-最多91个通用输入/输出(I / O)引脚取决于封装选择和2个输入专用管脚-磁滞和可配置上拉/下拉输入引脚上的所有设备-在所有输出引脚可配置驱动力量封装选择- 112引脚小外形四方扁平封装(LQFP封装)- 80引脚四方扁平封装(QFP)- 64引脚小外形四方扁平封装(LQFP封装)操作条件-宽单电源电压范围3.135 V至5.5 V的全性能-单独的电源内部电压调节器和I / O优化的EMC滤波容许- 40MHz的最大CPU总线频率-环境温度范围:-40°C至125°C-温度选项:- -40°C至85°C- -40°C至105°C- -40°C至125°C1.1.2 工作模式模式种类:正常的单芯片模式特别的单主动背景调试模式芯片模式1.1.3 信号的详细说明1.1.3.1 EXTAL,XTAL - 振荡器引脚EXTAL和XTAL是晶体驱动和外部时钟引脚。