并口编程

- 格式:pdf

- 大小:397.78 KB

- 文档页数:12

基于fpga的ad9268的并口读数据的代码1. 引言1.1 概述本文基于FPGA设计了一种并口读取数据的方案,该方案可以与AD9268芯片实现接口通信。

通过该方案,我们可以在FPGA平台上高效地读取AD9268芯片采集的数据。

1.2 文章结构本文共分为五个部分进行阐述。

首先,引言部分将介绍文章的背景和目的。

其次,AD9268简介部分将对AD9268芯片及其功能进行介绍,以及FPGA与AD9268之间接口通信的原理和并口读取数据的需求背景。

然后,在基于FPGA的AD9268并口读取数据设计方案中,将详细说明选择和搭建FPGA硬件平台、设计与实现AD9268数据读取流程、优化技术研究等内容。

随后,在实验与结果分析部分,将展示实验环境搭建与参数设置,并对AD9268并口读取数据性能测试结果进行详细分析,并评估优化方法对性能提升的影响。

最后,在结论与展望部分总结研究成果,并提出存在问题与改进方向以及未来发展趋势展望。

1.3 目的本文旨在针对AD9268芯片,并基于FPGA设计一种高效的并口读取数据的方案。

通过深入研究AD9268芯片的功能,对FPGA与AD9268之间的接口通信原理进行分析,并提出一种针对并口读取数据需求背景下的设计方案。

通过实验和结果分析,验证了该方案的可行性,并从优化方法的角度评估了其对性能提升的影响。

最后,总结研究成果,指出存在问题并提出改进方向,并展望了未来在该领域的发展趋势。

2. AD9268简介:2.1 AD9268芯片功能:AD9268是一款高性能、12位模数转换器(ADC)芯片,采用并行接口与FPGA 进行通信。

它具有较高的分辨率和采样速率,并且适用于广泛的模拟输入信号范围。

该芯片内置了功耗优化的电源管理电路,并提供了多种工作模式,以满足不同应用场景的需求。

2.2 FPGA与AD9268接口通信的原理:在FPGA与AD9268之间建立稳定可靠的通信通道是实现并口读取数据的关键。

并口编程器制作全过程-以后大家大胆的折腾BIOS吧!!这个教程本来打算在五一期间就做出来的,无奈哥们我五一冒着30度高温去电子市场的时候,人家也停业休息,上周去电子市场把材料买齐,这不,今天趁老婆上班,就窝在家里制作教程喽制作之前的准备:1工具:电烙铁万用表焊锡斜口钳美工刀(工具我就不上相片了)2材料:面包板一块芯片紧锁座一个并口头一个电阻电容若干(参考电路图)PNP(加菲我用的A1015)三极管一个4007三极管三个(用于串联实现将5V降为3.3V).也可直接使用AMS11173.3V稳压管,可直接将5V转换为3.3V(注:并非所有1117芯片都是3.3V稳压管,也有1.8V的,一般芯片上有标明)如下图,当AMS1117(左下角标明是3.3V的稳压管)这次放置时,左边脚为GND(接地,0V),中间脚为3.3V输出,最右边为电源输入(接USB 5V)当用AMS1117取代电路图中三个二级管时,只需将USB 5V接1117最右边脚,将原电路图中3个二极管之后电路接1117中间,1117最左边接地即可。

下面是其它的工具,地上太乱,就放床上拍照了器材:奥林巴斯FE-290 [奥林巴斯数码相机]时间:2011-04-21 06:23:50 快门:1/30 光圈:F/2.7 焦距:4毫米感光度:1253电路图一张:(我那个贴子里面有一个多功能编程器,图纸相对复杂,部分兄弟可能感觉制作起来有点难度,我就示范制作这个25类编程器吧)至此,工具,材料,图纸都已准备就绪了,现在开始正式制作。

用斜口钳将并口头的外壳固定脚修整,将25个针脚重新排位,固定焊接在万用板上器材:奥林巴斯FE-290 [奥林巴斯数码相机]时间:2011-04-23 02:52:28 快门:1/25 光圈:F/2.7 焦距:4毫米感光度:125这张是正面的,固定得还不错吧?上面的那个小贴片的芯片就是1117 3.3V稳压芯片,用它可获得更精确的电压。

用C#操作IO端口1-用并口控制发光二极管作者: Levent S. 翻译:Aweay为什么要写这篇文章,不可否认,用C#编写这类程序不是非常合适的, 相信来CSDN的很多朋友都能用其他语言轻松编写这样的程序, 不过如果有一天你的.net的项目里有这样的需求, 那么这篇文章或许就适合你了.什么是端口?端口包含了一系列信号线, 通过这个端口CPU可以同其他外部设备交换数据, 比如我们经常见到的Modem,打印机等.通常情况下, 打开的信号是”1”, 关闭的信号是”0”. 并口在同一时间内可以发送8位的数据, 接收5位的数据. 而串口RS-232则只能发送1位数据, 但串口是多向的, 所以在同一时刻既可以发送也可以接收.什么是RS-232RS-232(ANSI/EIA-232标准)是IBM-PC及其兼容机上的串行连接标准。

可用于许多用途,比如连接鼠标、打印机或者Modem,同时也可以接工业仪器仪表。

用于驱动和连线的改进,实际应用中RS-232的传输长度或者速度常常超过标准的值。

RS-232只限于PC串口和设备间点对点的通信。

RS-232串口通信最远距离是50英尺。

\ 1 2 3 4 5 /\ 6 7 8 9 /从计算机连出的线的截面。

RS-232针脚的功能:数据:TXD(pin 3):串口数据输出RXD(pin 2):串口数据输入握手:RTS(pin 7):发送数据请求CTS(pin 8):清除发送DSR(pin 6):数据发送就绪DCD(pin 1):数据载波检测DTR(pin 4):数据终端就绪地线:GND(pin 5):地线其他RI(pin 9):铃声指示RS232 通讯原理? RS485通讯原理?RS-232是串行数据接口标准,最初都是由电子工业协会(EIA)制订并发布的,RS-232在1962年发布,命名为EIA-232-E,作为工业标准,以保证不同厂家产品之间的兼容。

RS-422由RS-232发展而来,它是为弥补RS-232之不足而提出的。

8080并口时序

8080并口时序是一种用于输入输出数据的接口,常用于计算机与外部

设备之间的数据传输。

在该时序中,CPU与并口之间通过多根数据线,控制线以及时钟线进行数据的传输和控制。

8080并口的时序如下:

1. 起始信号:CPU向并口发送起始信号,表示即将开始进行数据传输。

2. 地址线传输:CPU将需要读取或写入的设备地址信息发送给并口,

以确定目标设备。

3. 控制信号传输:CPU向并口发送控制信号,包括读(Read)和写(Write)信号,用于区分数据的读写操作。

4. 数据线传输:CPU将需要读取或写入的数据通过数据线发送给并口,或者从并口读取数据放入数据线中。

5. 状态确认:并口接收到数据后,通过状态线向CPU发送确认信号,

表示数据已成功传输或接收。

6. 结束信号:数据传输完成后,CPU向并口发送结束信号,表明数据

传输结束。

在8080并口时序中,通过这些步骤可以实现计算机与外部设备之间的

数据传输,从而实现各种输入输出操作。

通过合理的控制和管理,能

够高效地完成数据的读取和写入操作,满足计算机与外部设备之间的

数据交互需求。

stm32并口数据处理方法

STM32并口数据处理方法是指使用STM32芯片的并口接口进行数据处理的方法。

并口接口是一种并行接口,可以同时传输多个数据位,速度快,但是需要使用更多的引脚。

在STM32芯片中,并口接口可以用于连接外部设备,如LCD屏幕、按键等。

在STM32并口数据处理中,首先需要配置并口接口的引脚和模式。

然后可以使用STM32提供的库函数或者自己编写的代码来读取或写

入数据。

对于读取数据,可以使用GPIO端口读取数据,也可以使用

外部中断或DMA等方式。

对于写入数据,可以使用GPIO端口输出数据,也可以使用TIM等定时器输出数据。

在实际应用中,可以根据具体的需求选择不同的数据处理方法。

例如,可以使用GPIO端口进行简单的输入输出操作,也可以使用外

部中断进行多任务处理。

对于需要高速数据传输的应用,可以使用DMA方式进行数据传输。

总之,STM32并口数据处理方法是一种灵活、高效的数据处理方式,可以满足不同的应用需求。

通过对STM32并口接口的深入理解和熟练应用,可以提高开发效率,实现更为复杂的应用功能。

- 1 -。

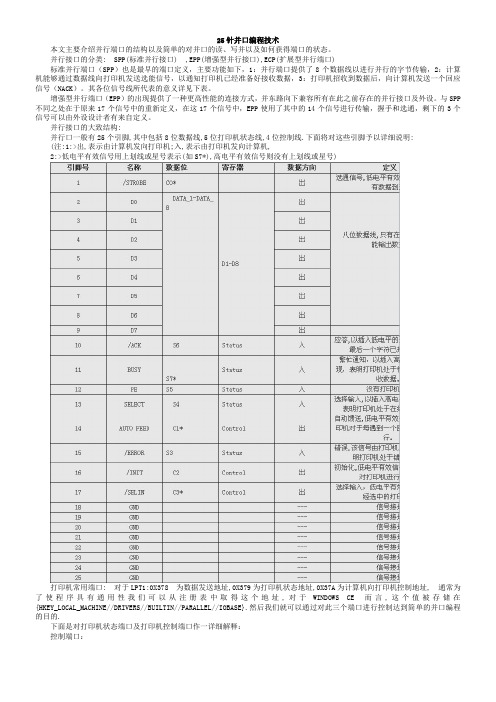

25针并口编程技术本文主要介绍并行端口的结构以及简单的对并口的读、写并以及如何获得端口的状态。

并行接口的分类: SPP(标准并行接口) ,EPP(增强型并行接口),ECP(扩展型并行端口)标准并行端口(SPP)也是最早的端口定义,主要功能如下,1:并行端口提供了8个数据线以进行并行的字节传输,2:计算机能够通过数据线向打印机发送选能信号,以通知打印机已经准备好接收数据,3:打印机招收到数据后,向计算机发送一个回应信号(NACK)。

其各位信号线所代表的意义详见下表。

增强型并行端口(EPP)的出现提供了一种更高性能的连接方式,并东路向下兼容所有在此之前存在的并行接口及外设。

与SPP 不同之处在于原来17个信号中的重新定义,在这17个信号中,EPP使用了其中的14个信号进行传输,握手和选通,剩下的3个信号可以由外设设计者有来自定义。

并行接口的大致结构:并行口一般有25个引脚,其中包括8位数据线,5位打印机状态线,4位控制线.下面将对这些引脚予以详细说明:(注:1:>出,表示由计算机发向打印机;入,表示由打印机发向计算机,2:>低电平有效信号用上划线或星号表示(如S7*),高电平有效信号则没有上划线或星号)打印机常用端口: 对于LPT1:0X378 为数据发送地址,0X379为打印机状态地址,0X37A为计算机向打印机控制地址, 通常为了使程序具有通用性我们可以从注册表中取得这个地址,对于WINDOWS CE 而言,这个值被存储在{HKEY_LOCAL_MACHINE//DRIVERS//BUILTIN//PARALLEL//IOBASE}.然后我们就可以通过对此三个端口进行控制达到简单的并口编程的目的.下面是对打印机状态端口及打印机控制端口作一详细解释:控制端口:这个0x37A计算机控制打印机的地址,可以产生对打印机进行控制的必要信号,可写,两高位(7和8)没什么用,第6位写1表示可以向并口输出数据。

并行接口程序设计本章介绍在Windows 2000/XP下的并行接口的程序设计方法,分析一下目前进行并行接口编程的方法,可以归纳为几种:•DLL直接I/O方式:应用程序通过一个可以进行端口I/O访问的DLL接口软件实现对并行接口的访问,即通过调用第三方DLL接口软件中的I/O端口读写函数实现对并行口的寄存器的读写。

这样的软件很多,像WinIo、Inpout32、TVicPort等;•Active X控件直接I/O方式:通过一个提供Active X控件实现对端口的直接I/O访问,一般控件的方式采用VB编程比较简单。

这样的软件包括Inpout32、TVicPort等;•并行接口专用接口软件:使用这一类软件对并行接口编程要比上2种方法简单,有些软件支持中断。

这样的软件如TVicLPT。

•自己编写驱动程序:直接在VC++环境下通过Windows 2000 DDK或Windows XP DDK编写驱动程序,这是一种最灵活的方法,但编程的难度比较大。

5.1 实现直接I/O方式的软件并行接口的编程在不同的操作系统下采取不同的方法,在DOS和Windows95之前的操作系统下,可以直接对端口进行读写,根据并行接口的不同模式的寄存器进行读写操作就可以完成各种模式的接口编程。

在目前的Windows 2000/XP操作系统下,不能直接对端口寄存器进行访问,这是由于Windows2000/XP对系统底层操作采取了屏蔽的策略,对用户而言,系统变得更为安全,但这却给接口和接口软件开发人员带来了不小的困难,因为只要应用程序中涉及到底层的操作,开发人员就不得不深入到Windows的内核去编写属于系统级的设备驱动程序。

对并行口的读写操作就是如此,由于Windows对系统的保护,应用程序不允许直接I/O操作。

在Windows2000/XP操作系统下,正规的接口程序的编程方法是采取驱动程序的开发方法。

由于驱动程序需要与操作系统最底层进行交互,因此不同的操作系统的底层结构对应不同的设备驱动程序模型。

实验八8255A可编程并行接口实验一、实验项目用8255A可编程并行接口芯片,重复实验四的内容。

PA口作为显示输出口,PB口作为开关量输入口。

二、实验目的1.了解8255A芯片的结构及编程方法2.掌握通过8255A并行接口读取开关数据的方法三、实验原理设置好8255A各端口的工作模式:三个端口都工作于方式0,PA口作为显示输出口,PB口作为开关量输入口。

四、实验连线8255A的PA0PA7接发光二极管L1L8,PB0PB7接开关K1K8,片选信号CS8255接CS0。

五、实验电路六、程序框图七、参考程序CSEG AT 0000HLJMP START开始置控制字从B通道读入开关状态从A通道输出到发光二极管延时一段时间.23.CSEG AT 4100HPA EQU 0CFA0HPB EQU HPCTL EQU HSTART: MOV DPTR, #PCTL ;置8255A控制字,A、B、C口均工作MOV A, # H ;方式0,A、C口为输出,B口为输入MOVX @DPTR, ALOOP: MOV DPTR, #PB ;从B口读入开关状态值MOVX A,MOV DPTR, #PA ;从A口将状态值输出显示MOVX , AMOV R7, #10H ;延时DEL0: MOV R6, #0FFHDEL1: DJNZ R6,DJNZ R7,LJMP LOOPEND八、问题思考试分析改置8255A控制字,A、B、C口工作方式1,B、C口为输出,A口为输入,可不可以。

.24.。

敬请登录网站在线投稿2018年第2期9F PG A的虚拟J T A G技术对并口F L A S H快速编程丁峰平,陈莉萍(诺基亚上海贝尔股份有限公司,杭州310053)摘要:集成数字电路板上经常有F L A S H器件需要编程,在工厂批量生产中往往要占据较多时间㊂特别是对于挂载在可编程器件(F P G A)的并行接口的F L A S H,使用边界扫描的方法靠移位数据来仿真F L A S H读写时序,从而完成F L A S H 器件编程的方法相当低效费时㊂应用了虚拟J T A G技术后,就不需要进行整个边界引脚的移位处理,可以一次性从J T A G链上加载较大的数据块,再配合并口F L A S H的接口逻辑进行编程,有效地提高了效率㊂关键词:F P G A;边界扫描;虚拟J T A G;并口F L A S H中图分类号:T P311文献标识码:AF a s t P a r a l l e l F L A S H P r o g r a m m i n g B a s e d o n V i r t u a l J T AG i n F P G AD i n g F e n g p i n g,C h e n L i p i n g(N o k i a S h a n g h a i B e l l C o.,L t d.,H a n g z h o u310053,C h i n a)A b s t r a c t:T h e r e i s a l w a y s p a r a l l e l F L A S H t o b e p r o g r a mm e d o n P CB i n f a c t o r y.T h e p r o g r a mm i n g t a k e s m u c h t i m e d u r i n g t h e m a s s p r o d u c t i o n,e s p e c i a l l y f o r F L A S H w h i c h i s m o u n t e d o n t h e p a r a l l e l i n t e r f a c e o f p r o g r a mm a b l e d e v i c e(F P G A).T h e m e t h o d o f u s i n g b o u n d a r y s c a n i s u s e d t o s i m u l a t e F L A S H r e a d a n d w r i t e,w h i c h i m p l e m e n t e d b y b i t s h i f t i n g t h r o u g h a l l t h e b o u n d a r y c e l l s i s c o n s u-m i n g.A f t e r t h e v i r t u a l J T A G t e c h n o l o g y i s a p p l i e d,t h e d i s p l a c e m e n t o f t h e e n t i r e b o u n d a r y p i n i s n o t r e q u i r e d,b e c a u s e t h e v i r t u a l J T A G c o r e c a n r e c e i v e m a s s i v e d a t a f r o m J T A G c h a i n w i t h i n o n e t i m e.A n d p r o g r a mm i n g w i t h t h e i n t e r f a c e l o g i c o f F L A S H,t h e e f f i c i e n c y i s i m p r o v e d.K e y w o r d s:F P G A;B o u n d a r y S c a n;v i r t u a l J T A G;p a r a l l e l F L A S H引言联合测试行动小组(J o i n t T e s t A c t i o n G r o u p,J T A G)边界扫描(B o u n d a r y S c a n)是I E E E1149.1标准,其接口在大量的数字芯片中集成,方便调试和编程㊂集成电路板上一般将各个芯片的J T A G接口串接起来形成菊花链,这样可以通过J T A G工具进行统一的自动化操作㊂F L A S H 存储芯片往往挂载在具有J T A G接口的芯片的总线上,这样在工厂进行大规模生产时,可以通过J T A G链对F L A S H芯片进行编程㊂1J T A G接口简介J T A G接口一般有4个信号,分别为测试数据输入(T D I)㊁测试数据输出(T D O)㊁测试时钟(T C K)㊁测试模式选择(TM S),测试复位信号(T R S T)是可选的㊂TM S㊁T C K连入芯片内部的测试接入端口(T A P),T D I串接到芯片引脚的边界扫描单元(B S)上,这些单元串接后通过T D O连出芯片㊂T A P控制器在T C K触发下通过一系列的TM S信号进行状态机的改变,这些状态包括:C a p t u r e D R(得到当前数据寄存器的内容),S h i f t D R(对数据寄存器进行数据移位,从T D I移入,T D O移出),U p d a t e D R (更新当前数据寄存器的内容),C a p t u r e I R(得到当前数据指令寄存器的内容),S h i f t I R(对指令寄存器进行数据移位,从T D I移入㊁T D O移出),U p d a t e I R(更新当前指令寄存器的内容)㊂I R和D R一起进行边界扫描单元的控制,比如当I R 是全1时,一般对应的功能是测试数据直通输出(通过1比特的移位寄存器B y p a s s R e g i s t e r)㊂还可以控制引脚数据是从内部逻辑得到还是扫描单元得到,扫描单元的数据是从引脚输入还是输出到引脚上,从而实现特定的J T A G 动作(如图1所示)㊂2F L A S H器件的编程集成电路板上的F L A S H器件一般挂载在具有J T A G接口的芯片上,在批量生产中往往需要通过J T A G 烧写一个小的引导程序或数据文件,大小从几十K B到几M B不等㊂传统的边界扫描方式是依次将数据串行移位到芯片10M i c r o c o n t r o l l e r s &E m b e d d e d S ys t e m s 2018年第2期w w w .m e s n e t .c o m .c n图1 T A P 控制器原理框图的扫描单元(B S )里,准备好各个数据线(d a t a)㊁地址线(a d d r e s s )㊁片选线(c s )㊁读写使能线(w r )㊁输出使能(o e)㊁编程使能(AW ),接线如图2所示㊂图2 F L A S H 连接图因为每次移位都需要遍历芯片的所有B S,一次数据的准备需要额外的开销,所以这种方式的编程十分低效,只能用来烧写小块的程序和数据㊂即便这样,这种方式的耗时也不可小觑,以1M B 的数据和有100个引脚的芯片以及有32字节编程块缓存的F L A S H (即有N=32K 字节块,一次性可以编程32字节)为例㊂为方便计算,忽略F L A S H 的命令字,仅仅计算有效字节编程时间㊂一个块编程周期包含片选C S 从高到低,然后写有效信号W E 从高到低,数据有效(可同时),W E从低到高,W E 从高到低,数据有效(可同时),W E 从低到高 最后C S 从低到高㊂J T A G 控制器就需要至少移位K=(2N+3)c yc l e s (对应一个T C K 时钟周期),每次都需要移位T s h i f t =100次㊂假设J T A G 控制器的T C K 时钟为T t c k =20MH z ,那么T c y c l e =50n s ㊂总时间就是:T=KˑT c yc l e ˑT s h i f t =327.695s >5m i n 实际上的引脚会更多,编程命令字的开销也不少,J T A G 工具每批次移位的间隔还有时间,需要更多的编程时间㊂3 虚拟J T A G 简介批量生产的自动化测试需要用到J T A G 接口,而传统的J T A G 编程又比较低效费时,有没有两全其美的方法呢?答案是肯定的,就是可编程器件F P G A 或C P L D (C o m p l e x P r o g r a mm a b l e L o g i c D e v i c e )的虚拟J T A G 技术㊂V i r t u a l J T A G 是A L T E R A (已被I n t e l 收购)公司提出的一个概念,X I L I N X 公司和L A T T I C E 公司也有相对应的提法,具体实现大同小异㊂在可编程器件里面,J T A G T A P 控制器可以作为一个硬核对用户开放,用户可以得到T A P 状态机的各种状态,当然包括T D I ㊁T C K ㊁T D O ,从而可以接管T D I 的数据,自定义返回给T D O 的数据㊂触发用户自定义的J T A G 后级控制器的原理用到了指令寄存器(i n s t r u c t i o n r e gi s t e r )里面的用户数据寄存器(u s e r d a t a r e gi s t e r )㊂当输入特定数据给用户寄存器0和用户寄存器1后,相应的状态指示线发出高电平,J T A G后级控制器就可以知道后面的数据都是输入给它的,就可以对这些数据进行自定义的操作㊁自定义虚拟指令寄存器(V i r t u a l I n s t r u c t i o n R e g i s t e r ,V I R )和虚拟数据寄存器(V i r t u a l D a t a R e g i s t e r ,V D R ),从而完成了虚拟J T A G 的实现,如图3所示㊂4 挂载F P G A 上的F L A S H 的快速编程基于V i r t u a l J T A G 技术,可以自定义后级J T A GT A P 控制器,定义好虚拟数据寄存器(V D R )和虚拟指令寄存器(I R )㊂再移植一个F l a s h M e m o r y Co n t r o l l e r ,由相应的虚拟I R 指令得到擦除㊁读取㊁编程等命令,相应的数据从V D R 得到或保存于V D R ㊂一般的F P G A 有足够的内部存储空间R AM ,所以上位机可以一次性把大容量数据通过虚拟J T A G 传给V D R ,后级的F l a s h C o n t r o l l e r 就可以启动相应的编程序列,从而节省了很多传输和边界移位的开销,极大地提高了F L A S H 的编程效率㊂图4就是一种实现的功能框图㊂敬请登录网站在线投稿 2018年第2期11图3 V i r t u a l J T A G实现原理图图4 虚拟J T A G 快速F L A S H 编程实现框图T A P 控制器里面对V i r t u a l J T A G 的内核进行了封装,导出了三个总线,分别是对下级模块输出的虚拟I R ㊁虚拟D R 以及从下级模块输入的虚拟D R ㊂下级的命令转换模块从输入的V I R 和V D R 得到命令和数据,通过W i s h b o n e 总线转换为F L A S H 控制器的命令和数据,以及得到返回的数据㊂F L A S H 控制器进行对F L A S H 的实际读写操作㊂V I R 定义为4比特位宽,其定义如表1所列㊂还是以1M B 的数据为例,V D R 存储深度为1K B ,表1 V I R V D R 对应关系表V I R 输入V D R 输出V D R (0000)读I D无定义32位宽的F L A S H I D(0001)导入数据1K B y t e 无定义(0010)开始编程无定义无定义(0011)读状态无定义1位宽,1:结束0:忙(0100)读取数据无定义1K BV I R 为4位㊂则一次数据搬运需要移动T s h i f t =1028次,一共需要搬运K=1024次㊂那么总时间为:T=KˑT c yc l e ˑT s h i f t =52.6336s <1m i n 如果V D R 的存储深度变得更大(一般F P G A 里面有足够多的内存),那么时间将更少,最后的瓶颈取决于F L A S H 自身的编程速度㊂结 语在工业4.0时代,对自动化测试的要求是更高效㊁更智能㊂而虚拟J T A G 技术不仅能优化诸如F L A S H 器件的编程效率,也能打通芯片内部逻辑的在线测试,提高了测试的覆盖率和有效性㊂参考文献[1]D r .B e n B e n n e t t s .I E E E 1149.1J T A Ga n d B o u n d a r y Sc a n T u t o r i a l [E B /O L ].[2017-10].h t t ps ://w w w .a s s e t -i n t e r t e c h .c o m /e r e s o u r c e s /i e e e -11491-j t a g -a n d -b o u n d a r y-s c a n -t u t o r i a l .[2]A L T E R A.V i r t u a l J T A G (a l t e r a _v i r t u a l _j t a g)I P C o r e U s e r [E B /O L ].[2017-10].h t t ps ://w w w.a l t e r a .c o m /e n _U S /p d f s /l i te r a t u r e /u g /u g _v i r t u a l jt a g .pd f .丁峰平(硬件工程师),主要研究方向为电信硬件电路㊁F P G A 设计和实现;陈莉萍(项目经理),主要研究方向为电信工程项目组织计划和实现㊂(责任编辑:杨迪娜 收稿日期:2017-10-23) 灵活,最后通过将该方法在一款实际D S P 设计中的应用说明了本方法是可行的㊁有效的㊂参考文献[1]韦祎.基于S ys t e m C 构建多核D S P 软件仿真平台[J ].微电子学与计算机,2016,33(4):8690.[2]彭德生,蒋志翔.基于S ys t e m C 的M I P S 处理器建模与架构[J ].计算机工程与设计,2015,36(4):10151021.[3]陈曦,徐宁仪,周祖成.嵌入式系统虚拟原型平台的S ys t e m C 实现[J ].计算器辅助设计与图形学报,2004,16(8):10701073.[4]K e i n e r t J ,S c h l i c h t e r T ,F a l k J ,e t a l .S y s t e m C o d e s i gn e r a n a u t o m a t i c E S L s y n t h e s i s a p p r o a c h b y d e s i g n s p a c e e x pl o r a -t i o n a n d b e h a v i o r a l s y n t h e s i s f o r s t r e a m i n g a p pl i c a t i o n [C ]//P r o c .o f t h e 45t h A n n u a l D e s i gn A u t o m a t i o n C o n f e r e n c e ,2008:580585.[5]莫寒以,王仁平.32位稀疏树可逆逻辑加法器的V e r i l o g 设计[J ].中国集成电路,2017,30(5):2833.[6]赵地,朱兴华.基于V e r i l o g的模拟前端时序的实现方法[J ].电子科技,2017,30(4):144147.[7]I E E E 16662005.I E E E S t a n d a r d S y s t e m C l a n g u a ge r ef e r -e n c e m a n u a l ,2006.[8]G h e n a s s i a F .T r a n s a c t i o n l e v e l m o d e l i n g w i t h S ys t e m C :T L M c o n c e p t s a n d a p p l i c a t i o n s f o r e m b e d d e d s ys t e m s [M ].B e r l i n :S p r i n ge r ,2005.[9]洪一,方体莲,赵斌等. 魂芯一号 数字信号处理器及其应用[J ].中国科学:信息科学,2015,45(4):574586.(责任编辑:薛士然 收稿日期:2017-11-16)。

附图是EPP数据写周期的时序图。

因它的握手信号由硬件完成,整个数据传输过程发生在一个ISA I/O周期内,因而使用EPP传送数据,协调可以获得500KB/S~2MB/S的传输率。

2.2、EPP端口及寄存器EPP 占用并行口基地址+0~+7共8个相邻的I/O映像地址。

基地址+3是EPP的地址口,对它进行I/O操作便产生地址周期;基地址+4是EPP的数据口,对它进行8位I/O读写操作,便产生数据读写周期。

如软件使用16位或32位的I/O操作,则会用到基地址+4~+7映像地址。

对基地址+0~+2的操作与SPP相同,这就保证了与SPP的兼容性。

但由于EPP为双向端口,其寄存器的内容比SPP有所增加(如表2所示)。

新增的位如下:(1)TIMEOUT位:逻辑“1”表示EPP读写操作时发生超时错误;逻辑“0”表示无超时发生。

(2)PCD位(Parallel Control Direction并行口方向控制):在双向传输种,PCD位为“0”时进行写操作;为“1”时进行读操作,8位数据线处于读状态。

2.3、EPP1.9和EPP1.7EPP1.7 是指Xircom 1.7版的提案,Intel在最初的82360 I/O控制器中使用这一协议,而那时IEEE1284标准还没建立起来。

EPP1.7与IEEE1284标准所规定的EPP1.9的区别在于,EPP1.7在读写周期开始时,nDATASTROBE或nADDRSTROBE置位时不考虑nWAIT 信号的状态。

这意味着外设不能通过清nWAIT来推迟一个EPP周期的开始。

因而服从1284标准的外设可以在EPP1.7的主机上工作,而EPP1.7的外设不能在服从1284 标准的主机上工作。

EPP 控制芯片中的看门狗时钟会防止系统锁死。

一般来讲,EPP1.9在读写周期开始10us 后,如果nWAIT仍没有响应,则发生TIMEOUT错误,状态寄存器的第0位TIMEOUT为“1”,EPP周期终止;而EPP1.7则是在EPP读写周期开始10us后仍未结束时,置TIMEOUT为“1”。