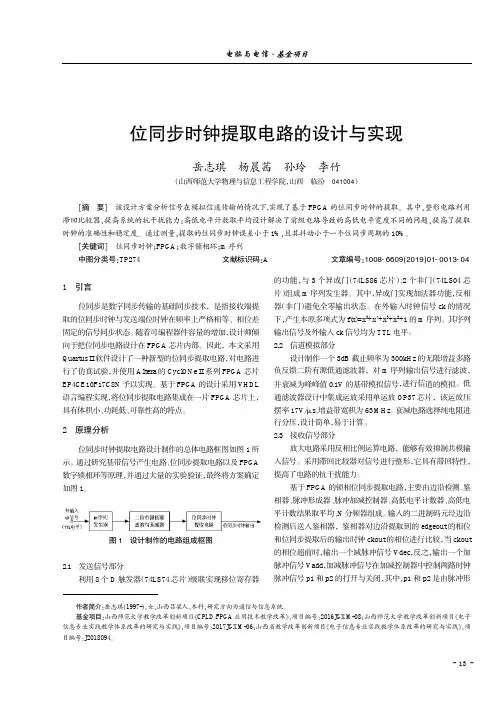

基于FPGA的新型位同步时钟提取方案的设计

- 格式:doc

- 大小:151.00 KB

- 文档页数:4

一种基于FPGA的锁相环位同步提取电路设计概述同步是通信系统中一个重要的问题。

在数字通信中,除了获取相干载波的载波同步外,位同步的提取是更为重要的一个环节。

因为只有确定了每一个码元的起始时刻,才能对数字信息作出正确的判决。

利用全数字锁相环可直接从接收到的单极性不归零码中提取位同步信号。

一般的位同步电路大多采用标准逻辑器件按传统数字系统设计方法构成,具有功耗大,可靠性低的缺点。

用FPGA设计电路具有很高的灵活性和可靠性,可以提高集成度和设计速度,增强系统的整体性能。

本文给出了一种基于fpga 的数字锁相环位同步提取电路。

数字锁相环位同步提取电路的原理数字锁相环位同步提取电路框本地时钟产生两路相位相差p的脉冲,其频率为fo=mrb,rb为输入单极性不归零码的速率。

输入信码的正、负跳变经过过零检测电路后变成了窄脉冲序列,它含有信码中的位同步信息,该位同步窄脉冲序列与分频器输出脉冲进行鉴相,分频比为m。

若分频后的脉冲相位超前于窄脉冲序列,则在1端有输出,并通过控制器将加到分频器的脉冲序列扣除一个脉冲,使分频后的脉冲相位退后;若分频后的脉冲相位滞后窄脉冲序列,则在2端有输出,并通过控制器将加到分频器的脉冲序列附加一个脉冲,使分频后的脉冲相位提前。

直到鉴相器的1、2端无输出,环路锁定。

基于fpga的锁相环位同步提取电路该电路如该电路由d触发器组成的二分频器和两个与门组成,它将fpga 的高频时钟信号clk_xm变换成两路相位相反的时钟信号,由e、f输出,然后送给控制电路的常开门g3和常闭门g4。

其中f路信号还作为控制器中的d1和。

基于FPGA的锁相环位同步提取电路设计锁相环(Phase-Locked Loop,PLL)是一种广泛应用于通信、控制及信号处理等领域的电路,能够实现频率同步和相位同步。

在本文中,我们将讨论基于FPGA的锁相环位同步提取电路设计。

首先,我们将介绍锁相环的基本原理。

锁相环由相位比较器、低通滤波器、VCO(Voltage-Controlled Oscillator)和分频器组成。

相位比较器用于比较参考信号和反馈信号的相位差,将相位差转换为电压差。

低通滤波器将电压差平滑处理,得到控制电压,用于控制VCO的频率。

VCO产生与输入信号频率相同的输出信号,通过分频器将输出信号分频后与参考信号进行比较,实现频率同步。

在基于FPGA的锁相环位同步提取电路设计中,我们的目标是实现一个能够提取输入信号的位同步信息的电路,其中输入信号可能包含多个周期不同的位同步序列。

首先,我们需要设计一个相位比较器,用于比较参考信号和输入信号的相位差。

可以使用FPGA中的数字时钟管理模块来实现相位比较器,将输入信号与参考信号都映射到固定的时钟边沿上,并通过计数器测量输入信号和参考信号之间的相位差。

然后,我们需要设计一个低通滤波器,用于平滑处理相位差。

可以使用FPGA中的滑动平均滤波器来实现低通滤波器,通过对相位差进行滑动平均运算,得到平滑的控制电压。

接下来,我们需要设计一个VCO,用于产生与输入信号频率相同的输出信号。

可以使用FPGA中的数字控制模块来实现VCO,通过调节VCO的控制电压来控制输出频率。

最后,我们需要设计一个分频器,将VCO的输出信号分频后与参考信号进行比较。

可以使用FPGA中的计数器来实现分频器,通过设置分频器的计数值来实现对VCO输出信号的分频。

在整个电路设计过程中,我们需要注意以下几点:1.选择合适的时钟频率和分辨率。

时钟频率要足够高,以满足输入信号的高速采样需求。

分辨率要足够高,以保证位同步信息的精确提取。

2.选择合适的滤波器参数。

FPGA位同步信号提取1. 简介FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,能够根据用户的需求进行重新配置,实现各种不同的数字电路功能。

在FPGA设计中,位同步信号提取是一个重要的任务,它能够从输入信号中提取出同步信息,用于控制和协调各个模块之间的操作。

本文将介绍FPGA位同步信号提取的原理、方法和实现步骤,并且详细说明如何使用FPGA设计工具进行开发。

2. 原理在FPGA设计中,通常会涉及到多个时钟域(clock domain),每个时钟域都有自己的时钟信号。

由于不同时钟域的时钟频率可能不同,因此需要一种机制来确保数据在不同时钟域之间正确地传输和处理。

这就是位同步(bit-level synchronization)的概念。

位同步信号提取就是从输入信号中提取出用于位同步的控制信息。

这些控制信息通常包括数据有效性标志(valid flag)和数据使能标志(enable flag)。

通过这些标志,可以确定数据何时有效以及何时可以被处理。

3. 方法3.1 插入寄存器为了实现位同步信号提取,通常需要在输入信号路径上插入寄存器。

寄存器能够将输入信号同步到目标时钟域的时钟边沿,确保数据在时序上的正确性。

具体方法是,在输入信号路径上插入一个寄存器,并将寄存器的时钟与目标时钟域的时钟相连接。

这样,输入信号就会在目标时钟边沿被锁存,从而达到位同步的效果。

3.2 控制逻辑设计除了插入寄存器外,还需要设计控制逻辑来提取位同步信号。

控制逻辑通常包括状态机(state machine)和组合逻辑电路。

状态机用于控制数据有效性标志和数据使能标志的生成和更新。

它根据输入信号的状态和当前状态来确定下一状态,并输出相应的控制信号。

组合逻辑电路用于根据输入信号和当前状态来生成数据使能标志。

它可以根据需要进行逻辑运算、比较操作等,以判断数据是否有效并生成相应的使能标志。

3.3 时序约束设置为了确保FPGA设计满足时序要求,需要设置正确的时序约束。

FPGA位同步信号提取1. 引言FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,可以通过编程实现不同的电路功能。

在许多应用中,需要对FPGA进行位同步信号提取,以确保各个模块之间的数据传输和处理的准确性和一致性。

本文将详细介绍FPGA位同步信号提取的原理、方法和实现过程。

2. 原理在FPGA中,位同步信号提取是指从输入数据中提取一个用于同步各个模块的时钟信号。

这个时钟信号通常由一个稳定的时钟源产生,并被分配给FPGA内部的各个模块。

位同步信号提取有两个主要任务:检测输入数据中的时钟边沿,以及生成一个与输入数据频率相匹配的稳定时钟。

2.1 时钟边沿检测在FPGA中,通常使用触发器来检测输入数据中的时钟边沿。

触发器是一种存储元件,在时钟上升沿或下降沿触发时将输入数据存储到输出端口。

通过检测触发器输出端口的变化,可以确定输入数据中是否存在时钟边沿。

常见的触发器类型包括D触发器、JK触发器和T触发器。

这些触发器可以根据需要进行级联,以实现更复杂的时钟边沿检测功能。

在FPGA中,可以使用硬件描述语言(如Verilog或VHDL)来描述和实现这些触发器电路。

2.2 稳定时钟生成一旦检测到输入数据中的时钟边沿,需要生成一个稳定的时钟信号,并将其分配给FPGA内部的各个模块。

稳定的时钟信号通常由一个PLL(Phase-Locked Loop)电路来生成。

PLL是一种反馈控制系统,可以根据输入参考时钟的相位和频率来生成一个稳定的输出时钟。

PLL通常由相位比较器、环形振荡器和反馈回路组成。

相位比较器用于比较输入参考时钟和反馈时钟之间的相位差,并产生一个控制信号。

环形振荡器根据控制信号调整自身的振荡频率,使得反馈时钟与输入参考时钟保持同步。

通过不断调整振荡频率,PLL能够自动消除相位差,并生成稳定的输出时钟。

3. 方法在FPGA中实现位同步信号提取有多种方法,下面将介绍两种常用的方法:基于触发器的位同步信号提取和基于PLL的位同步信号提取。

基于fpga的提取位同步时钟dpll设计近些年来,随着电子通信技术的不断发展,电子设备迅速普及到每个角落,电子设备高速数据传输、处理数据和执行各种任务等,应用范围更多更广,时钟同步技术变得越来越重要,时钟同步也是其中重要的技术之一。

时钟同步的核心原理是把多个接受机的时钟统一调整到同一个频率上,从而实现信息的有效传输。

为了实现多台电子设备之间的时钟同步,设计人员采用的一种技术就是用FPGA实现的微处理器时钟同步技术DPLL设计(Data Pathlocks Loop)。

DPLL (Data Pathlocks Loop)是一种用来提取和同步多个位时钟信号(称为目标位时钟)的技术,它可以同步多通道从电子设备接收到的位时钟信号,进而实现时钟同步功能。

基于FPGA的DPLL设计技术,大量地使用了FPGA中基础参数模块,设计工作者可以根据具体应用需求,根据芯片资源,灵活地进行设计。

由于FPGA在设计上的灵活性,在很多复杂的系统中可以很好地支撑时钟同步控制的实现。

首先,在采用基于FPGA的DPLL设计技术实现位同步时钟之前,需要对整个系统的时钟原理进行深入的理解。

基于FPGA的DPLL设计结构由以下几部分组成:锁定滤波器,多路移相器,比较器,控制电路,锁定状态输出状态指示器以及一系列诊断功能功能模块等。

首先,采用锁定滤波器,以把多个位时钟信号聚集到一个基准时钟的信号,以实现多个位时钟的精确同步;其次,采用多路移相器,可以把多个位时钟转换成单一的目标位时钟信号,以此,可以跟踪目标位时钟;比较器是负责对比多个输入位时钟和目标位时钟的差异,并输出差值;控制电路收集比较器输出的差值,并将其作为参数调整多路移相器;最后,锁定状态输出和状态指示器,可以把多通道位时钟同步系统的运行状态反馈出来,以指示系统的同步运行情况。

除此之外,在基于FPGA的DPLL设计中,设计工程师还可以根据具体的应用需求,将一系列的诊断测试功能模块也融入到设计中,以直观地显示出整个系统的状态,以保障系统的正常运行。

fpga 伪随机序列同步时钟的提取FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它具有高度的灵活性和可配置性,可以根据特定的应用需求进行定制。

在数字电路设计中,伪随机序列是一种常用的信号源,可用于各种应用,如通信系统、加密算法等。

在FPGA中,如何提取伪随机序列的同步时钟是一个重要的问题。

伪随机序列是由一系列看似随机的数字组成的序列,其特点是具有较长的周期、较好的均匀性和较低的自相关性。

FPGA中的伪随机序列通常采用线性反馈移位寄存器(LFSR)实现。

LFSR是一种特殊的寄存器,其输出通过与寄存器内部的某些位进行异或运算得到,这样就可以实现序列的循环移位和反馈,从而生成伪随机序列。

在FPGA中,提取伪随机序列的同步时钟是为了确保序列的稳定性和可靠性。

由于FPGA是一个并行计算的设备,其内部存在多个时钟域,不同时钟域之间存在时钟信号的延迟和相位差。

因此,在提取伪随机序列的过程中,需要考虑时钟同步的问题,以保证伪随机序列的正确性。

为了实现伪随机序列的同步时钟提取,可以采用两种常用的方法:外部时钟同步和内部时钟同步。

外部时钟同步是指利用外部时钟信号进行同步。

在FPGA设计中,通常会有一个主时钟源,该时钟源会被分配给各个模块进行同步。

在伪随机序列的提取过程中,可以利用主时钟信号进行同步,使得伪随机序列的生成和使用都处于同一个时钟域中。

这样可以有效避免时钟信号的延迟和相位差对伪随机序列的影响,提高序列的稳定性和可靠性。

内部时钟同步是指利用FPGA内部时钟信号进行同步。

FPGA内部通常有多个时钟域,不同时钟域之间存在时钟信号的延迟和相位差。

在伪随机序列的提取过程中,可以利用FPGA内部的时钟分频和相位锁定等技术,将伪随机序列的生成和使用都处于同一个时钟域中。

这样可以通过时钟同步电路的设计和优化,减小时钟信号的延迟和相位差,提高序列的稳定性和可靠性。

总结起来,FPGA伪随机序列的同步时钟提取是一个重要的问题,关系到序列的稳定性和可靠性。

基于FPGA的电子钟设计基于FPGA的电子钟设计随着物联网技术的发展,我们对于时间的要求也越来越精细。

电子钟作为一个基本的时间计量工具,其精度和稳定性至关重要。

而FPGA作为一种强大的可编程逻辑器件,具有高速、高效、灵活等优势,成为电子钟设计的重要基础。

一、电子钟的基本原理电子钟是指采用电路元器件、微处理器等电子器件构成的时钟。

其基本原理可以概括为:利用更精确的时间计量器件替代机械时钟中的发条和摆轮,同时采用数字处理器等电子元器件代替机械表盘展示时间。

电子钟的核心是时基电路,其作用是产生高精度的时间信号,为其它电路提供时间标准。

通常采用晶振、TCXO、OCXO等时基器件。

为了保证时间精度,还要从外部时钟或天线接收校正信号。

二、FPGA的优势FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,可以灵活地对电路进行编程和调整,从而实现不同的功能。

FPGA相对于ASIC(Application Specific Integrated Circuit),具有以下优点:1. 灵活性:FPGA可以通过重新编程来实现不同的逻辑功能,而ASIC则需要重新设计电路,成本和时间都比较高。

2. 高速:FPGA以可编程方式实现电路逻辑,减少了多级缓存的开销,因此运行速度更快。

3. 低功耗:FPGA可以在逻辑上进行优化,以达到低功耗效果,同时利用现代的制造技术,还可以采用低功耗工艺。

4. 可重用性:FPGA的电路设计可以在不同的项目中重复使用,从而提高了效率和经济性。

三、基于FPGA的电子钟设计基于FPGA的电子钟设计方案主要包括两部分,分别是时基电路和数码显示电路。

1. 时基电路设计时基电路是电子钟的核心部分,可以采用晶振、TCXO、OCXO等器件来产生高精度的时间信号。

在电子钟的设计中,一般还需要接收外部同步校时信号,用于校正时钟误差。

基于FPGA的时基电路设计主要包括以下几个部分:(1)时钟输入电路:接收来自外部同步信号的时钟脉冲,用于校准电子钟的误差。

基于FPGA 精确时钟同步SOPC 设计与实现柏 颖1,王晓明2(1.重庆邮电大学 重庆 400065;2.湖南商学院 资产管理处 长沙 410205)摘 要:随着控制网络技术的发展,分布式控制系统对时钟同步的要求越来越高。

当前的时钟同步系统通常是使用软件的方式,在网卡驱动时打上时间戳,然后根据时钟同步协议IEEE1588算法进行时钟同步。

然而操作系统、网卡时槽的延迟和时钟晶振的偏移等因素的影响导致时钟同步精度只能达到微秒级,为了满足工业控制总线时钟精度的要求,本文提出了基于FP GA 的时钟同步、时钟补偿和最佳主时钟的算法,通过搭建测试平台,最后使系统的时钟同步精度达到了纳秒级。

关键词:IEEE1588;FP GA ;时钟补偿;最佳主时钟中图分类号:TN431.2 文献标识码:ADesign and implementation of p recise clock synchronization on SO PC based on FP GABai Y ing 1,Wang Xiaoming 2(Chongqing Key Lab of NC &IC ,Chongqing University of Posts and Telecommunications ,Chongqing 400065,China ,Hunan university of commerce ,Asset Management Service ,Changsha 410205,China )Abstract :With the rapid development of network ,the synchronization of different devices in a distribu 2ted system becomes more and more important.Current implementations rely purely on software to get the time stamp through the network card ,then carries on the clock synchronization according to the clock synchronous protocol IEEE1588algorithm.However ,the delay of operating system and card slot and the displacement of crystal oscillator result the clock synchronization precision only to be able to a 2chieve a microsecond level.T o reach the requirement of the industry control bus ,we design the precise clock synchronization ,the clock compensation and the best master clock algorithm based on FPG A ,so that increased the clock synchronization precision.Though building the platform of test ,the final sys 2tem clock synchronization precision has achieved a nanosecond level.K eyw ords :IEEE1588;FP GA ;clock compensation ;t he best master clock0 引 言随着网络技术的发展,分布式控制系统中对时间同步的要求越来越高。

湖南工程学院毕业设计论文题目:基于单片机和FPGA的位同步信号提取专业班级:电子信息工程学生姓名:学号:完成日期:指导教师:评阅教师:2006 年6月湖南工程学院应用技术学院毕业设计(论文)诚信承诺书本人慎重承诺和声明:所撰写的《基于单片机和FPGA的位同步信号提取》是在指导老师的指导下自主完成,文中所有引文或引用数据、图表均已注解说明来源,本人愿意为由此引起的后果承担责任。

设计(论文)的研究成果归属学校所有。

学生(签名)年月日湖南工程学院应用技术学院毕业设计(论文)任务书设计(论文)题目:基于单片机和FPGA的位同步信号提取姓名李国冀专业电子信息工程班级 0281 学号 16指导老师刘正青职称实验师教研室主任刘望军一、基本任务及要求:本课题是设计一具有通用性的输入信号的位同步提取系统,系统可以实现10HZ~1MHZ的信号同步。

使用单片机进行实时控制现场可编程逻辑门阵列FPGA完成位同步信号提取,通过理论和实验研究,完成硬件电路和软件设计并试制样机,要求完成:1、单片机实时控制FPGA,完成实时频率跟踪测量和自动锁相;2、在FPGA 内部,设计完成以下部分:A、全数字锁相环DPLL,主要包含:数控振荡器、鉴相器、可控模分频器B、LED动态扫描电路、FPGA和单片机的数字接口,以完成两者之间的数字传递3、设计辅助电路:键盘、LED;二、进度安排及完成时间:(1)第二周至第四周:查阅资料、撰写文献综述和开题报告;(2)第五周至第六周:毕业实习;(3)第六周至第七周:项目设计的总体框架:各个模块以及各个模块之间的关系确定,各个模块的方案选择与各个模块的所用主要器件的确定;(4)第八周至第十三周:各个模块的主要器件熟悉及相关知识的熟悉;各个模块的具体任务实现:硬件电路、软件编程;(5)第十四周至第十五周:系统的总体仿真与调试(6)第十六周至第十七周:撰写设计说明书;(7)第十八周:毕业设计答辩;目录摘要........................................................................................................ 错误!未定义书签。

专利名称:一种基于FPGA的位同步时钟提取方法及装置专利类型:发明专利

发明人:丰泳翔,韩卓定,陈紫业,郑旎杉,陈小桥

申请号:CN201610994547.7

申请日:20161111

公开号:CN106533432A

公开日:

20170322

专利内容由知识产权出版社提供

摘要:本发明涉及通信技术领域,具体涉及一种基于FPGA的位同步时钟提取方法及装置,包括外部CK信号,包括信号发生模块、模拟信号传输模块、待测信号调理模块、信号处理模块、显示屏模块和键盘控制模块;外部CK信号输入信号发生模块,信号发生模块依次连接模拟信号传输模块、待测信号调理模块、信号处理模块、显示屏模块和键盘模块;信号发生模块用于产生测试m序列;模拟信号传输模块用于m序列滤波、衰减;待测信号调理模块用于m序列放大、整形;信号处理模块用于从m 序列提取位同步时钟信号;显示屏模块用于频率显示;键盘控制模块用于控制键盘。

该方法及装置利用m序列的自相关性质和新型锁相环方法,实现100kHz‑350kHz信号的位同步时钟提取,系统工作稳定。

申请人:武汉大学

地址:430072 湖北省武汉市武昌区珞珈山武汉大学

国籍:CN

代理机构:武汉科皓知识产权代理事务所(特殊普通合伙)

代理人:彭艳君

更多信息请下载全文后查看。

基于FPGA的新型位同步时钟提取方案的设计一种基于FPGA的新型位同步时钟提取方案及实现摘要:关键词:位同步,锁相环,FPGA,异步串行码流1 引言:同步技术在数字通信系统中,是非常重要的技术。

位同步是最基本的同步。

位同步时钟信号不仅用于对输入码元信号的监测保证收发同步,而且在对获取祯同步,群同步及对接收的数字码元进行各种处理过程中也为系统提供了一个基准的同步时钟。

随着现代电子技术的发展,数字系统趋于模块化,小型化,芯片华,因此如何实现同步系统的模块化和芯片化是急需解决的问题。

在数字通信中,通常直接从接收到的数字信号中提取位同步信号,这种直接法按其提取同步信号的方式,大致可分为滤波法和锁相法。

锁相法是指利用锁相环来提取位同步信号的方法,本设计方案就是基于锁相环的位同步提取方法,能够比较快速地提取位同步时钟,并且设计简单,方便修改参数。

采用Quartus II 设计软件对系统进行了仿真试验,并用Altera的Cyclone II系列FPGA芯片Ep2c5予以实现。

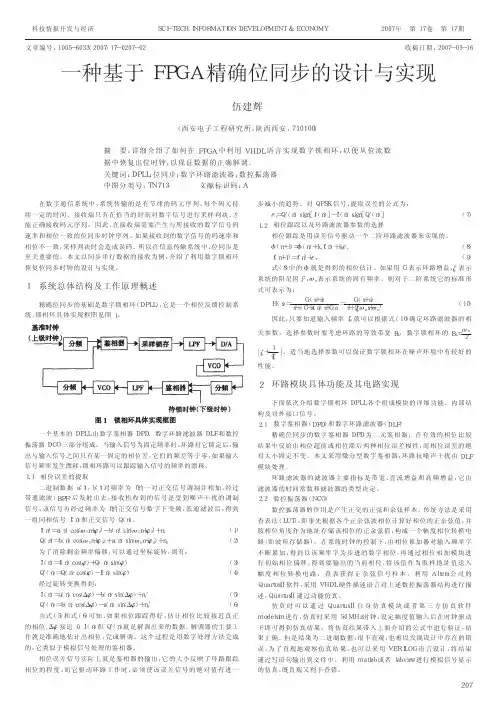

2 位同步时钟提取方案的原理本文设计的方案可以从异步串行码流中提取位同步时钟信号,设计思想的基本出发点是在外部码流(code_in)的上升沿和本地时钟(clk)上跳沿相比较无非两种情况,如图1和图2所示:图1 码流滞后于本地时钟△T示意图图2码流超前于本地时钟△T示意图从码流上跳沿的角度来看,若将码流code_in与本地时钟clk进行逻辑相与,若相与结果为“1”则说明码流滞后于本地时钟,若为“0”则说明码流超前于本地时钟。

用VHDL语言描述为:if (code_in’event and code_in=’1’) thenif (code_in and clk)=’1’ thenq<=’1’elseq<=’0’end ifend if程序中输出信号q可作为控制电路的输入信号。

本设计方案的系统框图如图3所示:框图中,鉴相器作用是鉴别出码流和本地时钟的相位超前滞后关系,控制计数器采用双向计数器,鉴相器输出q作为控制计数器的计数方向输入,q为1则向上计数,q为0则向下计数。

基于FPGA的提取位同步时钟DPLL设计在数字通信系统中,同步技术是非常重要的,而位同步是最基本的同步。

位同步时钟信号不仅用于监测输入码元信号,确保收发同步,而且在获取帧同步及对接收的数字码元进行各种处理的过程中也为系统提供了一个基准的同步时钟。

位同步的目的是使每个码元得到最佳的解调和判决。

位同步可以分为外同步法和自同步法两大类。

一般而言,自同步法应用较多。

外同步法需要另外专门传输位同步信息。

自同步法则是从信号码元中提取其包含的位同步信息。

自同步法又可以分为两种,即开环同步法和闭环同步法。

开环法采用对输入码元做某种变换的方法提取位同步信息。

闭环法则用比较本地时钟和输入信号的方法,将本地时钟锁定在输入信号上。

闭环法更为准确,但是也更为复杂。

本文采用了自同步法,在FPGA 构造片内对超前一滞后全数字锁相环提取曼彻斯特码中包含的位同步时钟。

1 提取位同步时钟全数字锁相环总体结构与工作原理这种超前一滞后全数字锁相环采用加减门结构,每输入一个码元后,根据鉴相器判断是超前还是滞后,通过反馈回路控制的加减门来调整相位,使之逼近输入码元的相位。

一旦失步,就需要通过反馈回路重新调整。

每一个超前和滞后脉冲仅能调整一步,如果接收码元出现连“1”或是连“O”的情况,锁定时间会很长,使其同步建立时间和调整精度变得相互制约。

尽管有此缺点,但由于这种结构具有失锁后的自我调节性,因此,码元消失或是码元相位出现抖动时,同步脉冲不会出现较大变化,仍然可以输出稳定的同步脉冲。

由于采用曼彻斯特码进行传输,该设计主要应用于地铁车辆总线上,传输速率为250 Kb/s,速率较低,且每个码元内都有一次电平跳变,不会出现连续的“O”或“1”,因此采用闭环的超前一滞后全数字锁相环非常适合提取比特流中的位时钟。

基本结构如图1 所示,主要由数字鉴相器(DPD)、数字环路滤波器(DLF)、数控振荡器。

课程设计说明书课程名称:EDA技术课程设计题目:基于FPGA的时钟提取电路的设计学院:后备军官学院专业:信息工程年级:2010级学生:张成良学号:362010*********指导教师:卿朝进完成日期:2013年7月7日基于FPGA的时钟提取电路的设计摘要:在数字通信系统中,同步技术是非常重要的,而位同步是最基本的同步。

位同步时钟信号不仅用于监测输入码元信号,确保收发同步,而且在获取祯同步、群同步及对接收的数字码元进行各种处理的过程中,也为系统提供了一个基准的同步时钟。

随着可编程器件容量的增加,设计师倾向于把位同步电路设计在CPLD/FPGA芯片内部。

因此,本文采用Quartus II软件设计了一种新型的位同步提取电路,对电路进行了仿真试验,并使用Altera的ACEX 1K系列FPGA芯片EP1K10TC100_3予以实现。

关键词:时钟提取,同步,FPGAAbstract:In digital communication systems, synchronization is very important, bit synchronization is the most basic synchronization. Bit synchronization clock signal is not only used to monitor the input symbol signal, to ensure the transceiver synchronization and frame synchronization in the acquisition, synchronization and the group receiving the digital code element to the process of treatment and also provide the system with a benchmark of the synchronous clock . With the increased capacity programmable devices, designers tend to bit synchronization circuit in the CPLD / FPGA chip. Therefore, the use Quartus II design software, a new bit synchronization extraction circuit, the circuit is simulated by computer and use Altera's ACEX 1K series FPGA chip EP1K10TC100_3 be achieved.Keywords:Clock Extraction,Synchronization,FPGA目录1 前言 (1)1.1 设计背景 (1)1.2 FPGA技术简介 (1)1.3 Quartus简介 (2)1.4 必备条件 (2)2 总体方案设计 (3)2.1 方案比较 (3)2.1.1 方案一: 基于超前滞后型锁相环的位同步提取电路 (3)2.1.2 方案二:采用跳变沿捕捉和计数器结构的位同步电路 (4)2.1.3 方案三:硬件开环位同步电路FPGA的实现 (5)2.2 方案论证 (5)2.3 方案选择 (6)3 单元模块设计 (6)3.1 各单元模块功能介绍及电路设计 (6)3.1.1 跳变沿捕捉模块设计 (6)3.1.2 状态寄存器模块设计 (7)3.1.3 可控计数器模块设计 (8)3.1.4 整体电路模块设计 (10)3.1.5 供电电路 (11)3.1.6 有源晶振电路 (12)3.1.7 JTAG下载电路 (12)3.2 FPGA器件选择 (13)3.2.1 ACEX 1K器件 (13)3.2.2 配置器件选择 (13)4 系统调试 (14)4.1 调试环境 (14)4.2 硬件调试 (14)4.2.1 硬件配置电路 (14)4.2.2 硬件配置和调试 (15)4.3 系统能实现的功能 (15)5 总结与体会 (17)6 谢辞(致谢) (18)参考文献 (19)附录 (20)1前言1.1 设计背景现代通信系统中异步串行数据进行发送和接收,就必须使其接收与发送的码元同步,位同步时钟信号不仅可用来对输入码元进行检测以保证收发同步,而且在对接收的数字码元进行误码率测试及各种处理过程中,也可以为系统提供一个基准的同步时钟。

一种基于FPGA的新型位同步时钟提取方案及实现

摘要:

关键词:位同步,锁相环,FPGA,异步串行码流

1 引言:

同步技术在数字通信系统中,是非常重要的技术。

位同步是最基本的同步。

位同步时钟信号不仅用于对输入码元信号的监测保证收发同步,而且在对获取祯同步,群同步及对接收的数字码元进行各种处理过程中也为系统提供了一个基准的同步时钟。

随着现代电子技术的发展,数字系统趋于模块化,小型化,芯片华,因此如何实现同步系统的模块化和芯片化是急需解决的问题。

在数字通信中,通常直接从接收到的数字信号中提取位同步信号,这种直接法按其提取同步信号的方式,大致可分为滤波法和锁相法。

锁相法是指利用锁相环来提取位同步信号的方法,本设计方案就是基于锁相环的位同步提取方法,能够比较快速地提取位同步时钟,并且设计简单,方便修改参数。

采用Quartus II 设计软件对系统进行了仿真试验,并用Altera的Cyclone II系列FPGA芯片Ep2c5予以实现。

2 位同步时钟提取方案的原理

本文设计的方案可以从异步串行码流中提取位同步时钟信号,设计思想的基本出发点是在外部码流(code_in)的上升沿和本地时钟(clk)上跳沿相比较无非两

种

情

况,

如图1和图2所示:

图1 码流滞后于本地时钟△T示意图图2

码流超前于本地时钟△T示意图

从码流上跳沿的角度来看,若将码流code_in与本地时钟clk进行逻辑相与,若相与结果为“1”则说明码流滞后于本地时钟,若为“0”则说明码流超前于本地时钟。

用VHDL语言描述为:

if (code_in’event and code_in=’1’) then

if (code_in and clk)=’1’ then

q<=’1’

else

q<=’0’

end if

end if

程序中输出信号q可作为控制电路的输入信号。

本设计方案的系统框图如图3所示:

框图中,鉴相器作用是鉴别出码流和本地时钟的相位超前滞后关系,控制计数器采用双向计数器,鉴相器输出q作为控制计数器的计数方向输入,q为1则向上计数,q为0则向下计数。

控制计数器的计数输出用来控制相位调整选择模块的选择端。

相位调整选择模块由相位调整和相位选择功能。

图3 系统功能框图

3 设计实现

依据图3系统功能框图,利用Altera 公司的Quartus II 设计软件,采用自顶向下的模块化设计方法,用VHDL 语言和电路原理图混合输入设计对位同步时钟提取电路的各个部件分别进行设计。

本设计方案的鉴相器原理相对简单,不需要用VHDL语言设计,仅用两个

与门和一个D触发器就可以实

现,如图4 所示。

图中的

的第二个与门(inst23)是为了实现D

触发器的时钟输入端与数据输入端

同步。

控制计数器设计使用Quartus

II的MegaWizard Plug_In

Manager工具来实现一个简单

的双向

数器,计数方向由鉴相器输出q控

制,q为1则计数器向上计数,q为0则计数器向下计数,计数系数由Count Modulus设定,设定的数值要求等于分频器的分频系数N。

在原理图输入时可以任意改变分频器的分频系数和计数器的计数系数。

分频器设计输出时钟信号的占空比为50%,且分频系数N可调,用VHDL 语言实现并由软件自动生成元件符号供原理图调用,如图5所示。

下面给出分频器的VHDL语言关键描述语句

if(clk'event and clk='1') then

if(count=N-1)then --计数周期

count<=0;

else

count<=count+1;

if count<(integer(N/2)) then

--产生分频脉冲

outclk<='0';

else

outclk<='1';

end if;

end if;

end if;

相位调整选择模块的相位调整功能可以用延迟方式实现。

在FPGA中要产生延时,信号必须经过一定的物理资源。

在硬件描述语言中有关键词Wait for xx ns,需要说明的是该语法是仅仅用于仿真而不能用于综合的,可综合的延时方法有:

(1)使信号经过逻辑门得到延时(如非门);

(2) 使用器件提供的延时单元(如Altera公司的LCELL);

(3)使用移位寄存器。

由于当使用多级非门的时候综合器往往会将其优化掉,因为综合器会认为一个信号非两次还是它自己,而且门延迟时间相对于具体器件是不固定的,LCELL延时单元也可以用来产生一定的延时,但这样形成的延时在FPGA芯片中并不稳定,会随温度等外部环境的改变而改变,并且门延迟和LCELL延迟时间都无法实现用户动态调整,不利于移植和调用,因此本设计的延迟采用由D触发器构成的移位寄存器实现,如图6所示,移位寄存器时钟输入端为内部时钟Clk_n,移位数据输入端为Clk_n的分频输出Clk1,如果Clk_n的频率为f0,分频器分频系数为N,则Clk1的频率为N×f0,并要求其等于Clk的频率即:f = N×f0。

相位调整选择模块的单位延迟时间决定了设计的时钟提取电路的精度。

单位延迟时间由内部时钟Clk_n决定,单位延迟时间为移位寄存器发生一次移位的时间也就是D触发器的触发时钟周期即为t = 1/f0 。

位同步时钟锁定时间由内部时钟Clk_n和分频器的分频系数N决定,显然Clk1最多经过N-1次移位时才可以与码流时钟锁定,则最大锁定时间为(N-1)/f0 ;Clk1最少经过1次移位就可以与码流时钟锁定,所以位同步时钟最小锁定时间为1/f0。

相位调整选择模块的相位选择功能由多选一多路选择器实现,对应图4的10

位的移位寄存器,可以采用图6所示的10选1多路选择器Mux10to1。

多路选择器的多选一选择端输入由双向计数器的计数输出端qn提供。

另外,Mux10to1输出端连接D触发器目的是为了消除毛刺。

此触发器的输出信号就是位同步时钟提取的输出信号,当然,作为一个锁相环结构的位同步提取电路,这个时钟信号会作为反馈引入鉴相器的输入端,与输入码流进行相与鉴相。

下面给出仿真波形,器件选择为Altera的Cyclone II系列FPGA芯片Ep2c5,

内部时钟为200MHz,码流时钟为20MHz,分频系

数和计数系数都选择为10。

4 本设计方案性能

本位同步提取电路比通常广泛采用的锁相环路法,有如下有点:

(1)本设计并没有应用复杂的算法实现锁相功能,也没有采用传统的添扣们结

构,电路结构简单易懂,节省硬件资源,占用器件资源情况如下:Device EP2C5Q208C8

Total logic elements 71 / 4,608 ( 2 % )

Total registers 49

Total pins 3 / 142 ( 2 % )

Total virtual pins 0

Total memory bits 0 / 119,808 ( 0 % )

Embedded Multiplier 9-bit elements 0 / 26 ( 0 % )

Total Plls 0 / 2 ( 0 % )

(2)本设计位同步时钟锁定时间较短,速度比较快(由设计时钟选择决定)。

(3)精度较高,并具有可调整性,时钟抖噪参数可以通过改变分频器分频系数和计数器计数系数调整,并可以实现频率很宽范围的码流的位同步时钟提取,因而本设计方案可以生成元件符号在各种FPGA芯片和部分CPLD芯片设计中调用,节省用户设计时间,缩短设计周期,具有很高的商用价值。

5结束语

本位同步时钟提取方案已经成功的用FPGA器件进行了实现,并在作者设计的数字通信系统中得到应用。

通过对此电路的测试和使用表明,此时钟提取电路可以快速准确地对高速串行输入码流进行位同步时钟提取,即使输入码流中的毛刺现象,本设计电路也有很好的时钟调整恢复功能,极大的减小了误码率。

由于本设计简单占有硬件资源少,因为可以同时调用多个时钟提取电路来提取多路同时输入的不同速度的串行码流的同步时钟,为下一步的数字复接提供了方便。

参考文献

[1]廖日坤,CPLD/FPGA嵌入式应用开发技术白金手册,中国电力出版社,2005

[2]陈世伟,锁相环路原理及应用,兵器工业出版社,1990

[3]段吉海,黄志伟,王毓银,基于CPLD/FPGA的数字通信系统建模与设计,2004。