多周期微处理器设计

- 格式:pdf

- 大小:1.28 MB

- 文档页数:15

MIPS架构多周期CPU的设计蔡晓燕;袁春风;张泽生【摘要】针对教育部最新提出的计算机专业系统结构课程设置要求,分析利用VerilogHDL代码完成多周期CPU设计的具体过程和方案,以南京大学计算机科学与技术系为例,总结将其应用在教学上的效果。

提出在计算机专业本科教学阶段可进行计算机组成与设计相关实践课程教学的观点。

【期刊名称】《计算机教育》【年(卷),期】2014(000)017【总页数】4页(P93-96)【关键词】MIPS架构;多周期;数据通路;状态图【作者】蔡晓燕;袁春风;张泽生【作者单位】南京大学计算机科学与技术系江苏南京 210046;南京大学计算机科学与技术系江苏南京 210046;南京大学计算机科学与技术系江苏南京210046【正文语种】中文【中图分类】G642近年来,教育部计算机专业教学指导委员会组织了对该专业学生能力培养和实践教学体系的研究。

研究指出,教学必须树立系统观,培养学生的系统眼光。

使学生学会在不同层面把握不同层次的系统,并全面考虑系统各部分与外界的逻辑与联系,能够完成一定规模的系统设计[1]。

研究还指出,有了计算机系统基础和计算机组成与设计课程的基础,学生将更容易从计算机系统整体角度理解操作系统、编译原理等后续课程[1]。

研究确定以MIPS为模型机进行讲解,讲透原理,强化实践。

MIPS架构的微处理器是最简单的体系结构之一,作为一种开放的架构,用户可自行开发MIPS内核,并在其中添加指令。

MIPS架构被国际上许多著名大学用于计算机系统结构的本科生和研究生教学。

CPU结构由其所能够执行的指令决定,MIPS 32位架构是一种采用RISC(精简指令集)的处理器架构,它指令长度固定,采用load/store数据模型,算术和逻辑运算采用三目操作数的形式,带有32个通用寄存器[2-3]。

自2007年起开始,南京大学计算机科学与技术系开始探索用Verilog HDL代码实现MIPS架构多周期CPU设计。

高性能微处理器结构设计与优化研究在当今数字化的时代,微处理器已经成为了一个非常重要的基础设施。

微处理器广泛应用在各种电子产品中,如手机、电脑、服务器等等,作为CPU的核心部件,其性能直接影响着整个系统的工作效率和稳定性。

在这样的背景下,高性能微处理器的研究和优化也变得越来越重要。

从最初的微处理器出现至今,性能的发展已经取得了巨大的进步。

英特尔公司的X86系列处理器已经发展成为了全球性能最快的产品之一。

例如,最近发布的英特尔酷睿i9-11900K处理器拥有8个核心、16个线程,最高主频可达到5.3GHz,配合高速内存和大容量存储,可以提供前所未有的运行速度和快速响应。

高性能微处理器的构成一般由多个部分组成,其中最为核心的部分就是计算单元。

计算单元可以分为算术逻辑单元(ALU)和浮点逻辑单元(FPU)两种。

ALU主要完成整数运算,如加减乘除等,而FPU则主要用于浮点运算,如加减乘除、开根、三角函数等。

同时,高性能微处理器还包括缓存、穿透缓存、磁盘控制器等模块,以及一些特殊用途的协处理器和图像加速器等。

高性能微处理器的设计和优化是一个非常复杂的任务,需要多个专业领域的知识和技术结合才能完成。

优化技术非常多,如:1. 指令优化技术指令优化技术主要是通过改变指令执行的顺序和方式来提高微处理器的性能。

例如,采用超标量设计和预测分支等方式可以提高处理器的吞吐量和效率。

2. 缓存优化技术缓存优化技术主要是通过调整缓存大小和级别,改善缓存访问策略,以及采用智能预取等方法来提高缓存的利用率和效率。

3. 浮点运算优化技术浮点运算优化技术主要是通过改善浮点运算单元的设计和实现方式,如使用超标量技术和硬件浮点加速器等,来提高浮点运算的速度和精度。

近年来,随着人工智能、深度学习、云计算等领域的快速发展,高性能微处理器也面临巨大的挑战。

为了满足这些新应用的需求,微处理器的设计和优化技术需要不断地更新和升级。

同时,新的硬件架构和虚拟化技术也在不断涌现。

微处理器的设计及性能优化微处理器是现代电子设备中不可或缺的一部分,它负责处理设备内部的数据和操作,从而使设备得以正常工作。

微处理器被广泛应用于计算机、手机、家电、汽车等各个领域。

本文将就微处理器的设计及性能优化展开详细的探讨。

一、微处理器的基本结构微处理器可以分为数据通路和控制单元两部分。

其中数据通路用于处理数据,而控制单元则负责控制数据通路的运行。

数据通路由运算单元、寄存器堆、数据缓存和总线组成,它们的协同工作使得微处理器能够对数据进行各种处理操作。

控制单元由时钟、指令译码器和状态机等组成,它控制数据通路的执行,使得微处理器能够实现复杂的计算和处理任务。

二、微处理器的设计流程微处理器的设计流程一般包括指令集架构设计、逻辑设计、物理设计和验证测试等环节。

1. 指令集架构设计指令集架构是微处理器的核心,它决定了微处理器能够执行哪些指令和操作。

在设计指令集架构时,需要考虑指令的复杂度和效率、寄存器数量和位宽、总线结构和数据缓存等问题。

这些问题的决策将直接影响微处理器的性能和功耗。

2. 逻辑设计逻辑设计是将指令集架构转化为电路设计的过程,它涉及到微处理器各个组成部分的电路设计。

在逻辑设计过程中,需要根据指令集架构设计各个时序和逻辑方案,保证微处理器的功能正确且效率高。

3. 物理设计物理设计是将逻辑电路转化为标准元件的物理电路实现。

在物理设计过程中,需要考虑芯片尺寸、功耗、散热等问题。

同时,还要进行电路布图和版图设计,保证电路的正确性和可靠性。

4. 验证测试在微处理器设计完成后,需要进行验收测试,以验证微处理器电路的正确性和性能。

测试方法包括仿真验证和硬件实验测试。

通过验证测试,可以发现设计中存在的问题,并对它们进行改善和优化。

三、微处理器的性能优化微处理器的性能优化是实现高性能芯片的关键。

针对不同应用场景和需求,有以下几种性能优化方法。

1. 时钟频率优化时钟频率是微处理器性能的一个关键指标,它决定了微处理器单位时间内能够执行的指令数量。

实验报告课程名称:数字系统设计实验Ⅱ学院:信电系数字系统设计实验Ⅱ流水线MIPS微处理器设计ContentsPart 1实验目的 (3)Part 2实验任务 (3)Part 3实验原理 (4)Part 4实验步骤 (12)1.IF级设计 (12)2.ID级设计 (14)3.Decode单元设计 (16)4.ALU单元设计 (22)5.EX级设计 (27)6.顶层模块设计 (29)Part 5仿真和波形分析 (37)1.IF级仿真分析 (37)2.Decode单元仿真分析 (38)3.ALU仿真分析 (40)4.顶层仿真分析 (41)Part 6心得 (42)实验报告一、实验目的(1)了解提高CPU性能的方法。

(2)理解数据冒险、控制冒险的概念以及流水线冲突的解决方法。

(3)掌握流水线MIPS微处理器的工作原理。

(4)掌握流水线MIPS微处理器的测试方法。

二、实验任务设计一个32位流水线MIPS微处理器。

设计要求:(1)至少执行下列MIPS32指令。

①算数运算指令:ADD ADDU SUB SUBU ADDI ADDU②逻辑运算指令:AND OR NOR XOR ANDI ORI XORI SLT SLTI SLTU SLTIU③移位指令:SLL SLLV SRL SRLV SRA④条件分支指令:BEQ BNE BGEZ BGTZ BLEZ BLTZ⑤无条件跳转指令:J JR⑥数据传输指令:LW SW⑦空指令:NOP(2)在用5级流水线技术,对数据冒险实现转发或阻塞功能。

(3)在XUP Vietex-II Pro开发系统中实现MIPS微处理器,要求CPU的运行速度大于25MHz.三、实验原理1.流水线MIPS CPU总体设计与构建流水线是数字系统中一种提高系统稳定性和工作速度的方法,广泛应用在高档CPU的构建中。

根据MIPS处理器指令的特点,将整体的处理过程分为取指令(IF)、指令译码、执行、存储器访问和寄存器写回五级,对应多周期CPU的五个处理阶段。

MIPS指令多周期CPU设计MIPS(Microprocessor without Interlocked Pipeline Stages)是一种经典的指令集架构,也是一种常用的计算机体系结构之一、在本文中,将介绍如何设计一个多周期CPU来执行MIPS指令。

多周期CPU是一种在各个阶段使用不同时钟周期数的中央处理器设计。

其核心思想是将指令处理过程划分为若干个阶段,每个阶段由单独的硬件电路来执行。

通过这种方式,可以提高CPU的效率和性能。

下面将逐步介绍多周期CPU的设计步骤:1. 指令存储器(Instruction Memory):首先,需要设计一个指令存储器,用于存储MIPS指令。

指令存储器通常使用随机存取存储器(Random Access Memory, RAM),可以通过指令地址来读取指令。

2. 指令解码(Instruction Decode):在该阶段中,需要将从指令存储器中读取的指令进行解码。

解码的目的是确定指令的类型以及操作数的位置。

根据指令的类型,还需要通过控制信号来决定执行的下一步操作。

3. 寄存器读取(Register Read):在这个阶段中,需要从寄存器文件中读取操作数。

MIPS架构中有32个通用寄存器,它们存储着变量和数据。

4. 执行(Execute):在这个阶段中,需要执行指令的操作。

具体的操作取决于指令的类型。

例如,加法操作需要将操作数相加,存储结果。

5. 存储器访问(Memory Access):在这个阶段中,需要进行内存访问操作。

MIPS架构中,可以使用lw(load word)指令将数据从内存中加载到寄存器中,使用sw(store word)指令将数据从寄存器中存储到内存中。

6. 寄存器写入(Register Write):在这个阶段中,需要将执行阶段的结果写入到寄存器文件中。

以上是多周期CPU的基本设计流程。

在设计过程中,还需要考虑异常处理和分支跳转等特殊情况。

微处理器的架构与运行过程微处理器是现代计算机的核心元件,负责控制和执行计算机的各种指令和操作。

它的架构和运行过程是计算机科学中重要的基础知识。

本文将详细介绍微处理器的架构和运行过程,并分点列出每个步骤。

一、微处理器的架构1. 寄存器:微处理器包含多个寄存器,用于存储临时数据和地址。

常见的寄存器有累加器、指令寄存器、程序计数器等。

2. 控制单元:负责控制微处理器的操作,包括指令的获取、解码和执行。

3. 算术逻辑单元(ALU):负责执行算术和逻辑运算,如加法、减法、与、或等。

4. 数据通路:用于传输数据和指令,连接寄存器、控制单元和ALU。

二、微处理器的运行过程1. 指令获取阶段- 程序计数器(PC)存储下一条指令的地址。

- 控制单元根据PC中的地址访问存储器,将指令读入指令寄存器(IR)。

2. 指令解码阶段- 控制单元从IR中解码指令的操作码和操作数。

- 控制单元根据操作码控制数据通路的操作。

3. 操作数寻址阶段- 根据操作数的地址模式,计算出操作数的真实地址。

- 控制单元从寄存器或存储器中获取操作数,存入寄存器。

4. 指令执行阶段- 控制单元根据操作码和操作数执行具体的指令。

- ALU执行算术和逻辑运算,将结果存入寄存器。

5. 结果写回阶段- 将运算结果写回寄存器或存储器,以便后续的指令使用。

- 更新程序计数器(PC),跳转到下一条指令。

三、微处理器运行过程中的关键技术1. 管道技术:将指令的执行过程划分为多个阶段,使多条指令可以同时执行,提高处理器的性能。

2. 流水线冒险:由于指令执行的依赖关系,可能会出现数据冒险、控制冒险等问题,需要通过乱序执行、数据前推等技术解决。

3. 缓存技术:为了加快指令和数据的访问速度,提供了多级缓存来存储经常访问的数据和指令。

4. 中断处理:当外部事件发生时,微处理器需要暂停当前的指令执行,保存现场,处理中断请求,并在处理完后返回之前的执行状态。

四、微处理器的应用领域1. 个人计算机(PC)和服务器:微处理器是PC和服务器的核心部件,负责控制和执行各种计算和操作。

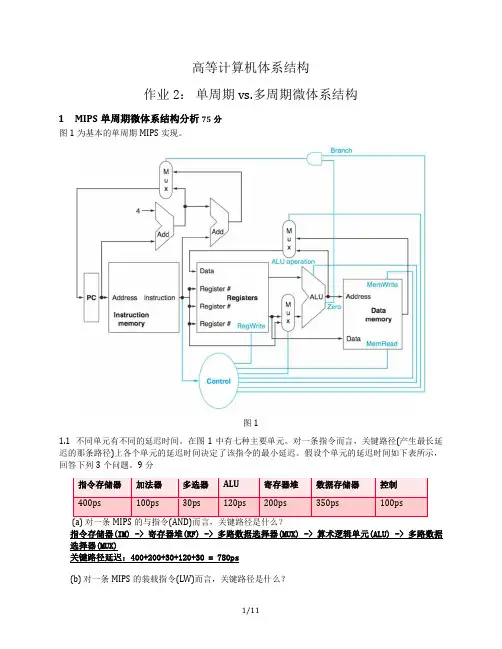

高等计算机体系结构作业2:单周期vs.多周期微体系结构1MIPS单周期微体系结构分析75分图1为基本的单周期MIPS实现。

图11.1 不同单元有不同的延迟时间。

在图1中有七种主要单元。

对一条指令而言,关键路径(产生最长延迟的那条路径)上各个单元的延迟时间决定了该指令的最小延迟。

假设个单元的延迟时间如下表所示,回答下列3个问题。

9分指令存储器(IM) -> 寄存器堆(RF) -> 多路数据选择器(MUX) -> 算术逻辑单元(ALU) -> 多路数据选择器(MUX)关键路径延迟:400+200+30+120+30 = 780ps(b) 对一条MIPS的装载指令(LW)而言,关键路径是什么?指令存储器(IM) -> 寄存器堆(RF) -> 多路数据选择器(MUX) -> 算术逻辑单元(ALU) -> 数据存储器(DM) -> 多路数据选择器(MUX)关键路径延迟:400+200+30+120+350+30 = 1130ps(c) 对一条MIPS的相等则分支指令(BEQ)而言,关键路径是什么?指令存储器(IM) -> 寄存器堆(RF) -> 多路数据选择器(MUX) -> 算术逻辑单元(ALU) -> 多路数据选择器(MUX)关键路径延迟:400+200+30+120+30+200 = 780ps1.2 图1中基本的单周期MIPS实现仅能实现某些指令。

可以在这个指令集中加入新的指令,但决定是否加入取决于给处理器的数据通路和数据通路增加的复杂度。

对于下表中的新指令而言,试回答下列3个问题。

18分(a) 对上述指令而言,哪些已有的单元还可以被使用?指令存储器(IM)、寄存器堆(RF)现存的读取数据端口和数据输出端口、算术逻辑单元(ALU)(b) 对上述指令而言,还需要增加哪些功能单元?寄存器的另一个读取端口(用于读取Rx)和第二个ALU(用于将Rx与Rs+Rt相加)(c) 为了支持这些指令,需要在控制单元增加哪些信号?需要一个控制信号来告诉新的ALU做什么,或者如果我们扩展了现有的ALU,我们需要添加一个新的ADD3操作。

2018 年软件2018,V〇1.39,N o. 8第 39 卷第 8 期COMPUTER ENGINEERING&SOFTWARE国际IT 传媒品牌基金项玛办文基于M IPS架构的多周期CPU设计柳成,荣静(扬州大学广陵学院,江苏扬州225000)摘要:为了提高多周期C P U流水线的效率,在指令存储器和数据存储器的数据读取中设计发送地址在上升 沿、读取数据在下降沿,从而实现译码和访存在一个周期内完成。

在取指级不再单独设置加法器,把PC+4放在ALU 中完成。

通过大量的多路选择器与数据交互总线来进行数据联通。

采用VerilogHDL语言设计出CPU,并在VIVADO 平台上实现仿真,最后通过龙芯公司的LS-CPU-EXB-002试验箱来进行验证,结果表明所设计的多周期C P U的有 效性。

关键词:流水线;V e r ilo g H D L;多周期C PU; L S-C P U-E X B-002试验箱中图分类号:TP332 文献标识码:A D O I: 10.3969/j.issn.l003-6970.2018.08.009本文著录格式:柳成,荣静•基于M IP S架构的多周期C P U设计[J].软件,2018, 39 (8):40-44Design of Multi-cycle CPU Based on MIPS ArchitectureLIU Cheng, RONG Jing(Guangling College ofYangzhou University, Yangzhou225000)【Abstract】:In order to improve the efficiency of the multi-cycle CPU pipeline,the designation of the sending ad-dress is on the rising edge and the reading data is on the falling edge in the data reading of the instruction memory and the data memory,so that the decoding and the access are completed in one cycle.The adder is no longer set separately at the fetch level,and PC+4 is placed in the ALU.Data communication is performed through a large number of multiplexers and data exchange buses.The CPU was designed using Verilog HDL language,and the simulation was implemented on the VIVADO platform.Finally,the verification was performed by the companyf s LS-CPU-EXB-002 test box.The results showed the effectiveness of the designed multi-cycle CPU.【Key words】:Pipeline;Verilog HDL;Multi-cycle CPU;LS-CPU-EXB-002 test box0引言M IPS架构是为流水线而生,每条M IPS指令的 执行分为五个部分,每一个部分为一个流水级。

微处理器的发展历史第一代:1971-1973年字长(4/8)典型产品:Intel 4004、4040, Intel8008Intel公司研制出MCS4微型计算机(CPU为4040,4位机)。

1971年,第一台微处理机4004由英特尔公司研制成功。

第二代:1974-1977年字长(8)典型产品:Intel8086,Motorola 6800,Zilog Z-80,Rockwell 6502 微型计算机的发展和改进阶段。

1975年,ATARI——8800微电脑问世。

1977年,柯莫道尔公司宣称全组合微电脑PET——2001研制成功。

1977年,TRS——80微电脑诞生。

1977年,苹果——II型微电脑诞生。

第三代:1978-1984年字长(16)典型产品:Intel 8086、8088、80186、8286,Motorola MC68000 16位微型计算机的发展阶段微型计算机代表产品是IBM-PC(CPU为8086)。

本阶段的顶峰产品是APPLE公司的Macintosh(1984年)和IBM公司的PC/AT286(1986年)微型计算机。

1979年,夏普公司宣布制成第一台手提式微电脑。

1982年,微电脑开始普及,大量进入学校和家庭。

1984年1月: Apple 的Macintosh发布。

基于Motorola 68000微处理器。

可以寻址16M。

第四代:1985-1991年字长(32)典型产品:Intel90386、80486,Motorola 68020、MC68030、68040,Z8000032位微型计算机的发展阶段Intel公司推出了Pentium或称P5(中文译名为“奔腾”)的微处理器,它具有64位的内部数据通道。

1985年10月17日: 80386 DX推出。

时钟频率到达33MHz,可寻址1GB内存。

比286更多的指令。

每秒6百万条指令,集成275000个晶体管。

1987: Macintosh II发布,基于Motorola 68020处理器。

大话计算机计算机系统底层架构原理极限剖析计算机是一种基础性的工具,它的发展已经深刻影响了人类社会的方方面面。

为了更好地理解计算机,我们需要从计算机系统的底层架构原理入手,深入剖析其设计与实现,揭示其中的奥秘。

计算机系统的底层架构主要包括硬件、操作系统和应用软件。

其中,硬件是计算机系统的基础,包括中央处理器(CPU)、内存、存储设备、输入输出设备等。

操作系统是指控制计算机硬件和软件资源的程序,它为应用软件提供了统一的接口。

应用软件则是运行在计算机系统上的各种程序和应用,如文本编辑器、游戏、浏览器等。

计算机的核心是中央处理器,它负责执行计算机指令和控制计算机的操作。

CPU的设计涉及到电路设计、指令集和微架构等方面。

其中,指令集是CPU的操作码集合,是CPU与应用软件之间的桥梁,它直接影响到CPU的性能和使用效率。

CPU是所有计算机硬件组件中最复杂和精密的部件之一,包含了大量的逻辑门、存储单元和控制单元等。

从微架构的角度来看,CPU可以分为:单周期处理器、多周期处理器和流水线式处理器。

单周期处理器包含一个时钟周期内执行一条指令的逻辑,它简单易懂,但效率较低。

而多周期处理器和流水线式处理器采用分阶段的操作方式,可以在一个时钟周期内执行多条指令,性能更高。

内存是计算机数据存储的主要容器,也是计算机系统速度的瓶颈之一。

内存的设计要考虑到存储器结构、容量和速度等因素。

现代计算机已经采用了高速缓存存储器(Cache)和虚拟内存技术,以提高内存的访问速度和容量。

存储设备是计算机系统的另一个重要组成部分,包括硬盘、固态硬盘和光盘等。

存储设备的设计要考虑到容量、速度、可靠性和价格等方面,不同类型的存储设备适用于不同的应用场景。

输入输出设备是计算机系统与外部世界交互的接口,包括鼠标、键盘、显示器和打印机等。

输入输出设备的设计要考虑到易用性、响应速度和精度等因素。

操作系统是计算机系统的核心软件之一,它负责管理计算机各种资源,提供各种服务和接口,是应用软件运行的基础。

多处理器系统与CPU设计【导读】这篇⽂章中,我们会涉及到在多处理系统中的设计中可能遇到的⼀些核⼼问题并进⼀步探论多处理器系统的可扩展性和系统设计的关系。

最后,我们简单分析⼀下产量对CPU设计的影响 产量对于CPU⽣产的影响⽂章⽬录 DMA与缓存⼀致性多处理器的可扩展性可扩展性的测试—SPECjbb2000 其它服务器基准测试 CPU与系统架构设计设计数据库应⽤数据库的数据完整性 64位系统的有效性⼤内存系统产量对CPU⽣产的影响 像AthlonXP, Celeron, Duron, Pentium 3, Pentium 4, and PowerPC这样的CPU产量都很⼤,有些甚⾄达到了每⽉⼀百万颗的出货量。

像AthlonMP和双处理器版的Pentium处理器拥有与单处理器版相同的设计,但是最后的质检要严格的多,⼀般最后的出货量要⼩得多,但是从⽣产的⾓度来说,他们都是⼀样的。

有些CPU之所以产量⾼是因为他们是被⽤在桌⾯系统上,⽽桌⾯系统的数量⽐⼯作站和服务器系统要多得多,虽然⼤量和少量都是相对意义上的。

像Itaniums, Pentium 3 Xeon, Xeon MP, SledgeHammer, UltraSPARC这样的CPU都是不同的设计则有不同的产量,每⽉的产量⼀般在1000-10,000左右。

对于⼀个新的CPU设计,⼀般需要9个⽉的时间来测试,调整(对于第⼀颗样品),优化来使它适合⽣产并批量供应客户。

这会花费巨⼤,外加上设计所需的时间,如果是⼀个全新的设计则所花时间更多。

⼀个全新的CPU设计包含了芯⽚组和整个系统,4-6年间的开发成本最⾼会达到10亿美元。

销售出更多的基于同⼀内核设计的CPU意味着将成本更为平均的分摊出去,所以每颗CPU就可以更便宜。

⾼产量的CPU除了还有其他的⼀些优势,正如提⾼CPU的性能和产量在许多⽅⾯不过是⼀个统计数字的游戏。

例如,对⽣产过程或者设计做出⼀点⼩的修改,⼈们都不清楚这样是否会带来好处,或者这样做了之后带来好处是否是因为运⽓的关系。

微处理器系统设计课程设计版本v1.0专业:集成电路设计与集成系统班级:电路1303班姓名:周小朋学号:051360852016年6月20 ~ 2016年7月1日多周期微处理器设计注:非正式版,仅为初稿一、功能描述MIPS微处理器是典型的32位定长指令字RISC处理器,此次设计的微处理器是基于verilogHDL语言、兼容MIPS指令格式、带有I/O接口和中断处理电路、能够实现26条指令功能,并且可以在DE2开发板上进行下载验证的多周期CPU。

可以实现的指令包括,R型:add、addu、sub、subu、and、or、xor、nor、slt、sltu、sll、srl、sra、jr;I型:addi、addiu、lui、andi、ori、xori、lw、sw、beq、bne;J型:jal、jump。

并且可以实现一段流水灯程序,程序的样式为1)10101010->010*******切换间隔为0.5秒2)11110000->00001111,切换间隔为1秒。

两种样式通过按键控制。

二、设计方案1.总体设计方案此次设计是在前期课程已经设计好的单周期CPU上进行多周期CPU的设计,多周期指令的执行分为5个阶段:取指、译码、执行、访存、回写。

由于PC,指令存储器只能在需要时写入新值,因此必须有“写使能信号”控制。

可以用状态机来实现5个状态的转换以及控制信号的产生。

来控制此次设计要实现一段流水灯程序,总共有两组不同的花型切换。

可以先利用ori指令初始化第一组花型到两个寄存器,再利用SW指令将存到寄存器的花型读出存储到IO接口,通过LED显示,最后用J指令实现花型的循环,此即使第一组花型的实现。

接下来考虑按键切换到下一组花型,可以使用按键产生一个中断信号,当按下按键时,进入中断程序,在中断程序里边存储第二个花型及其花型切换与循环,实现方式与花型一相同。

时间的控制可以利用指令的条数进行控制,通过分频产生一个标准时钟,sw占用4个时钟周期,j型占用2个时钟周期,可以通过指令的条数来控制题目所需要的0.5s与1s。

花型跳转示意图如下:图1.流水灯实现示意图总体设计框图如下:图2.多周期CPU总体设计框图接口信号说明:信号名称方向说明备注Clk_50M IN DE2开发板提供的时钟频率Rst IN Cpu复位信号Int0 IN 中断0信号Int1 IN 中断1信号Led OUT Led的输出信号,即流水灯花型输出表1:多周期CPU接口信号说明2.详细设计方案2.1中断设计方案此次设计的处理器有两个中断,int0和int1,其中int0的优先级比int1高。

Cpu在响应中断之前,应该先保存中断的断点返回地址。

中断返回地址保存在专用寄存器中,int0保存在$26,int1保存在$27。

为了解决中断优先级和嵌套,引入屏蔽寄存器,如下图图3.中断屏蔽寄存器Int0相应条件为imask[0]==0,in1相应条件为imask[1]==0,imask[0]==0。

下来是入口地址的确定,响应中断时,可以修改PC为中断程序的地址,即中短入口地址。

最后通过JR指令返回程序断点。

结构框图如下:图4.中断结构框图当中断信号有效时,将intpc存入寄存器,并且修改PC的值为中断入口地址接口信号说明:信号名称方向说明备注Clock IN Cpu工作频率Wpc IN PC的写使能信号Int0 IN 中断0信号Int1 IN 中断1信号PC OUT 程序指针,中断时值为中断入口地址IntPC OUT 输出到寄存器的中断断点地址表2:中断接口信号说明2.2.IO接口设计方案此次设计的IO和与存储器采用统一编址的方式,地址空间如下图所示,图5.IO与RAM地址空间分配IO地址空间为:FF00H~FFFFH,存储器地址空间为:0000H~0FFFH。

当立即数的高8位为FF时,对IO进行读写,否则为存储器的读写。

IO的实现如下结构所示,LED_CTRL与KEY_ctrl分别为LED与键盘的片选信号图6.IO结构框图表3:IO接口信号说明三、指令分析3.1、指令功能分析1、R型指令分析此次实现的R型指令包括:add、addu、sub、subu、and、or、xor、nor、slt、sltu、sll、srl、sra、jr。

指令的[31:26]位为OP操作码,[25:21] 位为rs寄存器的地址,[20:16] 位为rt寄存器的地址、[15:11]位为rd寄存器的地址、[10:6] 位为移位操作移位的位数,[5:0]位为功能码。

表4 R型指令分析2、I型指令分析此次实现的I型指令包括:addi、addiu、lui、andi、ori、xori、lw、sw、beq、bne。

指令的[31:26]位为OP操作码,[25:21] 位为rs寄存器的地址,[20:16] 位为rt寄存器的地址、[15:0]位为立即数。

表5 I型指令分析3、J型指令分析此次实现的I型指令包括:jal、jump。

指令的[31:26]位为OP操作码,[25:0] 位为地址值。

表6 J型指令分析3.2指令执行过程分析图7.指令执行过程分析三、ROM与RAM替换调用DE2开发板的IPmemory资源,具体步骤如下J-type opjal000011jal 10000$31<-PC+4;goto 10000$31<-PC+4 ; PC <-(PC+4)[31..28],address,0,0;address=10000/4jump000010j 10000goto 10000PC <-(PC+4)[31:28],address,0,0;address=10000/4addressaddressaddress图8.调用IP核实现指令ROM图9.调用IP核实现指令ROM四、验证方案:1.cpu功能验证此次设计的仿真验证程序为:先运行主程序,接着调用加法子程序,完成对四个数加法得到结果并存储,涉及到的指令有lui、ori、addi、jal、add、lw、bne、sll、jr。

接着进行其他指令的验证,指令包括:sw、sub、subu、addu、xori、addiu、andi、or、xor、and、nor、sra、slt、sltujump。

数据存储器存储的数据如下:Ram[14]:000000A3; % 0+A3=A3Ram[15]:00000027; % A3+27=CARam[16]:00000079; % CA+79=143Ram[17]:000000115; % 143+115=258仿真验证时,子程序运行后加法的结果应为258。

程序具体的功能以及涉及到的寄存器、运算结果如下所示:5'h00=32'h3c01_0000; //00 lui main r1,05'h01=32'h3424_0050; //04 ori r4,r1,805'h02=32'h2005_0004; //08 addi r5,r0,45'h03=32'h0c00_0018; //0c jal call:jal sum5'h04=32'hac82_0000; //10 sw r2,0(r4)5'h05=32'h8c89_0000; //14 lw r9,0(r4)5'h06=32'h0124_4022; //18 sub sub r8,r9,r45'h07=32'h2005_0003; //1c addi r5,r0,35'h08=32'h01a5_ff21; //20 addu5'h09=32'h34a8_ffff; //24 ori r8,r5,0xffff5'h0A=32'h3908_5555; //28 xori r8,r8,0x55555'h0B=32'h240a_ffff; //2c addiu5'h0C=32'h312a_ffff; //30 andi r10,r9,0xffff5'h0D=32'h0145_3025; //34 or r6,r10,r55'h0E=32'h0148_4026; //38 xor r8,r10,r85'h0F=32'h0146_3824; //3c and r7,r10,r65'h10=32'h014a_4027; //40 nor5'h11=32'h0008_4400; //44 sll r8,r8,165'h12=32'h0008_4403; //48 sra r8,r8,165'h13=32'h0005_43c0; //4c sll r8,r5, 155'h14=32'h0008_43c2; //50 sll r8,r8,155'h15=32'h0008_432a; //54 slt5'h16=32'h0008_432b; //58 sltu5'h17=32'h0800_0017; //5c jump finish:dead loop5'h18=32'h0000_4020; //60 add r8,r0,r05'h19=32'h8c89_0000; //64 lw r9,0(r4)5'h1A=32'h2084_0004; //68 addi r4,r4,45'h1B=32'h0109_4020; //6c add r8,r8,r95'h1C=32'h20a5_ffff; //70 addi r5,r5,-15'h1D=32'h14a0_fffb; //74 bne r5,r0,loop5'h1E=32'h0008_1000; //78 sll r2,r8,05'h1F=32'h03e0_0008; //7c jr r31 return4.2,LED流水灯实现验证方案设计一段实现题目要求的流水灯的花型,程序如下:001 : 342400aa;002 : 34250155;003 : ac04ff00;004 : ac04ff00;005 : ac05ff00;006 : 08000003;007 : 342600f0;008 : 3427000f;009 : ac06ff00;00a : ac06ff00;00b : ac06ff00;00c : ac06ff00;00d : ac07ff00;00e : ac07ff00;00f : ac07ff00;010 : ac07ff00;011 : 08000009;4.2.1仿真验证通过modelsim进行仿真分析,验证led输出是否为aa~155,短信号后为f0,0f4.2.2下载到开发板进行验证此次下载用的开发板型号为DE2,用quartus进行综合布局布线以及下载,如下图所示:图10.DE2开发板图11.综合布局布线、生成下载文件图12.综合报告(占用的资源)图图13.管脚分配图14.下载成功四、结果分析:1、逻辑功能仿真分析在Modelsim中对设计仿真,对照验证方案对仿真结果进行指令功能分析。