正弦信号发生器的设计

- 格式:doc

- 大小:144.04 KB

- 文档页数:11

基于FPGA的DDS正弦信号发生器的设计和实现引言在电子领域中,正弦信号是一种重要的基础信号,被广泛应用于通信、音频、视频等各个领域。

而DDS(Direct Digital Synthesis)直接数字合成技术则是一种通过数字方式生成高精度、高稳定性的正弦波信号的方法。

本文将详细介绍基于FPGA的DDS正弦信号发生器的设计和实现。

设计目标本次设计旨在实现一个可配置频率范围广泛且精度高的DDS正弦信号发生器。

具体设计目标如下: 1. 实现频率范围可调节,覆盖从几Hz到数十MHz; 2. 提供高精度的频率控制,满足特定应用场景对频率稳定性和相位精度的要求; 3. 支持模数转换器(DAC)输出,并能够通过外部接口控制输出幅值; 4. 使用FPGA作为主要硬件平台,以满足高速计算和灵活配置需求。

系统架构基于FPGA的DDS正弦信号发生器主要由以下几个部分组成: 1. 数字控制模块(Digital Control Module):负责接收外部输入的频率、相位和幅值等参数,并将其转换为对DDS核心模块的控制信号; 2. DDS核心模块(DDS Core Module):根据接收到的控制信号,通过数学运算生成正弦波形的离散采样值; 3. 数字模拟转换模块(Digital-to-Analog Converter, DAC):将DDS核心模块输出的数字采样值转换为模拟电压信号; 4. 输出放大器(Amplifier):用于放大DAC输出的电压信号,并通过外部接口提供可调节幅值的正弦波输出。

DDS核心模块设计DDS核心模块是整个系统中最关键的部分,它负责根据输入参数生成正弦波的离散采样值。

下面是DDS核心模块设计中需要考虑的几个关键要素:相位累加器相位累加器是DDS核心模块中最基础且重要的组件之一。

它根据输入的频率和时钟信号,在每个时钟周期内累加相位增量,从而实现相位连续变化。

相位累加器可以使用一个定点数或浮点数寄存器来表示,并通过固定步长进行相位递增。

利用LPM 设计正弦信号发生器一、设计目的:进一步熟悉maxplu sII 及其LPM 设计的运用。

二、设计要求:1、利用原理图输入方式。

2、信号数据点值自行想法实现。

3、得出正确时序仿真文件。

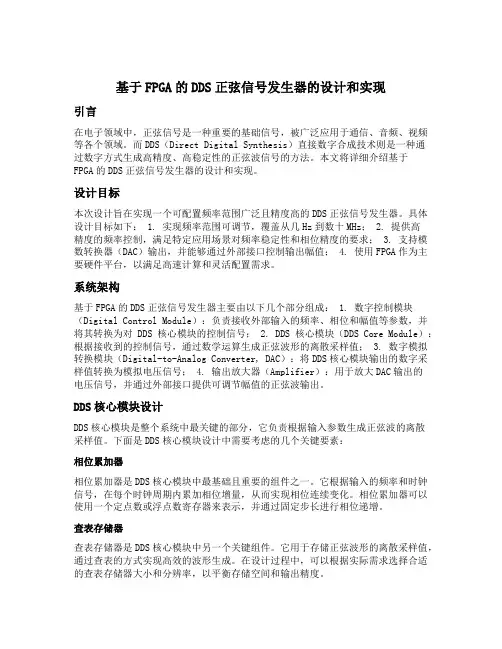

三、设计原理:图1 正弦信号发生器结构框图图1所示的正弦波信号发生器的结构由三部分组成计数器或地址发生器(这里选择8位),正弦信号数据ROM (8位地址线,8位数据线),含有256个8位数据(一个周期)。

四、VHDL 顶层设计。

设计步骤:1、建立.mif 格式文件建立C 语言文件sin.cpp ,运行产生sin.exe 文件。

sin.cpp 程序代码:#include <iostream>#include <cmath>#include <iomanip>using namespace std;int main(){int i;float s;VHDL 顶层设计sin.vhd8位计数器 (地址发生器) 正弦波数据 存储ROM 产生波形数据cout<<"WIDTH=8;\nDEPTH=256;\n\nADDRESS_RADIX=HEX;\nDA TA_R ADIX=HEX;\n\nCONTENT\nBEGIN\n";for(i=0;i<256;i++){s=sin(atan(1)*8*i/256);cout<<" "<<i<<" : "<<setbase(16)<<(int)((s+1)*255/2)<<";"<<endl;}cout<<"END"<<endl;return 0;}把上述程序编译后,在DOS命令行下执行命令:sin.exe > sin.mif;将生成的sin.mif 文件。

实验八正弦信号发生器的设计一、实验目的1、学习用VHDL设计波形发生器和扫频信号发生器。

2、掌握FPGA对D/A的接口和控制技术,学会LPM_ROM在波形发生器设计中的实用方法。

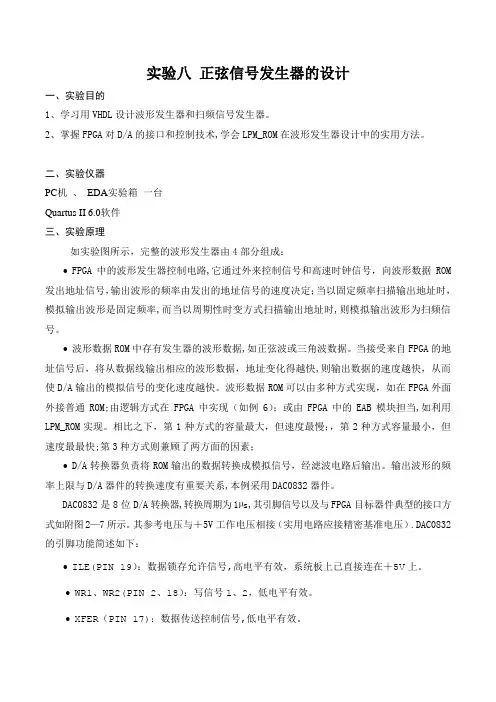

二、实验仪器PC机、EDA实验箱一台Quartus II 6.0软件三、实验原理如实验图所示,完整的波形发生器由4部分组成:• FPGA中的波形发生器控制电路,它通过外来控制信号和高速时钟信号,向波形数据ROM 发出地址信号,输出波形的频率由发出的地址信号的速度决定;当以固定频率扫描输出地址时,模拟输出波形是固定频率,而当以周期性时变方式扫描输出地址时,则模拟输出波形为扫频信号。

•波形数据ROM中存有发生器的波形数据,如正弦波或三角波数据。

当接受来自FPGA的地址信号后,将从数据线输出相应的波形数据,地址变化得越快,则输出数据的速度越快,从而使D/A输出的模拟信号的变化速度越快。

波形数据ROM可以由多种方式实现,如在FPGA外面外接普通ROM;由逻辑方式在FPGA中实现(如例6);或由FPGA中的EAB模块担当,如利用LPM_ROM实现。

相比之下,第1种方式的容量最大,但速度最慢;,第2种方式容量最小,但速度最最快;第3种方式则兼顾了两方面的因素;• D/A转换器负责将ROM输出的数据转换成模拟信号,经滤波电路后输出。

输出波形的频率上限与D/A器件的转换速度有重要关系,本例采用DAC0832器件。

DAC0832是8位D/A转换器,转换周期为1µs,其引脚信号以及与FPGA目标器件典型的接口方式如附图2—7所示。

其参考电压与+5V工作电压相接(实用电路应接精密基准电压).DAC0832的引脚功能简述如下:•ILE(PIN 19):数据锁存允许信号,高电平有效,系统板上已直接连在+5V上。

•WR1、WR2(PIN 2、18):写信号1、2,低电平有效。

•XFER(PIN 17):数据传送控制信号,低电平有效。

•VREF(PIN 8):基准电压,可正可负,-10V~+10V.•RFB(PIN 9):反馈电阻端。

实验四正弦信号发生器的设计1. 实验的目的和要求熟悉QuartusII 及其LPM_ROM 与FPGA 硬件资源的使用方法。

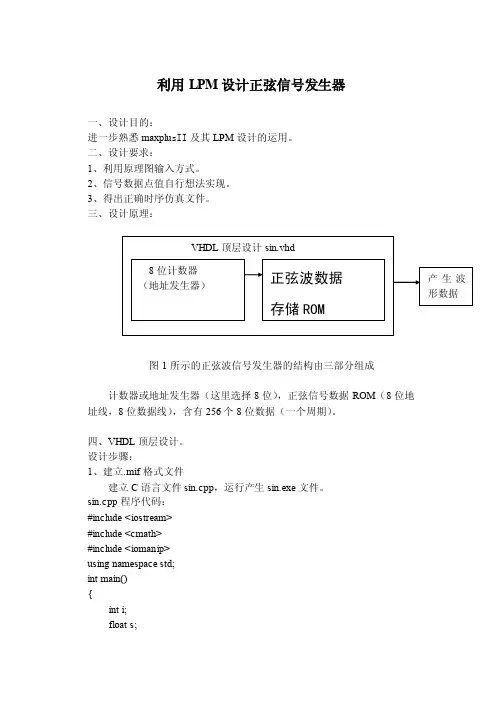

2.实践内容或原理正弦信号发生器的结构由3部分组成,数据计数器或地址发生器、数据ROM 和D/A 。

性能良好的正弦信号发生器的设计,要求此3部分具有高速性能,且数据ROM 在高速条件下,占用最少的逻辑资源,设计流程最便捷,波形数据获最方便。

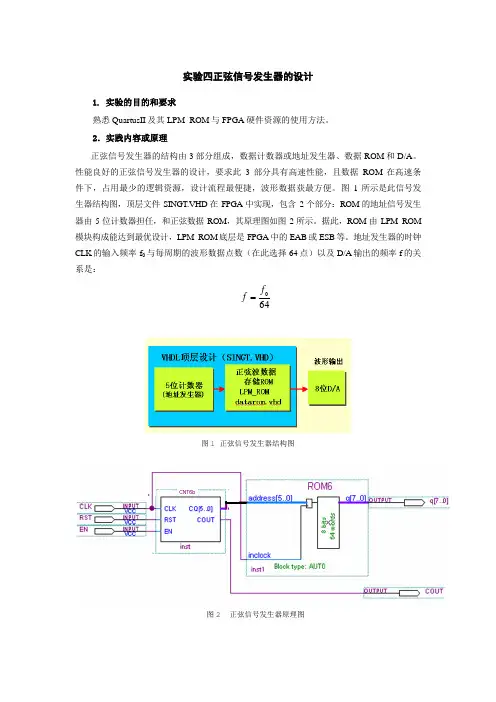

图1所示是此信号发生器结构图,顶层文件SINGT.VHD 在FPGA 中实现,包含2个部分:ROM 的地址信号发生器由5位计数器担任,和正弦数据ROM ,其原理图如图2所示。

据此,ROM 由LPM_ROM 模块构成能达到最优设计,LPM_ROM 底层是FPGA 中的EAB 或ESB 等。

地址发生器的时钟CLK 的输入频率f 0与每周期的波形数据点数(在此选择64点)以及D/A 输出的频率f 的关系是:640f f图1 正弦信号发生器结构图图2 正弦信号发生器原理图图3 正弦波的64个点的输入在Quartus II上完成正弦信号发生器设计,包括仿真和资源利用情况了解(假设利用Cyclone器件)。

最后在实验系统上实测,包括SignalTap II测试、FPGA中ROM的在系统数据读写测试和利用示波器测试。

最后完成EPCS1配置器件的编程。

3. 实验仪器(1)GW48系列SOPC/EDA实验开发系统(2)配套计算机及Quartus II 软件4.实践步骤或环节(1) 建立工程文件夹。

(2) 生成6位二进制计数器原理图。

(3)定制LPM_ROM元件。

(4)仿真。

(5)选择实验电路模式5,进行引脚下载配置。

(6)嵌入式逻辑分析仪的设置。

5. VHDL仿真实验(1)6位二进制计数器的仿真程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT6b ISPORT (CLK,RST,EN: IN STD_LOGIC;CQ: OUT STD_LOGIC_VECTOR (5 DOWNTO 0);COUT:OUT STD_LOGIC);END CNT6b;ARCHITECTURE behav OF CNT6b ISBEGINPROCESS(CLK,RST,EN)VARIABLE CQI:STD_LOGIC_VECTOR(5 DOWNTO 0); BEGINIF RST='1'THEN CQI:=(OTHERS=>'0');ELSIF CLK'EVENT AND CLK='1' THENIF EN='1' THENCQI:=CQI+1;END IF;END IF;IF CQI=63 THEN COUT<='1';ELSE COUT<='0';END IF;CQ<=CQI;END PROCESS;END behav;(2)RTL电路(3)时序仿真波形:(4)硬件验证选择试验箱的模式为模式5,时钟CLK选择为CLOCK0(PIN_28脚),频率f=65536Hz,EN对应的引脚编号PIN-233,RST对应的引脚编号PIN-234,COUT对应的引脚编号PIN-1,Q[7..0]对应的引脚编号PIN-20,19,18,17,16,15,14,13.(5)逻辑分析仪的测试波形6.实践教学报告要求(1)详细分析各模块的逻辑功能,及其他们工作原理,详细记录并分析实验内容和实验内容的过程和结果,完成实验报告。

课程设计I(论文)说明书(正弦波信号发生器设计)2010年1月19日摘要正弦波是通过信号发生器,产生正弦信号得到的波形,方波是通过对原信号进行整形得到的波形。

本文主要介绍了基于op07和555芯片的正弦波-方波函数发生器。

以op07和555定时器构成正弦波和方波的发生系统。

Op07放大器可以用于设计正弦信号,而正弦波可以通过555定时器构成的斯密特触发器整形后产生方波信号。

正弦波方波可以通过示波器检验所产生的信号。

测量其波形的幅度和频率观察是否达到要求,观察波形是否失真。

关键词:正弦波方波 op07 555定时器目录引言 (2)1 发生器系统设计 (2)1.1系统设计目标 (2)1.2 总体设计 (2)1.3具体参数设计 (4)2 发生器系统的仿真论证 (4)3 系统硬件的制作 (4)4 系统调试 (5)5 结论 (5)参考文献 (6)附录 (7)1引言正弦波和方波是在教学中经常遇到的两种波形。

本文简单介绍正弦波和方波产生的一种方式。

在这种方式中具体包含信号发生器的设计、系统的论证、硬件的制作,发生器系统的调制。

1、发生器系统的设计1.1发生器系统的设计目标设计正弦波和方波发生器,性能指标要求如下:1)频率范围100Hz-1KHz ;2)输出电压p p V ->1V ;3)波形特性:非线性失真~γ<5%。

1.2总体设计(1)正弦波设计:正弦波振荡电路由基本放大电路、反馈网络、选频网络组成。

2图1.1正弦波振荡电路产生的条件是要满足振幅平衡和相位平衡,即AF=1;φa+φb=±2nπ;A=X。

/Xid; F=Xf/X。

;正弦波振荡电路必须有基本放大电路,本设计以op07芯片作为其基本放大电路。

基本放大电路的输出和基本放大电路的负极连接电阻作为反馈网络。

反馈网络中两个反向二极管起到稳压的作用。

振荡电路的振荡频率f0是由相位平衡条件决定的。

一个振荡电路只在一个频率下满足相位平衡条件,这要求AF环路中包含一个具有选频特性的选频网络。

正弦信号发生器作者:程锟、晏婷婷、覃雄伟摘 要:本设计以凌阳SPCE061A 单片机为核心,基于直接数字频率合成(DDS )技术制作了一个频率值能任意调节的多功能信号源。

该信号源在1KHZ~10MHZ 范围能输出稳定可调的正弦波,并具有AM 、ASK 和PSK 等调制功能。

信号输出部分采用电流放大型宽带运放做电流放大,再用宽带电压运放做电压放大,很好地解决了带宽和带负载能力的要求。

系统采用液晶显示模组CPCL501显示和键盘控制功能,在Ω50负载电阻下输出的电压峰-峰值p p V -≥1V 可调。

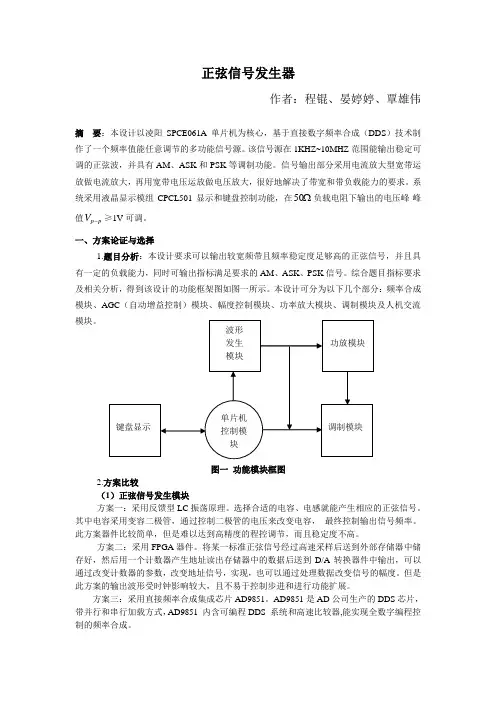

一、方案论证与选择1.题目分析:本设计要求可以输出较宽频带且频率稳定度足够高的正弦信号,并且具有一定的负载能力,同时可输出指标满足要求的AM 、ASK 、PSK 信号。

综合题目指标要求及相关分析,得到该设计的功能框架图如图一所示。

本设计可分为以下几个部分:频率合成模块、AGC (自动增益控制)模块、幅度控制模块、功率放大模块、调制模块及人机交流模块。

图一 功能模块框图2.方案比较(1)正弦信号发生模块方案一:采用反馈型LC 振荡原理。

选择合适的电容、电感就能产生相应的正弦信号。

其中电容采用变容二极管,通过控制二极管的电压来改变电容, 最终控制输出信号频率。

此方案器件比较简单,但是难以达到高精度的程控调节,而且稳定度不高。

方案二:采用FPGA 器件。

将某一标准正弦信号经过高速采样后送到外部存储器中储存好,然后用一个计数器产生地址读出存储器中的数据后送到D/A 转换器件中输出,可以通过改变计数器的参数,改变地址信号,实现,也可以通过处理数据改变信号的幅度。

但是此方案的输出波形受时钟影响较大,且不易于控制步进和进行功能扩展。

方案三:采用直接频率合成集成芯片AD9851。

AD9851是AD 公司生产的DDS 芯片,带并行和串行加载方式,AD9851 内含可编程DDS 系统和高速比较器,能实现全数字编程控制的频率合成。

简易正弦信号发生器设计

一、实验目的

1.进一步熟悉QuartusII及LPM-RAM宏模块与FPGA硬件资源的使用方法。

二、实验设备

计算机、和软件QuartusII和EDA/SOPC试验箱

三、试验内容

简易正弦信号发生器设计,要求ROM是8位数据线,8位地址线。

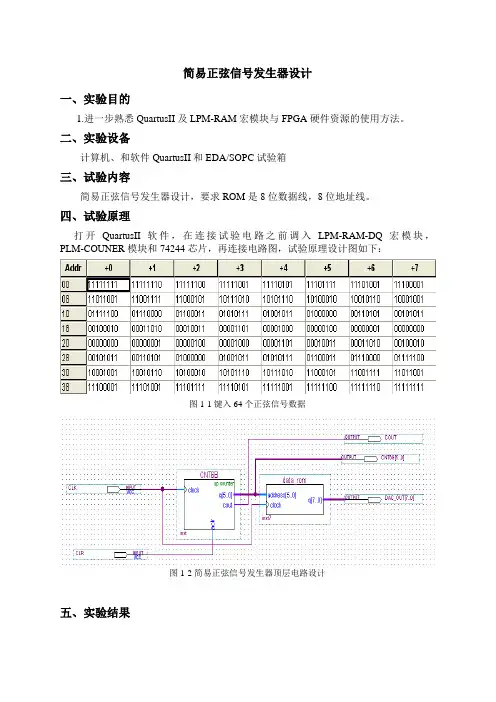

四、试验原理

打开QuartusII软件,在连接试验电路之前调入LPM-RAM-DQ宏模块,PLM-COUNER模块和74244芯片,再连接电路图,试验原理设计图如下:

图1-1键入64个正弦信号数据

图1-2简易正弦信号发生器顶层电路设计

五、实验结果

试验结果如下图:

图1-3综合后的RLT图

图1-4仿真波形图3.引脚锁定方案图

图1-5引脚锁定方案图

图1-6编程下载模式图

六、试验小节

一学期匆匆而过,通过大半学期的学习,我们学到了很多处理问题的技巧。

不过我们还要熟记很多单词,大多数的单词我们还不认识,相信通过进一步的学习,我们一定能学好这个软件。

我们也将以浓厚的兴趣和积极的态度去学习。

相信我们一定会有更加长足的进步。

高级数字系统设计实验——DDS正弦信号发生器设计姓名学号专业:通信与信息系统指导老师实验三 DDS 正弦信号发生器一、实验要求:利用LPM_ROM 设计一个DDS 正弦信号发生器,要求ROM 表长度为8位,频率控制字为8位,输出频率分辨率优于1Hz 。

二、设计方案 1、 方案流程图:由频率控制字提供,累加器在系统时钟控制下,来一个上升沿就累加一次频率控制字的值,累加器的位数高于8位,所以用其高8位作为正弦查表的地址,根据地址就能寻址到表内的值,该值通过DAC 转换再通过示波器就能显示波形。

累加器溢出一次就相当于正弦表寻址一圈,正弦信号经历一个周期。

2、参数设定系统时钟fclk :设定为50KHz ,频率控制字M :8位,取值范围:1~28-1, 分辨率:f=nfclk2 n 为累加器的位数,当系统时钟的频率越低,相位累加器的位数越高,所得到的频率分辨率就越高,累加器:为了使输出频率的分辨率能达到1Hz ,选定为16位, 输出频率:fout=n M fclk 2*=16250000M *=6553650000M*, 当M=1时,输出频率最小,fout=0.7629Hz ,当M=255时,输出频率最大,fout=0.7629*255=194.5496Hz 。

3、模块建立 1)累加器LIBRARY IEEE;USE IEEE.std_logic_1164.all;USE IEEE.std_logic_ARITH.ALL;USE IEEE.std_logic_unsigned.ALL;ENTITY add ISPORT(fclk : IN STD_LOGIC; --接入系统时钟rst : IN STD_LOGIC; --复位端fcontrol:IN STD_LOGIC_VECTOR(7 DOWNTO 0);--频率控制字8位asum:OUT STD_LOGIC_VECTOR(15 DOWNTO 0));--输出累加和END ENTITY;ARCHITECTURE behav OF add ISSIGNAL a:STD_LOGIC_VECTOR(15 DOWNTO 0);--累加器的暂存值SIGNAL fc:STD_LOGIC_VECTOR(7 DOWNTO 0);--频率控制字的寄存器BEGINfc<=fcontrol;PROCESS(fc,a,fclk,rst)BEGINIF(rst = '1' ) THENa <=(others=>'0');--复位端高电平有效ELSIF( fclk'event AND fclk = '1') THENa<=a+fc; --系统时钟来一个上升沿就累加一次频率控制字的值ELSENULL;END IF;asum<=a;--寄存器的值赋值给输出端END PROCESS;END behav;2)ROM表ROM表可以通过LPM宏功能模块来实现,通过MegaWizard管理器可以构建我们所需的存储单元,因为频率控制字为8位,DAC 采用实验箱上的THS5651为10位并行高速DAC,所以需要256个存储单元,每个单元为10bits。

正弦信号发生器实验报告引言本实验旨在设计并构建一个正弦信号发生器,用于产生具有特定频率和振幅的正弦波信号。

正弦信号在电子工程中具有广泛的应用,如通信系统、音频设备和信号处理等。

本实验将介绍设计思路、所需材料和步骤,以及实验结果和讨论。

设计思路为了设计一个正弦信号发生器,我们需要以下主要组件:1.振荡电路:产生正弦波信号的核心部分。

2.振幅调节电路:用于控制输出信号的振幅。

3.频率调节电路:用于控制输出信号的频率。

我们将使用基本的集成电路和电子元件来实现这些功能。

接下来,我们将逐步说明每个组件的设计和实现。

所需材料在开始实验之前,我们需要准备以下材料和工具:1.集成电路:例如操作放大器(Op-amp)。

2.电容器和电阻器:用于构建振荡电路和调节电路。

3.面包板:用于连接电子元件。

4.电源:为电路提供所需的电能。

5.示波器:用于测量信号的振幅和频率。

实验步骤1.第一步:振荡电路设计和构建–选择一个合适的振荡电路拓扑,如RC振荡电路。

–计算并选择所需的电容器和电阻器数值。

–使用面包板将电容器、电阻器和集成电路连接起来。

2.第二步:振幅调节电路设计和构建–选择一个合适的振幅调节电路拓扑,如非反相放大器。

–根据需要的振幅范围计算并选择所需的电阻器数值。

–使用面包板将电阻器和集成电路连接起来。

3.第三步:频率调节电路设计和构建–选择一个合适的频率调节电路拓扑,如电阻-电容调谐电路。

–根据需要的频率范围计算并选择所需的电容器和电阻器数值。

–使用面包板将电容器、电阻器和集成电路连接起来。

4.第四步:电源和示波器连接–将电源连接到电路以提供所需的电能。

–将示波器连接到电路以测量输出信号的振幅和频率。

5.第五步:实验验证和调试–打开电源,并使用示波器观察输出信号。

–调节振幅和频率调节电路,验证是否可以在所需范围内调节信号的振幅和频率。

实验结果和讨论经过实验验证和调试,我们成功设计和构建了一个正弦信号发生器。

该信号发生器能够在所需的频率范围内产生具有可调节振幅的正弦波信号。

正弦波信号发生器的设计及电路图正弦波信号发生器的设计结构上看,正弦波振荡电路就是一个没有输入信号的带选频网络的正反馈放大电路。

分析RC串并联选频网络的特性,根据正弦波振荡电路的两个条件,即振幅平衡与相位平衡,来选择合适的放大电路指标,来构成一个完整的振荡电路。

很多应用中都要用到范围可调的LC振荡器,它能够在电路输出负载变化时提供近似恒定的频率、几乎无谐波的输出。

电路必须提供足够的增益才能使低阻抗的LC电路起振,并调整振荡的幅度,以提高频率稳定性,减小THD(总谐波失真)。

1引言在实践中,广泛采用各种类型的信号产生电路,就其波形来说,可能是正弦波或非正弦波。

在通信、广播、电视系统中,都需要射频(高频)发射,这里的射频波就是载波,把音频(低频)、视频信号或脉冲信号运载出去,这就需要能产生高频信号的振荡器。

在工业、农业、生物医学等领域内,如高频感应加热、熔炼、淬火,超声波焊接,超声诊断,核磁共振成像等,都需要功率或大或小、频率或高或低的振荡器。

可见,正弦波振荡电路在各个科学技术部门的应用是十分广泛的。

2正弦波振荡电路的振荡条件从结构上来看,正弦波振荡电路就是一个没有输入信号的带选频网络的正反馈放大电路。

图1表示接成正反馈时,放大电路在输入信号某i=0时的方框图,改画一下,便得图2。

由图可知,如在放大电路的输入端(1端)外接一定频率、一定幅度的正弦波信号某a,经过基本放大电路和反馈网络所构成的环路传输后,在反馈网络的输出端(2端),得到反馈信号某f,如果某f与某a在大小和相位上一致,那么,就可以除去外接信号某a,而将1、2两端连接在一起(如图中的虚线所示)而形成闭环系统,其输出端可能继续维持与开环时一样的输出信号。

正弦信号发生器是信号中最常见的一种,它能输出一个幅度可调、频率可调的正弦信号,在这些信号发生器中,又以低频正弦信号发生器最为常用,在科学研究及生产实践中均有着广泛应用。

引言引言正弦信号发生器是信号中最常见的一种,它能输出一个幅度可调、频率可调的正弦信号,在这些信号发生器中,又以低频正弦信号发生器最为常用,在科学研究及生产实践中均有着广泛应用。

广泛应用。

目前,常用的信号发生器绝大部分是由模拟电路构成的,当这种模拟信号发生器用于低频信号输出往往需要的RC 值很大,这样不但参数准确度难以保证,而且体积大和功耗都很大,而由数字电路构成的低频信号发生器,虽然其低频性能好但体积较大,大,而由数字电路构成的低频信号发生器,虽然其低频性能好但体积较大,价格较贵,价格较贵,价格较贵,而本而本文借助DSP 运算速度高,系统集成度强的优势设计的这种信号发生器,比以前的数字式信号发生器具有速度更快,且实现更加简便。

号发生器具有速度更快,且实现更加简便。

系统原理系统原理一般的采样型SPWM 法分自然采样法和规则采样法,自然采样法是将基准正弦波与一个载波三角波相比较,由两者的交点决定开关模式的方法。

由于自然采样法得到的数学模型需要解超越方程,因而并不适合微控制器进行实时控制,又因为实践检验对称波形比非对称波形在三相电的相电流中引起的谐波失真小,所以我们使用对称规则采样法作为本系统的数学模型。

学模型。

这里说明一下使用TI 公司的DSP 芯片TMS320LF2407(以下简称2407)来产生PWM 信号的原理:由于产生一个PWM 信号需要有一个适合的定时器来重复产生一个与PWM 周期相同的计数周期,并用一个比较寄存器来保持调制值,并用一个比较寄存器来保持调制值,因此,因此,比较寄存器的值应不断与定时寄存器的值相比较,这样,当两个值相匹配时,时寄存器的值相比较,这样,当两个值相匹配时,就会在响应的输出上产生一个转换(从低就会在响应的输出上产生一个转换(从低到高或从高到低),从而产生输出脉冲,输出的开启,从而产生输出脉冲,输出的开启(或关闭)(或关闭)(或关闭)时间与被调制的数值成正比,时间与被调制的数值成正比,因此,改变调制数值,相关引脚上输出的脉冲信号的宽度也将随之改变。

学号:**********西北农林科技大学电子技术课程设计报告题目:正弦信号发生器(幅值频率可调)学院(系):机械与电子工程学院专业年级:学生姓名:指导教师:完成日期: 2013年7月3日目录1. 设计的任务与要求............................................................. - 2 -1.1 课题要求................................................................ - 2 -1.2具体要求................................................................. - 2 -1.3课题摘要:............................................................... - 2 -1.4设计步骤:............................................................... - 2 -2. 设计方案确定................................................................. - 3 -3. 硬件电路设计................................................................. - 4 -3.1整体电路框图............................................................. - 4 -3.2 主要元器件介绍.......................................................... - 4 -3.2.1 NE555芯片......................................................... - 4 -3.2.2 555定时器接成多谐振荡器.......................................... - 6 -3.2.3 NE5532P芯片....................................................... - 6 -3.3 整体电路设计............................................................ - 7 -3.4分立电路的设计及元件参数的选取及计算..................................... - 8 -3.4.1 555多谐振荡电路.................................................. - 8 -3.4.2带通滤波电路....................................................... - 8 -3.4.3反向比例运算放大器................................................. - 9 -4.调试与仿真................................................................... - 10 -4.1使用的主要仪器和仪表.................................................... - 10 -4.2分立电路的仿真(仿真图、操作的步骤、方法和结果)........................ - 10 -4.2.1 仿真图........................................................... - 10 -4.2.2仿真结果.......................................................... - 10 -4.3调试电路的方法和技巧:.................................................. - 12 -5. 总结........................................................................ - 13 -6. 参考文献.................................................................... - 15 - 附录一......................................................................... - 16 -1.元器件清单............................................................... - 16 -2.电路原理图............................................................... - 17 -3.PCB封装图................................................................ - 18 -4.3D效果图................................................................. - 21 -1. 设计的任务与要求1.1 课题要求:设计一个频率幅值可调的正弦信号发生器1.2具体要求:1.利用振荡电路产生正弦信号,要求有可调参数用以修改频率2.利用放大电路控制输出信号振幅。

制作一个正弦信号发生器的设计

一、正弦信号发生器的概念

正弦信号发生器是一种可以产生所需频率的正弦波信号的设备,可以

帮助开发者测量和分析频率特性,也可以用于相关系统的诊断。

正弦信号

发生器可以产生指定频率的正弦波形,以满足不同系统的需求。

它也可以

通过波形对比法进行精确的波形测量,用于分析电子系统特性。

(1)电路设计

正弦信号发生器的电路设计主要有两种:一种是基于模拟电路的设计,另一种是基于数字电路的设计。

(1)模拟电路

模拟电路设计采用的是电路模块,主要有振荡器、滤波器、缓冲器和

调制电路。

(a)振荡器

振荡器主要由振荡电路和调整元件组成,振荡器的作用是形成振荡的

正弦波,以满足信号发生器产生不同频率的要求。

(b)滤波器

滤波器的作用是滤除振荡器产生的额外噪声,以得到纯净的正弦信号。

(c)缓冲器

缓冲器的主要作用是将振荡器的正弦波输出,缓冲器的作用是减少信

号失真,使正弦波更加完美。

(d)调制电路

调制电路的作用是对信号发生器产生的正弦波进行调制,使其能够输出更加稳定的信号频率。

(2)数字电路

采用数字电路设计的正弦信号发生器。

★项目2:数字信号源

项目简述:设计制作一个正弦信号发生器。

(1)正弦波输出频率范围:1kHz~10MHz;

(2)具有频率设置功能,频率步进:100Hz;

(3)输出信号频率稳定度:优于10-2;

(4)输出电压幅度:1V到5V这间;

(5)失真度:用示波器观察时无明显失真。

(6)输出电压幅度:在频率范围内

50负载电阻上正弦信号输出电压的峰-峰值V opp=6V±1V;

(7)产生模拟幅度调制(AM)信号:在1MHz~10MHz范围内调制度m a可在30%~100%之间程控调节,步进量50%,正弦调制信号频率为1kHz,调制信号自行产生;

(8)产生模拟频率调制(FM)信号:在100kHz~10MHz频率范围内产生20kHz最大频偏,正弦调制信号频率为1kHz,调制信号自行产生;

(9)产生二进制PSK、ASK信号:在100kHz固定频率载波进行二进制键控,二进制基带序列码速率固定为10kbps,二进制基带序列信号自行产生;

开发时间:2007 开发人数:1

运行环境:windows xp、Quartus II

相关内容:(还未整体综合)

下面是调幅原理图:

下面是调频原理图:

下面是正弦信号发生器设计原理图:

下面是PSK设计原理图:。

正弦信号发生器摘要本系统以单片机和FPGA为控制和处理核心,基于直接数字频率合成原理,利用DDS集成芯片AD9851实现了300Hz~13MHz、步进为0.1Hz的正弦信号发生器和高频偏的DDS调频(FM)信号发生器;通过模拟乘法器MC1496实现调幅功能,其低频调制信号由FPGA和DAC0800构成DDS低频发生器产生;利用可变增益宽带放大器AD600实现幅度程控,通过检波和ADC反馈给单片机,检测和调整输出电压,实现精确的幅度控制。

使用了多种抗干扰措施以减少噪声并抑制高频自激;后级功放采用两片宽带运放AD811组成桥式功率放大器来实现。

本系统硬件设计应用了EDA工具,软件采用模块化的编程思想。

关键字:正弦信号发生器 DDS 调幅幅度控制桥式功率放大器AbstractBased on the principle of DDS, the system uses the A T89C51 and FPGA as the control and processing unit ,and uses the DDS chip AD9851 to realize the Sine and FM signal generator .The signal generator can output Sine signal of 300 Hz ~13M Hz with 0. 1 Hz frequency step, the MC 1496 is used to realize AM performance, the Amplitude control of signals are realized by using chip AD600,the low frequency modulation signal is produced by DDS made of FPGA and DAC 0800..Many methods are employed to diminish noises and restrain high frequency self-excitation. The test results show that the system achieves the requirements of design.正弦信号发生器一、方案论证与选择本系统难点有:1.产生稳定性高、频率步进较低、频带范围较广且具有一定带负载能力的正弦信号源;2.以1kHz为调制信号,在较大动态范围(100kHz~10MHz)内产生频偏为10kHz的调频信号;3.产生AM、ASK、PSK等调制信号。

基于fpga的dds正弦信号发生器的设计和实现

基于FPGA的DDS正弦信号发生器可以使用两种常见的实现

方法:Look-Up Table (LUT) 方法和相位累积器方法。

1. LUT方法:

- 首先,定义一个存储正弦波样本值的LUT (Look-Up Table),LUT的大小取决于所需的精度和波形频率范围。

- 使用一个计数器来生成一个相位值,该相位值是一个0到LUT大小之间的数字。

- 将该相位值作为索引,通过查找LUT来获取对应的正弦波

样本值。

- 将该正弦波样本值通过数字-模拟转换器(DAC)转换为模拟

信号输出。

2. 相位累积器方法:

- 使用一个固定频率的时钟作为参考信号输入,例如50 MHz。

- 使用一个相位累积器累积每个时钟周期的相位值。

- 计算相位值对应的正弦波样本值,并通过DAC转换为模拟信号输出。

- 相位累积器的更新频率由所需的输出频率确定,可以通过

增加或减小相位值的增量来调节输出频率。

需要注意的是,FPGA上实现DDS正弦信号发生器时,需要

一个高速的DAC来将数字信号转换为模拟信号输出。

同时,

为了提高性能和减少功耗,可以采用流水线技术,通过并行处理来提高输出频率的精度和速度。

此外,还可以通过添加相位调制、振幅调制等功能来进一步扩展DDS正弦信号发生器的

功能。

要设计和实现基于FPGA的DDS正弦信号发生器,可以使用硬件描述语言如Verilog或VHDL编写相应的代码,并使用FPGA开发工具进行综合、布局以及生成比特流文件。

最后,将比特流文件加载到目标FPGA芯片上,就可以实现DDS正弦信号发生器的功能。

XXXX大学现代科技学院DSP硬件电路设计基础课程设计设计名称正弦信号发生器的设计专业班级学号姓名DENG指导教师XXXX课程设计任务书注:上交(大张图纸不必装订)2.可根据实际内容需要续表,但应保持原格式不变。

日期:2014-12-10专业班级 XXXXXXX 学号 姓名 DENG 成绩设计题目正弦波信号发生器 设计目的学会使用CCS(Code Composer Studio)集成开发环境软件,在此集成开发环境下完成工程项目创建,程序编写,编译,链接,调试以及数据的分析。

同时完成一个正弦波信号发生器的程序的编写,并在集成开发环境下进行模拟运行,观察结果。

设计内容编写一个产生正弦波信号的程序,在CCS 软件下进行模拟运行,观察输出结果。

设计原理正弦波信号发生器已被广泛地应用于通信、仪器仪表和工业控制等领域的信号处理系统中。

通常有两种方法可以产生正弦波,分别为查表法和泰勒级数展开法。

查表法是通过查表的方式来实现正弦波,主要用于对精度要求不很高的场合。

泰勒级数展开法是根据泰勒展开式进行计算来实现正弦信号,它能精确地计算出一个角度的正弦和余弦值,且只需要较小的存储空间。

本次课程设计只要使用泰勒级数展开法来实现正弦波信号。

1. 产生正弦波的算法在高等数学中,正弦函数和余弦函数可以展开成泰勒级数,其表达式为若要计算一个角度x 的正弦和余弦值,可取泰勒级数的前5项进行近似计算。

……………………………………装………………………………………订…………………………………………线………………………………………由上述两个式子可以推导出递推公式,即sin(nx)=2cos(x)sin[(n-1)x]-sin[(n-2)x]cos(nx)=2cos(x)sin[(n-1)x]-cos[(n-2)x]由递推公式可以看出,在计算正弦和余弦值时,不仅需要已知cos(x),而且还需要sin[(n-1)x]、sin[(n-2)x]和cos[(n-2)x]。

2. 正弦波的实现⑴计算一个角度的正弦值利用泰勒级数的展开式,可计算一个角度x的正弦值,并采用子程序的调用方式。

在调用前先在数据存储器d_xs单元中存放x的弧度值,计算结果存放在d_sinx单元中。

⑵计算一个角度的余弦值利用余弦函数展开的泰勒级数的前五项计算一个角度的余弦值,可采用子程序的调用方式来实现。

调用前先将x弧度值放在数据存储器d_xc单元中,计算结果存放在d_cosx单元中。

⑶正弦波的实现利用计算一个角度的正弦值和余弦值程序可实现正弦波。

其实现步骤如下:第一步:利用sin_start和cos_start 子程序,计算 45°~0°(间隔为 0.5°)的正弦和余弦值;第二步:利用sin(2x)=2sin(x)cos(x)公式,计算 90°~0°的正弦值(间隔为1°);第三步:通过复制,获得359°~0°的正弦值;第四步:将359°~0°的正弦值重复从PA口输出,便可得到正弦波。

在实际应用中,正弦波是通过D/A口输出的。

选择每个正弦周期中的样点数、改变每个样点之间的延迟,就能够产生不同频率的波形,也可以利用软件改变波形的幅度以及起始相位。

总体方案设计1. 总体实现方案我们知道一个角度为x的正弦和余弦函数,都可以展开为泰勒级数,且其前五项可以看为:本程序的编程思想是这样的,正弦波的波形可以看为由无数点组成,这些点与x轴的每一个角度值相对应,那么我们可以利用DSP处理器处理大量重复计算的优势来计算,x轴每一点对应的y轴的值(在x轴取360个点来进行逼近),由于程序的编制采用小数形式,其弧度大于1的正弦值得不到,这就对正弦波的产生造成了障碍。

可由于正弦波的特殊的对称形式给程序的编制找到了出口。

Sin(∏/4)的弧度为0.7854<1,即0~∏/4之间的任意正弦、余弦值可以利用汇编程序得到N又可以利用公式:sin(2a)=2sin(a)cos(a) 得到0~∏/2 之间的正弦值。

而0~∏/2 之间的正弦曲线与∏/2~∏之间的正弦曲线通过x=∏/2这条轴左右对称,那么就可以得到∏/2~∏的正弦值,而0~∏的正弦曲线的相反数通过x=∏这条轴与∏~2∏左右对称。

这样∏~2∏的正弦值也得到了。

一个周期内完整的正弦波就得到了。

正弦波产生的流程图如下:2. 具体实现步骤本课程设计需要使用C54X汇编语言产生正弦波,并通过CCS的图形显示工具观察波形。

设计分以下几步完成:启动CCS,操作如下:1.建立新的工程文件:点击Project→New,保存文件名为sinx.pjt。

2.建立汇编源程序:点击File→New→Source File菜单命令,打开一个空白文档,将汇编源程序逐条输入后,单击Flie→Save菜单命令,文件类型保存为(*.asm),单击“保存”按钮,以上汇编程序被存盘。

3.建立连接命令文件:点击File→New→Source File菜单命令,打开一个空白文档,将链接命令文件逐条输入后,单击Flie→Save菜单命令,文件类型保存为(*.cmd),单击“保存”按钮,以上链接命令文件被存盘。

4.选择Project 菜单中的Add File to Project 选项,将汇编源程序sin.asm和链接定位sin.cmd文件依次添加到工程文件中。

5.选择Project 菜单中的Options 选项,并选择build options 项来修改或添加编译、连接中使用的参数。

选择Linker 窗口,在“Output Filename”栏中写入输出OUT 文件的名字,如sin.out,还可以设置生成的map文件名。

6.完成汇编,编译和链接,正确产生.out文件:点击Project菜单中的Rebuild all,请注意在监视窗口显示的汇编,编译和链接的相关信息。

如果没有错误,将产生sin.out文件;如果有错,在监视窗口以红色字体显示出错误行,用鼠标双击该行,光标跳将至源程序相应的出错行。

修改错误后,重新汇编链接。

7.在Project 选项中打开sin.pjt 文件,使用Build 选项完成编译、连接。

8.使用File 菜单中的Load Program 将OUT 文件装入。

然后选择Debug→Run,程序执行过程中可以使用Debug →Halt 暂停程序的执行。

9.选择View -> Graph -> Time/Frequency菜单打开一个图形显示窗口。

将“Start Address”项改为地址sin_x,将“Acquisition Buffer Size”项设置为360,将“Display Data Size”项设置为360,将“DSP Data Type”改为“16-bit signed integer”。

主要参数1.sin(theta)=x(1-x^2/2*3(1-x^2/4*5(1-x^2/6*7(1-x^2/8*9))))2. cos(theta)=1-x^2/2*3(1-x^2/4*5(1-x^2/6*7(1-x^2/8*9)))3. sin(2*theta)=2*sin(theta)*cos(theta)源程序1. 产生正弦波程序清单sin.asm.mmregs.def start.def d_xs,d_sinx,d_xc,d_cosx,sinx,cosxsin_x: .usect "sin_x",360STACK: .usect "STACK",10Hk_theta .set 286 ;theta=pi/360(0.5deg)start:.textSTM #STACK+10H,SPSTM k_theta,AR0STM 0,AR1STM #sin_x,AR6STM #90,BRCRPTB loop1-1LDM AR1,ALD #d_xs,DPSTL A,@d_xsSTL A,@d_xcCALL sinx ;d_sinx=sin(x)CALL cosx ;d_cosx=cos(x)LD #d_sinx,DPLD @d_sinx,16,A ;A=sin(x)MPYA @d_cosx ;B=sin(x)*cos(x)STH B,1,*AR6+ ;AR6----2*sin(x)MAR *AR1+0loop1: STM #sin_x+89, AR7 ;sin91(deg.)-sin179(deg.) STM #88,BRCRPTB loop2-1LD *AR7-,ASTL A,*AR6+loop2: STM #179,BRC ;sin180(deg.)-sin359(deg.) STM #sin_x,AR7RPTB loop3-1LD *AR7+,ANEG ASTL A,*AR6+loop3: STM #sin_x,AR6 ;generate sin waveSTM #1,AR0STM #360,BKB loop3sinx:.def d_xs,d_sinx.datatable_s .word 01C7H ;C1=1/(8*9).word 030BH ;C2=1/(6*7).word 0666H ;C3=1/(4*5).word 1556H ;C4=1/(2*3)d_coef_s .usect "coef_s",4d_xs .usect "sin_vars",1d_squr_xs .usect "sin_vars",1d_temp_s .usect "sin_vars",1d_sinx .usect "sin_vars",1d_l_s .usect "sin_vars",1.textSSBX FRCTSTM #d_coef_s,AR5 ;move coeffs table_sRPT #3MVPD #table_s,*AR5+STM #d_coef_s,AR3STM #d_xs,AR2STM #d_l_s,AR4ST #7FFFH,d_l_sSQUR *AR2+,A ;A=x^2ST A,*AR2 ;(AR2)=x^2||LD *AR4,B ;B=1MASR *AR2+,*AR3+,B,A ;A=1-x^2/72,T=x^2MPYA A ;A=T*A=x^2(1-x^2/72)STH A,*AR2 ;(d_temp)=x^2(1-x^2/72)MASR *AR2-,*AR3+,B,A ;A=1-x^2/42(1-x^2/72);T=x^2(1-x^2/72)MPYA *AR2+ ;B=x^2(1-x^2/42(1-x^2/72))ST B,*AR2 ;(d_temp)=x^2(1-x^2/42(1-x^2/72))||LD *AR4,B ;B=1MASR *AR2-,*AR3+,B,A ;A=1-x^2/20(1-x^2/42(1-x^2/72))MPYA *AR2+ ;B=x^2(1-x^2/20(1-x^2/42(1-x^2/72)))ST B,*AR2 ;(d_temp)=B||LD *AR4,B ;B=1MASR *AR2-,*AR3+,B,A ;A=1-x^2/6(1-x^2/20(1-x^2/42(1-x^2/72)))MPYA d_xs ;B=x(1-x^2/6(1-x^2/20(1-x^2/42(1-x^2/72))))STH B,d_sinx ;sin(theta)RETcosx:.def d_xc,d_cosxd_coef_c .usect "coef_c",4.datatable_c .word 0249H ;C1=1/(7*8).word 0444H ;C2=1/(5*6).word 0AABH ;C3=1/(3*4).word 4000H ;C4=1/2d_xc .usect "cos_vars",1d_squr_xc .usect "cos_vars",1d_temp_c .usect "cos_vars",1d_cosx .usect "cos_vars",1c_l_c .usect "cos_vars",1.textSSBX FRCTSTM #d_coef_c,AR5 ;move coeffs table_cRPT #3MVPD #table_c,*AR5+STM #d_coef_c,AR3STM #d_xc,AR2STM #c_l_c,AR4ST #7FFFH,c_l_cSQUR *AR2+,A ;A=x^2ST A,*AR2 ;(AR2)=x^2||LD *AR4,B ;B=1MASR *AR2+,*AR3+,B,A ;A=1-x^2/56,T=x^2MPYA A ;A=T*A=x^2(1-x^2/56)STH A,*AR2 ;(d_temp)=x^2(1-x^2/56)MASR *AR2-,*AR3+,B,A ;A=1-x^2/30(1-x^2/56); T=x^2(1-x^2/56)MPYA *AR2+ ;B=x^2(1-x^2/30(1-x^2/56))ST B,*AR2 ;(d_temp)=x^2(1-x^2/30(1-x^2/56))||LD *AR4,B ;B=1MASR *AR2-,*AR3+,B,A ;A=1-x^2/12(1-x^2/30(1-x^2/56))SFTA A,-1,A ;-1/2NEG AMPYA *AR2+ ;B=-x^2/2(1-x^2/12(1-x^2/30(1-x^2/56)))MAR *AR2+RETDADD *AR4,16,B ;B=-x^2/2(1-x^2/12(1-x^2/30(1-x^2/56)))STH B,*AR2 ;cos(theta)RET.end2. 产生连接程序清单sin.cmdMEMORY{PAGE 0:EPROM: org=0E000H, len=1000HVECS: org=0FF80H, len=0080HPAGE 1:SPRAM: org=0060H, len=0020HDARAM1: org=0080H, len=0010HDARAM2: org=0090H, len=0010HDARAM3: org=0200H, len=0200H}SECTIONS{.text :> EPROM PAGE 0.data :> EPROM PAGE 0STACK :> SPRAM PAGE 1sin_vars :> DARAM1 PAGE 1coef_s :> DARAM1 PAGE 1cos_vars :> DARAM2 PAGE 1coef_c :> DARAM2 PAGE 1sin_x : align(512) {} > DARAM3 PAGE 1.vectors :>VECS PAGE 0}设计仿真结果及分析在ccs集成环境中实现正弦波能够起到防止干扰的作用,同时也大大地减小了波形的线性失真。