基于时钟的24小时计时器的设计

- 格式:docx

- 大小:160.43 KB

- 文档页数:10

24秒计时器设计报告概述本文将介绍一个基于硬件电路的24秒计时器的设计过程。

该计时器可用于篮球比赛等需要精确计时的场合。

我们将逐步讨论设计思路和实施步骤。

设计思路我们的目标是设计一个简单而可靠的24秒计时器。

基于硬件电路的设计通常比软件实现更加稳定和精确。

我们将采用数字集成电路和准确的时钟源来实现计时功能。

步骤一:选择计时器芯片首先,我们需要选择一个合适的计时器芯片。

为了满足精确计时的要求,我们选择了XX型号的计时器芯片。

该芯片具有高精度的时钟源和适配器接口。

步骤二:设计电路原理图在这一步中,我们将根据计时器芯片的规格书设计电路原理图。

根据芯片的引脚定义,我们将确定输入按钮、显示器和报警器的连接方式。

同时,我们需要为芯片提供稳定的电源电压。

步骤三:制作电路板基于电路原理图,我们将制作一个电路板来实现计时器的电路部分。

我们可以使用PCB设计软件来绘制电路板图纸。

然后,我们可以通过特殊的设备将电路图纸转换为实际的电路板。

步骤四:组装计时器外壳当电路板制作完成后,我们将把它安装在一个适当的外壳内。

外壳可以保护电路板免受损坏,并提供按钮和显示器的合适位置。

步骤五:测试和调试在计时器完成组装后,我们将进行测试和调试。

我们将检查所有的功能是否正常工作,包括按钮操作、计时显示和报警器响铃。

如果发现问题,我们将修改电路或芯片的设置。

结论通过以上步骤,我们成功地设计和制作了一个24秒计时器。

这个计时器具有高精度、可靠性和易操作性的优点。

通过硬件电路的实现,我们可以确保计时的准确性,从而满足各种场合的计时需求。

注意:本文中的计时器设计仅为示例,实际设计可能需要根据具体要求进行调整和改进。

设计题目十七:带闹钟功能的24小时制闹钟系统的设计

设计要求:

(1) 计时功能:这是本计时器设计的基本功能,每隔一分钟计时一次,并在显示屏上显示当前时间。

(2) 闹钟功能:如果当前时间与设置的闹钟时间相同,则扬声器发出蜂鸣声。

(3) 设置新的计时器时间:用户用数字键‘0’~‘9’输入新的时间,然后按 "TIME"键确认。

(4) 设置新的闹钟时间:用户用数字键“0”~“9”输入新的时间,然后按“ALARM ”键确认。

过程与(3)类似。

(5) 显示所设置的闹钟时间:在正常计时显示状态下,用户直接按下“ALARM ”键,则已设置的闹钟时间将显示在显示屏上。

参考设计思路:

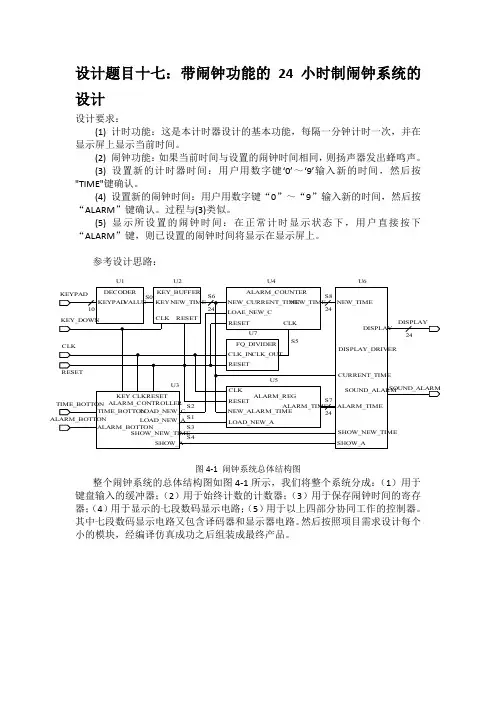

图4-1 闹钟系统总体结构图

整个闹钟系统的总体结构图如图4-1所示,我们将整个系统分成:(1)用于键盘输入的缓冲器;(2)用于始终计数的计数器;(3)用于保存闹钟时间的寄存器;(4)用于显示的七段数码显示电路;(5)用于以上四部分协同工作的控制器。

其中七段数码显示电路又包含译码器和显示器电路。

然后按照项目需求设计每个小的模块,经编译仿真成功之后组装成最终产品。

U4U6U2U1。

课程设计报告课程名称EDA课题名称24小时时钟专业自动化年级09级学号姓名1)课题的主要功能设计一个24小时的时钟,要有时分秒,分别用六位数码管显示,用两个拨码开关分别当做RST,EN用来控制时钟的复位和使能。

2)功能模块的划分图1 时钟功能模块图该智能时钟分为六个模块,分别为:计数器分频模块、三进制加法计数器模块、六进制加法计数器模块、十进制加法计数器模块、数码管动态显示模块、分频器模块。

3)主要功能的实现3.1、计数器分频功能计数器分频COUNTER如图2模块所示,计数器分频到0-22次,最后分出来的OUT[22]时间是0.8秒,近似于1秒。

3.2、三进制加法计数器功能三进制加法计数器模块DSQSAN如图4模块所示,CLK为计数时钟,RST 为1时,数码管上显示00,RST为0时EN为1时计数开始,每3个数,COUT 输出一个1。

3.3、六进制加法计数器功能六进制加法计数器模块DSQLIU如图3模块所示,CLK为计数时钟,RST 为1时,数码管上显示00,RST为0时EN为1时计数开始,每6个数,COUT输出一个1。

3.4、十进制加法计数器功能十进制加法计数器模块DSQSHI如图5模块所示,CLK为计数时钟,RST 为1时,数码管上显示00,RST为0时EN为1时计数开始,每10个数,COUT 输出一个1。

3.5、数码管动态显示功能数码管动态显示模块SMGM如图6模块所示,每一个数码管都有一个对应的CLK10到CLK5,CLK为数码管的扫描周期接COUT[10],SG接数码管的段码,BT接数码管的位码。

3.6、分频功能分频器模块FPQ如图7模块所示,对机器中自带的时钟频率进行分频由50MHZ分到10MHZ。

图2 COUNTER模块图3 DSQLIU模块图4 DSQSAN模块图5 DSQSHI模块图6 SMGM模块图7 FPQ模块4)各模块连接在一起最终图形解释:用COUT[22]当第一个十进制的CLK用这个十进制加法计数器当做秒钟的个位,然后用第一个十进制计数器的COUT当做第一个六进制加法计数器的CLK,用这个六进制加法计数器当做秒钟的十位,以此类推,上一个计数器的COUT接下一个计数器的CLK,用一个十进制加法计数器当做分钟的个位,一个六进制加法计数器当做分钟的十位,一个十进制加法计数器当做小时的个位,一个三进制加法计数器当做小时的十位,所有的计数器的RST和EN接在一起,实现同时复位和使能。

实验一 二十四小时数字计时器、实验内容及题目简介利用QuartusII 软件设计一个数字钟,并下载到SmartSOPC 实验系统中,可以完成00:00:00到23:59:59的计时功能,并在控制电路的作用下具有保持、清零、快速校 时、快速校分、整点报时等功能。

、实验设计要求(1)设计基本要求(2)设计提高部分要求1、使时钟具有整点报时功能(当时钟计到59' 53”时开始报时,在59' 53” , 59 '55” ,59 ' 57”时报时频率为512Hz,59' 59”时报时频率为1KHz,); 2、闹表设定功能; 3、自己添加其他功能;三、方案论证数字钟整体框图如下图所示1、能进行正常的时、分、秒计时功能; 2、3、 分别由六个数码管显示时分秒的计时; K1是系统的使能开关(K 仁0正常工作, K1=1时钟保持不变);4、5、 K2是系统的清零开关(K2=0正常工作, K3是系统的校分开关(K3=0正常工作,K2=1时钟的分、秒全清零); K3=1时可以快速校分); 6、 K4是系统的校时开关(K4=0正常工作, K4=1时可以快速校时);本实验的目的是利用QuartusII软件设计一个多功能的数字计时器,使该计时器具有计时,显示,清零,较分,校时及整点报时功能。

依据上述数字钟电路结构方框图可知,秒计时器和分计时器均为60进制,小时计时器是24进制计数器。

当秒计时器对1HZ时钟脉冲信号计数到60时,产生一个进位脉冲,使分计时器的数值加1,同样,分计时器计数到60时,使小时计时器的数值加一。

秒计数模块和分计数模块的核心是模60的计数器,时计数模块的核心为模24的计数器,并且采用同步计数的方法,即三个模块的时钟信号均来自同一个频率信号。

当数字钟走时出现误差时,通过校时电路对时,分的时间进行校正,其中校时电路和清零电路只需在原有电路的基础上采用一定的逻辑门电路实现。

24秒倒计时器的设计和制作设计和制作一个24秒倒计时器可以分为硬件设计和软件设计两个部分。

硬件设计:1. 选择一个适合的开发板或者单片机作为控制器。

常见的选择有Arduino、Raspberry Pi等。

2.连接一个LCD显示屏,用于显示倒计时的时间。

3.连接一个按钮,用于启动倒计时。

4.使用一个蜂鸣器或者其他声音装置,用于倒计时结束时发出提示音。

软件设计:1. 在选定的控制器上,使用相应的开发环境进行编程。

例如使用Arduino IDE进行Arduino编程。

2.编写倒计时函数,用于倒计时的逻辑。

3.编写LCD显示函数,用于在LCD上显示倒计时的时间。

4.编写按钮检测函数,用于检测按钮的按下事件。

5.编写蜂鸣器控制函数,用于在倒计时结束时发出提示音。

下面是一个简单的伪代码示例,展示了如何实现一个24秒倒计时器:```cpp#include <LiquidCrystal.h> // 引入LCD库LiquidCrystal lcd(12, 11, 5, 4, 3, 2); // 初始化LCD引脚const int buttonPin = 6; // 按钮引脚const int buzzerPin = 7; // 蜂鸣器引脚int buttonState = 0; // 按钮状态int countdownTime = 24; // 倒计时时间void setulcd.begin(16, 2); // 设置LCD行数和列数pinMode(buttonPin, INPUT); // 设置按钮引脚为输入pinMode(buzzerPin, OUTPUT); // 设置蜂鸣器引脚为输出void loobuttonState = digitalRead(buttonPin); // 读取按钮状态if (countdownTime > 0 && buttonState == HIGH) countdownTime--; // 倒计时减1秒displayTime(countdownTime); // 显示倒计时时间delay(1000); // 延迟1秒}if (countdownTime == 0)tone(buzzerPin, 1000, 500); // 发出提示音digitalWrite(buzzerPin, LOW); // 停止提示音delay(1000); // 延迟1秒countdownTime = 24; // 重置倒计时时间}lcd.setCursor(0, 0); // 设置LCD光标位置为第一行第一列lcd.print("Countdown: "); // 显示文本```这个示例使用了Arduino控制器和连接了16x2 LCD显示屏展示倒计时时间。

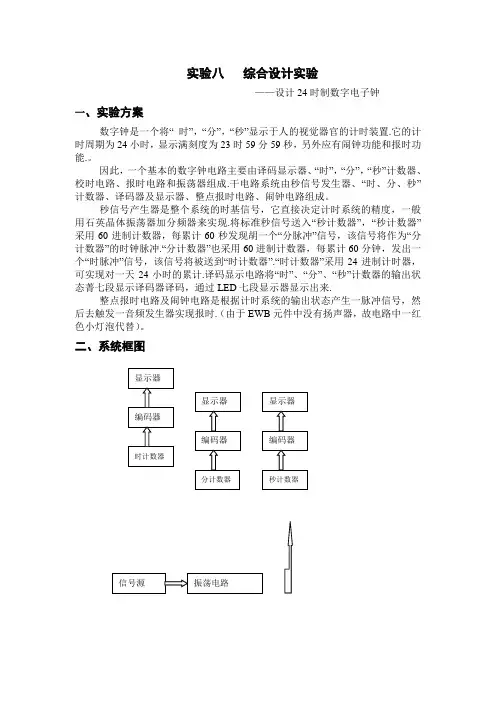

实验八 综合设计实验——设计24时制数字电子钟一、实验方案数字钟是一个将“ 时”,“分”,“秒”显示于人的视觉器官的计时装置.它的计时周期为24小时,显示满刻度为23时59分59秒,另外应有闹钟功能和报时功能.。

因此,一个基本的数字钟电路主要由译码显示器、“时”,“分”,“秒”计数器、校时电路、报时电路和振荡器组成.干电路系统由秒信号发生器、“时、分、秒”计数器、译码器及显示器、整点报时电路、闹钟电路组成。

秒信号产生器是整个系统的时基信号,它直接决定计时系统的精度,一般用石英晶体振荡器加分频器来实现.将标准秒信号送入“秒计数器”,“秒计数器”采用60进制计数器,每累计60秒发现胡一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲.“分计数器”也采用60进制计数器,每累计60分钟,发出一个“时脉冲”信号,该信号将被送到“时计数器”.“时计数器”采用24进制计时器,可实现对一天24小时的累计.译码显示电路将“时”、“分”、“秒”计数器的输出状态菁七段显示译码器译码,通过LED 七段显示器显示出来.整点报时电路及闹钟电路是根据计时系统的输出状态产生一脉冲信号,然后去触发一音频发生器实现报时.(由于EWB 元件中没有扬声器,故电路中一红色小灯泡代替)。

二、系统框图三、数字时钟的原理图:1、信号源及分频器信号源及分频器是数字电子中的核心,其作用是信号源产生一个频率标准,即时间标准信号,然后再由分频器生成秒脉冲。

由于实验室的信号源可提供10Hz 的信号,故要分频成1hz。

74290的引脚图74290的功能表分频电路的仿真图为:2、振荡器(如果要做成一个独立的电子时钟,则要一个能自动产生信号的电路,即振荡电路)振荡器是数字电子中的核心,其作用是产生一个频率标准,即时间标准信号,然后再由分频器生成秒脉冲。

我们有三种选择,即石英晶体振荡器、集成逻辑门与RC组成的时钟源振荡器和由集成电路定时器555和RC组成的多谐振荡器。

《数字与逻辑电路基础》课程设计——24小时计时器的设计姓名:学号:学院:任课教师:目录错误!未定义书签。

引言3摘要374LS390介绍3DCD-HEX数码管介绍4一、设计思路4二、设计框图5三、各个计时芯片的输出状态表51.秒针低位输出状态表错误!未定义书签。

2.秒针高位输出状态表63.分针低位输出状态表64.分针高位输出状态表65.时针低位输出状态表(高位为0、1时)76.时针低位输出状态表(高位为2时)77.时针高位输出状态表7四、反馈置数设计分析8五、进位信号的输入端分析与选择8六、电路图绘制9七、用M ULTISIM仿真并进行截图9八、对仿真结果分析9引言现在的日常生活都离不开时间,有些时候就需要进行时间的计时,比如奥运会的比赛需要计时,汽车动力性能技术指标的测试也需要计时,上到卫星火箭,下到潜艇游轮,甚至做个课堂练习也要计时,生活中无时不刻都在都离不开计时器的应用。

因此,精准计时器的设计与生产变得尤为重要。

所以,本次设计将基于Multisim软件进行计时器的设计与仿真。

摘要24时计时器将采用6个74LS390芯片对各个计时位进行输出,6个七段数码管进行译码以及显示,采用反馈置数的方式进行各个位的计时进行清零(该芯片清零方式为异步清零);根据设计框图分析先列出输出状态表,然后根据输出状态表结果进行电路的绘制;然后根据电路的绘制结果,在Multisim软件上进行电路设计与连接,最后进行计时器仿真截,图并且对仿真结果进行分析。

74LS390介绍74LS390双2-5-10进制的异步计数器且为下降沿触发,从CPA输入计数脉冲,由QA输出产生2分频信号:CPB输入计数脉冲,由QD 输出可产生5分频信号。

若在器件外部将QA于CPB相连,计数脉冲从CPA输入,即成为8421BCD码十进制计数器;若将QD与CPA相连,计数脉冲从CPB输入,便可成为5421BCD码十进制计数器,输出顺序是QAQDQCQB。

二十四小时计时器目录1.项目任务描述 (1)2.24小时计时器流程图 (1)3.24小时计时器源程序 (2)3.1六十进制计数器 (2)3.2二十四进制计数器 (2)4.24小时计时器波形仿真 (3)4.1六十进制计数器波形图 (3)4.2二十四进制计数器波形图 (3)24小时计时器的设计1.项目任务描述:二十四小时计时器是利用特定原理来测定时间的装置,本设计运用Quartus ii 9.0软件以编程的方式实现计时器,计时器由两片六十进制计数器和一片二十四进制计数器构成,输入CLK为1HZ(秒)的时钟,经过60分频后产生1分钟时钟信号,再经过60分频后,产生1小时的时钟信号,最后进行24分频,得到1天的脉冲送COUT输出。

将两个60分频和一个24分频的输出,得到24小时的计时结果,并用数码管显示,所以利用软件分别对二十四进制计数器和六十进制计数器分别编程,编程顺利通过后再通过Quartus ii 9.0软件的波形仿真对二十四进制计数器和六十进制计数器分别仿真,仿真编译通过通过调试得到正确结果,进而验证计数器的正确性,其中60计数器运用ModelSim仿真。

2.24小时计时器流程图:3.24小时计时器源程序:本项目是通过两块六十进制的计数器,和一个二十四进制计数器构成的,所以在这里我们将单独给出二十四进制计数器和六十进制计数器。

运用Quartus ii 9.0软件分别对六十进制计数器和二十四进制计数器编程,调试直到程序编译成功。

3.1六十进制计数器源程序:module cnt60(clk,clrn,j,q,cout);input clk,clrn,j;output reg[7:0]q;output reg cout;always@(posedge clk^j or negedge clrn)beginif(~clrn) q=0;else beginif(q==’h59) q=0;else q=q+1;if(q[3:0]==’h a) beginq[3:0]=0;q[7:4]=q[7:4]+1;endif(q==’h59) cout=1;else cout=0;endendendmodule3.2二十四进制计数器源程序:module cnt24(clk,clrn,j,q,cout);input clk,clrn,j;output reg[7:0]q;output reg cout;always@(posedge clk^j or negedge clrn)beginif(~clrn) q=0;else beginif(q==’h23) q=0;else q=q+1;if(q[3:0]==’ha) beginq[3:0]=0;q[7:4]=q[7:4]+1;endif(q==’h23) cout=1;else cout=0;endendendmodule4.24小时计时器波形仿真运用Quartus ii 9.0软件仿真出二十四进制计数器和六十进制计数器的波形,通过波形的仿真可以看到波形的具体变化,实现六十进制计数器(如图4.1)和二十四进制计数器(如图4.2)的计数功能。

秒表/时钟计时器的设计一.功能要求秒表/始终计数器要求用六位LED数码显示时,分,秒,以24小时计时方式。

使用按键开关可实现时分调整,秒表/时钟功能转换,省电等功能。

二.方案论证为了实现LED显示器的数字显示,可以采用静态显示法和动态显示法。

由于静态显示需要数据锁存器等硬件,接口复杂一些。

考虑时钟显示只有六位,且系统没有其他复杂的处理任务,所以决定采用动态扫描法实现LED 的显示。

单片机采用8052,这样单片机可具有足够的空与硬件资源实现其他的扩展功能,如考虑到要用电池供电的话,则可采用LV系列单片机。

现今的计时器通常只能通过启/停按键实现断点计时的功能,即通过启/停按键来记录一段时间。

这种计时器查看的时间只能为计时结束时刻。

实际的应用中往往需要在不影响正常计时的基础上,能查看记录过程中的某些点的时间。

本课设即针对此问题,设计了一种能通过按键方式查看记录过程中任一时刻值的计时器。

这种计时器在查看中间值时不会影响整个记录过程,并且能把相应数据送入存储模块及显示模块,以便查看。

三.系统硬件电路的设计本系统采用AT89C52单片机作控制器,LED数码管,实现显示时、分、秒,以24小时计时方式。

为了实现LED显示器的数字显示,可以采用静态显示法和动态显示法。

由于静态显示法需要数据锁存器等硬件,结构较为复杂,考虑时钟显示只有六位,且系统没有其他复杂的处理任务,所以采用动态扫描法实现LED的显示。

单片机采用AT89C52系列,有足够的空余硬件资源实现其它的扩充功能。

秒表/时钟计时器的总体设计框图如图1所示。

图1 硬件系统的总体设计框架具体实现电路图1.1 Sheet1.Sch图1.2 S heet2.Sch图1.3 总的连接图系统主要实现如下功能:1.时钟功能对于时钟功能,需要在数码管上显示小时、分钟和秒钟,因此,可以在内部存储空间分别定义它们的显示缓存空间,来存放小时、分钟和秒钟的BCD码,各2个字节。

由于时钟是不能停止的,因此需要采用内部定时器自动计时,并使用定时器中断处理程序来定时进行时间数值的刷新。

摘要时钟是人类日常生活必不可少的工具,本设计从日常生活中常见的事物入手,通过对时钟计时器的设计,让我们认识到单片机已经深入到我们生活的每个领域,该设计不仅可以锻炼我们的动手能力,而且可以加深我们对单片机的认识和激发我们对未知科学领域的探索。

本文利用单片机实现数字时钟计时功能的主要内容,采用独立式按键进行时间调整,其中AT89C52是核心元件同时采用数码管LED动态显示“时”,“分”,“秒”的现代计时装置。

与传统机械表相比,它具有走时精确,显示直观等特点。

它的计时周期为24小时,显满刻度为“23时59分59秒”,另外具有校时功能,断电后有记忆功能,恢复供电时可实现计时同步等特点。

该系统同时具有硬件设计简单、工作稳定性高、价格低廉等优点。

关键字AT89C52 LED显示244AbstractHuman Clock is an essential tool for everyday life, from the design of everyday things in common start, the clock timer through the design, let us recognize that SCM has the depth to each area of our lives, not only the design Can exercise our practical ability, but can also deepen our understanding of the SCM and inspire us to explore the unknown field of science.Using MCU digital clock timing of the main contents of a stand-alone keys to time to adjust, while AT89C52 is the core component of the LED digital display dynamic "," "points" and "seconds" of modern timing devices. Compared with the traditional mechanical watches, it has a precise path that intuitive, and other characteristics. It's time for the 24-hour cycle, in full scale as "23:59:59", and a school function, memory function after power and restore power supply can be realized at the time synchronization, and other characteristics. The system also has hardware design simple, high stability work, the advantages of low prices.Keyword: AT89C52 LED display 244目录第一章前言 (3)第一节选题目的和意义 (3)第二节国内外发展情况 (4)一单片机的发展历程 (4)二单片机的发展趋势 (6)三单片机的组成及特点 (8)四单片机的分类 (9)五单片机的应用 (10)第三节本设计研究的内容和所做的工作 (11)小结 (11)第二章系统硬件的设计 (12)第一节设计方案的提出、论证和确定 (12)一时钟功能 (12)二计时功能 (12)三功能按键 (12)四中断嵌套和控制 (13)五时钟计时器的硬件电路 (14)第二节元件选择 (17)一 AT89C52芯片 (17)二显示部分 (31)三 74LS244芯片说明 (31)小结 (33)第三章控制系统的软件设计 (34)第一节设计部分 (34)一主程序 (34)二显示子程序 (35)三定时器T0中断服务程序 (35)四定时器T1中断服务程序 (36)五调试功能程序 (37)六秒表功能程序 (38)七闹钟时间设定功能程序 (38)第二节控制程序的编制和调试 (38)一硬件调试 (38)二软件调试 (38)三性能分析 (39)小结 (39)第四章参考文献 (39)第五章附录 (40)外文资料 (65)中文译文 (74)致谢语 (80)总结与展望 (81)第一章前言第一节选题目的和意义时钟,自从它发明的那天起,就成为人类的朋友,但随着时间的推移,科学技术的不断发展,人们对时间计量的精度要求越来越高,应用越来越广。

一、设计任务与要求设计一个具有系统时间设置和带闹钟功能的24小时计时器中的应用。

电子钟要求如下:(1)计时功能:4位LED数字时钟对当前时间的小时和分钟进行显示,显示的最长时间为23小时59分。

(2)设置并显示新的闹钟时间:用户先按“set”键,再用数字键“0”~“9”输入时间,然后按“alarm”键确认。

在正常计时显示状态下,用户直接按下“alarm”键,则已设置的闹钟时间显示在显示屏上。

(3)设置新的计时器时间:用户先按“set”键,再用数字键“0”-“9”输入新的时间,然后按“time”键确认。

在输入过程中;输入的数字在显示屏上从右到左依次显示。

例如,用户要设置新的时间12:00,则按顺序输入“l”,“2”,“0”,“0”键,与之对应,显示屏上依次显示的信息为:“1”,“12”;“120”,“1200”。

如果用户在输入任意几个数字后较长时间内,例如5秒,没有按任何键,则计时器恢复到正常的计时显示状态。

(4)闹钟功能:如果当前时间与设置的闹钟时间相同,则扬声器发出蜂鸣声;目录摘要 (I)Abstract (II)1 任务分析 (1)2 FPGA简介 (2)2.1 FPGA简述 (2)2.2 FPGA工作原理 (2)2.3 FPGA的基本结构 (2)3主要模块设计 (5)3.1 分频模块 (5)3.1.1 分频模块源代码 (5)3.1.2 分频模块仿真 (6)3.2 按键模块 (7)3.2.1 按键模块源代码 (7)3.2.2 按键模块仿真 (10)3.3 时间模块 (10)3.3.1 时间模块源代码 (10)3.3.2 时间模块仿真 (13)3.4 显示模块 (14)3.4.1 显示模块源代码 (14)3.4.1 显示模块仿真 (17)3.5 闹钟模块 (18)3.5.1 闹钟模块源代码 (18)3.5.2 闹钟模块仿真 (19)3.6 顶层模块 (19)3.6.1 顶层模块源代码 (19)3.6.2 顶层模块仿真 (21)4 小结与体会 (22)参考文献 (23)FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,是在PAL、GAL、EPLD等可编程器件基础上进一步发展的产物。

沈阳航空航天大学课程设计(说明书)二十四小时制数字钟系统设计班级/ 学号14010101/37学生姓名赵志鸿指导教师徐嵩沈阳航空航天大学课程设计任务书课程名称数字逻辑课程设计课程设计题目二十四小时制数字钟系统设计课程设计的内容及要求:一、设计说明与技术指标设计一个二十四小时制数字钟系统电路,技术指标如下:该数字钟系统要求利用二十四小时制表示时间,利用6位数码管进行具体时间显示;另外要求有三个按键进行时间调节,一个调整时间功能键,按一次此键进入调时功能;连按两次进入调分功能;连按三次进入调秒功能;另外两个按键分别为“+”功能与“-”功能。

二、设计要求1.在选择器件时,应考虑成本。

2.根据技术指标,通过分析计算确定电路和元器件参数。

3.画出电路原理图(元器件标准化,电路图规范化)。

三、实验要求1.根据技术指标制定实验方案;验证所设计的电路,用软件仿真。

2.进行实验数据处理和分析。

四、推荐参考资料1. 童诗白,华成英主编.数字电子技术基础.[M]北京:高等教育出版社,2006年五、按照要求撰写课程设计报告成绩指导教师日期一、概述数字时钟是用数字集成电路做成的现在计时器,与传统的机械钟相比有走时准确,显示直观(六位数码显示器),无机械传动装置等优点。

而且钟表的数字化给人们生产生活带来了极大的方便,大大地扩展了钟表原先的单一报时功能。

诸如自动报警,定时广播,定时启闭电路,定时开关烘箱,通断电力设备,甚至各种定时电器的自动启动等。

所有这些都是以钟表数字化为基础的。

因此,研究数字的应用原理及扩大其应用,有着非常现实的意义。

关于二十四小时制时钟系统的设计,我用的主要是六位数码管显示时间,减小了计时误差,这种表具有时,分,秒显示的功能,还可以进行时分秒的校对,片选的灵活性也很不错。

本设计利用了六片74LS192芯片来实现数字时钟的计时和校时功能,其中74LS160是核心元件,用来作为切换控制档位的十进制计数器,同时采用数码管经过74LS162芯片相关进位和借位动态显示“时”,“分”,“秒”的现代计时装置。

计算机与信息技术学院综合性实验报告1.掌握EDA的设计流程和Verilog HDL;2.掌握计数器是实现方法;3.设计一个24小时的时钟,具有开始、暂停、清零等功能。

二、实验仪器或设备装Quartue II 5.0软件的微机一台三、总体设计(设计原理、设计方案及流程等)(一)设计原理:1.对于一个矩形脉冲信号,如果在其上升沿计数一次,就可以编写代码对其脉冲个数进行计数。

2.要设置一个时钟,要考虑到时钟的时、分、秒之间的进制关系。

3.可以将时、分、秒分别用8位二进制码来表示,高四位为它们的十位,低四位为它们的个位。

4.考虑到要让输出显示为十进制的格式,可以让低四位位从0计到9时,高四位加1。

5.由于时是24进制,可以设置当时间到23时59分59秒时,直接给时、分、秒赋值为0。

6.可以控制时钟的暂停、开始,可在秒进行加1之前先判断控制信号rst是0还是1。

当rst为0时,时钟暂停;当rst为1时,时钟接着开始计时。

7.可以设置一个清零信号clr。

当clr为0时,执行上述的操作;当clr为1时,给时、分、秒赋值为0。

(二)设计方案及流程图1.设计方案(1)判断清零信号clr是否为0。

如果为0,开始计数,如果为1,给时、分、秒赋值为0。

(2)在计时过程中,首先要判断控制信号rst是否1,为1时秒才加1,否则秒保持不变。

2.流程图(见下页)四、实验步骤(包括主要步骤、代码分析等)(一)主要步骤1.打开Quartue II 5.0集成调试软件2.单击“File”-“New”-“Verilog HDL File”,新建一个Verilog HDL 文件,命名为“clock.v”。

3.新建工程,命名为“clock”,进行“编译”。

4.编译无误后,进行波形仿真。

选“File”-“New”-“Other File”-“Vector Waveform File”新建一个波形仿真文件,根据需要添加clk、rst、clr、hour、min、sec的波形,对输入波形设置后,进行仿真。

《数字与逻辑电路基础》课程设计——24小时计时器的设计姓名:学号:学院:任课教师:目录 ....................................................................................... 错误!未定义书签。

引言. (3)摘要 (3)74LS390介绍 (3)DCD-HEX数码管介绍 (4)一、设计思路 (4)二、设计框图 (5)三、各个计时芯片的输出状态表 (5)1.秒针低位输出状态表 ................................................. 错误!未定义书签。

2.秒针高位输出状态表 (6)3.分针低位输出状态表 (6)4.分针高位输出状态表 (6)5.时针低位输出状态表(高位为0、1时) (7)6.时针低位输出状态表(高位为2时) (7)7.时针高位输出状态表 (7)四、反馈置数设计分析 (8)五、进位信号的输入端分析与选择 (8)六、电路图绘制 (9)七、用M ULTISIM仿真并进行截图 (9)八、对仿真结果分析 (9)引言现在的日常生活都离不开时间,有些时候就需要进行时间的计时,比如奥运会的比赛需要计时,汽车动力性能技术指标的测试也需要计时,上到卫星火箭,下到潜艇游轮,甚至做个课堂练习也要计时,生活中无时不刻都在都离不开计时器的应用。

因此,精准计时器的设计与生产变得尤为重要。

所以,本次设计将基于Multisim软件进行计时器的设计与仿真。

摘要24时计时器将采用6个74LS390芯片对各个计时位进行输出,6个七段数码管进行译码以及显示,采用反馈置数的方式进行各个位的计时进行清零(该芯片清零方式为异步清零);根据设计框图分析先列出输出状态表,然后根据输出状态表结果进行电路的绘制;然后根据电路的绘制结果,在Multisim软件上进行电路设计与连接,最后进行计时器仿真截,图并且对仿真结果进行分析。

24小时计时器设计摘要:使用硬件描述语言VHDL进行编程,设计六十进制和二十四进制计数器,利用原理图输入设计方法,使用两片六十进制计数器和一片二十四进制计数器,设计出了一个24小时计时器系统。

使用QuartusII软件进行编译,时序仿真,来验证该系统的正确性。

整个系统设计简单,使用方便,具有24小时计时显示功能,可以分别对时,分,秒进行校正。

关键词:VHDL 计数器24小时计时器目录1.设计背景 (1)2.设计方案 (1)2.1.六十进制计数器设计 (2)2.2.二十四进制计数器设计 (3)3.方案实施 (5)4.仿真结果 (6)5.参考文献 (7)1.设计背景随着EDA技术的发展和应用领域的扩大,EDA技术在电子信息、通信、自动控制及计算机应用等领域的重要性日益突出。

基于EDA技术的数字系统设计,一般可以再单片PLD实现,具有功能强、功耗低,体积小、可靠性高等特点,成为当今数字系统设计的主流。

此次EDA课程大作业,我的设计课题是24小时计时器系统设计,根据要求使用平时所学VHDL语言进行编程和原理图输入设计方法来完成。

报告书主要包括设计背景、设计方案、方案实施、仿真波形。

设计方案主要介绍了我对于设计课题的大致设计思路,之后各个部分将会详细介绍设计组成及程序。

2.设计方案24小时计时器的原理图如图2.1所示。

它由两片六十进制计时器和一片二十四进制计数器构成,输入CLK为1Hz的时钟,经过60分频后产生1分钟时钟信号,再经过60分频后,产生1小时的时钟信号,最后进行24分频,得到1天的脉冲送COUT输出。

将两个60分频和一个24分频的输出送7段数码管,得到24小时的计时显示结果。

图2.1 24小时计时器的原理图图2.1中的CLK是1Hz时钟输入端;RST是复位输入端,高电平有效;JM、JF和JS分别是校秒、校分和校时的输入端,下将沿有效;QM[7..0]、QF[7..0]和QS[7..0]分别是秒、分、时的计时输出端;COUT是“天”脉冲输出端。

《数字与逻辑电路基础》课程设计——24小时计时器的设计

姓名:

学号:

学院:

任课教师:

目录 ....................................................................................... 错误!未定义书签。

引言. (3)

摘要 (3)

74LS390介绍 (3)

DCD-HEX数码管介绍 (4)

一、设计思路 (4)

二、设计框图 (5)

三、各个计时芯片的输出状态表 (5)

1.秒针低位输出状态表 ................................................. 错误!未定义书签。

2.秒针高位输出状态表 (6)

3.分针低位输出状态表 (6)

4.分针高位输出状态表 (6)

5.时针低位输出状态表(高位为0、1时) (7)

6.时针低位输出状态表(高位为2时) (7)

7.时针高位输出状态表 (7)

四、反馈置数设计分析 (8)

五、进位信号的输入端分析与选择 (8)

六、电路图绘制 (9)

七、用M ULTISIM仿真并进行截图 (9)

八、对仿真结果分析 (9)

引言

现在的日常生活都离不开时间,有些时候就需要进行时间的计时,比如奥运会的比赛需要计时,汽车动力性能技术指标的测试也需要计时,上到卫星火箭,下到潜艇游轮,甚至做个课堂练习也要计时,生活中无时不刻都在都离不开计时器的应用。

因此,精准计时器的设计与生产变得尤为重要。

所以,本次设计将基于Multisim软件进行计时器的设计与仿真。

摘要

24时计时器将采用6个74LS390芯片对各个计时位进行输出,6个七段数码管进行译码以及显示,采用反馈置数的方式进行各个位的计时进行清零(该芯片清零方式为异步清零);根据设计框图分析先列出输出状态表,然后根据输出状态表结果进行电路的绘制;然后根据电路的绘制结果,在Multisim软件上进行电路设计与连接,最后进行计时器仿真截,图并且对仿真结果进行分析。

74LS390介绍

74LS390双2-5-10进制的异步计数器且为下降沿触发,从CPA输入计数脉冲,由QA输出产生2分频信号:CPB输入计数脉冲,由QD 输出可产生5分频信号。

若在器件外部将QA于CPB相连,计数脉冲从CPA输入,即成为8421BCD码十进制计数器;若将QD与CPA相连,计数脉冲从CPB输入,便可成为5421BCD码十进制计数器,输出顺

序是QAQDQCQB。

并且置数方式为异步置数高电平有效。

DCD-HEX数码管介绍

DCD-HEX数码管将译码与显示功能合一,从左到右四个引脚为8421BCD码的高位到低位,用来显示0到9。

一.设计思路

1.由秒时钟信号发生器、计时电路和反馈置数电路构成电路。

2.秒针计数可由发生器提供1Hz方波。

3.计时电路中采用两个60进制计数器分别完成秒计时和分计时;24进制计数器完成时计时;且各个74LS390之间进行级连得方式然后采用DCD-HEX数码管显示。

4.按照秒分时顺序依次提供计数脉冲,即满60秒后的分进位信号与满60分后的时进位信号进行电路的连接。

5.按照电路图用Multisim进行仿真设计,并且进行计时器的仿真并且截图。

二.设计框图

计时数字钟电路框图

三.列出各个计时芯片的输出状态表1.秒针低位输出状态表

2.秒针高位输出状态表

3.分针低位输出状态表

4.分针高位输出状态表

5.时针低位输出(高位为0或1时)状态表

6.时针低位输出(高位为2时)状态表

7.时针高位输出状态表

四.反馈置数设计分析(模60与模24的设计)

1. 秒针的高位输出为0~5,则选择的置数信号为2QB·2QC=1,即将2QB与2QC输出端相与作为2CLR的输入端。

2. 分针的高位输出为0~5,则选择的置数信号为4QB·4QC=1,即将4QB与4QC输出端相与作为4CLR的输入端。

3. 时针的低位输出0~9时,进行自置数;时针的低位输出为0~3时,则选择的置数信号为6QB·5QC=1(此时已经达到23时),即将6QB 与5QC输出端相与作为5CLR的输入端。

4.时针的高位输出为0~2,则选择的置数信号为6QB·5QC=1,即输出为24时的暂态作为6CLR的置数输入端。

五.进位信号的输入端分析与选择(满60秒后的分进位信号与满60分后的时进位信号)注:触发器触发方式为下降沿触发1.秒针高位的输入脉冲为1QD,当低位计满10秒后产生一个下降沿作为秒针高位脉冲输入。

2.分针低位的输入脉冲为2QC,当秒针位计满60秒后产生一个下降沿作为分针低位脉冲输入。

3.分针高位的输入脉冲为3QD,当低位计满10分后产生一个下降沿作为分针高位脉冲输入。

4.时针低位的输入脉冲为4QC,当低位计满60分后产生一个下降沿作为时针低位脉冲输入。

5.时针高位的输入脉冲为5QC,当低位计满10小时后产生一个下降沿作为时针高位脉冲输入。

六.电路图绘制如下

七.用Multisim仿真并进行截图

注:为了更好的了解该仿真结果显示,秒针输入频率进行了加倍;实际应用中应该输入1Hz。

八.对仿真结果分析

秒针高低位与分针高低位如预期按照00~59进行计时,时针按照00~23进行计时;且计满60秒后向分针进一,当计满60分后,向时针进一,当计满24小时后所有计时器归零,完成24小时计时。