ispLEVER使用指导

- 格式:doc

- 大小:4.98 MB

- 文档页数:62

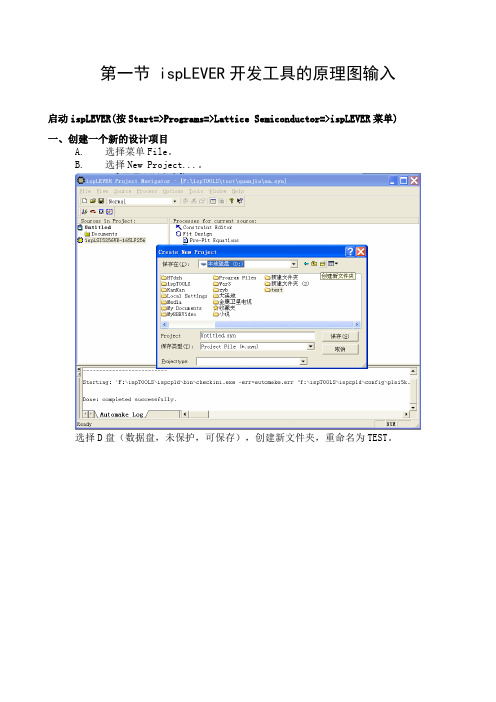

第一节 ispLEVER开发工具的原理图输入启动ispLEVER(按Start=>Programs=>Lattice Semiconductor=>ispLEVER菜单)一、创建一个新的设计项目A.选择菜单File。

B.选择New Project...。

选择D盘(数据盘,未保护,可保存),创建新文件夹,重命名为TEST。

进入文件夹,PROJECT命名为ADD1.SYN,保存类型为SYN,PROJECTTYPE选择第一项SCHEMATIC/ABEL,保存即可。

C.你可以看到默认的项目名和器件型号: Untitled andispLSI5256VE-165LF256。

二、项目命名D.用鼠标双击Untitled。

E.在Title文本框中输入“test”,并选OK(此操作可选)。

三、选择器件a)双击ispLSI5256VE-165LF256, 你会看到Device Selector对话框(如下图所示)。

b)方法一:在Select Device窗口中选择:Family中选择 ispLSI 1K Device;Device 中选择ispLSI1032E;Speed grade中选择70; Package中选择 84PLCC;Operating 中选择Industrial。

方法二:按动器件目录中(Part)的滚动条,直到找到并选中器件1032E-70LJ84I。

c)揿OK按钮,选择这个器件。

d)在软件弹出的如下图显示的ispLEVER Project Navigator窗口中,按否(N)按钮。

e)在软件弹出的如下图显示的Confirm Change窗口中,按Yes按钮。

f)因改选器件型号后,先前的约束条件可能对新器件无效,因此在软件接着弹出的如下图显示的ispLEVER Project Navigator窗口中,按Yes按钮,以用来去除原有的约束条件。

四、在设计中增加源文件一个设计项目由一个或多个源文件组成。

ispLEVER使用指南 (Lattice FPGA部分)1.介绍1.1 简介该使用指南适用于初次使用ispLEVER软件或者不常使用该软件的工程设计人员,它可以帮助你去了解不同的处理过程,使用各种工具,以及熟悉ispLEVER产生的各种报告。

在进行下一步时,可以准备一个设计,以此去了解设计的仿真,功耗的计算,静态时序分析,以及以时序驱动的布局和布线,检查由软件输出的报告等。

以此设计为例,你可以练习约束设计的输入,输出信号以及这些信号管脚的分配去满足系统要求。

也可以修改约束条件,达到最佳地利用LatticeEC的结构和资源,同时实现高性能。

该使用指南覆盖了绝大部分通常的流程和软件选项,那些更大的,时序要求更严的设计则需要更精细的控制才能满足你对性能和资源利用率要求的目标,在此之前,你必须对这些基本知识有所了解和掌握。

1.2 目标当你读完该使用指南时,你有能力完成以下的任务:1.使用ispLEVER软件创建一个新的Verilog语言的工程目录,选定你的目标器件,并利用Project Navigator在该工程目录中添加Verilog HDL源代码。

2.生成一个sysCLOCK 锁相环(PLL)模块,并把它添加到该工程项目,利用IPexpress和文本编译器(Text Editor)将该PLL模块添加到源代码中。

3.在器件的管脚上锁定相应的信号,用Design Planner定义信号的频率周期和时钟到输出(Clock-to-out)的时间。

4.利用映射(Mapping),布局(Placing),布线(Routing)等工具来完成设计。

同时,利用Project Navigator检查结果报告。

5.了解静态时序分析报告,调整设计去满足设计的时序要求。

6.修改和重新设置约束条件去满足设计的性能要求。

7.使用Design Planner来检查器件的实现情况,以及相应的布线阻塞情况,可编程单元(PFU)的利用率。

IspLEVER Classic软件安装说明安装点击“ispLEVER Classic Installer.exe”进行软件安装。

默认安装路径是“C:\ ispLEVER_Classic1_3”可更改为自己的安装路径。

安装过程中都是默认进行下去,一般不需要修改什么。

选择“Install ispLEVER Classic Design T ools”进行软件安装IspLEVER Classic安装成后会提示安装USB驱动。

可以取消以后再安装驱动。

驱动是在:“安装路径\ispvmsystem\FTDIUSBDriver”文件夹下。

没有的话,可以从安装的IspLEVER8.1软件路径下来寻找安装驱动。

软件环境变量位置(可以不改动)IspLEVER Classic的环境变量在软件安装时,就默认建立了。

默认指向license文件夹。

环境变量名:“LM_LICENSE_FILE”。

路径(指变量值)默认是:“\安装路径\ license\license.dat”。

一般不需要改动环境变量,只需要将所给软件里带的“license.dat”拷贝到“\安装路径\license\”文件夹下。

如果安装了IspLEVER8.1,并设置过环境变量,再安装IspLEVER Classic就不需要再设置环境变量了,证书文件直接使用的是IspLEVER8.1路径下指定的“license.dat”即可。

我的电脑→属性→高级→环境变量系统变量→LM_LICENSE_FILE\安装路径\license\license.dat建立虚拟网卡使用Lattice软件前,首先需要建立一个虚拟网卡,并使用网卡MAC地址修改软件将虚拟网卡的MAC(Physical Addr ess)值改为“license.dat”中HOSTID对应的值。

(虚拟网卡软件和网卡修改软件网上可以搜索到很多的。

)虚拟网卡MAC设置好了之后,将电脑重新启动,使设置好的MAC生效。

ispLEVER教程•教程简介与背景•ispLEVER 基础操作•原理图设计与编辑技巧•PCB 布局布线实战演练•仿真测试与验证方法论述•团队协作与版本控制策略分享目录CONTENTS01教程简介与背景ispLEVER概述ispLEVER 是Lattice半导体公司提供的一款集成开发环境(IDE),用于设计、模拟和编程Lattice FPGA和CPLD器件。

它提供了一套完整的工具链,包括设计输入、综合、布局布线、时序分析、仿真和下载等,方便用户进行FPGA/CPLD设计。

ispLEVER支持多种设计输入方式,如原理图、硬件描述语言(HDL)和混合输入等,并提供了丰富的IP核和库函数,以加速设计过程。

教程目标与内容本教程的目标是帮助读者掌握ispLEVER的基本操作和设计流程,能够独立完成简单的FPGA/CPLD设计。

教程内容包括ispLEVER的安装与配置、设计输入、综合与布局布线、时序分析、仿真和下载等关键步骤的详细讲解。

通过本教程的学习,读者将了解FPGA/CPLD设计的基本原理和方法,并具备一定的实践能力和问题解决能力。

1 2 3在学习本教程之前,读者应具备数字电路和计算机组成原理的基本知识,了解FPGA/CPLD的基本概念和原理。

读者需要掌握一种硬件描述语言(如VHDL或Verilog),以便进行FPGA/CPLD设计。

对于初学者,建议具备一定的编程基础,如C/C 或Python等,以便更好地理解和应用ispLEVER 中的相关概念和工具。

预备知识与技能要求本教程采用理论与实践相结合的方法,通过详细的步骤讲解和实例演示,帮助读者逐步掌握ispLEVER的使用方法。

对于遇到的问题和困难,可以通过查阅ispLEVER的官方文档或在线论坛寻求帮助和解决方案。

学习方法与建议在学习过程中,建议读者结合实例进行操作练习,加深对相关概念和工具的理解和掌握。

此外,鼓励读者在学习过程中积极思考和探索,尝试将所学知识应用于实际项目中,以提高学习效果和实践能力。

一、新建工程并加载程序文件1.1启动ispLEVER,选择File—New Project,在弹出的Project Wizard对话框中填写或选择Project Name、Location、Design Entry Type、Synthesis Tools、Simulator Tools,点击“下一步”。

我们给出一个例子,osc_led,见图1.1。

图1.11.2在Project Wizard—Select Device窗口中选择与所使用的演示板上搭载的器件名称相匹配的Family、Device、Speed grade、Package type、Operating、Part Name,点击“完成”。

见图1.2。

图1.21.3在ispLEVER软件的Source in Project窗口中,会出现新建的工程名称和选择的器件名称,见图1.3,工程名称:osc_led,选择的器件名称:LC4128V-10T1001。

图1.31.4加载程序文件有两种方法可以加载程序文件,一种是直接调用现有的程序文件,另一种是直接编写程序文件。

1.4.1调用现有的程序文件。

1.4.1.1在1.3中选择的器件名称LC4128V-10T1001上右击鼠标,选择Import,在弹出的对话框中选择现有的程序文件,点击打开。

见图1.4.1.1。

图1.4.1.11.4.1.2在弹出的Import Source Type对话框中选择Type of Source,源文件选择Verilog Module,点击OK。

见图1.4.1.2。

图1.4.1.21.4.1.3加载测试文件,方法同上面源文件的加载,区别是在选择source type时要选择“Verilog Test Fixture”,在弹出的“Associate Verilog Test Fixture”对话框中要选择器件名,如图1.4.1.3A、B、C所示:ABC图14.1.31.4.2直接编写程序文件。

目录第一节ispLEVER 简介第二节ispLEVER 开发工具的FPGA设计输入方法第三节ModelSim 的使用方法第四节设计的实现第一节 ispLEVER简介ispLEVER 是完整的CPLD和FPGA设计软件,能帮助用户完成从概念到完成产品的设计。

ispLEVER包含许多有力的开发的工具,用于设计输入、项目管理、IP集成、器件映射、布局和布线,以及在系统逻辑分析等。

ispLEVER (Windows) 还包含业界领头羊——我们的伙伴Synplicity 和Mentor Graphics ——的第三方工具,这些工具用于综合和仿真。

ispLEVER 6.0完全支持最新的高性能、低成本的90纳米LatticeECP2™和LatticeSC™ 终极性能的系统芯片FPGA系列,并且具有引以为豪的空前性能和经过重大改进的设计流程。

ispLEVER 6.0版的主要亮点包括:支持业界最快的90纳米FPGA;推出新的、高度集成的Design Planner接口、针对原理图FPGA设计支持的改进以及一个IPexpress™ 用户可配置的IP核拓展库。

ispLEVER设计流程如下:软件主要特征:1. 输入方式* 原理图输入* ABEL-HDL输入* VHDL输入* Verilog-HDL输入* EDIF输入* 原理图和硬件描述语言混合输入2.逻辑模拟* 功能模拟* 时序模拟3.编译器* 结构综合、映射、自动布局和布线4.支持的器件* 含有支持ispLSI器件的宏库及MACH器件的宏库、TTL库* 支持所有LatticeEC、LatticeECP、LatticeSC、LatticeXP、ispLSI、ispMACH、ispGDX、GAL、MachXO、ORCA FPGA/FPSC、ispXPGA和ispXPLD 器件5. 工具* Design Planner、EPIC Device Editor、IPexpress、ispTRACY Core Linker、ispVM、ispTRACY Logic Analyzer、Power Calculator、Block Modular Design Wizard、Memory Initialization Tool、Synplify Synthesis、Precisin Synthesis、ModelSim Simulator和TCL等。

ispLEVER培训教程上海莱迪思半导体公司市场部2002 年 12 月英文网址:中文网址:或目录第一节 ispLEVER 简介第二节 ispLEVER开发工具的原理图输入第三节设计的编译与仿真第四节硬件描述语言和原理图混合输入第五节ispLEVER工具中VHDL和Verilog语言的设计方法第六节 ispVM System-在系统编程的软件平台第七节约束条件编辑器(Constraint Editor)的使用方法附录一ispLEVER System上机实习题附录二ispLEVER软件中文件名后缀及其含义第一节ispLEVER 简介ispLEVER 是Lattice 公司最新推出的一套EDA软件。

设计输入可采用原理图、硬件描述语言、混合输入三种方式。

能对所设计的数字电子系统进行功能仿真和时序仿真。

编译器是此软件的核心,能进行逻辑优化,将逻辑映射到器件中去,自动完成布局与布线并生成编程所需要的熔丝图文件。

软件中的Constraints Editor工具允许经由一个图形用户接口选择I/O设置和引脚分配。

软件包含Synolicity公司的“Synplify”综合工具和Lattice的ispVM器件编程工具。

ispLEVER软件提供给开发者一个简单而有力的工具,用于设计所有莱迪思可编程逻辑产品。

软件支持所有Lattice公司的ispLSI 、MACH、ispGDX、ispGAL、GAL器件。

ispLEVER工具套件还支持莱迪思新的ispXPGA TM和ispXPLD TM产品系列,并集成了莱迪思ORCA Foundry设计工具的特点和功能。

这使得ispLEVER的用户能够设计新的ispXPGA和ispXPLD产品系列,ORCA FPGA/FPSC系列和所有莱迪思的业界领先的CPLD产品而不必学习新的设计工具。

软件主要特征:1. 输入方式* 原理图输入* ABEL-HDL输入* VHDL输入* Verilog-HDL输入* 原理图和硬件描述语言混合输入2.逻辑模拟* 功能模拟* 时序模拟3.编译器* 结构综合、映射、自动布局和布线4.支持的器件* 含有支持ispLSI器件的宏库及MACH器件的宏库、TTL库* 支持所有ispLSI、MACH、ispGDX、ispGAL、GAL、ORCA FPGA/FPSC、ispXPGA和ispXPLD 器件5. Constraints Editor工具* I/O参数设置和引脚分配6. ispVM工具* 对ISP器件进行编程软件支持的计算机平台:PC: Windows 98/NT/2000/XP第二节 ispLEVER开发工具的原理图输入I.启动ispLEVER(按Start=>Programs=>Lattice Semiconductor=>ispLEVER菜单)II.创建一个新的设计项目A.选择菜单File。

B.选择New Project...。

C.在Create New Project对话框的Project Name栏中,键入项目名d:\user\demo.syn。

在Project type栏中选择Schematic/ABEL(ispLEVER软件支持Schematic/ABEL、Schematic/VHDL、Schematic/Verilog等的混合设计输入,在此例中,仅有原理图输入,因此可选这三种中的任意一种)。

D.你可以看到默认的项目名和器件型号: Untitled and ispLSI5256VE-165LF256。

III.项目命名A.用鼠标双击Untitled。

B.在Title文本框中输入“Demo Project”,并选OK。

IV.选择器件A.双击ispLSI5256VE-165LF256, 你会看到Device Selector对话框(如下图所示)。

B.在Select Device窗口中选择ispMACH 4000项。

C.按动器件目录中的滚动条,直到找到并选中器件LC4032V-10T44I。

D.按OK按钮,选择这个器件。

E.在软件弹出的如下图显示的Confirm Change窗口中,按Yes按钮。

F.因改选器件型号后,先前的约束条件可能对新器件无效,因此在软件接着弹出的如下图显示的ispLEVER Project Navigato窗口中,按Yes按钮,以用来去除原有的约束条件。

V.在设计中增加源文件一个设计项目由一个或多个源文件组成。

这些源文件可以是原理图文件(*.sch)、ABEL HDL文件(*.abl)、VHDL设计文件(*.vhd)、Verilog HDL设计文件(*.v)、测试向量文件(*.abv)或者是文字文件(*.doc, *.wri, *.txt)。

在以下操作步骤中,你要在设计项目中添加一张空白的原理图纸。

A.从菜单上选择Source 项。

B.选择New... 。

C.在对话框中,选择Schematic(原理图),并按OK。

D.输入文件名demo.sch。

E.确认后按OK。

VI.原理图输入你现在应该进入原理图编辑器。

在下面的步骤中,你将要在原理图中画上几个元件符号,并用引线将它们相互连接起来。

A.从菜单栏选择Add, 然后选择Symbol,你会看到如下图所示的对话框:B.选择GATES.LIB库,然后选择G_2AND元件符号。

C.将鼠标移回到原理图纸上,注意此刻AND门粘连在你的光标上,并随之移动。

D.单击鼠标左键,将符号放置在合适的位置。

E.再在第一个AND门下面放置另外一个AND 门。

F.将鼠标移回到元件库的对话框,并选择G_2OR元件。

G.将OR门放置在两个AND门的右边。

H.现在选择Add菜单中的Wire项。

I.单击上面一个AND门的输出引脚,并开始画引线。

J.随后每次单击鼠标,便可弯折引线 (双击便终止连线)。

K.将引线连到OR门的一个输入脚。

L.重复上述步骤,连接下面一个AND门。

VII.添加更多的元件符号和连线A.采用上述步骤,从REGS.LIB库中选一个g_d寄存器,并从IOPADS.LIB库中选择G_OUTPUT符号。

B.将它们互相连接,实现如下的原理图:VIII.完成你的设计在这一节,通过为连线命名和标注I/O Markers来完成原理图。

当要为连线加信号名称时,你可以使用ispLEVER的特点,同时完成两件事-----同时添加连线和连线的信号名称。

这是一个很有用的特点,可以节省设计时间。

I/O Markers是特殊的元件符号,它指明了进入或离开这张原理图的信号名称。

注意连线不能被悬空(dangling),它们必需连接到I/O Marker或逻辑符号上。

这些标记采用与之相连的连线的名字,与I/O Pad符号不同,将在下面定义属性(Add Attributes)的步骤中详细解释。

A.为了完成这个设计,选择Add菜单中的Net Name项。

B.屏幕底下的状态栏将要提示你输入的连线名,输入‘A’并按Enter键,连线名会粘连在鼠标的光标上。

C.将光标移到最上面的与门输入端,并在引线的末连接端(也即输入脚左端的红色方块),按鼠标左键,并向左边拖动鼠标。

这可以在放置连线名称的同时,画出一根输入连线。

D.输入信号名称现在应该是加注到引线的末端。

E.重复这一步骤,直至加上全部的输入‘B’,’C’,’D’和‘CK’,以及输出‘OUT’。

F.现在选择Add菜单的I/O Marker项。

G.将会出现一个对话框,请选择Input。

H.将鼠标的光标移至输入连线的末端(位于连线和连线名之间),并单击鼠标的左键。

这时回出现一个输入I/O Marker,标记里面是连线名。

I.鼠标移至下一个输入,重复上述步骤,直至所有的输入都有I/OMarker。

J.现在请在对话框中选择Output,然后单击输出连线端,加上一个输出I/O Marker。

K.至此原理图就基本完成,它应该如下图所示。

IX.定义器件的属性(Attributes)你可以为任何一个元件符号或连线定义属性。

在这个例子中,你可以为输出端口符号添加引脚锁定LOCK的属性。

请注意,在ispLEVER中,引脚的属性实际上是加到I/O Pad符号上,而不是加到I/O Marker上。

同时也请注意,只有当你需要为一个引脚增加属性时,才需要I/O Pad符号,否则,你只需要一个I/O Marker。

A.在菜单条上选择Edit =>Attribute =>Symbol Attribute项,这时会出现一个SymbolAttribute Editor 对话框。

B.单击需要定义属性的输出I/O Pad。

C.对话框里会出现一系列可供选择的属性。

D.选择PinNumber属性,并且把文本框中的‘*’替换成‘4’(‘4’为器件的引脚号)。

这样,该I/O Pad上的信号就被锁定到器件的第四个引脚上了。

E.关闭对话框。

F.请注意,此时数字‘4’出现在I/O Pad符号内。

X.保存已完成的设计从菜单条上选择File,并选Save命令。

再选Exit命令。

第三节设计的编译与仿真I.建立仿真测试向量(Simulation Test Vectors)A.在已选择LC4032V-10T44I器件的情况下,选择Source菜单中的New...命令。

B.在对话框中,选择ABEL Test Vectors并按OK。

C.输入文件名demo.abv作为你的测试向量文件名。

D.按OK。

E.文本编辑器弹出后,输入下列测试向量文本:F.完成后,选择File菜单中的Save命令,以保留你的测试向量文件。

G.再次选择File,并选Exit命令。

H.此时你的项目管理器(Project Navigator)应如下图所示。

II.编译原理图与测试向量现在你已为你的设计项目建立起所需的源文件,下一步是执行每一个源文件所对应的处理过程。

选择不同的源文件,你可以从项目管理器窗口中观察到该源文件所对应的可执行过程。

在这一步,请你分别编译原理图和测试向量。

A.在项目管理器左边的项目源文件(Sources in Project)清单中选择原理图(demo.sch)。

B.双击原理图编译(Compile Schematic)处理过程。

C.编译通过后,Compile Schematic过程的左边会出现一个绿色的查对记号,以表明编译成功。

编译结果将以逻辑方程的形式表现出来。

D.然后从源文件清单中选择测试向量源文件(demo.abv)。

E.双击测试向量编译(Compile Test Vectors)处理过程。

III.设计的仿真ispLEVER开发系统不但可以进行功能仿真(Functional Simulation),而且可以进行时序仿真(Timing Simulation)。

在仿真过程中还提供了单步运行、断点设置功能。