第4章TTL电路半导体集成电路共14章 53页

- 格式:ppt

- 大小:1.28 MB

- 文档页数:53

《半导体集成电路》课程教学教案课程总体介绍:教材:选用清华大学出版社出版的朱正涌编写的高等学校电子信息类规划教材《半导体集成电路》一书。

根据同学的基础情况参考了上海科技出版社张延庆,张开华编写《半导体集成电路》。

1.该教材参考教学学时为120学时。

2.本教案按教学学时数:64学时编制。

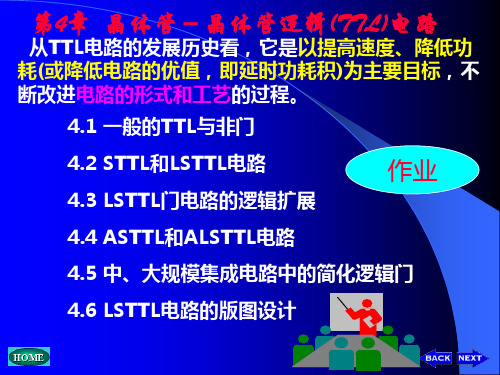

3.教学内容学时分配:第一篇半导体集成电路制造工艺与寄生效应11学时第0章绪论2学时第一章半导体集成电路基本制造工艺5学时第二章集成电路的寄生效应4学时第二篇双极型逻辑集成电路21学时第三章TTL集成电路11学时第四章TTL中大规模集成电路设计与版图设计8学时第五章ECL电路与IIL电路2学时第三篇MOS 逻辑集成电路24学时第六章MOS反相器与传输们10学时第七章MOS基本逻辑门与版图设计8学时第八章MOS存储器6学时第四篇模拟集成电路8学时第九章模拟集成电路中的元器件与基本单元8学时教案结构:课程内容;课程重点;课程难点;基本概念;基本要求。

基本概念视同学的基础可以适当删减。

:课程教案:第一篇半导体集成电路制造工艺与寄生效应11学时第0章绪论2学时第一章半导体集成电路基本制造工艺5学时第二章集成电路的寄生效应4学时绪论2学时课程内容: 认识集成电路;集成电路的定义:集成电路的应用特点;集成电路分类。

1 半导体集成电路的发展史2 集成电路发展的特点3 半导体集成电路的分类4 课程内容介绍及要求课程重点:介绍了何谓集成电路,集成电路发展过程,集成电路是如何分类的(即可分为膜集成电路.半导体集成电路和混合集成电路。

半导体集成电路)是以制造工艺分类的,以集成电路的发展史集成电路有何特点;介绍了何谓半导体集成电路,半导体集成电路的分类(即按照电路中晶体管的导电载流子状况分类,可分为双极型集成电路和单极型集成电路两种;按照电路工作性质分类,可分为数字集成电路和模拟集成电路两种),半导体集成电路的重要概念-集成度,以及半导体集成电路的优点(即体积小重量轻;技术指标先进可靠性高以及便于大批量生产和成本低等)。

详解TTL门电路一、什么是TTL门电路TTL 是一种集成电路,通过使用双极性晶体管组合来做到具有驱动能力的逻辑输出。

TTL 最重要的特性是门的输入在未连接时将为逻辑高电平。

在硬件电路中,会用到逻辑门这样的数字器件,对于这样的数字器件,从内部工艺结构来份的话主要有两个大的分支:一个是晶体管构成的,另一个是场效应管构成的。

而晶体管构成的门电路,被称为TTL门电路。

二、TTL电路工作原理TTL门电路也分很多种,比如说非门、与非门、或非门、与或非门以及OC输出的与非门。

虽然种类多,但是基本的工作原理都是类似的。

以常用的与非门电路为例对其工作原理进行介绍。

图 1 非门的TTL电路从图1中可以看出非门电路是由Q1输入级、Q2中间级以及Q3、Q4输出级组成。

1、输入级:Q1从结构上把它看成由二极管构成的,两个二极管的P结背靠背,N结分别连接输入和Q2的基极。

2、中间级:由三极管Q2和电阻R2、R4组成。

在电路的开通过程中利用Q2的放大作用,为输出管Q3和Q4提供较大的基极电流,加速了输出管的导通。

所以,中间级的作用是提高输出管的开通速度,改善电路的性能。

3、输出级:由三极管Q3、Q4、二极管D1和电阻R3组成。

从图中可以看出,输出级由三极管Q4实现逻辑非的运算。

但在输出级电路中用三极管Q3、二极管D1和R3组成的有源负载来使输出级具有较强的负载能力。

其中D1可以起到三极管be反向击穿的保护作用。

工作原理:1、当输入端Input为逻辑低电平时,电流流经R1至Input,Q1晶体管导通,此时Vb(Q2)的电压小于Vbe导通电压0.7V,Q2晶体管截止。

此时由于R2与R4的存在,使Q3导通、Q4截止,在Out上输出高电平。

由图1中输出结构可知,此时输出高电平电压将为:Vout=Vcc−Vce−V D1≈Vcc-1V。

2、当输入端Input为逻辑高电平时,Q1晶体管截止,此时电流流经R1和Q1的PN结,流向Q2的基极,Q2晶体管导通。

《半导体集成电路》考试题目及参考答案(DOC)1.双极性集成电路中最常用的电阻器和MOS集成电路中常用的电阻都有哪些?2.集成电路中常用的电容有哪些。

3. 为什么基区薄层电阻需要修正。

4. 为什么新的工艺中要用铜布线取代铝布线。

5. 运用基区扩散电阻,设计一个方块电阻200欧,阻值为1K的电阻,已知耗散功率为20W/c㎡,该电阻上的压降为5V,设计此电阻。

第4章TTL电路1.名词解释电压传输特性开门/关门电平逻辑摆幅过渡区宽度输入短路电流输入漏电流静态功耗瞬态延迟时间瞬态存储时间瞬态上升时间瞬态下降时间瞬时导通时间2. 分析四管标准TTL与非门(稳态时)各管的工作状态?3. 在四管标准与非门中,那个管子会对瞬态特性影响最大,并分析原因以及带来那些困难。

4. 两管与非门有哪些缺点,四管及五管与非门的结构相对于两管与非门在那些地方做了改善,并分析改善部分是如何工作的。

四管和五管与非门对静态和动态有那些方面的改进。

5. 相对于五管与非门六管与非门的结构在那些部分作了改善,分析改进部分是如何工作的。

6. 画出四管和六管单元与非门传输特性曲线。

并说明为什么有源泄放回路改善了传输特性的矩形性。

7. 四管与非门中,如果高电平过低,低电平过高,分析其原因,如与改善方法,请说出你的想法。

8. 为什么TTL与非门不能直接并联?9. OC门在结构上作了什么改进,它为什么不会出现TTL与非门并联的问题。

第5章MOS反相器1. 请给出NMOS晶体管的阈值电压公式,并解释各项的物理含义及其对阈值大小的影响(即各项在不同情况下是提高阈值还是降低阈值)。

2. 什么是器件的亚阈值特性,对器件有什么影响?3. MOS晶体管的短沟道效应是指什么,其对晶体管有什么影响?4. 请以PMOS晶体管为例解释什么是衬偏效应,并解释其对PMOS晶体管阈值电压和漏源电流的影响。

5. 什么是沟道长度调制效应,对器件有什么影响?6. 为什么MOS晶体管会存在饱和区和非饱和区之分(不考虑沟道调制效应)?7.请画出晶体管的D DS特性曲线,指出饱和区和I V非饱和区的工作条件及各自的电流方程(忽略沟道长度调制效应和短沟道效应)。

集成电路试题库(总49页) -本页仅作为预览文档封面,使用时请删除本页-半导体集成电路典型试题绪论1、什么叫半导体集成电路?【答案:】通过一系列的加工工艺,将晶体管,二极管等有源器件和电阻,电容等无源元件,按一定电路互连。

集成在一块半导体基片上。

封装在一个外壳内,执行特定的电路或系统功能。

2、按照半导体集成电路的集成度来分,分为哪些类型,请同时写出它们对应的英文缩写【答案:】小规模集成电路(SSI),中规模集成电路(MSI),大规模集成电路(VSI),超大规模集成电路(VLSI),特大规模集成电路(ULSI),巨大规模集成电路(GSI)3、按照器件类型分,半导体集成电路分为哪几类?【答案:】双极型(BJT)集成电路,单极型(MOS)集成电路,Bi-CMOS型集成电路。

4、按电路功能或信号类型分,半导体集成电路分为哪几类?【答案:】数字集成电路,模拟集成电路,数模混合集成电路。

5、什么是特征尺寸它对集成电路工艺有何影响【答案:】集成电路中半导体器件的最小尺寸如MOSFET的最小沟道长度。

是衡量集成电路加工和设计水平的重要标志。

它的减小使得芯片集成度的直接提高。

6、名词解释:集成度、wafer size、die size、摩尔定律?【答案:】7、分析下面的电路,指出它完成的逻辑功能,说明它和一般动态组合逻辑电路的不同,分析它的工作原理。

【答案:】该电路可以完成NAND逻辑。

与一般动态组合逻辑电路相比,它增加了一个MOS管M kp,它可以解决一般动态组合逻辑电路存在的电荷分配的问题。

对于一般的动态组合逻辑电路,在评估阶段,A=“H” B=“L”, 电荷被OUT处和A处的电荷分配,整体的阈值下降,可能导致OUT的输出错误。

该电路增加了一个MOS管M kp,在预充电阶段,M kp导通,对C点充电到V dd。

在评估阶段,M kp截至,不影响电路的正常输出。

8、延迟时间【答案:】时钟沿与输出端之间的延迟第1章集成电路的基本制造工艺1、四层三结的结构的双极型晶体管中隐埋层的作用【答案:】减小集电极串联电阻,减小寄生PNP管的影响2、在制作晶体管的时候,衬底材料电阻率的选取对器件有何影响【答案:】电阻率过大将增大集电极串联电阻,扩大饱和压降,若过小耐压低,结电容增大,且外延时下推大3、简单叙述一下pn结隔离的NPN晶体管的光刻步骤【答案:】第一次光刻:N+隐埋层扩散孔光刻第二次光刻:P隔离扩散孔光刻第三次光刻:P型基区扩散孔光刻第四次光刻:N+发射区扩散孔光刻第五次光刻:引线孔光刻第六次光刻:反刻铝4、简述硅栅p阱CMOS的光刻步骤【答案:】P阱光刻,光刻有源区,光刻多晶硅,P+区光刻,N+区光刻,光刻接触孔,光刻铝线5、以p阱CMOS工艺为基础的BiCMOS的有哪些不足【答案:】NPN晶体管电流增益小,集电极串联电阻大,NPN管的C极只能接固定电位6、以N阱CMOS工艺为基础的BiCMOS的有哪些优缺点?并请提出改进方法【答案:】首先NPN具有较薄的基区,提高了其性能:N阱使得NPN管C极与衬底断开,可根据电路需要接任意电位。