A Comparison of FPGA and GPU for Real-Time Phase-Based Optical Flow,Stereo, and Local Image Features

- 格式:pdf

- 大小:2.15 MB

- 文档页数:14

代号分类号学号密级10701TP37公开1102121253题(中、英文)目基于GPU/多核CPU平台下并行计算的实时超分辨和立体视图生成Real-time Super-resolution and Stereoscopic View Genera-tion with GPU/Multicore CPU Based Parallel Computing 作者姓名孙增增指导教师姓名、职务郑喆坤教授学科门类工学提交论文日期二〇一四年三月学科、专业模式识别与智能系统西安电子科技大学学位论文独创性(或创新性)声明秉承学校严谨的学风和优良的科学道德,本人声明所呈交的论文是我个人在导师指导下进行的研究工作及取得的研究成果。

尽我所知,除了文中特别加以标注和致谢中所罗列的内容以外,论文中不包含其他人已经发表或撰写过的研究成果;也不包含为获得西安电子科技大学或其它教育机构的学位或证书而使用过的材料。

与我一同工作的同志对本研究所做的任何贡献均已在论文中做了明确的说明并表示了谢意。

申请学位论文与资料若有不实之处,本人承担一切的法律责任。

本人签名:日期:西安电子科技大学关于论文使用授权的说明本人完全了解西安电子科技大学有关保留和使用学位论文的规定,即:研究生在校攻读学位期间论文工作的知识产权单位属西安电子科技大学。

学校有权保留送交论文的复印件,允许查阅和借阅论文;学校可以公布论文的全部或部分内容,可以允许采用影印、缩印或其它复制手段保存论文。

同时本人保证,毕业后结合学位论文研究课题再撰写的文章一律署名单位为西安电子科技大学。

(保密的论文在解密后遵守此规定)本人授权西安电子科技大学图书馆保存学位论文,本学位论文属于(保密级别),在年解密后适用本授权书,并同意将论文在互联网上发布。

本人签名:日期:导师签名:日期:摘要近些年来,许多因素导致了计算产业转向了并行化发展的方向。

在这过程中,受市场对实时、高清晰3维图形绘制的需求驱使,可编程的图形处理单元(GPU)逐渐发展进化成为了具有强大计算能力、非常高内存带宽的高度并行、多线程的众核处理器。

第46卷 第3期2024年3月系统工程与电子技术SystemsEngineeringandElectronicsVol.46 No.3March2024文章编号:1001 506X(2024)03 0795 10 网址:www.sys ele.com收稿日期:20230313;修回日期:20230616;网络优先出版日期:20230818。

网络优先出版地址:http:∥link.cnki.net/urlid/11.2422.TN.20230818.1441.002基金项目:国家自然科学基金(U1934222,62027809,U2268206);北京交通大学人才基金(2022XKRC003)资助课题 通讯作者.引用格式:王子涵,巴晓辉,姜维,等.基于GPU的北斗B1宽带复合信号实时发生器设计[J].系统工程与电子技术,2024,46(3):795 804.犚犲犳犲狉犲狀犮犲犳狅狉犿犪狋:WANGZH,BAXH,JIANGW,etal.Real timedesignofwidebandcompositesignalgeneratorforBeidouB1basedonGPU[J].SystemsEngineeringandElectronics,2024,46(3):795 804.基于犌犘犝的北斗犅1宽带复合信号实时发生器设计王子涵1,巴晓辉1,2,3, ,姜 维1,2,3,蔡伯根2,3,4,王 剑1,2,3,文 韬1,2,3(1.北京交通大学电子信息工程学院,北京100044;2.北京交通大学轨道交通控制与安全国家重点实验室,北京100044;3.北京市电磁兼容与卫星导航工程技术研究中心,北京100044;4.北京交通大学计算机与信息技术学院,北京100044) 摘 要:为了实现北斗B1C+B1I信号的联合生成,提出一种基于软件无线电和图形处理器(graphicsprocessingunit,GPU)加速的北斗B1宽带复合信号的实时生成方法,该方法针对单边带复数二进制偏移载波(single sidebandcomplexbinaryoffsetcarrier,SCBOC)调制方式的信号体制进行设计,系统根据用户配置的接收机运动轨迹和星历文件,生成中频信号并通过射频端发射。

行业研究东兴证券股份有限公司证券研究报告FPGA提供了什么价值?——“FPGA五问五答”系列报告一投资摘要:FPGA(可编程逻辑门阵列)又称“万能芯片”,美国禁运后,作为最“卡脖子”的芯片之一而家喻户晓。

虽然全球市场规模只有80亿美元,FPGA这个不大不小的市场却撑起了龙头赛灵思近500亿美元的市值(英特尔平均市值在2000亿美元上下,所在市场规模是FPGA的10倍)。

目前,全球90%的市场份额由美国FPGA厂商垄断,国产替代必要性不言而明。

美国禁运后,国产FPGA厂商迎来发展的历史性机遇。

FPGA究竟有什么价值?什么在驱动它的未来的成长?龙头为什么能有这么高的市场份额?护城河在哪里?本土厂商又要如何培育自己的竞争优势?针对这些问题,我们复盘了FPGA三大厂商:赛灵思、Altera和Lattice的发展历程,总结出了核心规律,并在FPGA五问五答系列报告中逐一为投资者解答。

作为我们FPGA五问五答第一篇,在这篇报告中,我们首先回答一个最关键的问题——FPGA提供了什么价值?为了回答这个问题,我们仔细研究了FPGA和其他处理器的架构演变和历史,回答如下:FPGA无可比拟的灵活性,以及确定性的低时延优势,是FPGA难以被替代的原因,也是FPGA为客户提供的独一无二的价值。

FPGA是什么?在半导体产业链中的位置?芯片分为模拟芯片和数字芯片,数字芯片负责处理数字信号,分为处理器、逻辑、存储三大类。

FPGA是可编程的逻辑芯片,和其它逻辑芯片的不同之处在于,用户可以随时定义其硬件功能。

虽然FPGA市场仅占逻辑芯片的5%,市场规模仅有微处理器的大约十分之一,但在许多领域是不可或缺的。

FPGA为什么在历史上脱颖而出?PLD诞生的动因来自于ASIC和ASSP的不足,通过可编程来满足降低芯片设计风险的需求。

FPGA并不是第一个被创造出来的可编程逻辑器件,但由于FPGA的架构弥补了PLD和ASIC/ASSP的缺环,能够满足下游不断增长的容量和速度的需求,在发明后的10年开始飞速替代SPLD和CPLD,成为独占鳌头的可编程逻辑器件。

2024年普通高等学校招生全国统一考试(新课标Ⅰ卷)英语学科姓名________________准考证号________________全卷共12页,满分150分,考试时间120分钟。

考生注意:1.答题前,请务必将自己的姓名、准考证号用黑色字迹的签字笔或钢笔分别填写在试题卷和答题纸规定的位置上。

2.答题时,请按照答题纸上“注意事项”的要求,在答题纸相应的位置上规范作答,在本试题卷上的作答一律无效。

第一部分听力(共两节,满分30分)做题时,先将答案标在试卷上。

录音内容结束后,你将有两分钟的时间将试卷上的答案转涂到答题纸上。

第一节(共5小题;每小题1.5分,满分7.5分)听下面5段对话。

每段对话后有一个小题,从题中所给的A、B、C三个选项中选出最佳选项。

听完每段对话后,你都有10秒钟的时间来回答有关小题和阅读下一小题。

每段对话仅读一遍。

例:How much is the shirt?A.£19.15.B.£9.18.C.£9.15.答案是C。

1.【此处可播放相关音频,请去附件查看】What is Kate doing?A.Boarding a flight.B.Arranging a trip.C.Seeing a friend off.2.【此处可播放相关音频,请去附件查看】What are the speakers talking about?A.A pop star.B.An old song.C.A radio program.3.【此处可播放相关音频,请去附件查看】What will the speakers do today?A.Go to an art show.B.Meet the man's aunt.C.Eat out with Mark.4.【此处可播放相关音频,请去附件查看】What does the man want to do?A.Cancel an order.B.Ask for a receipt.C.Reschedule a delivery.5.【此处可播放相关音频,请去附件查看】When will the next train to Bedford leave?A.At9:45.B.At10:15.C.At11:00.第二节(共15小题;每小题1.5分,满分22.5分)听下面5段对话或独白。

gpu 推理英语GPU Inference in EnglishGPU inference refers to the use of a graphics processing unit (GPU) for performing推理 tasks in deep learning and artificial intelligence applications. GPUs are specialized processors designed to handle parallel computations, making them well-suited for accelerating inference workloads.During the inference phase, a trained neural network model is used to make predictions or inferences on new data. Instead of processing the data on a central processing unit (CPU), GPUs can be utilized to expedite the inference process. By offloading the computations to the GPU, significant performance gains can be achieved, enabling real-time or near-real-time inference.GPU inference offers several benefits, including high throughput and low latency. GPUs possess a large number of cores and can simultaneously process multiple data elements in parallel, resulting in faster inference speeds. This is particularly beneficial for applications such as image recognition, natural language processing, and video analysis, where large amounts of data need to be processed in a timely manner.To perform GPU inference, deep learning frameworks and libraries often provide GPU-optimized versions or extensions. These frameworks leverage the parallel computing capabilities of GPUs to accelerate the execution of neural network models. By using CUDA (Compute Unified Device Architecture) or other GPU programming interfaces, developers can explicitly program the GPU to optimize the inference workflow.GPU inference is becoming increasingly prevalent in various industries, including healthcare, finance, autonomous vehicles, and entertainment. It allows for the deployment of complex AI models on edge devices or in the cloud, enabling real-time decision-making and enhanced user experiences.In summary, GPU inference leverages the parallel processing power of GPUs toaccelerate the inference process in deep learning and artificial intelligence applications, offering improved performance and efficiency.。

0引言深度卷积神经网络(Convolutional Neural Network ,CNN)已经成为了当前计算机视觉系统中最有前景的图像分析方法之一。

近年来,随着Binary-Net 、Dorefa-Net 、ABC-Net 等[1-3]低精度量化神经网络的深入研究,越来越多的研究集中于在FPGA 硬件中构建定制的加速器结构,实现CNN 的加速[4]。

基于FPGA 的低精度量化神经网络实现主要可分为两类:流架构[5-6]和层架构[7-8]。

其中,由于流架构实现了流水线化,每个阶段都可以独立处理输入且可以针对CNN 逐层设计并优化相应层的加速运算单元,因此拥有更高的吞吐率和更低的延迟以及内存带宽,但其逻辑资源等消耗也相当可观。

因此,现有的基于流架构实现的二值神经网络加速器研究大多是针对32×32尺度MNIST 数据集等小尺度的图像输入。

而实际应用中更多使用如448×448尺度的YOLO 、224×224尺度的VGG 等作为骨干网络,一方面,大尺度输入的网络结构参数量往往较大(以VGG 为例,其参数量大约500MB),高端FPGA 的片上内存容量也仅32.1Mb 左右,这对FPGA 实现CNN 加速将是资源瓶颈。

即使采用低精度量化策略,FPGA 有限的片上内存资源仍捉襟见肘。

另一方面,虽然各层运算单元可以得到特定优化,然而由于网络拓扑结构限制,往往各层网络很难实现计算周期的匹配,从而造成推断性能难以进一步提高。

针对基于流架构的二值卷积神经网络加速器设计存在的资源与性能的瓶颈,本文以224×224尺度的VGG-11网络加速器设计为例,重点研究了大尺度的二值卷积神经网络硬件加速器设计、优化及验证,主要工作如下:(1)针对大尺度流架构的二值VGG 卷积神经网络加速器设计存在的资源与性能瓶颈,提出了网络模型优化二值VGG 卷积神经网络加速器优化设计∗张旭欣,张嘉,李新增,金婕(上海工程技术大学电子电气工程学院,上海201600)摘要:基于FPGA 的二值卷积神经网络加速器研究大多是针对小尺度的图像输入,而实际应用主要以YOLO 、VGG 等大尺度的卷积神经网络作为骨干网络。

FPGA,GPU和CPU在高性能计算领域的应用及展望课程:系统及可编程芯片设计专业:微电子学与固体电子学姓名:学号:任课老师:FPGA,GPU和CPU在高性能计算领域的应用及展望目前FPGA对于浮点数的运算速度已经达到1TFLOP(每秒万亿次浮点运算),同时GPU和多核CPU通过利用最新的IC设计技术也大大提高了其运算能力。

本文将对比三种结构对于高性能计算的发展趋势,同时也会介绍在特定运算环境下三种结构的持续性能。

1. 高性能计算中FPGA,GPU和CPU的简介近年来,传统用于图像处理的GPU逐渐被发掘用来进行高性能计算,并且达到了相当好的效果,在单精度浮点运算中的速度达到5TFLOPs,在双精度浮点运算中的速度可以达到1TFLOPs。

如今性能最好的GPU处理器(比如NVidea 的Tesla K20和K40)与一些其他的多核处理器(比如Intel Xeon Phi处理器以及IBM和Inter的一些处理器)相比表现出了非常好的计算性能。

FPGA传统上是应用于单精度的定点运算,不过现在也可以浮点数进行高性能的计算,单精度浮点数的运算峰值已经超过1TFLOPs。

但是运算的峰值并不能代表在特定环境下器件的持续工作性能,比如在计算2级的FFT时,Inter的80-teraflop持续工作性能只能达到其峰值性能的2.73%(20GFLOPs)。

FPGA工作在一个较低的频率下,运算峰值较低,但是可以通过硬件优化来实现对特定应用的更好的运行效率,即持续性能能达到更接近峰值运算性能的值,同时与GPU 和CPU相比FPGA的功率效率更高。

一个特定的应用在不同的平台上运算是不一样的,对于运算结果的评估可以基于以下几点:性能、功耗、功率效率、运行效率、成本以及其他。

在本文中,我们分析每个期间在峰值性能以及能耗方面的发展趋势,并对三者在一些科学应用的持续性能进行对比,找出对于某一特定应用的最佳运算平台。

2. 峰值计算性能发展趋势2.1GPUGPU最初被设计用来进行图像处理并在该方面显示出了强大的优势,近10年来GPU逐渐被应用到通用计算领域,一般称为GPGPU。

华中师范大学物理学院物理学专业英语仅供内部学习参考!2014一、课程的任务和教学目的通过学习《物理学专业英语》,学生将掌握物理学领域使用频率较高的专业词汇和表达方法,进而具备基本的阅读理解物理学专业文献的能力。

通过分析《物理学专业英语》课程教材中的范文,学生还将从英语角度理解物理学中个学科的研究内容和主要思想,提高学生的专业英语能力和了解物理学研究前沿的能力。

培养专业英语阅读能力,了解科技英语的特点,提高专业外语的阅读质量和阅读速度;掌握一定量的本专业英文词汇,基本达到能够独立完成一般性本专业外文资料的阅读;达到一定的笔译水平。

要求译文通顺、准确和专业化。

要求译文通顺、准确和专业化。

二、课程内容课程内容包括以下章节:物理学、经典力学、热力学、电磁学、光学、原子物理、统计力学、量子力学和狭义相对论三、基本要求1.充分利用课内时间保证充足的阅读量(约1200~1500词/学时),要求正确理解原文。

2.泛读适量课外相关英文读物,要求基本理解原文主要内容。

3.掌握基本专业词汇(不少于200词)。

4.应具有流利阅读、翻译及赏析专业英语文献,并能简单地进行写作的能力。

四、参考书目录1 Physics 物理学 (1)Introduction to physics (1)Classical and modern physics (2)Research fields (4)V ocabulary (7)2 Classical mechanics 经典力学 (10)Introduction (10)Description of classical mechanics (10)Momentum and collisions (14)Angular momentum (15)V ocabulary (16)3 Thermodynamics 热力学 (18)Introduction (18)Laws of thermodynamics (21)System models (22)Thermodynamic processes (27)Scope of thermodynamics (29)V ocabulary (30)4 Electromagnetism 电磁学 (33)Introduction (33)Electrostatics (33)Magnetostatics (35)Electromagnetic induction (40)V ocabulary (43)5 Optics 光学 (45)Introduction (45)Geometrical optics (45)Physical optics (47)Polarization (50)V ocabulary (51)6 Atomic physics 原子物理 (52)Introduction (52)Electronic configuration (52)Excitation and ionization (56)V ocabulary (59)7 Statistical mechanics 统计力学 (60)Overview (60)Fundamentals (60)Statistical ensembles (63)V ocabulary (65)8 Quantum mechanics 量子力学 (67)Introduction (67)Mathematical formulations (68)Quantization (71)Wave-particle duality (72)Quantum entanglement (75)V ocabulary (77)9 Special relativity 狭义相对论 (79)Introduction (79)Relativity of simultaneity (80)Lorentz transformations (80)Time dilation and length contraction (81)Mass-energy equivalence (82)Relativistic energy-momentum relation (86)V ocabulary (89)正文标记说明:蓝色Arial字体(例如energy):已知的专业词汇蓝色Arial字体加下划线(例如electromagnetism):新学的专业词汇黑色Times New Roman字体加下划线(例如postulate):新学的普通词汇1 Physics 物理学1 Physics 物理学Introduction to physicsPhysics is a part of natural philosophy and a natural science that involves the study of matter and its motion through space and time, along with related concepts such as energy and force. More broadly, it is the general analysis of nature, conducted in order to understand how the universe behaves.Physics is one of the oldest academic disciplines, perhaps the oldest through its inclusion of astronomy. Over the last two millennia, physics was a part of natural philosophy along with chemistry, certain branches of mathematics, and biology, but during the Scientific Revolution in the 17th century, the natural sciences emerged as unique research programs in their own right. Physics intersects with many interdisciplinary areas of research, such as biophysics and quantum chemistry,and the boundaries of physics are not rigidly defined. New ideas in physics often explain the fundamental mechanisms of other sciences, while opening new avenues of research in areas such as mathematics and philosophy.Physics also makes significant contributions through advances in new technologies that arise from theoretical breakthroughs. For example, advances in the understanding of electromagnetism or nuclear physics led directly to the development of new products which have dramatically transformed modern-day society, such as television, computers, domestic appliances, and nuclear weapons; advances in thermodynamics led to the development of industrialization; and advances in mechanics inspired the development of calculus.Core theoriesThough physics deals with a wide variety of systems, certain theories are used by all physicists. Each of these theories were experimentally tested numerous times and found correct as an approximation of nature (within a certain domain of validity).For instance, the theory of classical mechanics accurately describes the motion of objects, provided they are much larger than atoms and moving at much less than the speed of light. These theories continue to be areas of active research, and a remarkable aspect of classical mechanics known as chaos was discovered in the 20th century, three centuries after the original formulation of classical mechanics by Isaac Newton (1642–1727) 【艾萨克·牛顿】.University PhysicsThese central theories are important tools for research into more specialized topics, and any physicist, regardless of his or her specialization, is expected to be literate in them. These include classical mechanics, quantum mechanics, thermodynamics and statistical mechanics, electromagnetism, and special relativity.Classical and modern physicsClassical mechanicsClassical physics includes the traditional branches and topics that were recognized and well-developed before the beginning of the 20th century—classical mechanics, acoustics, optics, thermodynamics, and electromagnetism.Classical mechanics is concerned with bodies acted on by forces and bodies in motion and may be divided into statics (study of the forces on a body or bodies at rest), kinematics (study of motion without regard to its causes), and dynamics (study of motion and the forces that affect it); mechanics may also be divided into solid mechanics and fluid mechanics (known together as continuum mechanics), the latter including such branches as hydrostatics, hydrodynamics, aerodynamics, and pneumatics.Acoustics is the study of how sound is produced, controlled, transmitted and received. Important modern branches of acoustics include ultrasonics, the study of sound waves of very high frequency beyond the range of human hearing; bioacoustics the physics of animal calls and hearing, and electroacoustics, the manipulation of audible sound waves using electronics.Optics, the study of light, is concerned not only with visible light but also with infrared and ultraviolet radiation, which exhibit all of the phenomena of visible light except visibility, e.g., reflection, refraction, interference, diffraction, dispersion, and polarization of light.Heat is a form of energy, the internal energy possessed by the particles of which a substance is composed; thermodynamics deals with the relationships between heat and other forms of energy.Electricity and magnetism have been studied as a single branch of physics since the intimate connection between them was discovered in the early 19th century; an electric current gives rise to a magnetic field and a changing magnetic field induces an electric current. Electrostatics deals with electric charges at rest, electrodynamics with moving charges, and magnetostatics with magnetic poles at rest.Modern PhysicsClassical physics is generally concerned with matter and energy on the normal scale of1 Physics 物理学observation, while much of modern physics is concerned with the behavior of matter and energy under extreme conditions or on the very large or very small scale.For example, atomic and nuclear physics studies matter on the smallest scale at which chemical elements can be identified.The physics of elementary particles is on an even smaller scale, as it is concerned with the most basic units of matter; this branch of physics is also known as high-energy physics because of the extremely high energies necessary to produce many types of particles in large particle accelerators. On this scale, ordinary, commonsense notions of space, time, matter, and energy are no longer valid.The two chief theories of modern physics present a different picture of the concepts of space, time, and matter from that presented by classical physics.Quantum theory is concerned with the discrete, rather than continuous, nature of many phenomena at the atomic and subatomic level, and with the complementary aspects of particles and waves in the description of such phenomena.The theory of relativity is concerned with the description of phenomena that take place in a frame of reference that is in motion with respect to an observer; the special theory of relativity is concerned with relative uniform motion in a straight line and the general theory of relativity with accelerated motion and its connection with gravitation.Both quantum theory and the theory of relativity find applications in all areas of modern physics.Difference between classical and modern physicsWhile physics aims to discover universal laws, its theories lie in explicit domains of applicability. Loosely speaking, the laws of classical physics accurately describe systems whose important length scales are greater than the atomic scale and whose motions are much slower than the speed of light. Outside of this domain, observations do not match their predictions.Albert Einstein【阿尔伯特·爱因斯坦】contributed the framework of special relativity, which replaced notions of absolute time and space with space-time and allowed an accurate description of systems whose components have speeds approaching the speed of light.Max Planck【普朗克】, Erwin Schrödinger【薛定谔】, and others introduced quantum mechanics, a probabilistic notion of particles and interactions that allowed an accurate description of atomic and subatomic scales.Later, quantum field theory unified quantum mechanics and special relativity.General relativity allowed for a dynamical, curved space-time, with which highly massiveUniversity Physicssystems and the large-scale structure of the universe can be well-described. General relativity has not yet been unified with the other fundamental descriptions; several candidate theories of quantum gravity are being developed.Research fieldsContemporary research in physics can be broadly divided into condensed matter physics; atomic, molecular, and optical physics; particle physics; astrophysics; geophysics and biophysics. Some physics departments also support research in Physics education.Since the 20th century, the individual fields of physics have become increasingly specialized, and today most physicists work in a single field for their entire careers. "Universalists" such as Albert Einstein (1879–1955) and Lev Landau (1908–1968)【列夫·朗道】, who worked in multiple fields of physics, are now very rare.Condensed matter physicsCondensed matter physics is the field of physics that deals with the macroscopic physical properties of matter. In particular, it is concerned with the "condensed" phases that appear whenever the number of particles in a system is extremely large and the interactions between them are strong.The most familiar examples of condensed phases are solids and liquids, which arise from the bonding by way of the electromagnetic force between atoms. More exotic condensed phases include the super-fluid and the Bose–Einstein condensate found in certain atomic systems at very low temperature, the superconducting phase exhibited by conduction electrons in certain materials,and the ferromagnetic and antiferromagnetic phases of spins on atomic lattices.Condensed matter physics is by far the largest field of contemporary physics.Historically, condensed matter physics grew out of solid-state physics, which is now considered one of its main subfields. The term condensed matter physics was apparently coined by Philip Anderson when he renamed his research group—previously solid-state theory—in 1967. In 1978, the Division of Solid State Physics of the American Physical Society was renamed as the Division of Condensed Matter Physics.Condensed matter physics has a large overlap with chemistry, materials science, nanotechnology and engineering.Atomic, molecular and optical physicsAtomic, molecular, and optical physics (AMO) is the study of matter–matter and light–matter interactions on the scale of single atoms and molecules.1 Physics 物理学The three areas are grouped together because of their interrelationships, the similarity of methods used, and the commonality of the energy scales that are relevant. All three areas include both classical, semi-classical and quantum treatments; they can treat their subject from a microscopic view (in contrast to a macroscopic view).Atomic physics studies the electron shells of atoms. Current research focuses on activities in quantum control, cooling and trapping of atoms and ions, low-temperature collision dynamics and the effects of electron correlation on structure and dynamics. Atomic physics is influenced by the nucleus (see, e.g., hyperfine splitting), but intra-nuclear phenomena such as fission and fusion are considered part of high-energy physics.Molecular physics focuses on multi-atomic structures and their internal and external interactions with matter and light.Optical physics is distinct from optics in that it tends to focus not on the control of classical light fields by macroscopic objects, but on the fundamental properties of optical fields and their interactions with matter in the microscopic realm.High-energy physics (particle physics) and nuclear physicsParticle physics is the study of the elementary constituents of matter and energy, and the interactions between them.In addition, particle physicists design and develop the high energy accelerators,detectors, and computer programs necessary for this research. The field is also called "high-energy physics" because many elementary particles do not occur naturally, but are created only during high-energy collisions of other particles.Currently, the interactions of elementary particles and fields are described by the Standard Model.●The model accounts for the 12 known particles of matter (quarks and leptons) thatinteract via the strong, weak, and electromagnetic fundamental forces.●Dynamics are described in terms of matter particles exchanging gauge bosons (gluons,W and Z bosons, and photons, respectively).●The Standard Model also predicts a particle known as the Higgs boson. In July 2012CERN, the European laboratory for particle physics, announced the detection of a particle consistent with the Higgs boson.Nuclear Physics is the field of physics that studies the constituents and interactions of atomic nuclei. The most commonly known applications of nuclear physics are nuclear power generation and nuclear weapons technology, but the research has provided application in many fields, including those in nuclear medicine and magnetic resonance imaging, ion implantation in materials engineering, and radiocarbon dating in geology and archaeology.University PhysicsAstrophysics and Physical CosmologyAstrophysics and astronomy are the application of the theories and methods of physics to the study of stellar structure, stellar evolution, the origin of the solar system, and related problems of cosmology. Because astrophysics is a broad subject, astrophysicists typically apply many disciplines of physics, including mechanics, electromagnetism, statistical mechanics, thermodynamics, quantum mechanics, relativity, nuclear and particle physics, and atomic and molecular physics.The discovery by Karl Jansky in 1931 that radio signals were emitted by celestial bodies initiated the science of radio astronomy. Most recently, the frontiers of astronomy have been expanded by space exploration. Perturbations and interference from the earth's atmosphere make space-based observations necessary for infrared, ultraviolet, gamma-ray, and X-ray astronomy.Physical cosmology is the study of the formation and evolution of the universe on its largest scales. Albert Einstein's theory of relativity plays a central role in all modern cosmological theories. In the early 20th century, Hubble's discovery that the universe was expanding, as shown by the Hubble diagram, prompted rival explanations known as the steady state universe and the Big Bang.The Big Bang was confirmed by the success of Big Bang nucleo-synthesis and the discovery of the cosmic microwave background in 1964. The Big Bang model rests on two theoretical pillars: Albert Einstein's general relativity and the cosmological principle (On a sufficiently large scale, the properties of the Universe are the same for all observers). Cosmologists have recently established the ΛCDM model (the standard model of Big Bang cosmology) of the evolution of the universe, which includes cosmic inflation, dark energy and dark matter.Current research frontiersIn condensed matter physics, an important unsolved theoretical problem is that of high-temperature superconductivity. Many condensed matter experiments are aiming to fabricate workable spintronics and quantum computers.In particle physics, the first pieces of experimental evidence for physics beyond the Standard Model have begun to appear. Foremost among these are indications that neutrinos have non-zero mass. These experimental results appear to have solved the long-standing solar neutrino problem, and the physics of massive neutrinos remains an area of active theoretical and experimental research. Particle accelerators have begun probing energy scales in the TeV range, in which experimentalists are hoping to find evidence for the super-symmetric particles, after discovery of the Higgs boson.Theoretical attempts to unify quantum mechanics and general relativity into a single theory1 Physics 物理学of quantum gravity, a program ongoing for over half a century, have not yet been decisively resolved. The current leading candidates are M-theory, superstring theory and loop quantum gravity.Many astronomical and cosmological phenomena have yet to be satisfactorily explained, including the existence of ultra-high energy cosmic rays, the baryon asymmetry, the acceleration of the universe and the anomalous rotation rates of galaxies.Although much progress has been made in high-energy, quantum, and astronomical physics, many everyday phenomena involving complexity, chaos, or turbulence are still poorly understood. Complex problems that seem like they could be solved by a clever application of dynamics and mechanics remain unsolved; examples include the formation of sand-piles, nodes in trickling water, the shape of water droplets, mechanisms of surface tension catastrophes, and self-sorting in shaken heterogeneous collections.These complex phenomena have received growing attention since the 1970s for several reasons, including the availability of modern mathematical methods and computers, which enabled complex systems to be modeled in new ways. Complex physics has become part of increasingly interdisciplinary research, as exemplified by the study of turbulence in aerodynamics and the observation of pattern formation in biological systems.Vocabulary★natural science 自然科学academic disciplines 学科astronomy 天文学in their own right 凭他们本身的实力intersects相交,交叉interdisciplinary交叉学科的,跨学科的★quantum 量子的theoretical breakthroughs 理论突破★electromagnetism 电磁学dramatically显著地★thermodynamics热力学★calculus微积分validity★classical mechanics 经典力学chaos 混沌literate 学者★quantum mechanics量子力学★thermodynamics and statistical mechanics热力学与统计物理★special relativity狭义相对论is concerned with 关注,讨论,考虑acoustics 声学★optics 光学statics静力学at rest 静息kinematics运动学★dynamics动力学ultrasonics超声学manipulation 操作,处理,使用University Physicsinfrared红外ultraviolet紫外radiation辐射reflection 反射refraction 折射★interference 干涉★diffraction 衍射dispersion散射★polarization 极化,偏振internal energy 内能Electricity电性Magnetism 磁性intimate 亲密的induces 诱导,感应scale尺度★elementary particles基本粒子★high-energy physics 高能物理particle accelerators 粒子加速器valid 有效的,正当的★discrete离散的continuous 连续的complementary 互补的★frame of reference 参照系★the special theory of relativity 狭义相对论★general theory of relativity 广义相对论gravitation 重力,万有引力explicit 详细的,清楚的★quantum field theory 量子场论★condensed matter physics凝聚态物理astrophysics天体物理geophysics地球物理Universalist博学多才者★Macroscopic宏观Exotic奇异的★Superconducting 超导Ferromagnetic铁磁质Antiferromagnetic 反铁磁质★Spin自旋Lattice 晶格,点阵,网格★Society社会,学会★microscopic微观的hyperfine splitting超精细分裂fission分裂,裂变fusion熔合,聚变constituents成分,组分accelerators加速器detectors 检测器★quarks夸克lepton 轻子gauge bosons规范玻色子gluons胶子★Higgs boson希格斯玻色子CERN欧洲核子研究中心★Magnetic Resonance Imaging磁共振成像,核磁共振ion implantation 离子注入radiocarbon dating放射性碳年代测定法geology地质学archaeology考古学stellar 恒星cosmology宇宙论celestial bodies 天体Hubble diagram 哈勃图Rival竞争的★Big Bang大爆炸nucleo-synthesis核聚合,核合成pillar支柱cosmological principle宇宙学原理ΛCDM modelΛ-冷暗物质模型cosmic inflation宇宙膨胀1 Physics 物理学fabricate制造,建造spintronics自旋电子元件,自旋电子学★neutrinos 中微子superstring 超弦baryon重子turbulence湍流,扰动,骚动catastrophes突变,灾变,灾难heterogeneous collections异质性集合pattern formation模式形成University Physics2 Classical mechanics 经典力学IntroductionIn physics, classical mechanics is one of the two major sub-fields of mechanics, which is concerned with the set of physical laws describing the motion of bodies under the action of a system of forces. The study of the motion of bodies is an ancient one, making classical mechanics one of the oldest and largest subjects in science, engineering and technology.Classical mechanics describes the motion of macroscopic objects, from projectiles to parts of machinery, as well as astronomical objects, such as spacecraft, planets, stars, and galaxies. Besides this, many specializations within the subject deal with gases, liquids, solids, and other specific sub-topics.Classical mechanics provides extremely accurate results as long as the domain of study is restricted to large objects and the speeds involved do not approach the speed of light. When the objects being dealt with become sufficiently small, it becomes necessary to introduce the other major sub-field of mechanics, quantum mechanics, which reconciles the macroscopic laws of physics with the atomic nature of matter and handles the wave–particle duality of atoms and molecules. In the case of high velocity objects approaching the speed of light, classical mechanics is enhanced by special relativity. General relativity unifies special relativity with Newton's law of universal gravitation, allowing physicists to handle gravitation at a deeper level.The initial stage in the development of classical mechanics is often referred to as Newtonian mechanics, and is associated with the physical concepts employed by and the mathematical methods invented by Newton himself, in parallel with Leibniz【莱布尼兹】, and others.Later, more abstract and general methods were developed, leading to reformulations of classical mechanics known as Lagrangian mechanics and Hamiltonian mechanics. These advances were largely made in the 18th and 19th centuries, and they extend substantially beyond Newton's work, particularly through their use of analytical mechanics. Ultimately, the mathematics developed for these were central to the creation of quantum mechanics.Description of classical mechanicsThe following introduces the basic concepts of classical mechanics. For simplicity, it often2 Classical mechanics 经典力学models real-world objects as point particles, objects with negligible size. The motion of a point particle is characterized by a small number of parameters: its position, mass, and the forces applied to it.In reality, the kind of objects that classical mechanics can describe always have a non-zero size. (The physics of very small particles, such as the electron, is more accurately described by quantum mechanics). Objects with non-zero size have more complicated behavior than hypothetical point particles, because of the additional degrees of freedom—for example, a baseball can spin while it is moving. However, the results for point particles can be used to study such objects by treating them as composite objects, made up of a large number of interacting point particles. The center of mass of a composite object behaves like a point particle.Classical mechanics uses common-sense notions of how matter and forces exist and interact. It assumes that matter and energy have definite, knowable attributes such as where an object is in space and its speed. It also assumes that objects may be directly influenced only by their immediate surroundings, known as the principle of locality.In quantum mechanics objects may have unknowable position or velocity, or instantaneously interact with other objects at a distance.Position and its derivativesThe position of a point particle is defined with respect to an arbitrary fixed reference point, O, in space, usually accompanied by a coordinate system, with the reference point located at the origin of the coordinate system. It is defined as the vector r from O to the particle.In general, the point particle need not be stationary relative to O, so r is a function of t, the time elapsed since an arbitrary initial time.In pre-Einstein relativity (known as Galilean relativity), time is considered an absolute, i.e., the time interval between any given pair of events is the same for all observers. In addition to relying on absolute time, classical mechanics assumes Euclidean geometry for the structure of space.Velocity and speedThe velocity, or the rate of change of position with time, is defined as the derivative of the position with respect to time. In classical mechanics, velocities are directly additive and subtractive as vector quantities; they must be dealt with using vector analysis.When both objects are moving in the same direction, the difference can be given in terms of speed only by ignoring direction.University PhysicsAccelerationThe acceleration , or rate of change of velocity, is the derivative of the velocity with respect to time (the second derivative of the position with respect to time).Acceleration can arise from a change with time of the magnitude of the velocity or of the direction of the velocity or both . If only the magnitude v of the velocity decreases, this is sometimes referred to as deceleration , but generally any change in the velocity with time, including deceleration, is simply referred to as acceleration.Inertial frames of referenceWhile the position and velocity and acceleration of a particle can be referred to any observer in any state of motion, classical mechanics assumes the existence of a special family of reference frames in terms of which the mechanical laws of nature take a comparatively simple form. These special reference frames are called inertial frames .An inertial frame is such that when an object without any force interactions (an idealized situation) is viewed from it, it appears either to be at rest or in a state of uniform motion in a straight line. This is the fundamental definition of an inertial frame. They are characterized by the requirement that all forces entering the observer's physical laws originate in identifiable sources (charges, gravitational bodies, and so forth).A non-inertial reference frame is one accelerating with respect to an inertial one, and in such a non-inertial frame a particle is subject to acceleration by fictitious forces that enter the equations of motion solely as a result of its accelerated motion, and do not originate in identifiable sources. These fictitious forces are in addition to the real forces recognized in an inertial frame.A key concept of inertial frames is the method for identifying them. For practical purposes, reference frames that are un-accelerated with respect to the distant stars are regarded as good approximations to inertial frames.Forces; Newton's second lawNewton was the first to mathematically express the relationship between force and momentum . Some physicists interpret Newton's second law of motion as a definition of force and mass, while others consider it a fundamental postulate, a law of nature. Either interpretation has the same mathematical consequences, historically known as "Newton's Second Law":a m t v m t p F ===d )(d d dThe quantity m v is called the (canonical ) momentum . The net force on a particle is thus equal to rate of change of momentum of the particle with time.So long as the force acting on a particle is known, Newton's second law is sufficient to。

0引言随着人工智能的快速发展,卷积神经网络越来越受到人们的关注。

由于它的高适应性和出色的识别能力,它已被广泛应用于分类和识别、目标检测、目标跟踪等领域[1]。

与传统算法相比,CNN 的计算复杂度要高得多,并且通用CPU 不再能够满足计算需求。

目前,主要解决方案是使用GPU 进行CNN 计算。

尽管GPU 在并行计算中具有自然优势,但在成本和功耗方面存在很大的缺点。

卷积神经网络推理过程的实现占用空间大,计算能耗大[2],无法满足终端系统的CNN 计算要求。

FPGA 具有强大的并行处理功能,灵活的可配置功能以及超低功耗,使其成为CNN 实现平台的理想选择。

FPGA 的可重配置特性适合于变化的神经网络网络结构。

因此,许多研究人员已经研究了使用FPGA 实现CNN 加速的方法[3]。

本文参考了Google 提出的轻量级网络MobileNet 结构[4],并通过并行处理和流水线结构在FPGA 上设计了高速CNN 系统,并将其与CPU 和GPU 的实现进行了比较。

1卷积神经网络加速器的设计研究1.1卷积神经网络的介绍在深度学习领域中,卷积神经网络占有着非常重要的地位,它的图像识别准确率接近甚至高于人类的识别水平。

卷积神经网络是同时具有层次结构性和局部连通性的人工神经网络[5]。

卷积神经网络的结构都是类似的,它们采用前向网络模型结构,节点使用神经元来实现分层连接。

并且,相邻层之间的节点是在局部区域内相连接,同一层中的一些神经元节点之间是共享连接权基于FPGA 的卷积神经网络并行加速器设计王婷,陈斌岳,张福海(南开大学电子信息与光学工程学院,天津300350)摘要:近年来,卷积神经网络在许多领域中发挥着越来越重要的作用,然而功耗和速度是限制其应用的主要因素。

为了克服其限制因素,设计一种基于FPGA 平台的卷积神经网络并行加速器,以Ultra96-V2为实验开发平台,而且卷积神经网络计算IP 核的设计实现采用了高级设计综合工具,使用Vivado 开发工具完成了基于FPGA 的卷积神经网络加速器系统设计实现。

如何选择高效的深度学习硬件?剖析GPU、FPGA、ASIC和DSP 深度学习最近取得的成功势不可挡:从图像分类和语音识别到图片标注、理解视觉场景、视频概述、语言翻译、绘画,甚至是生成图像、语音、声音和音乐!随着我们的家变得越来越智能,你会发现许多设备都会需要连续地使用深度学习应用、收集和处理数据。

所以我们需要新的硬件,一个比Intel Xeon 所驱动的服务器更加高效的硬件。

一个英特尔服务器CPU 可能会消耗100-150 瓦功率并需要一个有着冷却装置的超大系统来支持其性能的正常发挥。

还有哪些其它的选择?图形处理器、GPU 现场可编程的逻辑器件、FPGA(现场可编程门阵列/Field-Programmable Gate Array)定制芯片、特殊应用型集成电路、ASIC、[**芯片**](http://pubads.g.doubleclick/gampad/clk?id=132505090">GPUGPU 最早是为生成基于多边形网络的计算机图形而设计的。

在最近几年,由于近来计算机游戏和图形引擎领域的需求和复杂度需要,GPU 积累了强大的处理性能。

英伟达是GPU 领域的领军者,能生产有数千个内核的处理器,这些内核的设计工作效率可以达到100%。

实际上这些处理器也非常适用于运行神经网络和矩阵乘法方面的计算。

注意,矩阵向量的乘法运算被认为是「尴尬的并行(embarrassingly parallel)」,因为它可以通过简单的算法扩展被并行化(它们缺少分支因而可以避免缓存信息丢失)。

Titan X 是训练深度学习模型的一个最得力的助手。

它拥有3500 多个内核,每秒能够执行超过11 万亿次浮点运算。

更多测试性能方面的信息请参考这里(https://github/soumith/convnet-benchmarks)。

由于GPU 的超多核(~3500 个,对比Intel Xeon 的16 个/ Xeon Phi 的32 个),英特尔的CPU 和英伟达的GPU 之间的竞争助长了后者的发展,使其GPU 比CPU 在时钟频率快2~3 倍。

Zynq UltraScale+ MPSoCsA comprehensive device family, Zynq UltraScale+ MPSoCs offer single-chip, all programmable,heterogeneous multiprocessors that provide designers with software, hardware, interconnect, power, security, and I/O programmability. The range of devices in the Zynq UltraScale+MPSoC family allows designers to target cost-sensitive as well as high-performance applications from a single platform using industry-standard tools. While each Zynq UltraScale+MPSoC contains the same PS, the PL, Video hard blocks, and I/O resources vary between the devices.•Automotive: Driver assistance, driver information, and infotainment•Wireless Communications: Support for multiple spectral bands and smart antennas•Wired Communications: Multiple wired communications standards and context-aware network services •Data Centers: Software Defined Networks (SDN), data pre-processing, and analytics •Smarter Vision: Evolving video-processing algorithms, object detection, and analytics•Connected Control/M2M: Flexible/adaptable manufacturing, factory throughput, quality, and safetyThe UltraScale MPSoC architecture provides processor scalability from 32 to 64 bits with support for virtualization, the combination of soft and hard engines for real-time control, graphics/video processing, waveform and packet processing, next-generation interconnect and memory, advanced powermanagement, and technology enhancements that deliver multi-level security, safety, and reliability. Xilinx offers a large number of soft IP for the Zynq UltraScale+MPSoC family. Stand-alone and Linux device drivers are available for the peripherals in the PS and the PL. Xilinx’s Vivado® Design Suite, SDK™, and PetaLinux development environments enable rapid product development for software, hardware, and systems engineers. The Arm-based PS also brings a broad range of third-party tools and IP providers in combination with Xilinx's existing PL ecosystem.The Zynq UltraScale+MPSoC family delivers unprecedented processing, I/O, and memory bandwidth in the form of an optimized mix of heterogeneous processing engines embedded in a next-generation, high-performance, on-chip interconnect with appropriate on-chip memory subsystems. Theheterogeneous processing and programmable engines, which are optimized for different application tasks, enable the Zynq UltraScale+ MPSoCs to deliver the extensive performance and efficiency required to address next-generation smarter systems while retaining backwards compatibility with the original Zynq-7000 All Programmable SoC family. The UltraScale MPSoC architecture also incorporates multiple levels of security, increased safety, and advanced power management, which are critical requirements of next-generation smarter systems. Xilinx’s embedded UltraFast™ design methodology fully exploits the Table 7:Zynq UltraScale+ MPSoC Device FeaturesCG DevicesEG DevicesEV DevicesAPU Dual-core Arm Cortex-A53Quad-core Arm Cortex-A53Quad-core Arm Cortex-A53RPU Dual-core Arm Cortex-R5Dual-core Arm Cortex-R5Dual-core Arm Cortex-R5GPU –Mali-400MP2Mali-400MP2VCU––H.264/H.265找FPGA 和CPLD 可编程逻辑器件,上深圳宇航军工半导体有限公司ASIC-class capabilities afforded by the UltraScale MPSoC architecture while supporting rapid system development.The inclusion of an application processor enables high-level operating system support, e.g., Linux. Other standard operating systems used with the Cortex-A53 processor are also available for theZynq UltraScale+MPSoC family. The PS and the PL are on separate power domains, enabling users to power down the PL for power management if required. The processors in the PS always boot first, allowing a software centric approach for PL configuration. PL configuration is managed by software running on the CPU, so it boots similar to an ASSP.Programmable LogicThis section covers the information about blocks in the Programmable Logic (PL).Device LayoutUltraScale architecture-based devices are arranged in a column-and-grid layout. Columns of resources are combined in different ratios to provide the optimum capability for the device density, target market or application, and device cost. At the core of UltraScale+MPSoCs is the processing system that displaces some of the full or partial columns of programmable logic resources. Figure 1 shows a device-level view with resources grouped together. For simplicity, certain resources such as the processing system, integrated blocks for PCIe, configuration logic, and System Monitor are not shown.Resources within the device are divided into segmented clock regions. The height of a clock region is 60CLBs. A bank of 52 I/Os, 24 DSP slices, 12 block RAMs, or 4 transceiver channels also matches the height of a clock region. The width of a clock region is essentially the same in all cases, regardless of device size or the mix of resources in the region, enabling repeatable timing results. Each segmented clock region contains vertical and horizontal clockrouting that span its full height and width. These horizontal and vertical clock routes can be segmented at the clock region boundary to provide a flexible, high-performance, low-power clock distribution architecture. Figure 2 is a representation of a device divided into regions.Figure 1:Device with Columnar ResourcesFigure 2:Column-Based Device Divided into Clock RegionsHigh-Speed Serial TransceiversUltra-fast serial data transmission between devices on the same PCB, over backplanes, and across even longer distances is becoming increasingly important for scaling to 100Gb/s and 400Gb/s line cards. Specialized dedicated on-chip circuitry and differential I/O capable of coping with the signal integrity issues are required at these high data rates.Three types of transceivers are used in Zynq UltraScale+ MPSoCs: GTH, GTY, and PS-GTR. All transceivers are arranged in groups of four, known as a transceiver Quad. Each serial transceiver is a combined transmitter and receiver. Table 10 compares the available transceivers.The following information in this section pertains to the GTH and GTY only.The serial transmitter and receiver are independent circuits that use an advanced phase-locked loop (PLL) architecture to multiply the reference frequency input by certain programmable numbers between 4 and 25 to become the bit-serial data clock. Each transceiver has a large number of user-definable features and parameters. All of these can be defined during device configuration, and many can also be modified during operation.Table 10:Transceiver InformationZynq UltraScale+ MPSoCsType PS-GTRGTH GTY Qty40–440–28Max. Data Rate 6.0Gb/s 16.3Gb/s 32.75Gb/s Min. Data Rate1.25Gb/s0.5Gb/s0.5Gb/sApplications•PCIe Gen2•USB•Ethernet•Backplane •HMC•100G+Optics •Chip-to-Chip •25G+Backplane •HMC。

符合OpenGL标准的国产化显卡研究与实现黎小玉;田泽;郭亮;马城城【摘要】我国现有显卡设计基本依赖国外产品,没有统一的软硬件接口,导致显示性能不高、显示软件升级和移植困难。

OpenGL( Open Graphics Library)以其强大的功能、性能及良好的兼容性成为业界广为使用的图形API接口。

文中基于对OpenGL标准的深入分析,介绍了一款基于OpenGL 1.3标准的显卡设计与实现方案。

该显卡与主机采用PCI总线互联,核心图形处理功能基于FPGA,采用专用硬件处理逻辑与软件结合的方式实现,可完成二维/三维硬件加速功能。

经过测试和验证,该显卡可替代以ATI M9-CSP64芯片为核心的显卡。

%In domestic market,the design of the existing video card is basically dependent on foreign products,there is no unified hardware and software interfaces,which makes display performance is not high,the display software upgrading and migration difficult. OpenGL is widely used graphics API interface with its powerful functions,performance and good compatibility. Based on the analysis of OpenGL standard,introduce a scheme of design and implementation of a video card based on OpenGL1. 3 standard. The card is connected to a host with PCI bus,the key graphic function is based on FPGA,in the way of combining the special hardware processing logic and software,to be completed 2D/3D hardware acceleration. After testing and verification,the card can replace the video card used ATI M9-CSP64 as its core.【期刊名称】《计算机技术与发展》【年(卷),期】2014(000)005【总页数】4页(P173-175,179)【关键词】显卡;OpenGL;FPGA【作者】黎小玉;田泽;郭亮;马城城【作者单位】中国航空计算技术研究所,陕西西安 710119;中国航空计算技术研究所,陕西西安 710119;中国航空计算技术研究所,陕西西安 710119;中国航空计算技术研究所,陕西西安 710119【正文语种】中文【中图分类】TP39显卡又称为视频卡、视频适配器、图形卡等,作为计算机系统的重要组成部件,是主机与显示器之间连接的“桥梁”,负责将CPU处理后的数据信号转化为模拟信号被人们识别[1]。

Highly efficient programing environment for handling AI workloadsTom Michiels, System ArchitectSynopsys ARC®Processor Summit 2022Agenda•The AI Programming Challenge •Optimizations For Programming AI-Enabled SoCs •Quantifying The BenefitsThe AI Programing ChallengeCNNRNN/LSTMTransformersRecommendersVision, Lidar, Audio, SpeechSpeech, Audio, Action RecognitionNLP , Speech,VisionCommerce, RecommendationsPopular & Emerging Neural Networks Are Still EvolvingRecurrent Neural Networks process sequential data like audio or speech streamsConvolutional Neural Networks process uncompressed imagesUses parallelism and focused attention onrelevant portions of imageA woman throwing a frisbee in the parkRecommender system predicts future preference of a set of items for a userMust “future -proof” your software to handle new ML graphsCPU, GPU, DSPs, NPUs, AI Accelerators…AI Software Runs On a Spectrum Of Hardware TypesHardware PerformanceAreaEfficiencyPowerEfficiencyFlexibilityTypical ProgrammingModelCPU C/C++ code GPU OpenCL or CUDA FPGA Vendor Specific DSP C/C++ or OpenCL C NPU Vendor Specific Accelerator Hardwired or Special SDK Ideally, your NN’s will take advantage of any AI-enabled hardwareWide Variety Of Performance For AI Edge Devices•Driver monitoring system•Surveillance•Facial recognition •Digital still cameras •High End Gaming •Augmented reality •Mid-end smartphones•Facial recognition1 to 10 TOPS•ADAS Front Cameras •ADAS LiDAR/Radar •High end surveillance •High-end smartphones •DTV •HPC•Microservers (inference)•Data center (inference)10 to 1000+ TOPS•Robotics / Drones•Automotive Powertrain •Games/toys•Audio / Voice control •Facial detection100 GOPS to 1 TOPS•AIoT•Human activity recognition<100 GOPS Same programming environment to serve multiple domainsDeep Learning Performance Outpacing Memory•Moore’s Law: CPUperformance outpacingmemory access speed•GPUs initiated DeepLearning in 2012, wideningthe gap•Deep Learning acceleratorsoutpacing GPUs•Goal: reduce data movement–Innovative heterogeneousmemory architecturesrequired–From on-chip memorycompilers to high bandwidthHBM2 Limited memory bandwidth requires optimized data movementsCompeting Machine Learning FrameworksLack of Programming Model Standardization for AI AlgorithmsProgramming model should support all popular frameworks1.Quantization2.Multi-level Layer Fusion and Multi-level Tiling3.Feature Map Compression/Decompression4.Structured Sparsity5.Featuremap partitioning111131111111111111111151111111170111111001111111671415fraction (7 bit)exponent (8 bit)sign 1111111111011100fraction (10 bit)exp (5 bit)sign09141510011111100111111122233031fraction (23 bit)exponent (8 bit)sign111~~NN Applications Use Wide Range Of Data RepresentationsFP16BF16INT16INT8INT4FP3211011100fraction (2 bit)exp (5 bit)sign 01672FP8•FP8 has more traction for training than inference •FP16 & BF16 are NOT needed for accuracy overINT8/16 –they make the transition from GPU easier, avoids having to retrain models•INT8standard for neural network object detection •INT16provides accuracy ‘insurance’ for radar and super resolution (at reduced performance)•FP32 typical format used in GPUs for NN model training•INT4can save bandwidth; not very popular yetMixed Precision Quantization Enables Optimized Accuracy with Minimum Bandwidth ImpactLayer 18bit/8bit Optimize Accuracy with Minimum BandwidthLayer 28bit/8bitLayer 38bit/8bit Layer 48bit/8bitLayer 18bit/8bit Layer 216b/8bitLayer 38bit/8bit Layer 48bit/8bitAccuracy ReportInitial 8bit Quantized ModelMixed-Precision Quantized Model•Multi-level Layer Fusion–Merging multiple folded layers into single primitives reduces feature map bandwidth –Merged layers can be fused into layers groups and tiled, taking advantage of L1 and L2 memories•Coefficient Pruning and Compression–Coefficients with a zero value are skipped/counted, a compressed coefficient bitstream is created offline –Compression ratio can be increased through pruning and retraining•Feature Map Compression–Lossless runtime compression and decompression of feature maps to external memory –Approx. 40% feature-map bandwidth reduction, exploiting sparsity•Layer, Frame based and Feature Map Partitioning with DMA Broadcasting–Broadcast of common data across slices to minimize bandwidth of coefficients and feature-maps loadingTechniques for Minimizes Bandwidth Requirements1x1 conv 3x3 DW conv 1x1 conv+64BW = 11x1 conv 3x3 DW conv 1x1 conv+Fused Layers64BW = 0.161x1 conv 3x3 DW conv 1x1 conv Fused Layers+64BW = 0.33256256646464Multi-level Layer Fusion MobileNet v1/v2Feature Map Partitioning / DMA BroadcastingNPX6…NN Accelerator Slice 11K/4K MAC ActivationControlNN Accelerator Slice 21K/4K MAC Activatio n ControlNN Accelerator Slice N 1K/4K MACActivationControlL2 Control Core L2DMAAdvanced Data Bandwidth Reduction TechniquesMulti-level Layer Fusion and Multi-level TilingNN AcceleratorNN Core1L1NN Core2L1NN Core NL1On-chip Shared Mem (L2)DDR (L3)…C o n 3x 3d wB N /R e L UC o n v 1x 1B N /R e L UC o n v 1x 1B N /R e L U+C o n 3x 3d wB N /R e L UC o n v 1x 1B N /R e L UC o n v 1x 1B N /R e L U+C o n 3x 3d wB N /R e L UC o n v 1x 1B N /R e L UC o n v 1x 1B N /R e L U+•Convolutions, Pooling and Activations: merged layers•Merged layers can be fused into layer groups•Intermediate feature maps within a layer group are tiled to fit in the L1 Closely Coupled Memories of the DNN cores •Layer groups can be fused into segments•Intermediate feature maps within a segment are tiled to fit in the L2 On-chip Shared Memory•The output of a segment may be too large (>10MB) to fit in L2 On-chip Shared Memory and is spilled to L3 DDR•Coefficient Pruning–Coefficients with a zero value are skipped/counted–Decompression done between local VM memory and NN datapath registers–Offline coefficient pruning (with retraining) can increase proportion of zero coefficients–Support of structured and unstructured sparsity•Feature map compression/decompression–Runtime compression and decompression –NN core DMA supports HW compression mode –Bandwidth reduction of 40~45% measured typicallyData Compression/DecompressionNN Accelerator CoreMACsVM: L1 Local SRAMFeature-map Coefficients Storage StorageDMAExternal AXI Bus InterfaceAXI I/F per CoreRegisters decompressF-map Compression and DecompressionCoefficient decompressionFeature-map de/compress•Sparsity takes advantage of a matrix of numbers that includes many zeros or values that will not significantly impact a calculation •Can exploits sparsity in coefficients–Flexible use of sparsity in coefficient vectors in channel dimension–Effective speedup of 1.4X~1.8X with almost no accuracy loss•Doubles the effective MACs on applicable layers •Requires pruning and retraining–No accuracy loss for key model families:e.g. ResNet, ResNext, Densenet, Bert, GNMT –Other models may have accuracy vs. performance tradeoffsStructured Sparsity Can Improve Performance 2XCombination of 2 sparse 2:4groups= Zero value = Non-zero valueNPU…NN Accelerator Core 11K/4K MAC L1 MemDMAActivationControlNN Accelerator Core 21K/4K MAC L1 MemDMAActivationControlNN Accelerator Core N 1K/4K MAC L1 MemDMAActivationControlLatency Reduction via Feature-map partitioningSplit each layer over multiple cores•Higher throughput –up to N X•Lower latency –up to N X –due to parallel processing of a layer C o n v 3x 3L2 Control Core L2 SharedDMANPUSpatial partitioning: Reuse weights across cores through a broadcast DMA…Weights / CoefficientsBroadcast to DMAsInput features…NN Core 11K/4K MACL1 MemDMAActivationControlNN Core 21K/4K MACL1 MemDMAActivationControlNN Core N1K/4K MACL1 MemActivationControlL2Control Core L2 SharedDMA DMANPUChannel partitioning: Reuse features across cores through a broadcast DMABroadcast to DMAs……Weights / CoefficientsInput features…NN Core 11K/4K MACL1 MemDMAActivationControlNN Core 21K/4K MACL1 MemDMAActivationControlNN Core N1K/4K MACL1 MemActivationControlDMAL2Control Core L2 SharedDMAQuantifying the Benefits•Scalable NPX6 architecture–1 to 24 core NPU up to 96K MACS (440 TOPS*)–Multi-NPU support (up to eight for 3500 TOPS*)•Trusted software tools scale with the architecture•Convolution accelerator –MAC utilizationimprovements with emphasis on modern network structures•Generic Tensor accelerator –Flexible Activation & support of Tensor Operator Set Architecture (TOSA)•Memory Hierarchy –high bandwidth L1 and L2 memories•DMA broadcast lowers external memorybandwidth requirements and improves latencySynopsys Introduces ARC NPX6 NPU and MetaWare MXMetaWare MX Development ToolkitRuntimes & LibrariesCompilers & Debugger NN SDKSimulatorsVirtualPlatforms SDKSynopsys ARC NPX6 NPU IP4K MAC to 96K MAC ConfigurationsL2 Shared MemoryHigh-bandwidth, low latency interconnect with DMA BroadcastStreaming Transfer UnitsL2 Controller with MMU Debug Trace… C o r e 24C o r e 2C o r e 1DMAConvolution Accelerator 4K MAC L1 MemoryTensor AcceleratorL1 Controller with MMU T e n s o r F P U•Integrated toolkit providesoptimizing compilers, debugger, libraries and a simulator fordevelopment on ARC processors •Includes Vector DSP and Linear Algebra Libraries (BLAS/LAPACK) and MATLAB Plug-In for Model-Based Design Environment •MetaWare Neural Network SDK for enabling and optimizing Machine Learning and inference applications•Includes simulation platforms for early software development and architectural exploration with MetaWare Virtual Platforms SDK •Development of Computer Vision for pre-& post-processing eased Modular Toolkit Supports Control, DSP , Vision and ML Software DevelopmentCompiler toolchain, Debugger & IDEDSP and Linear Algebra Libraries nSIM NCAM Simulator Neural Network SDK MetaWare MXSPEED RuntimeMATLAB Plug-In Virtual Platforms SDKVision SDKDesignWare® ARC® MetaWare MX Development ToolkitBenchmark Performance vs. L2 CSM size and DDR BandwidthResult for selected NPX6-32K config –without structured sparsity10020030040050060070080050100150200250300F P SDDR BW (GB/s)scaled_yolo5(960x544) on NPU32K(384 KB)16 MB CSM 8 MB CSM 4 MB CSM 2 MB CSM no CSM•NPX6 configuration: 8 NN cores * 4096 MACs per core •NN core internal memory (L1): 384 KB per NN core •Cluster Shared Memory (L2): 0 to 16 MB•Ext. DRAM bandwidth (L3): 16, 32, 64, 128, 256 GB/s •8 bit data02040608010012014016018050100150200250300A v g . u s e d D R A MB W (G B /s )DDR BW (GB/s)scaled_yolo5(960x544) on NPU32K(384 KB)16 MB CSM 8 MB CSM 4 MB CSM 2 MB CSM no CSMPerformance Gains Obtained with Structured SparsityNPX6-4K NPX6-16K NPX6-64KGraph% FPS improvementWith Structured Sparsity% FPS improvementWith Structured Sparsity% FPS improvementWith Structured SparsityInception v3151%142%124% Inception v3 FHD148%148%148% ResNet-50 v1.5146%147%128% ResNet-50 v1.5 FHD142%147%147% MobileNet v2124%133%114% MobileNet v2 FHD120%121%117% Yolo v3152%171%165% Yolo v3 FHD165%164%168% SSD-ResNet34167%171%171% SSD-MobileNet151%138%115% DeepLab v3127%129%128% EDSR200%191%190% SRGAN176%173%171% BERT_large128%135%147% BERT_large (batch=4)128%163%166% Vit_B_16144%128%154% Vit_L_16132%145%149% Vit_H_16129%145%144% swin_tiny148%148%134% swin_small156%158%136% swin_base153%163%143%•Helps solve the challenge of hardwaredependency related to AImodels•Open format to representboth deep learning andtraditional models•Defines a common set ofoperators and file format•AI developers can usemodels with a variety offrameworks, tools,runtimes, and compilers•Enables deploying sameAI models to multipleHW-accelerated targetsSource: Microsoftto the RescueIndustry Standard Runtimes•MetaWare NN Compiler integrates with standard frameworks•Automatic mapping to NPX6 and VPX5 vector DSP with no manual optimization required–User-driven optimization options: e.g. Latency, throughput, bandwidth•Generated code can run on multiple development platforms–Fast Performance Models (FPM)–Zebu H/W Emulator–HAPS FPGA boardSupport for Different Programming FrameworksMetaWare NN Compiler Execution IR MetaWare NN RuntimeFutureML frameworksNPX6NPUVPX5xN DSPARC Processor IPState-Of-The-Art System Level Modeling And AnalysisBenchmarking & ProfilingPower profilingSoftware DevelopmentArchitecture DesignNP core NP l a t f o r m A r c h i t e c t M o d e lNP core 1-Fast, functional, execution -Cycle-based NN accel. timing -Cycle-based DMA timingN N A c c e l e r a t o rC o n t r o l C o r e-Fast, functional execution-Cycle-based DMA modelF a s t T i m e d I n t e r f a c eNPX6 Fast Performance Model•Fast Performance Model–Fast cycle-based Performance Model of NPX6 (and VPX5 cores)–Integrated Platform Architect simulation environments•Virtualizer Virtual Prototyping–VDK (Virtualizer development Kit for early Software Development Platform)•ZeBu Emulation–Accurate performance and power modeling•HAPS Prototyping–NPX6 mapped to HAPS board provides cycle accurate performance for benchmarking and software developmentNPX6ZeBuH/W EmulatorHAPS-100®FPGA BoardSummary•AI Programming is a challenge amid evolving Neural Networks, absence of a standard programing model and the wide spectrum of HW types. A key challenges is the limited memory bandwidth•Synopsys advanced optimizations for AI includes Mixed Precision Quantization to increase accuracy, Data Bandwidth Reduction techniques like multi-level tiling, Feature Map Partitioning to minimize bandwidth requirements, and Structured Sparsity utilization•Synopsys MetaWare MX Development Toolkit supports different programming frameworks, different HW targets, is extensible, and includes state-of-the-art system level modelingThank You。

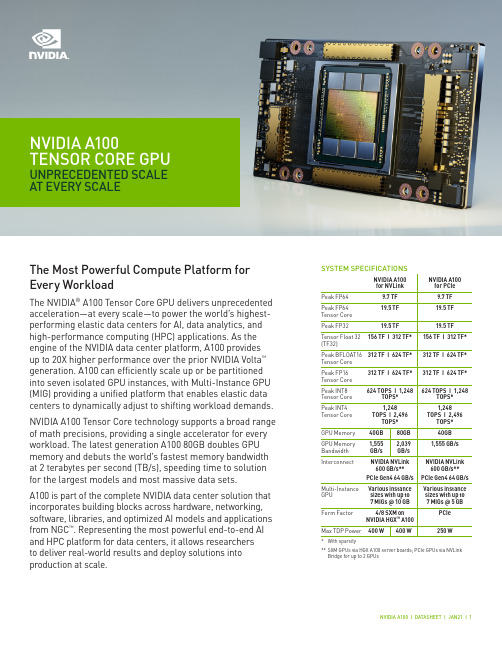

SYSTEM SPECIFICATIONSNVIDIA A100 for NVLinkNVIDIA A100 for PCIePeak FP649.7 TF 9.7 TF Peak FP64 Tensor Core 19.5 TF 19.5 TF Peak FP3219.5 TF 19.5 TF Tensor Float 32 (TF32)156 TF | 312 TF*156 TF | 312 TF*Peak BFLOAT16 Tensor Core 312 TF | 624 TF*312 TF | 624 TF*Peak FP16 Tensor Core 312 TF | 624 TF*312 TF | 624 TF*Peak INT8 Tensor Core 624 TOPS | 1,248 TOPS*624 TOPS | 1,248TOPS*Peak INT4 Tensor Core 1,248TOPS | 2,496TOPS*1,248TOPS | 2,496TOPS*GPU Memory 40GB 80GB 40GB GPU Memory Bandwidth 1,555 GB/s2,039 GB/s1,555 GB/s InterconnectNVIDIA NVLink 600 GB/s**PCIe Gen4 64 GB/s NVIDIA NVLink 600 GB/s**PCIe Gen4 64 GB/s Multi-Instance GPU Various instance sizes with up to 7 MIGs @ 10 GB Various instance sizes with up to 7 MIGs @ 5 GBForm Factor 4/8 SXM on NVIDIA HGX ™ A100PCIe Max TDP Power400 W400 W250 W* With sparsity** SXM GPUs via HGX A100 server boards; PCIe GPUs via NVLink Bridge for up to 2 GPUsNVIDIA A100TENSOR CORE GPUUNPRECEDENTED SCALE AT EVERY SCALEThe Most Powerful Compute Platform for Every WorkloadThe NVIDIA ® A100 Tensor Core GPU delivers unprecedented acceleration—at every scale—to power the world’s highest-performing elastic data centers for AI, data analytics, and high-performance computing (HPC) applications. As the engine of the NVIDIA data center platform, A100 provides up to 20X higher performance over the prior NVIDIA Volta ™ generation. A100 can efficiently scale up or be partitioned into seven isolated GPU instances, with Multi-Instance GPU (MIG) providing a unified platform that enables elastic data centers to dynamically adjust to shifting workload demands. NVIDIA A100 Tensor Core technology supports a broad range of math precisions, providing a single accelerator for every workload. The latest generation A100 80GB doubles GPU memory and debuts the world’s fastest memory bandwidth at 2 terabytes per second (TB/s), speeding time to solution for the largest models and most massive data sets. A100 is part of the complete NVIDIA data center solution that incorporates building blocks across hardware, networking, software, libraries, and optimized AI models and applications from NGC ™. Representing the most powerful end-to-end AI and HPC platform for data centers, it allows researchers to deliver real-world results and deploy solutions into production at scale.1X2X3XUp to 3X Higher AI Training on Largest Models DLRM TrainingUp to 249X Higher AI Inference Performance over CPUs BERT-LARGE InferenceGroundbreaking InnovationsNEXT-GENERATION NVLINKNVIDIA NVLink in A100 delivers 2X higher throughput compared to the previous generation. When combined with NVIDIA NVSwitch ™,up to 16 A100 GPUs can be interconnected at up to 600 gigabytes per second (GB/ sec), unleashing the highest application performance possible on a single server . NVLink is available in A100 SXM GPUs via HGX A100 server boards and in PCIe GPUs via an NVLink Bridge for up to 2 GPUs.efficiency at 95%. A100 delivers 1.7X highermemory bandwidth over the previous generation.to breakthrough acceleration for all their applications, and IT administrators can offer right-sized GPU acceleration for every job, optimizing utilization and expanding access to every user and application.STRUCTURAL SPARSITYAI networks have millions to billions of parameters. Not all of these parameters are needed for accurate predictions, and somecan be converted to zeros, making the models “sparse” without compromising accuracy. Tensor Cores in A100 can provide up to 2X higher performance for sparse models. While the sparsity feature more readily benefits AI inference, it can also improve the performance of model training.01X2XUp to 1.25X Higher AI Inference Performance over A100 40GB RNN-T Inference: Single StreamTime to Solution - Relative PerformanceCPU OnlyV100 32GBA100 40GBA100 80GBBig data analytics benchmark | 30 analytical retail queries, ETL, ML, NLP on 10TB dataset | CPU: Intel Xeon Gold 6252 2.10 GHz, Hadoop | V100 32GB, RAPIDS/Dask | A100 40GB and A100 80GB, RAPIDS/Dask/BlazingSQLUp to 1.8X Higher Performance for HPC Applications Quantum Espresso2017P1002016201820192020Throughput - Relative PerformanceGeometric mean of application speedups vs. P100: Benchmark application: Amber [PME-Cellulose_NVE], Chroma [szscl21_24_128], GROMACS [ADH Dodec], MILC [Apex Medium], NAMD [stmv_nve_cuda], PyTorch (BERT-Large Fine Tuner], Quantum Espresso [AUSURF112-jR]; Random Forest FP32 [make_blobs (160000 x 64: 10)], TensorFlow [ResNet-50], VASP 6 [Si Huge] | GPU node with dual-socket CPUs with 4x NVIDIA P100, V100, or A100 GPUs.Incredible Performance Across Workloads© 2021 NVIDIA Corporation. All rights reserved. NVIDIA, the NVIDIA logo, CUDA, DGX, HGX, HGX A100, NVLink, NVSwitch, OpenACC, TensorRT, To learn more about the NVIDIA A100 Tensor Core GPU, visit /a100The NVIDIA A100 Tensor Core GPU is the flagship product of the NVIDIA data center platform for deep learning, HPC, and data analytics. The platform accelerates over 1,800 applications, including every major deep learning framework. A100 is available everywhere, from desktops to servers to cloud services, delivering both dramatic performance gains and cost-saving opportunities.。