模拟集成电路设计实验教程(王向展,宁宁,于奇)思维导图

- 格式:xmin

- 大小:4.64 KB

- 文档页数:1

实验报告课程名称:集成电路原理实验名称:模拟集成电路版图设计与验证小组成员:实验地点:科技实验大楼606实验时间:2017年6月19日2017年6月19日微电子与固体电子学院一、实验名称:模拟集成电路版图设计与验证二、实验学时:4三、实验原理1、电路设计与仿真实验2内容,根据电路的指标和工作条件,然后通过模拟计算,决定电路中各器件的参数(包括电参数、几何参数等),EDA软件进行模拟仿真。

2、工艺设计根据电路特点结合所给的工艺,再按电路中各器件的参数要求,确定满足这些参数的工艺参数、工艺流程和工艺条件。

3、版图设计按电路设计和确定的工艺流程,把电路中有源器件、阻容元件及互连以一定的规则布置在Candence下的版图编辑器内。

并优化版图结构。

四、实验目的本实验是基于微电子技术应用背景和《集成电路原理》课程设置及其特点而设置,为IC设计性实验。

其目的在于:1、根据实验任务要求,综合运用课程所学知识自主完成相应的模拟集成电路版图设计,掌握基本的IC版图布局布线技巧。

2、学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行版图的的设计与验证。

通过该实验,使学生掌握CMOS模拟IC版图设计的流程,加深对课程知识的感性认识,增强学生的设计与综合分析能力。

五、实验内容1、UNIX操作系统常用命令的使用,Cadence EDA仿真环境的调用。

2、根据实验2所得参数,自主完成版图设计,并掌握布局布线的基本技巧。

3、整理版图生成文件,总结、撰写并提交实验报告。

六、实验仪器设备(1)工作站或微机终端一台(2)EDA仿真软件1套七、实验步骤1、根据实验指导书掌握Cadence EDA仿真环境的调用。

熟悉版图编辑器Layout Editor的使用。

了解基本的布局布线方法及元器件的画法。

2、根据实验2所计算验证的两级共源CMOS运放的元器件参数如表1所示,在版图设计器里画出相应的元器件,对V+、V-、V out、V DD、GND的压焊点位置合理化放置,通过金属画线将各个元器件按实验2的电路图合理连接,避免跳线。

模拟集成电路设计三本经典教材学习经验我想说的是三本经典教材。

没有看完,应该说根本不能入门,现在我想谈谈对三本教材的学习经验论坛上有很多大虾的心得。

我还想谈谈!我是从艾伦的开始,可以说艾伦的书是模拟CMOS IC 设计的最基本的书,它完全是从集成电路的角度,而且和工艺结合的很紧,好像和分立的电路完全分开,我觉得艾伦的书最经典的分析在于大信号的分析,让你了解集成电路的设计要考虑的问题,而不是对实际电路的具体分析,此书更好的是书中的电路直接来自工程实践的,从设计的角度谈的很多,很好。

特别是5,6,7。

但是如果基础不够,那刚开始时有难度!那就再看GRAY 的,此书是三本中,最基本的,是从分立到集成的桥梁,看艾伦的如果某些地方有难度,特别是级零点,小信号的分析(刚从分立的模拟电路设计转入集成电路设计的朋友,喜欢从小信号来分析电路参数的),强烈推荐GRAY(理论大师,讲解的特别清晰、详细).以上两本书看完了后,你可能跃跃欲试,想设计个电路看看,然后电路结构想改进,电路的拓扑结构越来越难,小信号的分析有难度的,大信号也不能一目了然了,遇到了瓶颈了,怎么办?看拉扎维的(有网友说拉是用艺术的眼光来设计电路的)此书从大局的角度来分析电路的。

三本书后,基本上你算入门了,可以跟大牛做项目了,然后多看IEEE的资料,(基准源,运放,比较器)是要继续训练的,(有位大侠谈过了,看帖子,模拟电路的四重境界--文章结尾有)。

然后再从CMOS 到BICMOS等等!!我再推荐两本好书(专业性更强)introducation to cmos op-amps and comparators;design of analogy chip本人刚刚学习,说得不好,不专业,还请各位朋友多多提醒模拟电路的四重境界复旦攻读微电子专业模拟芯片设计方向研究生开始到现在五年工作经验,已经整整八年了,其间聆听过很多国内外专家的指点。

最近,应朋友之邀,写一点心得体会和大家共享。

因两三极管基极对地电位相等,差分放大电路v i1v i2线性放大电路v o 电路完全对称的理想情况:)(21i i VD o v v A v −=差模电压增益差模成分id v 放大两个输入信号之差输入信号的共模成分)(2121i i ic v v v +=差模信号:是指在两个输入端加幅度相等,极性相反的信号。

共模信号:是指在两个输入端加幅度相等,极性相同的信号。

2010-3-31差分放大电路的组成差分放大电路是由两个互为发射极耦合的共射极放大电路组成,电路参数完全对称。

差分放大电路的静态和动态计算方法与基本放大电路基本相同。

时,021==i i v v 静态分析动态分析(增益,输入、输出电阻)当输入信号为零时,即0=2/21C C CC CE 0C 21=−=+−===C C o BEC C v v v V R I V V I I i i 由于电路完全对称。

差模信号共模信号cCQ c c CQ c i I i i I i −=+=2211,cCQ c c CQ c i I i i I i +=+=2211,电压增益越小,放大电路的性能越好(3)共模输出电阻单端输出时,c o R R =co 2R R =(2)共模输入电阻(相当于两部分并联)]2)1([21o be ic r r R β++=双端输出时,双电源差分放大电路差分放大电路的静态计算将电路中信号源短路即可获得计算静态的直流通路。

已知:β=100,V BE =0.6VmAV I R e EE E 6.020122==≈()AI IE Bμβ61006.01=≈+=V V BE C C CCCE R I V V 6≈+−=01V U 86.01=Δ。

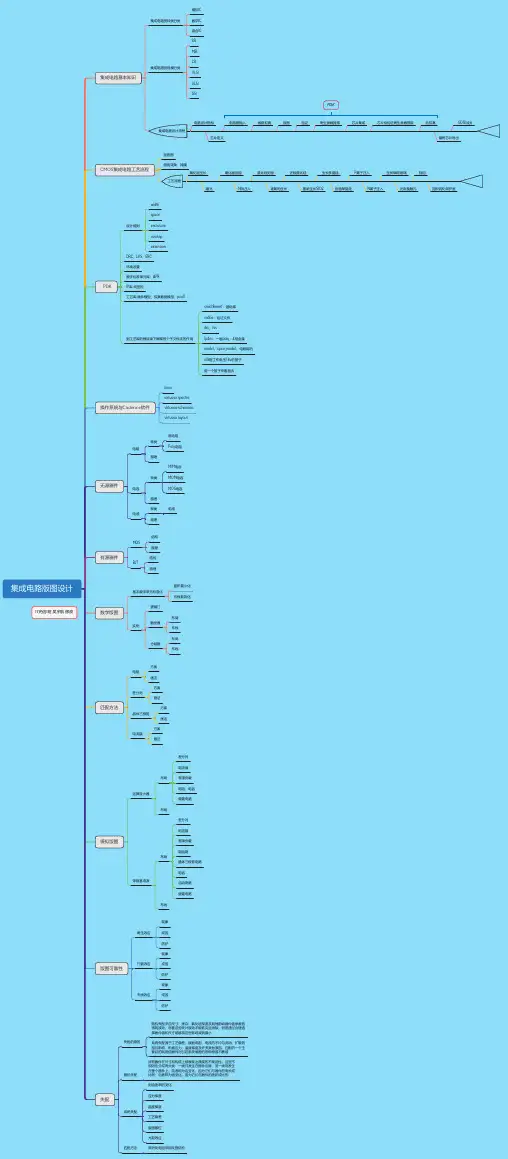

集成电路版图设计集成电路基本知识集成电路按种类分类模拟IC数字IC混合IC集成电路按规模分类S SIM SIL SIV LSIU LSIG SI集成电路设计流程电路设计指标芯片定义电路图输入线路拟真版图验证寄生参数提取芯片集成芯片级验证寄生参数提取后拟真最终芯片导出G DSII流片P DKC MOS集成电路工艺流程剖面图俯视效果,掩膜工艺流程氧化层生长曝光氧化层刻蚀N阱注入氮化硅刻蚀场氧的生长去除氮化硅重新生长SIO2生长多晶硅刻蚀单晶硅P离子注入N离子注入生长磷硅玻璃光刻接触孔刻铝淀积钝化保护层PDK设计规则w idths pacee nclosureo verlape xtensionD RC、LVS、ERC环境设置数字标准单元库:APRI P库:成型的工艺库:器件模型、拟真数据模型、pcell到工艺库的根目录下解释各个子文件夹的作用s mic18mmrf:基础库c alibe:验证文件d rc,lvs1p4m,一层poly,4层金属m odel,spice_model,电路用的n18指工作电压1.8v的管子用一个管子来看层次操作系统与Cadence软件l inuxv irtuoso spectrev irtuoso schematicv irtuoso layout无源器件电阻种类阱电阻P oly电阻原理电容种类M IM电容M OM电容M OS电容原理电感种类电感原理有源器件M OS结构原理B JT结构原理数字版图基本数字单元标准化面积最小化布线最简化实例逻辑门触发器布局布线分频器布局布线匹配方法电阻方案画法差分对方案画法晶体三极管方案画法电流镜方案画法模拟版图运算放大器布局差分对电流镜有源负载电阻、电容偏置电路布线带隙基准源布局差分对电流镜有源负载电阻箱晶体三极管电路电容启动电路偏置电路布线版图可靠性寄生效应现象成因防护闩锁效应现象成因防护天线效应现象成因防护失配失配的原因随机失配来自尺寸、掺杂、氧化层厚度及其他影响器件值参数的微观波动。

模拟集成电路设计实习培训内容介绍培训目的经过本培训,学员将会学到在模拟集成电路设计过程中的绝大部分环节。

1.学会使用数模混合集成电路设计EDA工具进行简单的模拟集成电路设计的流程,包括Cadence的Virtuoso原理图输入、版图设计,Cadence的Spectre电路仿真,及Mentor Graphics 的Calibre版图规则检查(DRC)、电路图版图一致性检查(LVS)。

2.学会使用三大常用的仿真方式(DC,AC,以及Transient)来对电路进行性能的验证与设计参数的调整培训内容本培训首先设计一个运算放大器,在该放大器中采用了一个理想的电流源做偏置。

接着设计一个带隙基准源(Bandgap reference)来提供这个运算放大器中用到的电流源,然后对整个电路进行仿真验证。

整个电路Lab_top电原理图以及仿真激励如下图所示。

最后,参加培训的学员要求对所设计的Bandgap reference进行版图设计以及DRC、LVS检查,时间充裕的学员进一步设计运算放大器的版图及对其进行DRC/LVS的检查。

图1-0 Lab_top 原理图上图中的运算放大器(opam)电路如下图所示,值得注意的是,该运算放大器需要一个current sink做偏置,该current sink由上图中的NM1来提供。

其中的bandgap电路如下图。

Schematic 到layout的Quick start一、Schematic (opam)1. 运行虚拟机vmware;2. 在虚拟机界面中打开并运行CentOS.vmx;3. 用户登陆,登录名:eda,登录密码:123456;4. 界面按鼠标右键->选Open Terminal进入eda根目录下的命令行界面;5. 输入csh并回车;6. 输入icfb&命令后台运行Cadence的工具进入icfb界面。

图1-1 icfb的主界面在icfb中,任何一个电路,不论是已经存在的可以引用的库,还是用户新建立的一个电路,都是一个library. 一个library一般有若干个Cell(单元电路),每个cell由多个CellView组成,CellView可以是schematic(电路原理)和layout(版图)或symbol(符号),或者其他Cadence工具所调用的hspiceS等。