ARM微处理器硬件结构

- 格式:pptx

- 大小:338.87 KB

- 文档页数:60

ARM处理器详解(1)-ARMCortex-A系列处理器如图所⽰,绿⾊的部分都是v7-A的架构,蓝⾊的是v8-A架构,基本上绿⾊都是可以⽀持到32和64位的,除了A32,只⽀持到32位。

在右边的每个部分,⽐如说需要⾼效能的最上⾯的A15-A73这个部分是最⾼效的,接下来就是⽐较注重整个效率的部分了,中间那个部分是⽐较⾼效率的,最下⾯那栏的是效率最好的,在电池的效能⽅⾯达到了最好的标准。

最新的还有使⽤在麒麟980上的,基于Dynamiq技术的第⼆代优质内核 Cortex A76。

Acore主打的就是⾼性能,消费类的产品⽐如⼿机,平板,机顶盒等需要上系统的基本上都需要使⽤Acore。

Acore的发展曲线基本上和⼯艺曲线重叠,最新的A76是基于7nm的⼯艺,A73基于10nm的⼯艺,更早些的A5,A9基本上使⽤40nm或28nm的⼯艺。

这是ARM 2016年发布的最新A系列处理器,Cortex-A73⽀持全尺⼨ARMv8-A构架,ARMv8-A是ARM公司的⾸款⽀持64位指令集的处理器架构,包括ARM TrustZone技术、NEON、虚拟化和加密技术。

所以⽆论是32位还是64位,Cortex-A73都可以提供适应性最强的移动应⽤⽣态开发环境。

Cortex-A73包括128位 AMBR 4 ACE接⼝和ARM的big.LITTLE系统⼀体化接⼝,采⽤了⽬前最先进的10nm技术制造,可以提供⽐Cortex-A72⾼出30%的持续处理能⼒,⾮常适合移动设备和消费级设备使⽤。

预计今年晚些时候到2017年,Cortex-A73处理器将会逐渐覆盖到我们合作伙伴的⾼端智能⼿机、平板电脑、翻盖式移动设备、数字电视等⼀系列消费电⼦设备。

big.LITTLE架构发展到最新的A76,更新了Dynamiq架构,core的外⾯再包了⼀层L3 cache,减少了对外部DDR的读写,所以性能更优。

Cortex-A72最早发布于2015年年初,也是基于ARMv8-A架构,采⽤台积电16nm FinFET制造⼯艺,Cortex-A72可在芯⽚上单独实现性能,也可以搭配Cortex-A53处理器与ARMCoreLinkTMCCI⾼速缓存⼀致性互连(CacheCoherentInterconnect)构成ARMbig.LITTLETM配置,进⼀步提升能效。

ZT:arm cpu的架构及分类说明今天在编译mplayer for mx27ads的时候,碰到了armv5te与armv6优化的问题。

默认的交叉编译器支持armv5te也支持armv6,就默认使用了mplayer中mpeg4的armv6解码代码,结果在mx27ads版上,播放mpeg4视频时颜色空间转换出错。

对比x86后总算找到了这个问题,顺手根据ARM官方资料和网上资料整理了一篇arm cpu的架构及分类说明。

ARM微处理器系列ARM 微处理器目前包括下面几个系列,以及其它厂商基于 ARM 体系结构的处理器,除了具有ARM 体系结构的共同特点以外,每一个系列的 ARM 微处理器都有各自的特点和应用领域。

- ARM7 系列- ARM9 系列- ARM9E 系列- ARM10E 系列- ARM11系列- Cortex 系列- SecurCore 系列- OptimoDE Data Engines- Xcale其中,ARM7、ARM9、ARM9E 和 ARM10 为4 个通用处理器系列,每一个系列提供一套相对独特的性能来满足不同应用领域的需求。

SecurCore 系列专门为安全要求较高的应用而设计。

以下我们来详细了解一下各种处理器的特点及应用领域。

ARM7系列ARM7 系列微处理器为低功耗的 32位 RISC 处理器,最适合用于对价位和功耗要求较高的消费类应用。

ARM7 微处理器系列具有如下特点:-具有嵌入式 ICE-RT 逻辑,调试开发方便。

-极低的功耗,适合对功耗要求较高的应用,如便携式产品。

-能够提供 0.9MIPS/MHz 的三级流水线结构。

-代码密度高并兼容 16 位的 Thumb 指令集。

-对操作系统的支持广泛,包括 Windows CE、Linux、Palm OS 等。

-指令系统与 ARM9 系列、ARM9E 系列和 ARM10E 系列兼容,便于用户的产品升级换代。

-主频最高可达 130MIPS,高速的运算处理能力能胜任绝大多数的复杂应用。

张凌001关于ARM的内核架构很多时候我们都会对M0,M0+,M3,M4,M7,arm7,arm9,CORTEX-A系列,或者说AVR,51,PIC等,一头雾水,只知道是架构,不知道具体是什么,有哪些不同?今天查了些资料,来解解惑,不是很详细,但对此有个大体了解。

咱先来当下最火的ARM吧1.ARMARM即以英国ARM(Advanced RISC Machines)公司的内核芯片作为CPU,同时附加其他外围功能的嵌入式开发板,用以评估内核芯片的功能和研发各科技类企业的产品.ARM 微处理器目前包括下面几个系列,以及其它厂商基于 ARM 体系结构的处理器,除了具有ARM 体系结构的共同特点以外,每一个系列的 ARM 微处理器都有各自的特点和应用领域。

- ARM7 系列- ARM9 系列- ARM9E 系列- ARM10E 系列- ARM11系列- Cortex 系列- SecurCore 系列- OptimoDE Data Engines- Intel的Xscale- Intel的StrongARM ARM11系列2. Cortex 系列32位RISCCPU开发领域中不断取得突破,其设计的微处理器结构已经从v3发展到现在的v7。

Cortex 系列处理器是基于ARMv7架构的,分为Cortex-M、Cortex-R和Cortex-A三类。

由于应用领域的不同,基于v7架构的Cortex处理器系列所采用的技术也不相同。

基于v7A的称为“Cortex-A系列。

高性能的Cortex-A15、可伸缩的Cortex-A9、经过市场验证的Cortex-A8处理器以及高效的Cortex-A7和Cortex-A5处理器均共享同一体系结构,因此具有完整的应用兼容性,支持传统的ARM、Thumb指令集和新增的高性能紧凑型Thumb-2指令集。

1Cortex-M系列Cortex-M系列又可分为Cortex-M0、Cortex-M0+、Cortex-M3、Cortex-M4;2Cortex-R系列Cortex-R系列分为Cortex-R4、Cortex-R5、Cortex-R7;3Cortex-A 系列Cortex-A系列分为Cortex-A5、Cortex-A7、Cortex-A8、Cortex-A9、Cortex-A15、Cortex-A50等 ,同样也就有了对应内核的Cortex-M0开发板、Cortex-A5开发板、Cortex-A8开发板、Cortex-A9开发板、Cortex-R4开发板等等。

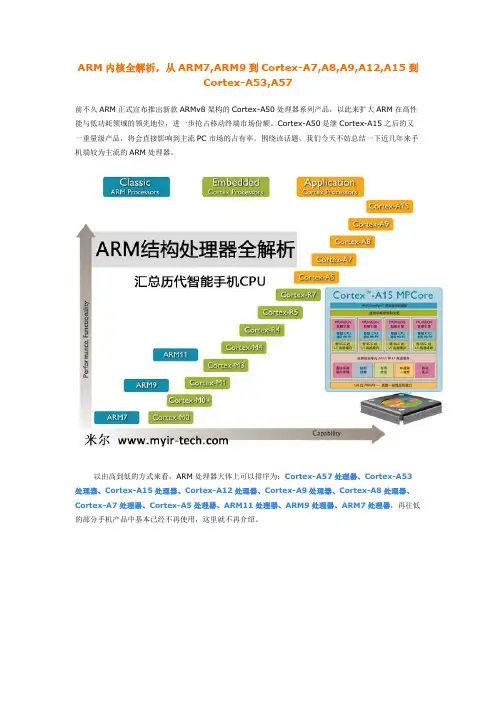

ARM内核全解析,从ARM7,ARM9到Cortex-A7,A8,A9,A12,A15到Cortex-A53,A57前不久ARM正式宣布推出新款ARMv8架构的Cortex-A50处理器系列产品,以此来扩大ARM在高性能与低功耗领域的领先地位,进一步抢占移动终端市场份额。

Cortex-A50是继Cortex-A15之后的又一重量级产品,将会直接影响到主流PC市场的占有率。

围绕该话题,我们今天不妨总结一下近几年来手机端较为主流的ARM处理器。

以由高到低的方式来看,ARM处理器大体上可以排序为:Cortex-A57处理器、Cortex-A53处理器、Cortex-A15处理器、Cortex-A12处理器、Cortex-A9处理器、Cortex-A8处理器、Cortex-A7处理器、Cortex-A5处理器、ARM11处理器、ARM9处理器、ARM7处理器,再往低的部分手机产品中基本已经不再使用,这里就不再介绍。

ARM 处理器架构发展● Cortex-A57、A53处理器Cortex-A53、Cortex-A57两款处理器属于Cortex-A50系列,首次采用64位ARMv8架构,意义重大,这也是ARM最近刚刚发布的两款产品。

Cortex-A57是ARM最先进、性能最高的应用处理器,号称可在同样的功耗水平下达到当今顶级智能手机性能的三倍;而Cortex-A53是世界上能效最高、面积最小的64位处理器,同等性能下能效是当今高端智能手机的三倍。

这两款处理器还可整合为ARM big.LITTLE(大小核心伴侣)处理器架构,根据运算需求在两者间进行切换,以结合高性能与高功耗效率的特点,两个处理器是独立运作的。

应用案例:预计于2014年推出。

● Cortex-A15处理器架构解析ARM Cortex-A15处理器隶属于Cortex-A系列,基于ARMv7-A架构,是业界迄今为止性能最高且可授予许可的处理器。

Cortex-A15 MPCore处理器具有无序超标量管道,带有紧密耦合的低延迟2级高速缓存,该高速缓存的大小最高可达4MB。

Armv9核心A710、A715和A510微架构解读1、引言在上一篇文章“从A76到A78——在变化中学习Arm微架构”中,我们了解了Arm处理器微架构的基本组成,介绍了Armv8架构最后几代经典处理器架构。

现在,Arm公司已经在2021年3月推出了其最新的Armv9架构系列处理器,距上一代Armv8系列架构发布相隔了整整10年时间。

新一代的Armv9产品,不但会带来更强大的计算性能,在安全、AI等领域也带来了全新的设计。

可以说,Armv9系列继承了Armv8架构的优势,同时也为Arm公司的下一个十年拉开了帷幕。

本文将着重介绍基于Armv9架构的A710、A715、A510等处理器架构,让大家了解Armv9架构和Armv8架构的差异。

2、Arm的Cortex-X定制CPU计划在介绍Armv9系列前,我们先看一下ARM的Cortex-X定制CPU计划。

Cortex-X方案先于Armv9发布,在Arm发布A78时,同时也发布了Cortex-X1这一颗性能强大的CPU,后续大家习惯称之为超级大核。

从此,旗舰处理器的架构从4+4(4大+4小)逐步变成了1+3+4(1超大+3大+4小)架构。

Cortex-X计划不但带来了如X1这样的超级大核心设计,也允许厂商参与定制Cortex-X 系列的核心设计。

X系列超级大核心相比A系列大核心,拥有更大的芯片面积,同时支持更多的发射和解码能力,还增加了缓存和ROB空间等,图中Arm 宣称X1相比A78的性能提升超过30%。

后续计划专门写一篇文章介绍Cortex-X 的系列处理器。

3、64bit应用生态32bit和64bit应用兼容问题已经历经多年讨论,主流的苹果和安卓平台都明确表示要切换到64bit以提供更大的应用访问空间和支持处理器的最新特性。

苹果公司在2017年的iOS11中就强制要求开发者切换到64bit应用,谷歌公司则要求安卓开发者在2021年将上传的应用完全切换到64bit。

浅析CPU两⼤架构ARM和X86区别及拓展windowsx86与x64的区别 由于在 linux 安装nodejs环境时遇到⼀个不可执⾏⽂件的问题,涉及到了ARM和x64⽂件,所以查了点资料初步了解了⼀下cpu两⼤架构:ARM与X86的区别。

⼀、CPU是什么 中央处理单元(CPU)主要由运算器、控制器、寄存器三部分组成,从字⾯意思看运算器就是起着运算的作⽤,控制器就是负责发出CPU每条指令所需要的信息,寄存器就是保存运算或者指令的⼀些临时⽂件,这样可以保证更⾼的速度。

CPU有着处理指令、执⾏操作、控制时间、处理数据四⼤作⽤,打个⽐喻来说,CPU就像我们的⼤脑,帮我们完成各种各样的⽣理活动。

因此如果没有CPU,那么电脑就是⼀堆废物,⽆法⼯作。

移动设备其实很复杂,这些CPU需要执⾏数以百万计的指⽰,才能使它向我们期待的⽅向运⾏,⽽CPU的速度和功率效率是⾄关重要的。

速度影响⽤户体验,⽽效率影响电池寿命。

最完美的移动设备是⾼性能和低功耗相结合。

⼆、要了解X86和ARM,就得先了解复杂指令集(CISC)和精简指令集(RISC) 从CPU发明到现在,有⾮常多种架构,从我们熟悉的X86,ARM,到不太熟悉的MIPS,IA64,它们之间的差距都⾮常⼤。

但是如果从最基本的逻辑⾓度来分类的话,它们可以被分为两⼤类,即所谓的“复杂指令集”与“精简指令集”系统,也就是经常看到的“CISC”与“RISC”。

Intel和ARM处理器的第⼀个区别是,前者使⽤复杂指令集(CISC),⽽后者使⽤精简指令集(RISC)。

属于这两种类中的各种架构之间最⼤的区别,在于它们的设计者考虑问题⽅式的不同。

我们可以继续举个例⼦,⽐如说我们要命令⼀个⼈吃饭,那么我们应该怎么命令呢?我们可以直接对他下达“吃饭”的命令,也可以命令他“先拿勺⼦,然后舀起⼀勺饭,然后张嘴,然后送到嘴⾥,最后咽下去”。

从这⾥可以看到,对于命令别⼈做事这样⼀件事情,不同的⼈有不同的理解,有⼈认为,如果我⾸先给接受命令的⼈以⾜够的训练,让他掌握各种复杂技能(即在硬件中实现对应的复杂功能),那么以后就可以⽤⾮常简单的命令让他去做很复杂的事情——⽐如只要说⼀句“吃饭”,他就会吃饭。

ARM体系结构

ARM作为一种微处理器体系结构,具有广泛应用范围、高性价比、低功耗等优势,在晶体管规模以及架构方面有着很大的节省,因而受到了越来越多应用者的青睐。

ARM体系结构包括处理器(Processor)、片外存储器(External Memory)、I/O接口(Input/Output Interface)、外围器件(Peripheral Devices)、软件支持(Software Support)等内容。

从处理器来说,ARM体系结构提供了一系列非常细分的机型,它们有不同的特性和操作速度,可以满足不同的性能需求,而且这些机型一般都有较高的可缩放性,所以在产品设计的过程中可以根据实际要求选择合适的特性和速度。

从片外存储器来说,ARM体系结构支持使用不同类型的存储器,比如SRAM、DRAM、Flash等,可以根据应用性能和耗电量的需求,来选择合适的存储器以满足不同应用场景的需求,而且存储器容量也比较可观,一般可以满足大部分应用场景的要求。

从I/O接口来说,ARM体系结构支持多种接口,如USB、I2C、SPI、UART等,通过这些接口可以与周边的外设进行连接,而这些接口的功耗和速度也比较低。

ARM公司及产品架构简介--ARM概述1.ARM 是英国一家电子公司的名字,该公司成立于1990年11月,是苹果电脑,Acorn电脑集团和VLSI Technology的合资企业。

Acorn曾在1985年推出世界上首个商用单芯片RISC (Reduced Instruction Set Computing)处理器。

ARM主要出售芯片设计技术的授权。

2.ARM体系架构的版本就是它所使用的指令集的版本。

ARM架构支持32位的ARM指令集和16位的Thumb指令集,后者使得代码的存储空间大大减小。

还提供了一些扩展功能,还在使用的ARM指令集(ISA,Instruction Set Architecture)有以下版本。

arm v4:只支持32位指令集arm v4t:增加t(thumb)指令集arm v5te:增加增强型dsp指令e指令arm v5tej :提供java加速功能arm v6 :thumb-2 增加多媒体功能的支持arm v7:thumb-2 改良浮点运算总结版本名中的T表示Thumb指令集,E表示增强型DSP指令,J表示Java加速器。

3.ARM处理器的系列:在相同指令集下,搭配不同部件就可以组装出具有不同功能的处理器,比如有无内存管理单元、有无调试功能等。

它们可以分为8个系列,系列名中有7个后缀,这些后缀可以组合,含义如下。

①T:表示支持Thumb指令集。

②D:表示支持片。

上调试( Debug)。

③M:表示内嵌硬件乘法器(Multiplier)。

④1:支持片上断点和调试点。

⑤E:表示支持增强型DSP功能。

⑥J:表示支持Jazelle技术,即Java加速器。

⑦S:表示全合成式( full synthesizable)。

8大系列:这8个系列中,ARM7、ARM9、ARM9E和ARM10为通用处理器系列,每个系列提供-“套相对独特的性能来满足不同应用领域的需求。

SecurCore系列专门为安全要求较高的应用而设计。

arm体系结构特点

ARM 体系结构是一种广泛使用的 32 位微处理器体系结构,具有以下特点:

1. 简单的指令集:ARM 指令集是一种 RISC(精简指令集计算机)指令集,它具有固定长度的指令和简单的指令格式。

这种简单的指令集可以提高指令的执行速度和效率,同时也可以减少指令的解码时间。

2. 高效的流水线:ARM 体系结构采用了高效的流水线技术,可以在一个时钟周期内执行多条指令。

这种流水线技术可以提高指令的执行速度和效率,从而提高处理器的性能。

3. 低功耗设计:ARM 体系结构采用了低功耗设计,可以在不影响性能的情况下降低处理器的功耗。

这种低功耗设计对于移动设备和嵌入式系统非常重要,可以延长设备的电池寿命。

4. 可扩展性:ARM 体系结构具有很好的可扩展性,可以通过增加更多的寄存器和指令来扩展处理器的功能。

这种可扩展性可以满足不同应用的需求,例如多媒体处理、网络通信等。

5. 支持Thumb 指令集:ARM 体系结构还支持 Thumb 指令集,这是一种 16 位的指令集。

Thumb 指令集可以在不损失性能的情况下减少代码的大小,从而节省存储空间。

6. 强大的异常处理机制:ARM 体系结构具有强大的异常处理机制,可以处理各种硬件和软件异常。

这种异常处理机制可以提高系统的可靠性和稳定性。

总之,ARM 体系结构具有简单的指令集、高效的流水线、低功耗设计、可扩展性、支持Thumb 指令集和强大的异常处理机制等特点,这些特点使得 ARM 体系结构成为了移动设备和嵌入式系统领域的主流处理器体系结构。

体系结构: RISC, CISC, x86, ARM, MIPS硬件体系结构(Architecture)软件操作系统(Operating System)一、RISC与CISC1.CISC(Complex Instruction SetComputer,复杂指令集计算机)复杂指令集(CISC,Complex Instruction Set Computer)是一种微处理器指令集架构(ISA),每个指令可执行若干低阶操作,诸如从内存读取、储存、和计算操作,全部集于单一指令之中。

CISC特点:1.指令系统庞大,指令功能复杂,指令格式、寻址方式多;2.绝大多数指令需多个机器周期完成;3.各种指令都可访问存储器;4.采用微程序控制;5.有专用寄存器,少量;6.难以用优化编译技术生成高效的目标代码程序;在CISC指令集的各种指令中,大约有20%的指令会被反复使用,占整个程序代码的80%。

而余下的80%的指令却不经常使用,在程序设计中只占20%。

2.RISC(reduced instruction setcomputer,精简指令集计算机)精简指令集这种设计思路对指令数目和寻址方式都做了精简,使其实现更容易,指令并行执行程度更好,编译器的效率更高。

它能够以更快的速度执行操作。

这种设计思路最早的产生缘自于有人发现,尽管传统处理器设计了许多特性让代码编写更加便捷,但这些复杂特性需要几个指令周期才能实现,并且常常不被运行程序所采用。

此外,处理器和主内存之间运行速度的差别也变得越来越大。

在这些因素促使下,出现了一系列新技术,使处理器的指令得以流水执行,同时降低处理器访问内存的次数。

实际上在后来的发展中,RISC与CISC在竞争的过程中相互学习,现在的RISC指令集也达到数百条,运行周期也不再固定。

虽然如此,RISC设计的根本原则——针对流水线化的处理器优化—0—没有改变,而且还在遵循这种原则的基础上发展出RISC的一个并行化变种VLIW(包括Intel EPIC),就是将简短而长度统一的精简指令组合出超长指令,每次执行一条超长指令,等于并行执行多条短指令。