存储器 补充习题

- 格式:ppt

- 大小:419.50 KB

- 文档页数:5

1. 用下列芯片构成存储系统,各需要多少个RAM芯片?需要多少位地址作为片外地址译码?设系统为20位地址线,采用全译码方式。

(1)512×4位RAM构成16KB的存储系统;(2)1024×1位RAM构成128KB的存储系统;(3)2K×4位RAM构成64KB的存储系统;(4)64K×1位RAM构成256KB的存储系统。

解:(1 需要16KB/512×4=64片,片外地址译码需20-log2512=11位地址线。

(2 需要128KB/1K×1=1024片,片外地址译码需20-log21024=10位地址线。

(3 需要64KB/2K×4=64片,片外地址译码需20-log2(1024×2=9位地址线。

(4 需要256KB/64K×1位=32片,片外地址译码需20-log2(1024×64=4位地址线。

2. 现有一种存储芯片容量为512×4位,若要用它组成4KB的存储容量,需多少这样的存储芯片?每块芯片需多少寻址线?而4KB存储系统最少需多少寻址线?解: 4K×8bit /512×4bit= 16片,需要16片存储芯片;29 = 512,每片芯片需9条寻址线;212 = 4096,4KB存储系统最少需12条寻址线。

3. 一个具有8KB直接相联Cache的32位计算机系统,主存容量为32MB,假定该Cache 中块的大小为4个32位字。

(1)求该主存地址中区号、块号和块内地址的位数。

(2)求主存地址为ABCDEF16的单元在Cache中的位置。

解: (1 主存区数为32MB/8KB = 4096,212 = 4096,区号的位数为12;区内块数为8KB/4×4B = 512,29 = 512,块号的位数为9;块内单元数(字节编址)为4×32 / 8 = 16,24 = 16,块内地址的位数4。

预览:计算机组成原理——习题与解析第四章存储器系统邵桂芳 4.2半导体存储器4.2.1填空题1. 计算机中的存储器是用来存放__①___的, 随机访问存储器的访问速度与___②___无关。

答案:①程序和数据②存储位置2. 对存储器的访问包括______和________两类。

答案:①读②写3. 计算机系统中的存储器分为__①___和___②____。

在CPU 执行程序时,必须将指令存在____③____中。

答案:①内存②外存③内存4. 主存储器的性能指标主要是①、②、存储周期和存储器带宽。

答案:①存储容量②存取时间5. 存储器中用①来区分不同的存储单元, 1GB=②KB 。

答案:①地址②1024X1024(或220)6. 半导体存储器分为①、②、只读存储器(ROM)和相联存储器等。

答案:①静态存储器(SRAM) ②动态存储器(DRAM)7. RAM 的访问时间与存储单元的物理位置①,任何存储单元的内容都能被②答案:①无关②随机访问8. 存储揣芯片由①、②、地址译码和控制电路等组成。

答案:①存储体②读写电路9. 地址译码分为①方式和②方式。

答案:①单译码②双译码10.双译码方式采用①个地址译码器,分别产生②和③信号。

答案:①两②行选通③列选通11.若RAM 芯片内有1024个单元,用单译码方式,地址译码器将有①条输出线;用双译码方式,地址译码器有②条输出线。

答案:①1024 ②6412. 静态存储单元是由晶体管构成的①, 保证记忆单元始终处于稳定状态, 存储的信息不需要②。

答案:①双稳态电路②刷新(或恢复)13.存储器芯片并联的目的是为了①,串联的目的是为了②。

答案:①位扩展②字节单元扩展14.计算机的主存容量与①有关,其容量为②。

答案:①计算机地址总线的根数②2地址线数15.要组成容量为4MX8位的存储器, 需要①片4MXl 位的存储器芯片并联, 或者需要②片1MX3的存储器芯片串联。

答案:①8 ② 416.内存储器容量为256K 时,若首地址为00000H ,那么末地址的十六进制表示是答案:3FFFFH17.主存储器一般采用①存储器件,它与外存比较存取速度②、成本③。

第四章存储器一、填空题1. 计算机中的存储器是用来存放的,随机访问存储器的访问速度与无关.√2。

主存储器的性能指标主要是、存储周期和存储器带宽。

√3。

存储器中用来区分不同的存储单元,1GB= KB。

√4。

半导体存储器分为、、只读存储器(ROM)和相联存储器等。

√5. 地址译码分为方式和方式.√6。

双译码方式采用个地址译码器,分别产生和信号。

√7。

若RAM芯片内有1024个单元,用单译码方式,地址译码器将有条输出线;用双译码方式,地址译码器有条输出线。

√8. 静态存储单元是由晶体管构成的,保证记忆单元始终处于稳定状态,存储的信息不需要。

√9. 存储器芯片并联的目的是为了 ,串联的目的是为了。

10. 计算机的主存容量与有关,其容量为。

11。

要组成容量为4M×8位的存储器,需要片4M×1位的存储器芯片并联,或者需要片1M×8位的存储器芯片串联。

12. 内存储器容量为6K时,若首地址为00000H,那么末地址的十六进制表示是。

13 主存储器一般采用存储器件,它与外存比较存取速度、成本。

14 三级存储器系统是指这三级、、。

15 表示存储器容量时KB= ,MB= ;表示硬盘容量时,KB= ,MB= 。

16一个512KB的存储器,其地址线和数据线的总和是。

17 只读存储器ROM可分为、、和四种.18 SRAM是;DRAM是;ROM是;EPROM是。

19半导体SRAM靠存储信息,半导体DRAM则是靠存储信息。

20半导体动态RAM和静态RAM的主要区别是。

21MOS半导体存储器可分为、两种类型,其中需要刷新。

22 广泛使用的和都是半导体③存储器。

前者的速度比后者快,但不如后者高,它们的共同缺点是断电后保存信息.23 EPROM属于的可编程ROM,擦除时一般使用,写入时使用高压脉冲.24 单管动态MOS型半导体存储单元是由一个和一个构成的。

25 动态半导体存储器的刷新一般有、和三种方式。

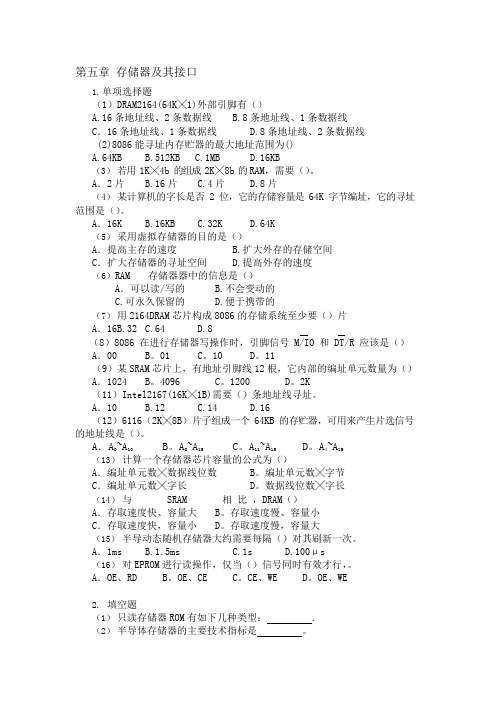

第五章存储器及其接口1.单项选择题(1)DRAM2164(64K╳1)外部引脚有()A.16 条地址线、2 条数据线B.8 条地址线、1 条数据线C.16 条地址线、1 条数据线 D.8 条地址线、2 条数据线(2)8086 能寻址内存贮器的最大地址范围为()A.64KBB.512KBC.1MBD.16KB(3)若用1K╳4b的组成2K╳8b的RAM,需要()。

A.2 片 B.16 片 C.4 片 D.8 片(4)某计算机的字长是否 2 位,它的存储容量是 64K 字节编址,它的寻址范围是()。

A.16K B.16KB C.32K D.64K(5)采用虚拟存储器的目的是()A.提高主存的速度 B.扩大外存的存储空间C.扩大存储器的寻址空间 D.提高外存的速度(6)RAM 存储器器中的信息是()A.可以读/写的 B.不会变动的C.可永久保留的D.便于携带的(7)用2164DRAM 芯片构成8086 的存储系统至少要()片A.16 B.32 C.64 D.8(8)8086 在进行存储器写操作时,引脚信号 M/IO 和 DT/R 应该是()A.00 B。

01 C。

10 D。

11(9)某SRAM 芯片上,有地址引脚线12 根,它内部的编址单元数量为()A.1024 B。

4096 C。

1200 D。

2K(11)Intel2167(16K╳1B)需要()条地址线寻址。

A.10 B.12 C.14 D.16(12)6116(2K╳8B)片子组成一个 64KB 的存贮器,可用来产生片选信号的地址线是()。

A.A0~A10B。

A~A15C。

A11~A15D。

A4~A19(13)计算一个存储器芯片容量的公式为()A.编址单元数╳数据线位数B。

编址单元数╳字节C.编址单元数╳字长D。

数据线位数╳字长(14)与 SRAM 相比,DRAM()A.存取速度快、容量大B。

存取速度慢、容量小C.存取速度快,容量小D。

存取速度慢,容量大(15)半导动态随机存储器大约需要每隔()对其刷新一次。

第3章 多层次的存储器习题参考答案1、设有一个具有20位地址和32位字长的存储器,问 (1) 该存储器能存储多少字节的信息?(2) 如果存储器由512K ×8位SRAM 芯片组成,需要多少片? (3) 需要多少位地址作芯片选择? 解:(1) 该存储器能存储:字节4M 832220=⨯(2) 需要片8823228512322192020=⨯⨯=⨯⨯K (3) 用512K ⨯8位的芯片构成字长为32位的存储器,则需要每4片为一组进行字长的位数扩展,然后再由2组进行存储器容量的扩展。

所以只需一位最高位地址进行芯片选择。

2、已知某64位机主存采用半导体存储器,其地址码为26位,若使用4M ×8位的DRAM 芯片组成该机所允许的最大主存空间,并选用内存条结构形式,问; (1) 若每个内存条为16M ×64位,共需几个内存条? (2) 每个内存条内共有多少DRAM 芯片?(3) 主存共需多少DRAM 芯片? CPU 如何选择各内存条? 解:(1) 共需条4641664226=⨯⨯M 内存条 (2) 每个内存条内共有32846416=⨯⨯M M 个芯片(3) 主存共需多少1288464648464226=⨯⨯=⨯⨯M M M 个RAM 芯片, 共有4个内存条,故CPU 选择内存条用最高两位地址A 24和A 25通过2:4译码器实现;其余的24根地址线用于内存条内部单元的选择。

3、用16K ×8位的DRAM 芯片构成64K ×32位存储器,要求: (1) 画出该存储器的组成逻辑框图。

(2) 设存储器读/写周期为0.5μS ,CPU 在1μS 内至少要访问一次。

试问采用哪种刷新方式比较合理?两次刷新的最大时间间隔是多少?对全部存储单元刷新一遍所需的实际刷新时间是多少?解:(1) 用16K ×8位的DRAM 芯片构成64K ×32位存储器,需要用16448163264=⨯=⨯⨯K K 个芯片,其中每4片为一组构成16K ×32位——进行字长位数扩展(一组内的4个芯片只有数据信号线不互连——分别接D 0~D 7、D 8~D 15、D 16~D 23和D 24~D 31,其余同名引脚互连),需要低14位地址(A 0~A 13)作为模块内各个芯片的内部单元地址——分成行、列地址两次由A 0~A 6引脚输入;然后再由4组进行存储器容量扩展,用高两位地址A 14、A 15通过2:4译码器实现4组中选择一组。

存储器选择题:1、下面关于半导体存储器组织叙述中,错误的是()。

DA、存储器的核心部分是存储体,由若干存储单元构成B、存储单元由若干存放0和1的存储元件构成C、一个存储单元有一个编号,就是存储单元地址D、同一个存储器中,每个存储单元的宽度可以不同2、下面()存储器是目前已被淘汰的存储器。

CA、半导体存储器B、磁表面存储器C、磁芯存储器D、光盘存储器3、若SRAM芯片的容量为1024*4位,则地址和数据引脚的数目分别是()。

AA、10,4B、5,4C、10,8D、5,84、若计算机字长16位,主存地址空间大小是64KB,按字节编址,则主存寻址范围是()。

AA、0~64K-1B、0~32K-1C、0~64KB-1D、0~32KB-15、需要定时刷新的半导体存储器芯片是()BA、SRAMB、DRAMC、EPROMD、Flash Memory6、假定用若干个16K*1位的存储器芯片组成一个64K*8位的存储器,芯片内各单元连续编址,则地址BFF0H所在的芯片的最小地址为()。

CA、4000HB、6000HC、8000HD、A000H7、假定用若干个16K*8位的存储器芯片组成一个64K*8位的存储器,芯片内各单元交叉编址,则地址BFFFH所在的芯片的最小地址为()。

DA、0000HB、0001HC、0002HD、0003H8、假定主存地址位数为32位,按字节编址,主存和Cache之间采用直接映射方式,,主存块大小为1个字,每字32位,写操作时采用全写方式,则能存放32K字数据的Cache的总容量至少应有多少位( )。

BA、1504KB、1536KC、1568KD、1600K9、假定主存地址位数为32位,按字节编址,主存和Cache之间采用直接映射方式,,主存块大小为1个字,每字32位,写操作时采用回写方式,则能存放32K字数据的Cache的总容量至少应有多少位( )。

CA、1504KB、1536KC、1568KD、1600K10、假定主存地址位数为32位,按字节编址,主存和Cache之间采用全相连映射方式,,主存块大小为1个字,每字32位,写操作时采用回写方式和随机替换策略,则能存放32K 字数据的Cache的总容量至少应有多少位( )。

最新--01-存储器练习题-带参考答案资料存储器练习题参考答案⼀、选择题(75+7题)1、计算机系统中的存储器系统是指( D )。

A、RAM存储器B、ROM存储器C、主存储器D、主存储器和外存储器2、存储器是计算机系统中的记忆设备,它主要⽤来( C )。

A、存放数据B、存放程序C、存放数据和程序D、存放微程序3、存储单元是指( B )。

A、存放⼀个⼆进制信息位的存储元B、存放⼀个机器字的所有存储元集合C、存放⼀个字节的所有存储元集合D、存放两个字节的所有存储元集合4、计算机的存储器采⽤分级存储体系的主要⽬的是( D )。

A、便于读写数据B、减⼩机箱的体积C、便于系统升级D、解决存储容量、价格和存取速度之间的⽭盾5、存储周期是指( C )。

A、存储器的读出时间B、存储器的写⼊时间C、存储器进⾏连续读和写操作所允许的最短时间间隔D、存储器进⾏连续写操作所允许的最短时间间隔6、和外存储器相⽐,内存储器的特点是( C )。

A、容量⼤,速度快,成本低B、容量⼤,速度慢,成本⾼C、容量⼩,速度快,成本⾼D、容量⼩,速度快,成本低B、0~32KC、0~64KBD、0~32KB8、某SRAM芯⽚,其存储容量为64K×16位,该芯⽚的地址线和数据线数⽬为( D )。

A、64,16B、16,64C、64,8D、16,169、某DRAM芯⽚,其存储容量为512K×8位,该芯⽚的地址线和数据线数⽬为( D )。

A、8,512B、512,8C、18,8D、19,810、某机字长32位,存储容量1MB,若按字编址,它的寻址范围是( C )。

A、0~1MB、0~512KBC、0~256KD、0~256KB11、某计算机字长32位,其存储容量为4MB,若按字编址,它的寻址范围是( A )。

A、0~1MB、0~4MBC、0~4MD、0~1MB12、某计算机字长32位,其存储容量为4MB,若按半字编址,它的寻址范围( C )。

习题四参考答案1.某机主存储器有16位地址,字长为8位。

(1)如果用1k×4位的RAM芯片构成该存储器,需要多少片芯片?(2)该存储器能存放多少字节的信息?(3)片选逻辑需要多少位地址?解:需要存储器总容量为:16K×8位,故,(1)需要1k×4位的RAM芯片位32片。

(2)该存储器存放16K字节的信息。

(3)片选逻辑需要4位地址。

2. 用8k×8位的静态RAM芯片构成64kB的存储器,要求:(1)计算所需芯片数。

(2)画出该存储器组成逻辑框图。

解:(1)所需芯片8片。

(2)逻辑图为:3. 用64k×1位的DRAM芯片构成256k×8位存储器,要求:(1)画出该存储器的逻辑框图。

(2)计算所需芯片数。

(3)采用分散刷新方式,如每单元刷新间隔不超过2ms,则刷新信号周期是多少?如采用集中刷新方式,存储器刷新一遍最少用多少读/写周期?解:(1)(2)所需芯片为32片。

(3)设读写周期为0.5微妙,则采用分散式刷新方式的刷新信号周期为1微妙。

因为64K ×1的存储矩阵是由四个128×128的矩阵构成,刷新时4个存储矩阵同时对128个元素操作,一次刷新就可完成512个元素,整个芯片只有128次刷新操作就可全部完成。

所以存储器刷新一遍最少用128个读/写周期。

4. 用8k×8位的EPROM芯片组成32k×16位的只读存储器,试问:(1)数据寄存器多少位?(2)地址寄存器多少位?(3)共需多少个EPROM芯片?(4)画出该只读存储器的逻辑框图?解:因为只读存储器的容量为:32k×16,所以:(1)数据寄存器16位。

(2)地址寄存器15位。

(3)共需8个EPROM芯片?(4)逻辑框图为:5. 某机器中,已经配有0000H~3FFFH的ROM区域,现在再用8k×8位的RAM芯片形成32k ×8位的存储区域,CPU地址总线为A0~A15,数据总线为D0~D7,控制信号为R/W(读/写)、MREQ(访存),要求:(1)画出地址译码方案。

第三章存储系统习题参考答案1.有一个具有20位地址和32 位字长的存储器,问:(1)该存储器能存储多少个字节的信息?(2)如果存储器由512K×8位SRAM芯片组成,需要多少芯片?(3)需要多少位地址作芯片选择?解:(1)∵ 220= 1M,∴ 该存储器能存储的信息为:1M×32/8=4MB (2)(1000/512 )×(32/8 )= 8(片)(3)需要 1 位地址作为芯片选择。

2. 已知某64位机主存采用半导体存储器,其地址码为26位,若使用4M×8 位的DRAM芯片组成该机所允许的最大主存空间,并选用模块板结构形式,问:(1)每个模块板为16M×64 位,共需几个模块板?(2)个模块板内共有多少DRAM芯片?(3)主存共需多少DRAM芯片? CPU如何选择各模块板?解:(1). 共需模块板数为m:m= ÷224=4(块)(2). 每个模块板内有DRAM芯片数为n:n=(224/2 22)×(64/ 8)=32 (片)(3)主存共需DRAM芯片为:4×32=128 (片)每个模块板有32片DRAM芯片,容量为16M×64 位,需24根地址线(A23~A0)完成模块板内存储单元寻址。

一共有 4 块模块板,采用 2 根高位地址线(A25~A24),通过2:4 译码器译码产生片选信号对各模块板进行选择。

3.用16K×8位的DRAM芯片组成64K×32 位存储器,要求:(1)画出该存储器的组成逻辑框图。

(2)设存储器读/写周期为0.5 μS, CPU在1μS内至少要访问一次。

试问采用哪种刷新方式比较合理?两次刷新的最大时间间隔是多少?对全部存储单元刷新一遍所需的实际刷新时间是多少? 解: ( 1)组成 64K × 32 位存储器需存储芯片数为N=(64K/16K )×( 32 位/8 位) =16(片)每 4 片组成 16K ×32 位的存储区,有 A13-A0作为片内地址,用 A15 经 2: 4 译码器产生片选信号 ,逻辑框图如下所示:(2)依题意,采用异步刷新方式较合理,可满足 CPU 在 1μS 内至少访问内存 一次的要求。

计算机硬件基础(下)补充习题1.写出存储器读指令LD R1, (R2) 的控制序列,该指令完成R1<- MEM(R2)2.写出无条件绝对跳转指令JMP的控制序列3.用MiniSys语言编写程序,完成10×$1+15×$24.在数据段定义任意10个数。

编程查找其中是否有23.如果有,在$V0中放23存放的位置,$V1=1(表示查找到),否则$V0=$V1=-1.5.用MiniSys汇编语言编写程序,完成内存中两个16位的数M1和M2相乘,乘积放在$1中。

6.请写出组合逻辑控制电路中,针对ADD, BR, BRN,LD和JMP 5条指令的Zout与PCout控制信号的产生电路7.在内存中有一个名为BUFF的32位数的数组,数组元素个数为10,现在已有9个数以严格升序排列在数组中,请用MiniSys汇编语言编写程序,将第10个数(在$2中)插入到数组中的合适的位置中。

假设10个数没有相等的。

8.请说明程序、指令、微程序、微指令和微命令之间的关系。

9.名词解释:流水线、超流水线、超标量、多核、超长指令字10.在单流水系统中,下列指令序列怎样的执行顺序会高效且结果不错。

lw $1, buff($0)add $2,$1,$4srl $3,$2,3addi $4,$0,5or $6,$5,$7and $7,$5,$811.在一个带有两个执行单元的按序发射的超标量处理器中,以下程序段的执行要花几个时钟周期?假定每条指令的执行都需要1个时钟周期,并且每个执行单元都能执行每条指令。

lw $1,buff($2)sub $4,$5,$6add $3,$1,$7and $8,$3,$3sw $4,buff($11)sw $8,buff($12)add $15,$14,$13sub $10,$15,$10sw $10,buff($9)12.名词解释:CISC、RISC、微程序、通道程序13.数据传输的控制方式有哪几种?哪种CPU占有率最高?14.名词解释:指令系统、堆栈、输入输出系统、接口、中断15.中断优先级有哪些判别方法?16.简述CPU对中断的响应条件和响应过程。

计算机组成原理补充题判断题1.磁盘机存储中如果文件长度超过磁道容量,会将其放在同一个记录面的不同磁道上。

2.随机存储存储器的访问时间与存储位置有关。

3.微程序控制器中,一条机器指令对应于一个微程序。

4.任何指令的执行可以由硬件来实现,也可以由软件来完成。

5..通常多级中断系统可实现中断嵌套。

6. RR、RS及SS型指令中,RR型指令的执行速度最慢。

7.寄存器间址中,实际操作数应为内存操作数。

8.半导体存储器均为易失性存储器。

9. 计算机中最小的时序定义是机器周期。

10.不同画质的同一幅图像在显存存放的信息量一样。

11.现场保护指对CPU全部资源的入栈保护。

12. 单级中断系统中,由于各中断源优先级相同而无法中断嵌套。

填空题1. 流水CPU中可能造成“断流”的主要原因是存在数据相关、资源相关和控制相关。

2.双端口存储器和多模块交叉存储器均为并行存储器结构,前者采用空间并行技术,后者采用时间并行技术。

3. 集中式仲裁通常可采用优先(级)策略或公平策略选择下一个总线主设备。

4. CPU从主存取出一条指令并执行该指令的时间叫指令周期,它通常包含若干个机器周期,而后者有包含有若干个时钟周期。

5.冯.诺依曼型计算机的工作原理为:存储程序、程序控制。

6.指令的寻址方式包括顺序寻址和跳跃寻址两种方式。

7.保存当前正在执行的指令的寄存器是指令寄存器。

8.计算机通常使用程序计数器来指定将要执行的指令的地址。

9.建立Cache的理论依据是程序访问的局部性原理。

10.磁盘上访问信息的最小物理单位是扇区。

11.计算机系统是由硬件、软件组成的多级层次结构,它通常由微程序级、一般机器级、操作系统级、汇编语言级、高级语言级组成。

12.要组成片内先行进位,片间先行进位的十六位运算器,需要4片181和1片182.13.一般来讲,取指周期从内存读出的信息流是控制流,它流向控制器;而在执行周期从内存读出的信息流是数据流,它由内存流向运算器。

第四章主存储器习题一、选择题:将正确的答案序号填在横线上1.存储器是计算机系统的记忆设备,它主要用来存放。

A.数据B.程序C.微程序D.程序和数据2.若存储器的存储周期250ns,每次读出16 位,则该存储器的数据传送率为_ _。

A. 4×106B/秒B.4MB/秒C.8×106B/秒D.8Mb/ 秒3.按字节编址的存储器中,每个编址单元中存放信息。

A.1位B.8 位C.16 位D.64 位4.和外存储器相比,内存储器的特点是。

A. 容量大、速度快、成本低B.容量大、速度慢、成本高C.容量小、速度快、成本高D.容量小、速度快、成本低5.下列存储器中,属于非易失性存储器的是。

A.RAM B.静态存储器 C.动态存储器D.ROM6.下列部件中存取速度最快的是。

A.寄存器B.Cache C.内存D.外存7.EPROM 是指。

A.读写存储器B.紫外线擦除可编程只读存储器C.闪速存储器D.电擦除可编程只读存储器8.若某单片机的系统程序不允许用户在执行时改变,则可以选用作为存储芯片。

A.SRAM B. Cache C. EEPROM D.辅助存储器9.存储周期是指。

A.存储器的读出时间B.存储器进行连续写操作所允许的最短时间间隔C.存储器的写入时间D.存储器进行连续读或写操作所允许的最短时间间隔10.设某静态RAM 芯片容量为8K×8位,若由它组成32K×8的存储器,所用的芯片数及这种芯片的片内地址线的数目分别是_。

A.4 片,13 根B.4 片,12 根C.6 片,11 根D.4 片,16 根11.若SRAM 中有 4K 个存储单元,采用双译码方式时要求译码输出线为_ _根。

A. 4096 B.64 C.128 D.102412.半导体静态存储器SRAM 能够存储信息是。

A.依靠双稳态电路B.依靠定时刷新C.依靠读后再生D.信息不再变化13.Cache 是指。

A.高速缓冲存储器 B. 主存C.ROM D. 外部存储器14.磁盘按盘片的组成材料分为软盘和。

计算机组成原理第三章习题第三章、内部存储器1、存储器是计算机系统中的记忆设备,它主要是用来_____A.存放数据B.存放程序C.存放数据和程序D.存放微程序2、存储单元是指______A.存放一个二进制信息位的存储元B.存放一个机器字的所有存储单元集合C.存放一个字节的所有存储元集合D.存放两个字节的所有存储元集合3、计算机的存储器采用分级存储体系的主要目的是________A.便于读写数据B.减小机箱的体积C.便于系统升级D.解决存储容量、价格和存取速度之间的矛盾5、和外存相比,内存的特点是____A.容量大,速度快,成本低B.容量大,速度慢,成本高C.容量小,速度快,成本高D.容量小,速度快,成本低6、某单片机字长16位,它的存储容量64KB,若按字编址,那么它的寻址范围是______A.64KB.32KC.64KBD.32KB7、某SRAM芯片,其存储容量为64K×16位,该芯片的地址线和数据线数目为_______A.64,16B.16,64C.64,8D.16,168、某DRAM芯片,其存储器容量为512K×8位,该芯片的地址线和数据线数目为________A.8,512B.512,8C.18,8D.19,89、某机器字长32位,存储容量256MB,若按字编址,它的寻址范围是_______A.1MB.512KBC.64MD.256KB10、某机器字长32位,存储容量4GB,若按字编址,它的寻址范围是_______A.1GB.4GBC.4GD.1GB11、某机器字长64位,存储容量4GB,若按字编址,它的寻址范围是_______A.4GB.2GC.0.5GD.1MB12、某机器字长32位,存储容量4GB,若按双字编址,它的寻址范围是_______A.4GB.5GC.8GD.2G13、某SRAM芯片,其容量为512×8位,包括电源端和接地端,该芯片引出线的数目应为_____A.23B.25C.50D.1914、某微型计算机系统,其操作系统保存在硬盘上,其内存储器应该采用__________A.RAMB.ROMC.RAM 和ROM/doc/7e17276989.html,D15、相联存储是按____进行寻址的存储器。

第4章主存储器一、选择题(每题3.5分)1.动态半导体存储器的特点是()A.在工作中存储器内容会产生变化B.每次读出后,需要根据原存内容重新写入一遍C.每隔一定时间,需要根据原存内容重新写入一遍D.在工作中需要动态地改变访存地址【答案】C2.某SRAM芯片,存储容量为64K×16位,该芯片的地址线和数据线数目为______。

A 64,16B 16,64C 64,8D 16,16 。

【答案】D3.交叉存贮器实质上是一种______存贮器,它能_____执行______独立的读写操作。

A 模块式,并行,多个B 模块式串行,多个C 整体式,并行,一个D 整体式,串行,多个【答案】A4. EPROM是指______。

A. 读写存储器B. 只读存储器C. 可编程的只读存储器D. 光擦除可编程的只读存储器【答案】D5.存储器是计算机系统的记忆设备,主要用于______。

A.存放程序B.存放软件C.存放微程序D.存放程序和数据【答案】D6. 外存储器与内存储器相比,外存储器______。

A.速度快,容量大,成本高B.速度慢,容量大,成本低C.速度快,容量小,成本高D.速度慢,容量大,成本高【答案】B7. 一个256K×8的存储器,其地址线和数据线总和为______。

A.16B.18C.26D.20【答案】C8.某存储器芯片的存储容量为8K×12位,则它的地址线为____。

A.11B.12C.13D.14 【答案】C9. 某一SRAM芯片,其容量为512×8位,考虑电源端和接地端,该芯片引出线的最小数目应为______。

A.23B.25C.50D.19【答案】D10.存储器是计算机系统的记忆设备,它主要用来()。

A.存放数据B.存放程序C.存放数据和程序D.存放微程序【答案】C11.内存若为16MB,则表示容量为()KB。

A.16B.16384C.1024D.16000【答案】B12.下列说法正确的是()。

习题四参考答案1.某机主存储器有16位地址,字长为8位。

(1)如果用1k×4位的RAM芯片构成该存储器,需要多少片芯片?(2)该存储器能存放多少字节的信息?(3)片选逻辑需要多少位地址?解:需要存储器总容量为:16K×8位,故,(1)需要1k×4位的RAM芯片位32片。

(2)该存储器存放16K字节的信息。

(3)片选逻辑需要4位地址。

2. 用8k×8位的静态RAM芯片构成64kB的存储器,要求:(1)计算所需芯片数。

(2)画出该存储器组成逻辑框图。

解:(1)所需芯片8片。

(2)逻辑图为:3. 用64k×1位的DRAM芯片构成256k×8位存储器,要求:(1)画出该存储器的逻辑框图。

(2)计算所需芯片数。

(3)采用分散刷新方式,如每单元刷新间隔不超过2ms,则刷新信号周期是多少?如采用集中刷新方式,存储器刷新一遍最少用多少读/写周期?解:(1)(2)所需芯片为32片。

(3)设读写周期为0.5微妙,则采用分散式刷新方式的刷新信号周期为1微妙。

因为64K ×1的存储矩阵是由四个128×128的矩阵构成,刷新时4个存储矩阵同时对128个元素操作,一次刷新就可完成512个元素,整个芯片只有128次刷新操作就可全部完成。

所以存储器刷新一遍最少用128个读/写周期。

4. 用8k×8位的EPROM芯片组成32k×16位的只读存储器,试问:(1)数据寄存器多少位?(2)地址寄存器多少位?(3)共需多少个EPROM芯片?(4)画出该只读存储器的逻辑框图?解:因为只读存储器的容量为:32k×16,所以:(1)数据寄存器16位。

(2)地址寄存器15位。

(3)共需8个EPROM芯片?(4)逻辑框图为:5. 某机器中,已经配有0000H~3FFFH的ROM区域,现在再用8k×8位的RAM芯片形成32k ×8位的存储区域,CPU地址总线为A0~A15,数据总线为D0~D7,控制信号为R/W(读/写)、MREQ(访存),要求:(1)画出地址译码方案。