Quartus操作指南

- 格式:ppt

- 大小:879.00 KB

- 文档页数:34

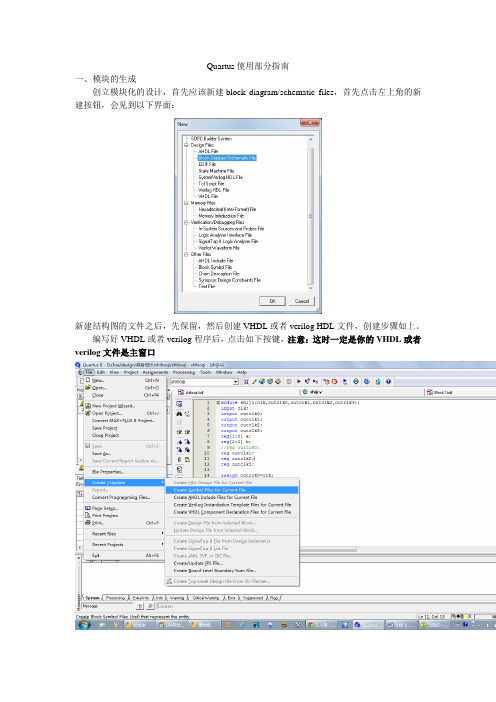

Quartus使用部分指南一、模块的生成创立模块化的设计,首先应该新建block diagram/schematic files,首先点击左上角的新建按钮,会见到以下界面:新建结构图的文件之后,先保留,然后创建VHDL或者verilog HDL文件,创建步骤如上。

编写好VHDL或者verilog程序后,点击如下按键,注意:这时一定是你的VHDL或者verilog文件是主窗口这时软件会提醒保存刚创建的block diagram/schematic files,保存时注意要和工程名一致,这样才能将这个图表文件保存成工程的主文件。

执行这步操作之后,双击block diagram/schematic files的空白处,会出现左边的PROJECT中就能找到你刚创建的模块,选择这个模块就能添加进block diagram/schematic files了,然后连线什么的就行了,同时在这个界面里的左下角的Mega……按钮可以调用出诸如锁相环PLL,ROM,RAM等IP核。

二、程序的编译过程在完成全部的程序编写之后,单击上部的编译按钮,进行编译,这时软件会识别输入输出口,检查程序是否存在语法等问题。

编译之后,单击上部的管脚设定按钮,选定管脚,管脚的选择根据开发板上标出的管脚进行选定,时钟输入管脚应该是特定的,其他的IO口可以随意选择开发板上预留出的管脚。

这时进行逻辑分析仪的设置,在新建中选择然后会进入以下界面逻辑分析仪是FPGA内部集成的一个类似于示波器的仪器,可以实时反映各个管脚和程序内部的寄存器等各种信号的变化,右边clock是其采样时钟,下面的sample depth是其采样深度,即每次显示采几个点,触发一般采取默认,如想改变可以将滚动条下来,来设置那个触发菜单。

选择采样时钟,采样深度应注意以下几点:采样时钟和被观测信号应满足采样定律,否则观测可能会出问题,此外如果采样时钟频率过高,而观测信号频率过低,则可能采样深度内所有采样点的数据都是一样,而且可能多次采样之后都是这样的,所以可能无法观测到信号的实时变化,故采样时钟的选择要有考虑,虽然一般选择大多数器件的工作频率,但是针对个别信号要进行适当的选择。

Quartus是一款FPGA(现场可编程门阵列)设计软件,它提供了主程序和子程序的使用方法。

主程序是Quartus程序的主入口,通常包含在main函数中。

主程序负责调用子程序,并控制程序的执行流程。

子程序是Quartus程序中的辅助函数或模块,它们被定义在主程序之外,并在需要时被调用。

子程序可以包含一些重复的代码,或者一些需要被多次使用的功能。

以下是使用Quartus主程序和子程序的一般步骤:

1. 创建主程序:在Quartus中创建一个新的项目,并在该项目中创建一个新的源文件(如.v或.verilog文件)。

在源文件中编写主程序的代码,包括对子程序的调用。

2. 创建子程序:在Quartus中创建一个新的源文件,并在其中定义子程序的代码。

子程序可以包含一些重复的代码或功能,例如处理数字、控制硬件等。

3. 编译和仿真:使用Quartus的编译器将源文件编译成可执行文件。

然后,使用Quartus的仿真工具对程序进行仿真,以确保程序的正确性。

4. 在FPGA上实现:将可执行文件下载到FPGA上,并使用Quartus

的配置工具对FPGA进行配置。

需要注意的是,使用Quartus主程序和子程序的具体方法可能因项目需求和硬件平台而有所不同。

因此,在使用Quartus时,建议参考相关文档和教程,以确保正确使用主程序和子程序。

Quartus II使用过程1、1. 建立工程,点击File->New Project Wizad点击New Project Wizard后弹出如下对话框点击NEXT,弹出指定工程名的对话框,在Diectory, Name,Top-Level Entity中如下图填写:点击Next按钮,出现添加工程文件的对话框:在这里我们先不用管它,直接按Next进行下一步,选择FPGA器件的型号:在Family下拉筐中,我们选择MAX II系列FPGA,然后在“Available devices:”中根据核心板的FPGA型号选择FPGA型号,注意在Filters一栏选上“Show Advanced Devices”以显示所有的器件型号。

执行下一步出现对话框:在相应位置处都选择NONE,点击NEXT进入工程的信息总概对话框:按Finish按钮即完成一个项目的建立。

2.建立顶层图执行File->New,弹出新建文件对话框:选择"Block Diagra m|Schematic File”按OK即建立一个空的顶层图3.添加逻辑元件(Symbol)双击顶层图图纸的空白处,弹出添加元件的对话筐:在Libraries里寻找所需要的逻辑元件,如果知道逻辑元件的名称的话,也可以直接在Name一栏敲入名字,右边的预览图即可显示元件的外观,按OK后鼠标旁边即拖着一个元件符号,在图纸上点击左键,元件即安放在图纸上。

在图纸上分别添加非门(not)、输入(input)、输出(output)二个symbol,如图所示:连线,将鼠标移到symbol连线端口的那里,鼠标变成连线,按下左键拖动鼠标到另一个symbol的连线端。

本例中,这三个symbol的连线如下图所示:分别双击input和output symbol的名字“pin_ name", "pin_ namel",将它们的名字改为a,b.在工具栏上点击Start Analysis&Synthesis,出现如下对话框。

Quartus II的使用1、开始一个新的逻辑电路设计,第一步就是新建一个文件夹来保存文件,这里在D盘新建了introtutorial文件夹。

2、打开Quartus II软件,将会看到图1界面,该显示界面包括若干窗口,可以使用鼠标选择,以访问Quartus II软件的相关功能。

Quartus II提供的大多数命令都可用菜单形式来访问。

图1 Quartus II主体显示3、按如下步骤新建工程:①选择File>New Project Wizard,以打开图2所示窗口,可通过Don't show me this introduction again跳过此窗口步骤。

单击Next,出现图3所示窗口。

图2 引导的任务显示图3 创建新的工程②选择工作文件夹introtutorial,也可以使用您自己设定的文件夹。

工程必须有一个名字,通常情况下,与顶层设计实体的名字相同。

如图3所示,这里选择light作为工程名和顶层实体名。

单击Next。

如果还没有创建introtutorial文件夹,Quartus II会弹出一个对话框,询问是否新建所需文件夹,如图4所示。

单击Yes,将会引出图5所示的窗口。

图4 创建新的工程文件夹与否?图5 添加用户指定设计文件③如果没有已存在的设计文件,单击Next,将会打开如图6所示的画面。

图6 选择器件家族和指定的器件④此处选择的器件为EPM3064ATC100-10,器件家族为MAX3000A,有100个管脚,单击Next,出现图所示7画面。

图7 指定第三方EDA工具⑤用户可指定一些第三方EDA工具,这里没有进行Simulation选用,单击Next,出现图8所示窗口,单击Finish,返回Quartus II主体窗口。

标题栏将显示light工程,如图9所示。

图8 工程设置一览图9 Quartus II显示已建工程3 使用Verilog代码设计输入使用Verilog代码来描述。

使用Quartus设计数字电路系统的流程1. 准备工作在开始使用Quartus设计数字电路系统之前,需要进行一些准备工作:•安装Quartus软件:根据你的操作系统下载并安装Quartus软件。

Quartus支持Windows和Linux操作系统,并提供30天的免费试用期。

•获取开发板:选择一块兼容Quartus的开发板,例如Altera提供的Cyclone系列开发板。

•了解基本概念:熟悉数字电路设计的基本概念,如逻辑门、触发器、计数器等。

2. 创建工程在Quartus中创建一个新的工程以开始数字电路设计:1.启动Quartus软件。

2.打开“File”菜单,选择“New Project Wizard”。

3.在弹出的对话框中,选择工程名称和存储位置。

4.选择目标设备类型和型号,并确认。

5.选择设计文件的类型,可以选择使用VHDL或Verilog进行设计。

6.添加设计文件到工程中。

3. 设计电路在Quartus中设计数字电路系统有两种主要的方法:使用逻辑图或硬件描述语言(VHDL或Verilog)。

3.1 使用逻辑图1.打开“Tools”菜单,选择“Block Diagram/Schematic File”。

2.在弹出的对话框中,选择使用排版编辑器或图形编辑器进行设计。

3.使用逻辑图元件工具,如逻辑门、触发器等,拖放到设计区域。

4.连接逻辑图元件并设置其属性和功能。

5.保存设计并编译。

3.2 使用VHDL或Verilog1.打开“File”菜单,选择“New”,再选择“Design Files”。

2.在弹出的对话框中,选择使用VHDL或Verilog进行设计。

3.在代码编辑器中编写设计代码。

4.保存设计文件并编译。

4. 仿真在Quartus中进行仿真可以验证设计的正确性以及进行性能评估。

1.打开“Tools”菜单,选择“RTL Simulation”。

2.在弹出的对话框中,选择仿真工具和仿真文件。

Quartus使用的简易流程简介Quartus是一种集成电路设计工具,广泛应用于数字电路和逻辑设计。

本文将介绍Quartus的使用流程,包括安装、项目创建、设计与仿真、编译、下载与调试等步骤。

安装1.下载Quartus软件包并解压缩。

2.运行安装程序,并按照提示完成安装过程。

项目创建1.打开Quartus软件。

2.在欢迎界面点击“New Project”创建新项目。

3.设置项目名称和存放位置。

4.选择适当的目标设备和波特率设置。

5.点击“Next”进入下一步。

6.添加需要的源文件和约束文件。

7.点击“Finish”完成项目创建。

设计与仿真1.双击项目中的设计文件以打开编辑器。

2.使用编辑器进行设计与编码。

3.选择合适的仿真工具,如ModelSim。

4.配置仿真工具的设置。

5.运行仿真,检查设计的正确性。

编译1.点击“Compile Design”按钮开始编译设计。

2.等待编译完成。

下载与调试1.连接开发板或FPGA设备到计算机。

2.点击“Assignments”菜单,选择“Device”。

3.配置下载设置,包括设备和下载文件。

4.点击“Start”按钮开始下载。

5.下载完成后,进行调试和验证设计功能。

总结本文介绍了Quartus使用的简易流程,包括安装、项目创建、设计与仿真、编译、下载与调试等步骤。

希望通过这些简要的步骤能够帮助您更好地使用Quartus 进行集成电路设计。

如果您有其他疑问,请参考Quartus的官方文档或寻求相关的帮助。

实验一_QuartusII的使用引言:Quartus II是一款由美国Intel公司开发的FPGA设计软件,广泛应用于数字集成电路设计和原型验证。

本实验将介绍Quartus II的基本使用方法,包括项目创建、设计输入、约束设置、编译与仿真等。

一、环境准备二、项目创建1.启动Quartus II软件,选择"File" -> "New Project Wizard"创建新项目。

在弹出的对话框中,选择项目的存储位置和名称,并选择合适的目标设备和设计流程。

点击"Next"进入下一步。

2.在第二步中,选择项目的项目类型和是否要添加预定义的IP (Intellectual Property)核。

IP核是现成的、可重用的模块,可以简化设计。

根据自己的需求进行选择,点击"Next"。

3.在第三步中,选择顶层设计文件的命名,并点击"Next"。

5.在第五步中,对项目的设置进行回顾,并点击"Finish"完成项目创建。

三、设计输入1.双击项目中的顶层设计文件,打开Design Entry工具。

在Design Entry工具中,可以通过图形界面或者Verilog/VHDL语言进行设计输入。

a.如果选择使用图形界面,可以在左侧工具栏中选择需要的元件,然后在设计区域中拖拽放置,最终形成需要的电路结构。

b.如果选择使用Verilog/VHDL语言,可以在设计区域中输入相应的代码,然后进行语法检查。

2.在设计完成后,可以使用编译按钮对设计进行编译。

编译过程中,Quartus II会对设计进行分析、优化和进行布线等操作,生成逻辑网表。

四、约束设置1.双击项目中的顶层设计文件,打开Design Constraints工具。

在Design Constraints工具中,可以设置时钟频率、信号约束、引脚约束等。